Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Becano                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 44-VTLA (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f064dt-i-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 6: PIN NAMES FOR 28-PIN USB DEVICES

## 28-PIN QFN (TOP VIEW)<sup>(1,2,3,4)</sup>

PIC32MX210F016B PIC32MX220F032B PIC32MX230F064B PIC32MX230F256B PIC32MX250F128B PIC32MX250F128B

28

1

| Pin # | Full Pin Name                              | Pin # | Full Pin Name                                    |

|-------|--------------------------------------------|-------|--------------------------------------------------|

| 1     | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0  | 15    | TDO/RPB9/SDA1/CTED4/PMD3/RB9                     |

| 2     | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1 | 16    | Vss                                              |

| 3     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2  | 17    | VCAP                                             |

| 4     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3    | 18    | PGED2/RPB10/D+/CTED11/RB10                       |

| 5     | Vss                                        | 19    | PGEC2/RPB11/D-/RB11                              |

| 6     | OSC1/CLKI/RPA2/RA2                         | 20    | VUSB3V3                                          |

| 7     | OSC2/CLKO/RPA3/PMA0/RA3                    | 21    | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 8     | SOSCI/RPB4/RB4                             | 22    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 9     | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4             | 23    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 10    | Vdd                                        | 24    | AVss                                             |

| 11    | TMS/RPB5/USBID/RB5                         | 25    | AVDD                                             |

| 12    | VBUS                                       | 26    | MCLR                                             |

| 13    | TDI/RPB7/CTED3/PMD5/INT0/RB7               | 27    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 14    | TCK/RPB8/SCL1/CTED10/PMD4/RB8              | 28    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: Shaded pins are 5V tolerant.

#### TABLE 10: PIN NAMES FOR 44-PIN USB DEVICES

#### 44-PIN QFN (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX210F016D PIC32MX220F032D PIC32MX230F064D PIC32MX230F256D PIC32MX250F128D PIC32MX270F256D

|       |                                                  |       | 44 1                                      |

|-------|--------------------------------------------------|-------|-------------------------------------------|

| Pin # | Full Pin Name                                    | Pin # | Full Pin Name                             |

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                         | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 2     | RPC6/PMA1/RC6                                    | 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 3     | RPC7/PMA0/RC7                                    | 25    | AN6/RPC0/RC0                              |

| 4     | RPC8/PMA5/RC8                                    | 26    | AN7/RPC1/RC1                              |

| 5     | RPC9/CTED7/PMA6/RC9                              | 27    | AN8/RPC2/PMA2/RC2                         |

| 6     | Vss                                              | 28    | Vdd                                       |

| 7     | VCAP                                             | 29    | Vss                                       |

| 8     | PGED2/RPB10/D+/CTED11/RB10                       | 30    | OSC1/CLKI/RPA2/RA2                        |

| 9     | PGEC2/RPB11/D-/RB11                              | 31    | OSC2/CLKO/RPA3/RA3                        |

| 10    | VUSB3V3                                          | 32    | TDO/RPA8/PMA8/RA8                         |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                       | 33    | SOSCI/RPB4/RB4                            |

| 12    | PGED4/TMS/PMA10/RA10                             | 34    | SOSCO/RPA4/T1CK/CTED9/RA4                 |

| 13    | PGEC4/TCK/CTED8/PMA7/RA7                         | 35    | TDI/RPA9/PMA9/RA9                         |

| 14    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 | 36    | AN12/RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            | 37    | RPC4/PMA4/RC4                             |

| 16    | AVss                                             | 38    | RPC5/PMA3/RC5                             |

| 17    | AVDD                                             | 39    | Vss                                       |

| 18    | MCLR                                             | 40    | Vdd                                       |

| 19    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 | 41    | RPB5/USBID/RB5                            |

| 20    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       | 42    | VBUS                                      |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        | 43    | RPB7/CTED3/PMD5/INT0/RB7                  |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       | 44    | RPB8/SCL1/CTED10/PMD4/RB8                 |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

5: Shaded pins are 5V tolerant.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site:

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- *"MPLAB<sup>®</sup> ICD 3 Design Advisory"* (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

### 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

## 2.7 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

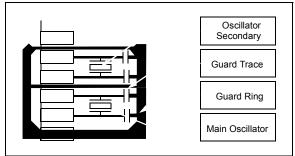

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

#### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

## 2.8 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

#### 7.1 Interrupt Control Registers

#### TABLE 7-2: INTERRUPT REGISTER MAP

| ess                         |                                 | â             |        |        |        |         |             |         |            | Bits    |        |          |          |            |                      |            |        |        |               |

|-----------------------------|---------------------------------|---------------|--------|--------|--------|---------|-------------|---------|------------|---------|--------|----------|----------|------------|----------------------|------------|--------|--------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14  | 29/13  | 28/12   | 27/11       | 26/10   | 25/9       | 24/8    | 23/7   | 22/6     | 21/5     | 20/4       | 19/3                 | 18/2       | 17/1   | 16/0   | All<br>Resets |

| 1000                        | INTCON                          | 31:16         | _      | _      | —      | _       |             |         | _          | -       |        |          | _        | _          |                      | —          |        |        | 0000          |

| 1000                        | INTCOM                          | 15:0          | —      | _      | —      | MVEC    | -           |         | TPC<2:0>   |         | -      | —        | _        | INT4EP     | INT3EP               | INT2EP     | INT1EP | INT0EP | 0000          |

| 1010                        | INTSTAT <sup>(3)</sup>          | 31:16         | —      |        | —      | _       | _           | _       | —          | —       |        | _        | _        | _          |                      |            | —      | —      | 0000          |

| 1010                        | INTOTAL                         | 15:0          | —      | _      | —      | —       | _           |         | SRIPL<2:0> |         | _      | _        |          |            | VEC<5:0              | )>         |        |        | 0000          |

| 1020                        | IPTMR                           | 31:16<br>15:0 |        |        |        |         |             |         |            | IPTMR<3 | 1:0>   |          |          |            |                      |            |        |        | 0000          |

| 1020 1550                   |                                 | 31:16         | FCEIF  | RTCCIF | FSCMIF | AD1IF   | OC5IF       | IC5IF   | IC5EIF     | T5IF    | INT4IF | OC4IF    | IC4IF    | IC4EIF     | T4IF                 | INT3IF     | OC3IF  | IC3IF  | 0000          |

| 1030                        | IFS0                            | 15:0          | IC3EIF | T3IF   | INT2IF | OC2IF   | IC2IF       | IC2EIF  | T2IF       | INT1IF  | OC1IF  | IC1IF    | IC1EIF   | T1IF       | INT0IF               | CS1IF      | CS0IF  | CTIF   | 0000          |

| 1010                        | 1504                            | 31:16         | DMA3IF | DMA2IF | DMA1IF | DMA0IF  | CTMUIF      | I2C2MIF | I2C2SIF    | I2C2BIF | U2TXIF | U2RXIF   | U2EIF    | SPI2TXIF   | SPI2RXIF             | SPI2EIF    | PMPEIF | PMPIF  | 0000          |

| 1040                        | IFS1                            | 15:0          | CNCIF  | CNBIF  | CNAIF  | I2C1MIF | I2C1SIF     | I2C1BIF | U1TXIF     | U1RXIF  | U1EIF  | SPI1TXIF | SPI1RXIF | SPI1EIF    | USBIF <sup>(2)</sup> | CMP3IF     | CMP2IF | CMP1IF | 0000          |

| 1060                        | IEC0                            | 31:16         | FCEIE  | RTCCIE | FSCMIE | AD1IE   | OC5IE       | IC5IE   | IC5EIE     | T5IE    | INT4IE | OC4IE    | IC4IE    | IC4EIE     | T4IE                 | INT3IE     | OC3IE  | IC3IE  | 0000          |

| 1060                        |                                 | 15:0          | IC3EIE | T3IE   | INT2IE | OC2IE   | IC2IE       | IC2EIE  | T2IE       | INT1IE  | OC1IE  | IC1IE    | IC1EIE   | T1IE       | INT0IE               | CS1IE      | CS0IE  | CTIE   | 0000          |

| 1070                        | IEC1                            | 31:16         | DMA3IE | DMA2IE | DMA1IE | DMA0IE  | CTMUIE      | I2C2MIE | I2C2SIE    | I2C2BIE | U2TXIE | U2RXIE   | U2EIE    | SPI2TXIE   | SPI2RXIE             | SPI2EIE    | PMPEIE | PMPIE  | 0000          |

| 1070                        |                                 | 15:0          | CNCIE  | CNBIE  | CNAIE  | I2C1MIE | I2C1SIE     | I2C1BIE | U1TXIE     | U1RXIE  | U1EIE  | SPI1TXIE | SPI1RXIE | SPI1EIE    | USBIE <sup>(2)</sup> | CMP3IE     | CMP2IE | CMP1IE | 0000          |

| 1090                        | IPC0                            | 31:16         | —      | _      | —      |         | INT0IP<2:0> |         | INTOIS     | <1:0>   | -      | —        | _        | CS1IP<2:0> |                      | CS1IS<1:0> |        | 0000   |               |

| 1030                        | 11 00                           | 15:0          | —      | —      | —      |         | CS0IP<2:0>  |         | CS0IS      | <1:0>   | _      | —        | —        | CTIP<2:0>  |                      | CTIS       | <1:0>  | 0000   |               |

| 10A0                        | IPC1                            | 31:16         | —      |        | —      |         | INT1IP<2:0> |         | INT1IS     | <1:0>   | _      | —        | _        | 0          | C1IP<2:0>            |            | OC1IS  | S<1:0> | 0000          |

| 10,10                       |                                 | 15:0          | —      | —      | —      |         | IC1IP<2:0>  |         | IC1IS•     | <1:0>   | _      | —        | —        | ٦          | Γ1IP<2:0>            |            | T1IS   | <1:0>  | 0000          |

| 10B0                        | IPC2                            | 31:16         | _      | —      | —      |         | INT2IP<2:0> |         | INT2IS     | <1:0>   | _      | —        | _        | 0          | C2IP<2:0>            |            | OC2IS  | 6<1:0> | 0000          |

| 1000                        | 11 02                           | 15:0          | —      |        | —      |         | IC2IP<2:0>  |         | IC2IS<     | <1:0>   | _      | —        | _        | 1          | [21P<2:0>            |            | T2IS   | <1:0>  | 0000          |

| 10C0                        | IPC3                            | 31:16         | —      | —      | —      |         | INT3IP<2:0> |         | INT3IS     | <1:0>   | —      |          | —        | 0          | C3IP<2:0>            |            | OC3IS  | 6<1:0> | 0000          |

| 1000                        | 1 00                            | 15:0          | —      | —      | —      |         | IC3IP<2:0>  |         | IC3IS<     | <1:0>   | —      |          | —        |            | [3IP<2:0>            |            | T3IS-  |        | 0000          |

| 10D0                        | IPC4                            | 31:16         | —      |        | —      |         | INT4IP<2:0> |         | INT4IS     | <1:0>   | _      | —        | _        | 0          | C4IP<2:0>            |            | OC4IS  | S<1:0> | 0000          |

| 1020                        |                                 | 15:0          | —      | —      | —      |         | IC4IP<2:0>  |         | IC4IS<     | <1:0>   |        | —        | _        | 1          | [4IP<2:0>            |            | T4IS   | <1:0>  | 0000          |

| 10E0                        | IPC5                            | 31:16         | —      | —      | —      |         | AD1IP<2:0>  |         | AD1IS      | -       | _      | —        | _        | 0          | C5IP<2:0>            |            | OC5IS  | S<1:0> | 0000          |

| 1020                        |                                 | 15:0          | —      | _      | —      |         | IC5IP<2:0>  |         | IC5IS<     |         | -      | —        | —        | T5IP<2:0>  |                      | T5IS<1:0>  |        | 0000   |               |

| 10F0                        | IPC6                            | 31:16         | —      | —      | —      |         | CMP1IP<2:0> |         | CMP1IS     |         |        | _        | —        | F          | CEIP<2:0>            |            | FCEIS  | S<1:0> | 0000          |

| 101 0                       |                                 | 15:0          | —      | —      | —      | F       | RTCCIP<2:0> |         | RTCCIS     | 6<1:0>  | —      |          | _        | FS         | CMIP<2:0>            | >          | FSCMI  | S<1:0> | 0000          |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX1XX devices.

3: This register does not have associated CLR, SET, INV registers.

| REGIST  | ER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER (CONTINUED)                                                         |  |  |  |  |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| bit 9-8 | IS01<1:0>: Interrupt Subpriority bits                                                                                 |  |  |  |  |  |  |  |

|         | 11 = Interrupt subpriority is 3                                                                                       |  |  |  |  |  |  |  |

|         | 10 = Interrupt subpriority is 2                                                                                       |  |  |  |  |  |  |  |

|         | 01 = Interrupt subpriority is 1                                                                                       |  |  |  |  |  |  |  |

|         | 00 = Interrupt subpriority is 0                                                                                       |  |  |  |  |  |  |  |

| bit 7-5 | Unimplemented: Read as '0'                                                                                            |  |  |  |  |  |  |  |

| bit 4-2 | IP00<2:0>: Interrupt Priority bits                                                                                    |  |  |  |  |  |  |  |

|         | 111 = Interrupt priority is 7                                                                                         |  |  |  |  |  |  |  |

|         | •                                                                                                                     |  |  |  |  |  |  |  |

|         | •                                                                                                                     |  |  |  |  |  |  |  |

|         | •                                                                                                                     |  |  |  |  |  |  |  |

|         | 010 = Interrupt priority is 2                                                                                         |  |  |  |  |  |  |  |

|         | 001 = Interrupt priority is 1                                                                                         |  |  |  |  |  |  |  |

|         | 000 = Interrupt is disabled                                                                                           |  |  |  |  |  |  |  |

| bit 1-0 | IS00<1:0>: Interrupt Subpriority bits                                                                                 |  |  |  |  |  |  |  |

|         | 11 = Interrupt subpriority is 3                                                                                       |  |  |  |  |  |  |  |

|         | 10 = Interrupt subpriority is 2                                                                                       |  |  |  |  |  |  |  |

|         | 01 = Interrupt subpriority is 1                                                                                       |  |  |  |  |  |  |  |

|         | 00 = Interrupt subpriority is 0                                                                                       |  |  |  |  |  |  |  |

| Note:   | This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions. |  |  |  |  |  |  |  |

#### REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- bit 3-0 ROSEL<3:0>: Reference Clock Source Select bits<sup>(1)</sup>

- 1111 = Reserved; do not use

- 1001 = Reserved; do not use 1000 = REFCLKI 0111 = System PLL output 0110 = USB PLL output 0101 = Sosc 0100 = LPRC 0011 = FRC 0010 = POSC 0001 = PBCLK 0000 = SYSCLK

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- 2: This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

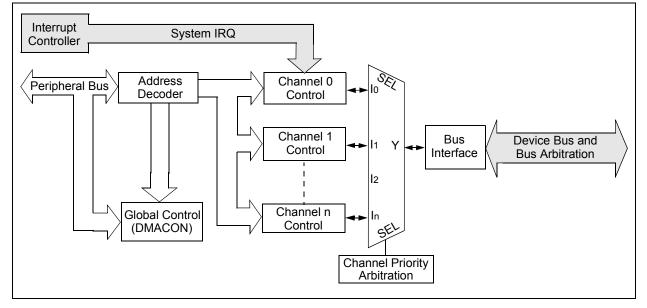

## 9.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32, such as Peripheral Bus devices: SPI, UART, PMP, etc., or memory itself. Figure 9-1 show a block diagram of the DMA Controller module.

The DMA Controller module has the following key features:

- Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

#### FIGURE 9-1: DMA BLOCK DIAGRAM

- Fixed priority channel arbitration

- · Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- · Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- · Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 21.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24     | CHSSA<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00:40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16     | CHSSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8      | CHSSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0       |                   |                   |                   | CHSSA             | <7:0>             |                   |                  |                  |  |  |  |  |

#### **REGISTER 9-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER**

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0

CHSSA<31:0> Channel Source Start Address bits

Channel source start address.

Note: This must be the physical address of the source.

#### **REGISTER 9-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | CHDSA<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | CHDSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | CHDSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | CHDSA             | <7:0>             |                   |                  |                  |  |  |  |

| Legend:           |                  |                                          |                    |  |  |  |

|-------------------|------------------|------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | e bit U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                     | x = Bit is unknown |  |  |  |

bit 31-0 **CHDSA<31:0>:** Channel Destination Start Address bits Channel destination start address.

$\ensuremath{\textbf{Note:}}$  This must be the physical address of the destination.

## 12.2 Timer1 Control Registers

### TABLE 12-1: TIMER1 REGISTER MAP

| ess                       | Register<br>Name <sup>(1)</sup> | 0         |       |       |       |       |       |       |      | В    | its    |      |       |        |      |       |      |      | s          |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|--------|------|-------|--------|------|-------|------|------|------------|

| Virtual Addre<br>(BF80_#) |                                 | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7   | 22/6 | 21/5  | 20/4   | 19/3 | 18/2  | 17/1 | 16/0 | All Resets |

| 0600                      | T1CON                           | 31:16     | _     | _     | _     | _     | _     | —     | _    | —    | _      | —    | —     | —      | _    | —     | _    | _    | 0000       |

| 0600                      | TICON                           | 15:0      | ON    | —     | SIDL  | TWDIS | TWIP  | —     | _    | —    | TGATE  | _    | TCKPS | S<1:0> | —    | TSYNC | TCS  | _    | 0000       |

| 0610                      | TMR1                            | 31:16     | —     | -     | —     | —     | —     | —     | —    | —    | —      | —    | _     | _      | —    | —     | —    | —    | 0000       |

| 0010                      |                                 | 15:0      |       |       |       |       |       |       |      | TMR1 | <15:0> |      |       |        |      |       |      |      | 0000       |

| 0620                      | PR1                             | 31:16     | —     | _     | _     | _     | _     | —     |      | —    | —      | _    | —     | _      | _    | _     | _    |      | 0000       |

| 0020                      | PRI                             | 15:0      |       |       |       |       |       |       |      | PR1< | :15:0> |      |       |        |      |       |      |      | FFFF       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

NOTES:

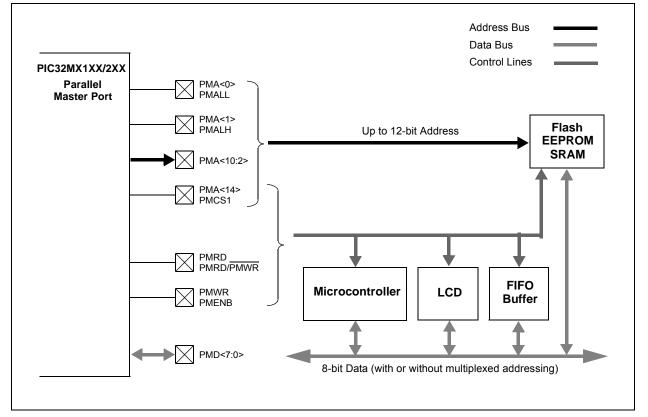

## 20.0 PARALLEL MASTER PORT (PMP)

| Note: | This data sheet summarizes the features<br>of the PIC32MX1XX/2XX 28/36/44-pin<br>Family of devices. It is not intended to be<br>a comprehensive reference source. To<br>complement the information in this data<br>sheet, refer to Section 13. "Parallel<br>Master Port (PMP)" (DS60001128), |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | which is available from the <i>Documentation</i><br>> <i>Reference Manual</i> section of the<br>Microchip PIC32 web site<br>(www.microchip.com/pic32).                                                                                                                                       |

The PMP is a parallel 8-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable. Key features of the PMP module include:

- Fully multiplexed address/data mode

- Demultiplexed or partially multiplexed address/ data mode

- up to 11 address lines with single Chip Select

- up to 12 address lines without Chip Select

- One Chip Select line

- Programmable strobe options

- Individual read and write strobes or;

- Read/write strobe with enable strobe

- · Address auto-increment/auto-decrement

- Programmable address/data multiplexing

- Programmable polarity on control signals

- · Legacy parallel slave port support

- · Enhanced parallel slave support

- Address support

- 4-byte deep auto-incrementing buffer

- · Programmable Wait states

- · Selectable input voltage levels

Figure 20-1 illustrates the PMP module block diagram.

#### FIGURE 20-1: PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 |                     | _                 | _                 |                   | —                | _                |

| 00.40        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                   | _                 | _                 |                   | —                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 15:8         | ON <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | _                 | —                 | —                 | —                | COUT             |

| 7.0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7:0          | EVPOL             | _<1:0>            |                     | CREF              | _                 | _                 | CCH              | <1:0>            |

#### REGISTER 23-1: CMXCON: COMPARATOR CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

- bit 14 **COE:** Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

- bit 12-9 Unimplemented: Read as '0'

- bit 8 **COUT:** Comparator Output bit

- 1 = Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 **EVPOL<1:0>:** Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

- bit 4 CREF: Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CXINA pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the CxIND pin

- 01 = Comparator inverting input is connected to the CxINC pin

- 00 = Comparator inverting input is connected to the CxINB pin

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

#### REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED)

- bit 10 EDGSEQEN: Edge Sequence Enable bit 1 = Edge1 must occur before Edge2 can occur 0 = No edge sequence is needed IDISSEN: Analog Current Source Control bit<sup>(2)</sup> bit 9 1 = Analog current source output is grounded 0 = Analog current source output is not grounded bit 8 **CTTRIG:** Trigger Control bit 1 = Trigger output is enabled 0 = Trigger output is disabled bit 7-2 ITRIM<5:0>: Current Source Trim bits 011111 = Maximum positive change from nominal current 011110 000001 = Minimum positive change from nominal current 000000 = Nominal current output specified by IRNG<1:0> 111111 = Minimum negative change from nominal current 100010 100001 = Maximum negative change from nominal current bit 1-0 IRNG<1:0>: Current Range Select bits<sup>(3)</sup> 11 = 100 times base current 10 = 10 times base current

- 01 = Base current level

- 00 = 1000 times base current<sup>(4)</sup>

- Note 1: When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- Refer to the CTMU Current Source Specifications (Table 30-41) in Section 30.0 "Electrical 3: Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

| DC CHARACTERISTICS                   |        |                                                           |      | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |                                                                                         |  |

|--------------------------------------|--------|-----------------------------------------------------------|------|-------------------------------------------------------|------|-------|-----------------------------------------------------------------------------------------|--|

| Param.<br>No. Symbol Characteristics |        |                                                           | Min. | Typical                                               | Max. | Units | Comments                                                                                |  |

| D300                                 | VIOFF  | Input Offset Voltage                                      | -    | ±7.5                                                  | ±25  | mV    | AVDD = VDD,<br>AVSS = VSS                                                               |  |

| D301                                 | VICM   | Input Common Mode Voltage                                 | 0    | -                                                     | Vdd  | V     | AVDD = VDD,<br>AVss = Vss<br>(Note 2)                                                   |  |

| D302                                 | CMRR   | Common Mode Rejection Ratio                               | 55   | —                                                     | _    | dB    | Max VICM = (VDD - 1)V<br>(Note 2)                                                       |  |

| D303A                                | Tresp  | Large Signal Response Time                                | _    | 150                                                   | 400  | ns    | AVDD = VDD, AVSS = VSS<br>(Note 1,2)                                                    |  |

| D303B                                | TSRESP | Small Signal Response Time                                | -    | 1                                                     | _    | μS    | This is defined as an input<br>step of 50 mV with 15 mV<br>of overdrive <b>(Note 2)</b> |  |

| D304                                 | ON2ov  | Comparator Enabled to Output<br>Valid                     | _    | _                                                     | 10   | μs    | Comparator module is<br>configured before setting<br>the comparator ON bit<br>(Note 2)  |  |

| D305                                 | IVREF  | Internal Voltage Reference                                | 1.14 | 1.2                                                   | 1.26 | V     | _                                                                                       |  |

| D312                                 | TSET   | Internal Comparator Voltage<br>DRC Reference Setting time | _    | —                                                     | 10   | μs    | (Note 3)                                                                                |  |

#### TABLE 30-13: COMPARATOR SPECIFICATIONS

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

**2:** These parameters are characterized but not tested.

**3:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

**4:** The Comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

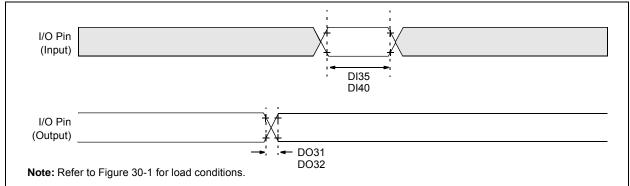

#### FIGURE 30-3: I/O TIMING CHARACTERISTICS

#### TABLE 30-21: I/O TIMING REQUIREMENTS

| AC CHAF                          | RACTERIS                       | STICS                 | Standard Ope<br>(unless other<br>Operating tem | wise state             |      | ≤ +85°C fc | or Industria |            |

|----------------------------------|--------------------------------|-----------------------|------------------------------------------------|------------------------|------|------------|--------------|------------|

| Param.<br>No. Symbol Characteris |                                | stics <sup>(2)</sup>  | Min.                                           | Typical <sup>(1)</sup> | Max. | Units      | Conditions   |            |

| DO31                             | TIOR Port Output Rise Time     |                       | ne                                             |                        | 5    | 15         | ns           | Vdd < 2.5V |

|                                  |                                |                       |                                                |                        | 5    | 10         | ns           | Vdd > 2.5V |

| DO32                             | TIOF                           | Port Output Fall Time |                                                | _                      | 5    | 15         | ns           | Vdd < 2.5V |

|                                  | DI35 TINP INTx Pin High or Low |                       |                                                |                        | 5    | 10         | ns           | VDD > 2.5V |

| DI35                             |                                |                       | w Time                                         | 10                     | _    | _          | ns           | _          |

| DI40                             | Trbp                           | CNx High or Low Tir   | me (input)                                     | 2                      | _    |            | TSYSCLK      |            |

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: This parameter is characterized, but not tested in manufacturing.

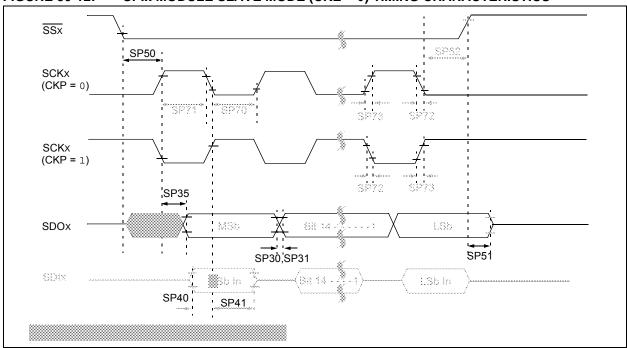

#### FIGURE 30-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

#### TABLE 30-30: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS                           |                       |                                                                    | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                     |      |       |                    |  |

|----------------------------------------------|-----------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|--|

| Param. Symbol Characteristics <sup>(1)</sup> |                       |                                                                    | Min.                                                                                                                                                                                                          | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |  |

| SP70                                         | TscL                  | SCKx Input Low Time (Note 3)                                       | TSCK/2                                                                                                                                                                                                        | —                   | _    | ns    | —                  |  |

| SP71                                         | TscH                  | SCKx Input High Time (Note 3)                                      | TSCK/2                                                                                                                                                                                                        | —                   | _    | ns    | —                  |  |

| SP72                                         | TscF                  | SCKx Input Fall Time                                               | —                                                                                                                                                                                                             | _                   |      | ns    | See parameter DO32 |  |

| SP73                                         | TscR                  | SCKx Input Rise Time                                               | —                                                                                                                                                                                                             | —                   | _    | ns    | See parameter DO31 |  |

| SP30                                         | TDOF                  | SDOx Data Output Fall Time (Note 4)                                | —                                                                                                                                                                                                             | —                   |      | ns    | See parameter DO32 |  |

| SP31                                         | TDOR                  | SDOx Data Output Rise Time (Note 4)                                | _                                                                                                                                                                                                             | _                   | _    | ns    | See parameter DO31 |  |

| SP35                                         | TscH2doV,             | SDOx Data Output Valid after                                       | —                                                                                                                                                                                                             | _                   | 15   | ns    | VDD > 2.7V         |  |

|                                              | TscL2DoV              | SCKx Edge                                                          | —                                                                                                                                                                                                             | —                   | 20   | ns    | VDD < 2.7V         |  |

| SP40                                         | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge                         | 10                                                                                                                                                                                                            |                     |      | ns    | —                  |  |

| SP41                                         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge                       | 10                                                                                                                                                                                                            | _                   | _    | ns    | —                  |  |

| SP50                                         | TssL2scH,<br>TssL2scL | $\overline{\text{SSx}}\downarrow$ to SCKx $\uparrow$ or SCKx Input | 175                                                                                                                                                                                                           |                     |      | ns    | —                  |  |

| SP51                                         | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <b>(Note 3)</b>             | 5                                                                                                                                                                                                             | —                   | 25   | ns    | _                  |  |

| SP52                                         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                                | Тѕск + 20                                                                                                                                                                                                     | —                   |      | ns    | —                  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: The minimum clock period for SCKx is 50 ns.

4: Assumes 50 pF load on all SPIx pins.

#### TABLE 30-33: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE) (CONTINUED)

| AC CHA                               | RACTERIS   |                            | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |      |       |                                                  |

|--------------------------------------|------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------------------------------------------------|

| Param.<br>No. Symbol Characteristics |            |                            |                                                                                                                                                                                                                                                                                     | Min. | Max. | Units | Conditions                                       |

| IS34                                 | THD:STO    | Stop Condition             | 100 kHz mode                                                                                                                                                                                                                                                                        | 4000 | _    | ns    | —                                                |

|                                      |            | Hold Time                  | 400 kHz mode                                                                                                                                                                                                                                                                        | 600  | —    | ns    |                                                  |

|                                      |            |                            | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                              | 250  |      | ns    |                                                  |

| IS40                                 | 40 TAA:SCL | Output Valid from<br>Clock | 100 kHz mode                                                                                                                                                                                                                                                                        | 0    | 3500 | ns    | —                                                |

|                                      |            |                            | 400 kHz mode                                                                                                                                                                                                                                                                        | 0    | 1000 | ns    |                                                  |

|                                      |            |                            | 1 MHz mode<br><b>(Note 1)</b>                                                                                                                                                                                                                                                       | 0    | 350  | ns    |                                                  |

| IS45                                 | TBF:SDA    | Bus Free Time              | 100 kHz mode                                                                                                                                                                                                                                                                        | 4.7  | —    | μs    | The amount of time the bus                       |

|                                      |            |                            | 400 kHz mode                                                                                                                                                                                                                                                                        | 1.3  | —    | μs    | must be free before a new transmission can start |

|                                      |            |                            | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                              | 0.5  | —    | μS    |                                                  |

| IS50                                 | Св         | Bus Capacitive Lo          | ading                                                                                                                                                                                                                                                                               |      | 400  | pF    | —                                                |

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

| AC CHARAG                         | S <sup>(2)</sup> | (unless of            | Operating<br>herwise state<br>temperature |                 |                            |

|-----------------------------------|------------------|-----------------------|-------------------------------------------|-----------------|----------------------------|

| ADC Speed                         | TAD Min.         | Sampling<br>Time Min. | Rs Max.                                   | Vdd             | ADC Channels Configuration |

| 1 Msps to 400 ksps <sup>(1)</sup> | 65 ns            | 132 ns                | 500Ω                                      | 3.0V to<br>3.6V | ANX CHX ADC                |

| Up to 400 ksps                    | 200 ns           | 200 ns                | 5.0 kΩ                                    | 2.5V to<br>3.6V | ANX CHX<br>ANX OF VREF-    |

#### TABLE 30-35:10-BIT CONVERSION RATE PARAMETERS

**Note 1:** External VREF- and VREF+ pins must be used for correct operation.

2: These parameters are characterized, but not tested in manufacturing.

**3:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

| U1OTGSTAT (USB OTG Status)       | 110 |

|----------------------------------|-----|

| U1PWRC (USB Power Control)       | 112 |

| U1SOF (USB SOF Threshold)        | 123 |

| U1STAT (USB Status)              | 118 |

| U1TOK (USB Token)                | 122 |

| UxMODE (UARTx Mode)              |     |

| UxSTA (UARTx Status and Control) | 185 |

| WDTCON (Watchdog Timer Control)  | 155 |

| Resets                           |     |

| Revision History                 |     |

| RTCALRM (RTC ALARM Control)      |     |

## S

| Serial Peripheral Interface (SPI) | 165 |

|-----------------------------------|-----|

| Software Simulator (MPLAB SIM)    |     |

| Special Features                  | 239 |

### Т

| Timer1 Module<br>Timer2/3, Timer4/5 Modules<br>Timing Diagrams |     |

|----------------------------------------------------------------|-----|

| 10-Bit Analog-to-Digital Conversion                            |     |

| (ASAM = 0, SSRC<2:0> = 000)                                    | 293 |

| 10-Bit Analog-to-Digital Conversion (ASAM = 1,                 |     |

| SSRC<2:0> = 111, SAMC<4:0> = 00001)                            | 294 |

| EJTAG                                                          | 300 |

| External Clock                                                 | 269 |

| I/O Characteristics                                            | 272 |

| I2Cx Bus Data (Master Mode)                                    | 283 |

| I2Cx Bus Data (Slave Mode)                                     | 286 |

| I2Cx Bus Start/Stop Bits (Master Mode)                         | 283 |

| I2Cx Bus Start/Stop Bits (Slave Mode)                          | 286 |

| Input Capture (CAPx)                                           | 276 |

| OCx/PWM                                                        |     |

| Output Compare (OCx)                                           | 277 |

| Parallel Master Port Read                                      | 296 |

| Parallel Master Port Write                                     | 297 |

|                                                                |     |

| Parallel Slave Port                      | . 295 |

|------------------------------------------|-------|

| SPIx Master Mode (CKE = 0)               | . 278 |

| SPIx Master Mode (CKE = 1)               | . 279 |

| SPIx Slave Mode (CKE = 0)                | . 280 |

| SPIx Slave Mode (CKE = 1)                | . 281 |

| Timer1, 2, 3, 4, 5 External Clock        | . 275 |

| UART Reception                           | . 187 |

| UART Transmission (8-bit or 9-bit Data)  | . 187 |

| Timing Requirements                      |       |

| CLKO and I/O                             | . 272 |

| Timing Specifications                    |       |

| I2Cx Bus Data Requirements (Master Mode) |       |

| I2Cx Bus Data Requirements (Slave Mode)  |       |

| Input Capture Requirements               |       |

| Output Compare Requirements              |       |

| Simple OCx/PWM Mode Requirements         |       |

| SPIx Master Mode (CKE = 0) Requirements  |       |

| SPIx Master Mode (CKE = 1) Requirements  |       |

| SPIx Slave Mode (CKE = 1) Requirements   |       |

| SPIx Slave Mode Requirements (CKE = 0)   | . 280 |

| Timing Specifications (50 MHz)           |       |

| SPIx Master Mode (CKE = 0) Requirements  |       |

| SPIx Master Mode (CKE = 1) Requirements  |       |

| SPIx Slave Mode (CKE = 1) Requirements   |       |

| SPIx Slave Mode Requirements (CKE = 0)   | . 305 |

| U                                        |       |

| LIADT                                    | 101   |

| UART                |     |

|---------------------|-----|

| USB On-The-Go (OTG) | 103 |

| V                   |     |

| VCAP nin            | 250 |

| VCAP pin                    |     |

|-----------------------------|-----|

| Voltage Regulator (On-Chip) | 250 |

|                             |     |

| W                           |     |

| M/M/M/ Addross              | 2/1 |

| WWW Address          | . 341 |

|----------------------|-------|

| WWW, On-Line Support | 16    |