Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | ·                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 10x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f256b-i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                     |      |                                    |                  | Rem             | appab                                  | le Pe | riphe                | erals                              |                    |                     |                  |     | (                                        |      | ls)                          |      |          |      |                                 |

|---------------------|------|------------------------------------|------------------|-----------------|----------------------------------------|-------|----------------------|------------------------------------|--------------------|---------------------|------------------|-----|------------------------------------------|------|------------------------------|------|----------|------|---------------------------------|

| Device              | Pins | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins | Timers <sup>(2)</sup> /Capture/Compare | UART  | SPI/I <sup>2</sup> S | External Interrupts <sup>(3)</sup> | Analog Comparators | USB On-The-Go (OTG) | I <sup>2</sup> C | dMq | DMA Channels<br>(Programmable/Dedicated) | CTMU | 10-bit 1 Msps ADC (Channels) | RTCC | I/O Pins | JTAG | Packages                        |

| PIC32MX210F016B     | 28   | 16+3                               | 4                | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX210F016C     | 36   | 16+3                               | 4                | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 25       | Y    | VTLA                            |

| PIC32MX210F016D     | 44   | 16+3                               | 4                | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX220F032B     | 28   | 32+3                               | 8                | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX220F032C     | 36   | 32+3                               | 8                | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA                            |

| PIC32MX220F032D     | 44   | 32+3                               | 8                | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX230F064B     | 28   | 64+3                               | 16               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX230F064C     | 36   | 64+3                               | 16               | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA                            |

| PIC32MX230F064D     | 44   | 64+3                               | 16               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX250F128B     | 28   | 128+3                              | 32               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX250F128C     | 36   | 128+3                              | 32               | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA<br>VTLA,                   |

| PIC32MX250F128D     | 44   | 128+3                              | 32               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | TQFP,<br>QFN                    |

| PIC32MX230F256B     | 28   | 256+3                              | 16               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX230F256D     | 44   | 256+3                              | 16               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX270F256B     | 28   | 256+3                              | 64               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX270F256D     | 44   | 256+3                              | 64               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX270F256DB(4) | 44   | 256+3                              | 64               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

### TABLE 2: PIC32MX2XX 28/36/44-PIN USB FAMILY FEATURES

Note 1: This device features 3 KB of boot Flash memory.

**2:** Four out of five timers are remappable.

3: Four out of five external interrupts are remappable.

4: This PIC32 device is targeted to specific audio software packages that are tracked for licensing royalty purposes. All peripherals and electrical characteristics are identical to their corresponding base part numbers.

NOTES:

# 8.1 Oscillator Control Regiters

| TABLE 8-1: OSCILLATOR CONTROL REGISTER MAP |                                 |           |       |       |                                                |            |           |       |           |      |         |                      |          |       |        |                       |           |       |                     |

|--------------------------------------------|---------------------------------|-----------|-------|-------|------------------------------------------------|------------|-----------|-------|-----------|------|---------|----------------------|----------|-------|--------|-----------------------|-----------|-------|---------------------|

| ess                                        |                                 | 0         |       |       |                                                |            |           |       |           |      | Bits    |                      |          |       |        |                       |           |       | ú                   |

| Virtual Address<br>(BF80_#)                | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13                                          | 28/12      | 27/11     | 26/10 | 25/9      | 24/8 | 23/7    | 22/6                 | 21/5     | 20/4  | 19/3   | 18/2                  | 17/1      | 16/0  | All Reset           |

| F000                                       | OSCCON                          | 31:16     | —     | _     | Р                                              | LLODIV<2:0 | )>        | F     | RCDIV<2:0 | )>   | —       | SOSCRDY              | PBDIVRDY | PBDI\ | /<1:0> | PL                    | LMULT<2:0 | >     | x1xx <sup>(2)</sup> |

| FUUU                                       | 030001                          | 15:0      | —     |       | COSC<2:0                                       | V          | Ι         |       | NOSC<2:0  | >    | CLKLOCK | ULOCK <sup>(3)</sup> | SLOCK    | SLPEN | CF     | UFRCEN <sup>(3)</sup> | SOSCEN    | OSWEN | xxxx(2)             |

| F010                                       | OSCTUN                          | 31:16     | _     | _     |                                                | _          | _         |       |           | _    | _       | _                    | _        | _     |        | _                     | —         | _     | 0000                |

| 1010                                       | 030101                          | 15:0      | _     | _     |                                                | _          | _         |       |           | _    | _       | _                    |          |       | TUN    | l<5:0>                |           |       | 0000                |

| 5000                                       |                                 | 31:16     | _     |       |                                                |            |           |       |           |      | RODIV<1 | 4:0>                 |          |       |        |                       |           |       | 0000                |

| F020                                       | REFOCON                         | 15:0      | ON    |       | - SIDL OE RSLP - DIVSWEN ACTIVE ROSEL<3:0> 000 |            |           |       |           |      |         |                      |          |       | 0000   |                       |           |       |                     |

| F000                                       | DEFOTDIM                        | 31:16     |       |       |                                                | R          | OTRIM<8:0 | )>    |           |      |         | _                    | _        | _     | _      | _                     | _         | _     | 0000                |

| F030                                       | REFOTRIM                        | 15:0      | _     | _     |                                                | _          | _         |       |           | -    | _       | _                    | _        | _     |        | _                     | —         | _     | 0000                |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

3: This bit is only available on PIC32MX2XX devices.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 24.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 31:24        |                     | —                 | —                 | _                 | _                 | _                 |                  | _                     |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 23:16        | —                   | —                 | —                 | -                 | _                 | —                 | —                | —                     |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0                 |

| 15:8         | CHBUSY              | —                 | —                 | _                 | _                 | _                 | _                | CHCHNS <sup>(1)</sup> |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R-0               | R/W-0            | R/W-0                 |

| 7:0          | CHEN <sup>(2)</sup> | CHAED             | CHCHN             | CHAEN             |                   | CHEDET            | CHPF             | RI<1:0>               |

### REGISTER 9-7: DCHxCON: DMA CHANNEL 'x' CONTROL REGISTER

### Legend:

| 0                 |                  |                                    |                    |  |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |  |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 CHBUSY: Channel Busy bit

- 1 = Channel is active or has been enabled

- 0 = Channel is inactive or has been disabled

- bit 14-9 Unimplemented: Read as '0'

- bit 8 CHCHNS: Chain Channel Selection bit<sup>(1)</sup>

- 1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

- 0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

### bit 7 CHEN: Channel Enable bit<sup>(2)</sup>

- 1 = Channel is enabled

- 0 = Channel is disabled

### bit 6 CHAED: Channel Allow Events If Disabled bit

- 1 = Channel start/abort events will be registered, even if the channel is disabled

- 0 = Channel start/abort events will be ignored if the channel is disabled

### bit CHCHN: Channel Chain Enable bit

- 1 = Allow channel to be chained

- 0 = Do not allow channel to be chained

- bit 4 CHAEN: Channel Automatic Enable bit

- 1 = Channel is continuously enabled, and not automatically disabled after a block transfer is complete

0 = Channel is disabled on block transfer complete

### bit 3 Unimplemented: Read as '0'

- bit 2 CHEDET: Channel Event Detected bit

- 1 = An event has been detected

- 0 = No events have been detected

- bit 1-0 CHPRI<1:0>: Channel Priority bits

- 11 = Channel has priority 3 (highest)

- 10 = Channel has priority 2

- 01 = Channel has priority 1

- 00 = Channel has priority 0

- Note 1: The chain selection bit takes effect when chaining is enabled (i.e., CHCHN = 1).

- 2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

### REGISTER 10-7: U1IE: USB INTERRUPT ENABLE REGISTER

|              |                   | •                 |                   |                   |                   |                   |                       |                                                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|--------------------------------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0                                 |

| 31:24        | U-0                   | U-0                                              |

| 51.24        | —                 | —                 | —                 | —                 | —                 | —                 | —                     | —                                                |

| 23:16        | U-0                   | U-0                                              |

| 23:10        | -                 | —                 | —                 | —                 | —                 | —                 | —                     | —                                                |

| 15:8         | U-0                   | U-0                                              |

| 15.0         | _                 | —                 | —                 | _                 | —                 | _                 | _                     | —                                                |

|              | R/W-0                 | R/W-0                                            |

| 7:0          | STALLIE           | ATTACHIE          | RESUMEIE          | IDLEIE            | TRNIE             | SOFIE             | UERRIE <sup>(1)</sup> | URSTIE <sup>(2)</sup><br>DETACHIE <sup>(3)</sup> |

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 | STALLIE: STALL Handshake Interrupt Enable bit |

|-------|-----------------------------------------------|

|       |                                               |

- 1 = STALL interrupt is enabled

- 0 = STALL interrupt is disabled

- bit 6 ATTACHIE: ATTACH Interrupt Enable bit

- 1 = ATTACH interrupt is enabled 0 = ATTACH interrupt is disabled

- bit 5 **RESUMEIE:** RESUME Interrupt Enable bit

- 1 = RESUME interrupt is enabled

- 0 = RESUME interrupt is disabled

- bit 4 IDLEIE: Idle Detect Interrupt Enable bit

- 1 = Idle interrupt is enabled

- 0 = Idle interrupt is disabled

- bit 3 TRNIE: Token Processing Complete Interrupt Enable bit

- 1 = TRNIF interrupt is enabled

- 0 = TRNIF interrupt is disabled

- bit 2 SOFIE: SOF Token Interrupt Enable bit

- 1 = SOFIF interrupt is enabled

- 0 = SOFIF interrupt is disabled

- bit 1 UERRIE: USB Error Interrupt Enable bit<sup>(1)</sup>

- 1 = USB Error interrupt is enabled

- 0 = USB Error interrupt is disabled

- bit 0 URSTIE: USB Reset Interrupt Enable bit<sup>(2)</sup>

- 1 = URSTIF interrupt is enabled

- 0 = URSTIF interrupt is disabled

### DETACHIE: USB Detach Interrupt Enable bit<sup>(3)</sup>

- 1 = DATTCHIF interrupt is enabled

- 0 = DATTCHIF interrupt is disabled

**Note 1:** For an interrupt to propagate USBIF, the UERRIE (U1IE<1>) bit must be set.

- 2: Device mode.

- 3: Host mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        |                   | _                 |                   | _                 | —                 |                   | -                | -                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        |                   | _                 |                   | _                 | —                 |                   | -                | -                |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.0         |                   | _                 |                   | _                 | —                 |                   | -                | -                |  |  |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | LSPD              | RETRYDIS          |                   | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |  |  |

### REGISTER 10-21: U1EP0-U1EP15: USB ENDPOINT CONTROL REGISTER

### Legend:

| ======================================= |                  |                                    |                    |  |  |  |  |

|-----------------------------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit                        | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR                       | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 LSPD: Low-Speed Direct Connection Enable bit (Host mode and U1EP0 only)

- 1 = Direct connection to a Low-Speed device enabled

- 0 = Direct connection to a Low-Speed device disabled; hub required with PRE\_PID

- bit 6 **RETRYDIS:** Retry Disable bit (Host mode and U1EP0 only)

- 1 = Retry NAKed transactions disabled

- 0 = Retry NAKed transactions enabled; retry done in hardware

### bit 5 Unimplemented: Read as '0'

bit 4 **EPCONDIS:** Bidirectional Endpoint Control bit

If EPTXEN = 1 and EPRXEN = 1:

1 = Disable Endpoint n from Control transfers; only TX and RX transfers allowed

0 = Enable Endpoint n for Control (SETUP) transfers; TX and RX transfers also allowed Otherwise, this bit is ignored.

- bit 3 **EPRXEN:** Endpoint Receive Enable bit

- 1 = Endpoint n receive is enabled

- 0 = Endpoint n receive is disabled

- bit 2 EPTXEN: Endpoint Transmit Enable bit

- 1 = Endpoint n transmit is enabled

- 0 = Endpoint n transmit is disabled

- bit 1 EPSTALL: Endpoint Stall Status bit

- 1 = Endpoint n was stalled

- 0 = Endpoint n was not stalled

- bit 0 EPHSHK: Endpoint Handshake Enable bit

- 1 = Endpoint Handshake is enabled

- 0 = Endpoint Handshake is disabled (typically used for isochronous endpoints)

## TABLE 11-7: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| ss                          |                      |           |       | Bits  |       |       |       |       |      |      |      |      |      |      |      |      |       |      |            |

|-----------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|-------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0 | All Resets |

| 5000                        | RPC8R <sup>(1)</sup> | 31:16     | _     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | _    | _    | —    | —     | —    | 0000       |

| FB8C                        | RPCoR                | 15:0      | —     | —     | —     | —     | —     | _     | —    | —    | _    | —    | —    | —    |      | RPC8 | <3:0> |      | 0000       |

| 5000                        | RPC9R <sup>(3)</sup> | 31:16     | —     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | _    | _    | —    | —     |      | 0000       |

| FB90                        | RPC9R                | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    |      | RPC  | <3:0> |      | 0000       |

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1:

2:

This register is only available on 44-pin devices. This register is only available on PIC32MX1XX devices. This register is only available on 36-pin and 44-pin devices. 3:

NOTES:

| REGISTE | R 18-1:           | I2CxCON: I <sup>2</sup> C CONTROL REGISTER (CONTINUED)                                                                                                                |

|---------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7   | GCEN: Ge          | eneral Call Enable bit (when operating as I <sup>2</sup> C slave)                                                                                                     |

|         | (module           | interrupt when a general call address is received in the I2CxRSR<br>e is enabled for reception)                                                                       |

|         |                   | al call address is disabled                                                                                                                                           |

| bit 6   | STREN: S          | CLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)                                                                                               |

|         |                   | njunction with SCLREL bit.                                                                                                                                            |

|         |                   | e software or receive clock stretching                                                                                                                                |

| L:1 F   |                   | e software or receive clock stretching                                                                                                                                |

| bit 5   |                   | cknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive) is transmitted when the software initiates an Acknowledge sequence. |

|         |                   | a NACK during an Acknowledge sequence                                                                                                                                 |

|         |                   | an ACK during an Acknowledge sequence                                                                                                                                 |

| bit 4   | ACKEN: A receive) | cknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master                                                                   |

|         | Hardwa            | Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit.<br>are clear at end of master Acknowledge sequence.<br>wledge sequence not in progress        |

| bit 3   | RCEN: Re          | ceive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                          |

|         |                   | es Receive mode for I <sup>2</sup> C. Hardware clear at end of eighth bit of master receive data byte.<br>The sequence not in progress                                |

| bit 2   | PEN: Stop         | Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                      |

|         |                   | Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence. ondition not in progress                                                         |

| bit 1   | RSEN: Re          | peated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                         |

|         |                   | Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of Repeated Start sequence.                                                                     |

|         | 0 = Repeat        | ted Start condition not in progress                                                                                                                                   |

| bit 0   |                   | Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                      |

|         |                   | Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence. ondition not in progress                                                       |

|         |                   |                                                                                                                                                                       |

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

# 21.1 RTCC Control Registers

### TABLE 21-1: RTCC REGISTER MAP

| ess                         |                                 | ē         |        |       |          |          |       |       |                   |      | Bits                       |                       |           |         |         |         |            |       | ŝ          |

|-----------------------------|---------------------------------|-----------|--------|-------|----------|----------|-------|-------|-------------------|------|----------------------------|-----------------------|-----------|---------|---------|---------|------------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15  | 30/14 | 29/13    | 28/12    | 27/11 | 26/10 | 25/9              | 24/8 | 23/7                       | 22/6                  | 21/5      | 20/4    | 19/3    | 18/2    | 17/1       | 16/0  | All Resets |

| 0200                        | RTCCON                          | 31:16     | —      | _     | —        | —        | —     |       |                   |      | CAL<9:0>                   |                       |           |         |         |         | 0000       |       |            |

| 0200                        | RICCON                          | 15:0      | ON     | _     | SIDL     | —        | —     | —     |                   | —    | RTSECSEL                   | RTCCLKON              | —         |         | RTCWREN | RTCSYNC | HALFSEC    | RTCOE | 0000       |

| 0210                        | RTCALRM                         | 31:16     | —      |       |          | —        | —     | _     |                   | —    | —                          | _                     | —         |         | _       | —       | _          | —     | 0000       |

| 0210                        | RICALIN                         | 15:0      | ALRMEN | CHIME | PIV      | ALRMSYNC |       | AMASI | <b>&lt;</b> <3:0> |      |                            | ARPT<7:0> 0           |           |         |         |         | 0000       |       |            |

| 0220                        | RTCTIME                         | 31:16     | —      | _     | HR1      | 0<1:0>   |       | HR01  | <3:0>             |      | —                          | MIN10<2:0> MIN01<3:0> |           |         |         | xxxx    |            |       |            |

| 0220                        |                                 | 15:0      | —      |       | SEC10<2: | 0>       |       | SEC07 | 1<3:0>            |      | —                          | —                     | —         | _       | _       | _       | —          | —     | xx00       |

| 0230                        | RTCDATE                         | 31:16     |        | YEAR  | 10<3:0>  |          |       | YEAR0 | 1<3:0>            |      | — — — MONTH10 MONTH01<3:0> |                       |           |         | xxxx    |         |            |       |            |

| 0230                        | RICDAIL                         | 15:0      | _      | _     | DAY      | 10<1:0>  |       | DAY01 | 1<3:0>            |      | —                          | —                     | —         |         | _       | W       | /DAY01<2:0 | >     | xx00       |

| 0240                        | ALRMTIME                        | 31:16     | _      |       | HR1      | 0<1:0>   |       | HR01  | <3:0>             |      | _                          | М                     | IN10<2:0> |         |         | MIN01   | <3:0>      |       | xxxx       |

| 0240                        |                                 | 15:0      | —      |       | SEC10<2: | 0>       |       | SEC02 | 1<3:0>            |      | —                          | _                     | —         |         | —       | —       | _          | —     | xx00       |

| 0250                        | ALRMDATE                        | 31:16     | _      | _     | _        | _        | _     | _     |                   | _    | —                          | _                     | —         | MONTH10 |         | MONTH   | 01<3:0>    |       | 00xx       |

| 0250                        | ALNIUATE                        | 15:0      |        | DAY1  | 0<3:0>   |          |       | DAY01 | <3:0>             |      | _                          | _                     | _         | -       | _       | W       | /DAY01<2:0 | >     | xx0x       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

### REGISTER 21-2: RTCALRM: RTC ALARM CONTROL REGISTER (CONTINUED)

bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits<sup>(2)</sup> 11111111 = Alarm will trigger 256 times

> 00000000 = Alarm will trigger one time The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1.

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

Note: This register is reset only on a Power-on Reset (POR).

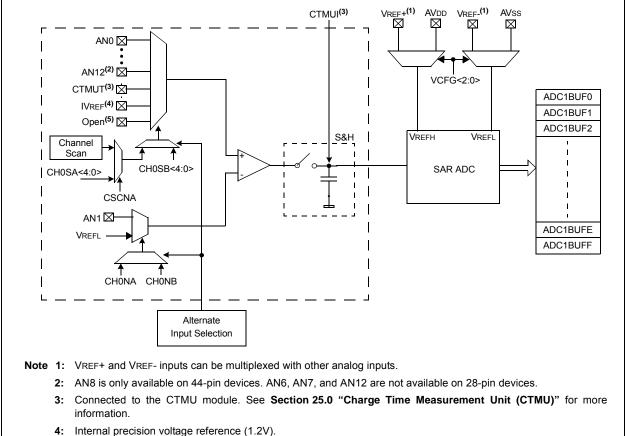

#### 22.0 **10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)**

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- · Up to 1 Msps conversion speed

**FIGURE 22-1:**

- Up to 13 analog input pins

- External voltage reference input pins

- · One unipolar, differential Sample and Hold Amplifier (SHA)

- Automatic Channel Scan mode

- Selectable conversion trigger source

- · 16-word conversion result buffer

- Selectable buffer fill modes

- Eight conversion result format options

- · Operation during Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 22-1. Figure 22-2 illustrates a block diagram of the ADC conversion clock period. The 10-bit ADC has up to 13 analog input pins, designated AN0-AN12. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

### 5: This selection is only used with CTMU capacitive and time measurement.

ADC1 MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.04        | R/P               | R/P               | R/P               | R/P               | r-1               | r-1               | r-1              | r-1              |  |

| 31:24        | FVBUSONIO         | FUSBIDIO          | IOL1WAY           | PMDL1WAY          | _                 |                   | _                | _                |  |

| 23:16        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |  |

| 23.10        | —                 | —                 | —                 | —                 | _                 | —                 | _                | —                |  |

| 15.0         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 15:8         | USERID<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 7:0          |                   |                   |                   | USERID<           | 7:0>              |                   |                  |                  |  |

### REGISTER 27-4: DEVCFG3: DEVICE CONFIGURATION WORD 3

| Legend:           | r = Reserved bit | P = Programmable bit  |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 31 FVBUSONIO: USB VBUSON Selection bit

- 1 = VBUSON pin is controlled by the USB module 0 = VBUSON pin is controlled by the port function

- bit 30 **FUSBIDIO:** USB USBID Selection bit 1 = USBID pin is controlled by the USB module 0 = USBID pin is controlled by the port function

- bit 29 IOL1WAY: Peripheral Pin Select Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 28 PMDI1WAY: Peripheral Module Disable Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 27-16 Reserved: Write '1'

- bit 15-0 USERID<15:0>: User ID bits

This is a 16-bit value that is user-defined and is readable via ICSP™ and JTAG.

| DC CHARACTERISTICS |        |                                      |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |        |                                               |  |  |

|--------------------|--------|--------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|-----------------------------------------------|--|--|

| Param.<br>No.      | Symbol | Characteristics                      | Min.   | Typical <sup>(1)</sup>                                                                                                                                                                                                                                                              | Max. | Units  | Conditions                                    |  |  |

|                    |        | Program Flash Memory <sup>(3)</sup>  |        |                                                                                                                                                                                                                                                                                     |      |        |                                               |  |  |

| D130               | Eр     | Cell Endurance                       | 20,000 | —                                                                                                                                                                                                                                                                                   | _    | E/W    | —                                             |  |  |

| D131               | Vpr    | VDD for Read                         | 2.3    | —                                                                                                                                                                                                                                                                                   | 3.6  | V      | —                                             |  |  |

| D132               | VPEW   | VDD for Erase or Write               | 2.3    | —                                                                                                                                                                                                                                                                                   | 3.6  | V      | —                                             |  |  |

| D134               | Tretd  | Characteristic Retention             | 20     | —                                                                                                                                                                                                                                                                                   | _    | Year   | Provided no other specifications are violated |  |  |

| D135               | IDDP   | Supply Current during<br>Programming | _      | 10                                                                                                                                                                                                                                                                                  | _    | mA     | —                                             |  |  |

|                    | Tww    | Word Write Cycle Time                | —      | 411                                                                                                                                                                                                                                                                                 | _    | es     | See Note 4                                    |  |  |

| D136               | Trw    | Row Write Cycle Time                 | —      | 6675                                                                                                                                                                                                                                                                                | _    | Cycles | See Note 2,4                                  |  |  |

| D137               | TPE    | Page Erase Cycle Time                | —      | 20011                                                                                                                                                                                                                                                                               | _    |        | See Note 4                                    |  |  |

|                    | TCE    | Chip Erase Cycle Time                | —      | 80180                                                                                                                                                                                                                                                                               | _    | FRC    | See Note 4                                    |  |  |

### TABLE 30-12: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: The minimum SYSCLK for row programming is 4 MHz. Care should be taken to minimize bus activities during row programming, such as suspending any memory-to-memory DMA operations. If heavy bus loads are expected, selecting Bus Matrix Arbitration mode 2 (rotating priority) may be necessary. The default Arbitration mode is mode 1 (CPU has lowest priority).

**3:** Refer to the *"PIC32 Flash Programming Specification"* (DS60001145) for operating conditions during programming and erase cycles.

4: This parameter depends on FRC accuracy (See Table 30-19) and FRC tuning values (See Register 8-2).

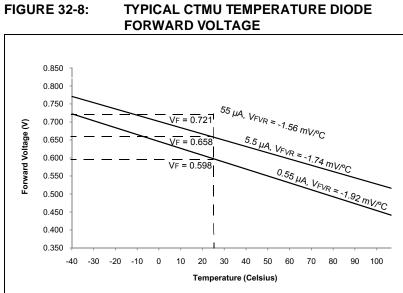

TYPICAL FRC FREQUENCY @ VDD = 3.3V

**FIGURE 32-6:**

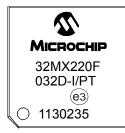

# 33.1 Package Marking Information (Continued)

### 44-Lead VTLA

### 44-Lead QFN

### 44-Lead TQFP

Example

# Example

# Example

# Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (@3) |

|--------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                                          | can be found on the outer packaging for this package.                                                                                                                                                                                                                                                               |

| Note:  |                                          | <i>l</i> icrochip part number cannot be marked on one line, it is carried over to the next limiting the number of available characters for customer-specific information.                                                                                                                                           |

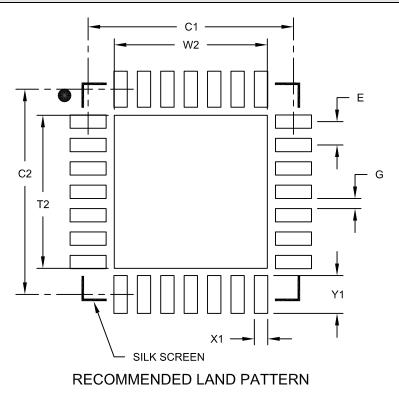

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS      |      |          |      |

|----------------------------|------------------|------|----------|------|

| Dimensi                    | Dimension Limits |      |          |      |

| Contact Pitch              | Е                |      | 0.65 BSC |      |

| Optional Center Pad Width  | W2               |      |          | 4.25 |

| Optional Center Pad Length | T2               |      |          | 4.25 |

| Contact Pad Spacing        | C1               |      | 5.70     |      |

| Contact Pad Spacing        | C2               |      | 5.70     |      |

| Contact Pad Width (X28)    | X1               |      |          | 0.37 |

| Contact Pad Length (X28)   | Y1               |      |          | 1.00 |

| Distance Between Pads      | G                | 0.20 |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A

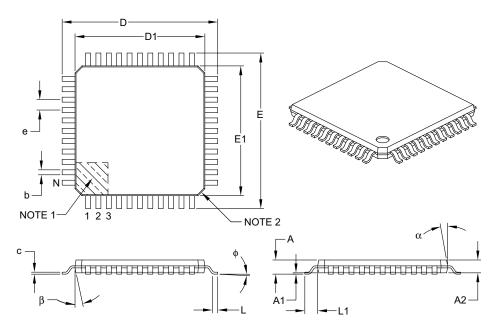

# 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units        |      | MILLIMETERS |      |  |

|--------------------------|--------------|------|-------------|------|--|

| Dime                     | nsion Limits | MIN  | NOM         | MAX  |  |

| Number of Leads          | N            | 44   |             |      |  |

| Lead Pitch               | е            |      | 0.80 BSC    |      |  |

| Overall Height           | А            | _    | -           | 1.20 |  |

| Molded Package Thickness | A2           | 0.95 | 1.00        | 1.05 |  |

| Standoff                 | A1           | 0.05 | -           | 0.15 |  |

| Foot Length              | L            | 0.45 | 0.60        | 0.75 |  |

| Footprint                | L1           |      | 1.00 REF    |      |  |

| Foot Angle               | φ            | 0°   | 3.5°        | 7°   |  |

| Overall Width            | E            |      | 12.00 BSC   |      |  |

| Overall Length           | D            |      | 12.00 BSC   |      |  |

| Molded Package Width     | E1           |      | 10.00 BSC   |      |  |

| Molded Package Length    | D1           |      | 10.00 BSC   |      |  |

| Lead Thickness           | С            | 0.09 | -           | 0.20 |  |

| Lead Width               | b            | 0.30 | 0.37        | 0.45 |  |

| Mold Draft Angle Top     | α            | 11°  | 12°         | 13°  |  |

| Mold Draft Angle Bottom  | β            | 11°  | 12°         | 13°  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

# **Revision F (February 2014)**

This revision includes the addition of the following devices:

In addition, this revision includes the following major changes as described in Table A-5, as well as minor updates to text and formatting, which were incorporated throughout the document.

- PIC32MX170F256B PIC32MX270F256B

- PIC32MX170F256D

PIC32MX270F256D

### TABLE A-5: MAJOR SECTION UPDATES

| Section                                                                                                                           | Update Description                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32-bit Microcontrollers (up to 256<br>KB Flash and 64 KB SRAM) with<br>Audio and Graphics Interfaces,<br>USB, and Advanced Analog | Added new devices to the family features (see Table 1 and Table 2).<br>Updated pin diagrams to include new devices (see " <b>Pin Diagrams</b> ").    |

| 1.0 "Device Overview"                                                                                                             | Added Note 3 reference to the following pin names: VBUS, VUSB3V3, VBUSON, D+, D-, and USBID.                                                         |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"                                                                          | Replaced Figure 2-1: Recommended Minimum Connection.<br>Updated Figure 2-2: MCLR Pin Connections.<br>Added <b>2.9 "Sosc Design Recommendation"</b> . |

| 4.0 "Memory Organization"                                                                                                         | Added memory tables for devices with 64 KB RAM (see Table 4-4 through Table 4-5).                                                                    |

|                                                                                                                                   | Changed the Virtual Addresses for all registers and updated the PWP bits in the DEVCFG: Device Configuration Word Summary (see Table 4-17).          |

|                                                                                                                                   | Updated the ODCA, ODCB, and ODCC port registers (see Table 4-19, Table 4-20, and Table 4-21).                                                        |

|                                                                                                                                   | The RTCTIME, RTCDATE, ALRMTIME, and ALRMDATE registers were updated (see Table 4-25).                                                                |

|                                                                                                                                   | Added Data Ram Size value for 64 KB RAM devices (see Register 4-5).                                                                                  |

|                                                                                                                                   | Added Program Flash Size value for 256 KB Flash devices (see Register 4-5).                                                                          |

| 12.0 "Timer1"                                                                                                                     | The Timer1 block diagram was updated to include the 16-bit data bus (see Figure 12-1).                                                               |

| 13.0 "Timer2/3, Timer4/5"                                                                                                         | The Timer2-Timer5 block diagram (16-bit) was updated to include the 16-bit data bus (see Figure 13-1).                                               |

|                                                                                                                                   | The Timer2/3, Timer4/5 block diagram (32-bit) was updated to include the 32-<br>bit data bus (see Figure 13-1).                                      |

| 19.0 "Parallel Master Port (PMP)"                                                                                                 | The CSF<1:0> bit value definitions for '00' and '01' were updated (see Register 19-1).                                                               |

|                                                                                                                                   | Bit 14 in the Parallel Port Address register (PMADDR) was updated (see Register 19-3).                                                               |

| 20.0 "Real-Time Clock and                                                                                                         | The following registers were updated:                                                                                                                |

| Calendar (RTCC)"                                                                                                                  | RTCTIME (see Register 20-3)                                                                                                                          |

|                                                                                                                                   | RTCDATE (see Register 20-4)                                                                                                                          |

|                                                                                                                                   | ALRMTIME (see Register 20-5)                                                                                                                         |

|                                                                                                                                   | ALRMDATE (see Register 20-6)                                                                                                                         |

| 26.0 "Special Features"                                                                                                           | Updated the PWP bits (see Register 26-1).                                                                                                            |

| 29.0 "Electrical Characteristics"                                                                                                 | Added parameters DO50 and DO50a to the Capacitive Loading Requirements on Output Pins (see Table 29-14).                                             |

|                                                                                                                                   | Added Note 5 to the IDD DC Characteristics (see Table 29-5).                                                                                         |

|                                                                                                                                   | Added Note 4 to the IIDLE DC Characteristics (see Table 29-6).                                                                                       |

|                                                                                                                                   | Added Note 5 to the IPD DC Characteristics (see Table 29-7).                                                                                         |

|                                                                                                                                   | Updated the conditions for parameters USB321 (VOL) and USB322 (VOH) in the OTG Electrical Specifications (see Table 29-38).                          |

| Product Identification System                                                                                                     | Added 40 MHz speed information.                                                                                                                      |

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| Program Memory Size<br>Pin Count<br>Software Targeting<br>Tape and Reel Flag (if<br>Speed (if applicable)<br>Temperature Range<br>Package | 32-bit RISC MCU with M4K <sup>®</sup> core,<br>32 KB program memory, 44-pin,                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                           | Flash Memory Family                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Architecture                                                                                                                              | $MX = M4K^{\odot} MCU \text{ core}$                                                                                                                                                                                                                                                                                                                                                                                                    |

| Product Groups                                                                                                                            | 1XX = General purpose microcontroller family<br>2XX = General purpose microcontroller family                                                                                                                                                                                                                                                                                                                                           |

| Flash Memory Family                                                                                                                       | F = Flash program memory                                                                                                                                                                                                                                                                                                                                                                                                               |

| Program Memory Size                                                                                                                       | 016 = 16K<br>032 = 32K<br>064 = 64K<br>128 = 128K<br>256 = 256K                                                                                                                                                                                                                                                                                                                                                                        |

| Pin Count                                                                                                                                 | B = 28-pin<br>C = 36-pin<br>D = 44-pin                                                                                                                                                                                                                                                                                                                                                                                                 |

| Software Targeting                                                                                                                        | B = Targeted for Bluetooth <sup>®</sup> Audio Break-in devices                                                                                                                                                                                                                                                                                                                                                                         |

| Speed                                                                                                                                     | <ul> <li>= 40 MHz - () indicates a blank field; package markings for 40 MHz devices do not include the Speed</li> <li>= 50 MHz</li> </ul>                                                                                                                                                                                                                                                                                              |

| Temperature Range                                                                                                                         | I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)<br>V = $-40^{\circ}$ C to $+105^{\circ}$ C (V-temp)                                                                                                                                                                                                                                                                                                                                |

| Package                                                                                                                                   | ML= 28-Lead (6x6 mm) QFN (Plastic Quad Flatpack)ML= 44-Lead (8x8 mm) QFN (Plastic Quad Flatpack)PT= 44-Lead (10x10x1 mm) TQFP (Plastic Thin Quad Flatpack)SO= 28-Lead (7.50 mm) SOIC (Plastic Small Outline)SP= 28-Lead (300 mil) SPDIP (Skinny Plastic Dual In-line)SS= 28-Lead (5.30 mm) SSOP (Plastic Shrink Small Outline)TL= 36-Lead (5x5 mm) VTLA (Very Thin Leadless Array)TL= 44-Lead (6x6 mm) VTLA (Very Thin Leadless Array) |

| Pattern                                                                                                                                   | Three-digit QTP, SQTP, Code or Special Requirements (blank otherwise)<br>ES = Engineering Sample                                                                                                                                                                                                                                                                                                                                       |