Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| D-4-!I-                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Details                    |                                                                                |

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| /oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 10x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| perating Temperature       | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f256b-i-ss |

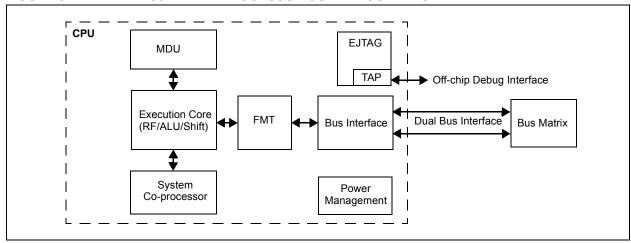

#### 3.0 CPU

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS60001113), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). Resources for the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core are available at: www.imgtec.com.

The MIPS32® M4K® Processor Core is the heart of the PIC32MX1XX/2XX family processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the destinations.

#### 3.1 Features

- · 5-stage pipeline

- · 32-bit address and data paths

- MIPS32 Enhanced Architecture (Release 2)

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- Bit field manipulation instructions

- MIPS16e<sup>®</sup> code compression

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE and RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8 and 16-bit data types

- Simple Fixed Mapping Translation (FMT) mechanism

- · Simple dual bus interface

- Independent 32-bit address and data buses

- Transactions can be aborted to improve interrupt latency

- · Autonomous multiply/divide unit

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (rs) sign extension-dependent)

- Power control

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- · EJTAG debug and instruction trace

- Support for single stepping

- Virtual instruction and data address/value

- Breakpoints

#### FIGURE 3-1: MIPS32® M4K® PROCESSOR CORE BLOCK DIAGRAM

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

TABLE 3-3: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE EXCEPTION TYPES

| Exception | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                               |

| DSS       | EJTAG debug single step.                                                                                                                |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                                |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                            |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                         |

| AdEL      | Fetch address alignment error. Fetch reference to protected address.                                                                    |

| IBE       | Instruction fetch bus error.                                                                                                            |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                                      |

| Sys       | Execution of SYSCALL instruction.                                                                                                       |

| Вр        | Execution of BREAK instruction.                                                                                                         |

| RI        | Execution of a reserved instruction.                                                                                                    |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                           |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled.                                                                     |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                                 |

| Tr        | Execution of a trap (when trap condition is true).                                                                                      |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                           |

| AdEL      | Load address alignment error. Load reference to protected address.                                                                      |

| AdES      | Store address alignment error. Store to protected address.                                                                              |

| DBE       | Load or store bus error.                                                                                                                |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                            |

#### 3.3 Power Management

The MIPS M4K processor core offers many power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or Halting the clocks, which reduces system power consumption during Idle periods.

# 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see **Section 26.0** "Power-Saving Features".

#### 3.4 EJTAG Debug Support

The MIPS M4K processor core provides an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the M4K core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used.

#### REGISTER 4-4: BMXDUPBA: DATA RAM USER PROGRAM BASE ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | -                 | _                 | -                 |                   | _                | _                |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |

| 15:8         |                   |                   |                   | BMXDU             | PBA<15:8>         |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | BMXDU             | PBA<7:0>          |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUPBA<15:10>: DRM User Program Base Address bits

When non-zero, the value selects the relative base address for User mode program space in RAM, BMXDUPBA must be greater than BMXDUDBA.

bit 9-0 BMXDUPBA<9:0>: Read-Only bits

This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| PIC32M | X1XX/2 | XX 28/3 | 6/44-PI | N FAM | LY |  |

|--------|--------|---------|---------|-------|----|--|

| NOTES: |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

|        |        |         |         |       |    |  |

### 7.1 Interrupt Control Registers

#### TABLE 7-2: INTERRUPT REGISTER MAP

| ess                         |                                 | •             |                 |                 |                 |                   |                   |                    |                   | Bits              |                 |                    |                   |                         |                                  |          |                  |                 |               |        |      |

|-----------------------------|---------------------------------|---------------|-----------------|-----------------|-----------------|-------------------|-------------------|--------------------|-------------------|-------------------|-----------------|--------------------|-------------------|-------------------------|----------------------------------|----------|------------------|-----------------|---------------|--------|------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15           | 30/14           | 29/13           | 28/12             | 27/11             | 26/10              | 25/9              | 24/8              | 23/7            | 22/6               | 21/5              | 20/4                    | 19/3                             | 18/2     | 17/1             | 16/0            | All<br>Resets |        |      |

| 1000                        | INTCON                          | 31:16         | _               | _               | _               | _                 | _                 | _                  |                   | _                 | _               | _                  | _                 | _                       |                                  | _        | _                | _               | 0000          |        |      |

|                             |                                 | 15:0<br>31:16 | _               | _               | _               | MVEC              |                   |                    | TPC<2:0>          | _                 |                 | _                  | _                 | INT4EP                  | INT3EP                           | INT2EP   | INT1EP           | INT0EP          | 0000          |        |      |

| 1010                        | INTSTAT <sup>(3)</sup>          | 15:0          |                 |                 | _               | _                 |                   |                    | SRIPL<2:0>        | _                 |                 | _                  | _                 | _                       | VEC<5:0                          |          | _                | _               | 0000          |        |      |

| 1020                        | IPTMR                           | 31:16<br>15:0 |                 |                 |                 |                   |                   |                    | OINI LAZ.UP       | IPTMR<3           | 1:0>            |                    |                   |                         | VEO 10.0                         | ,,,      |                  |                 | 0000          |        |      |

| 4000                        | 1500                            | 31:16         | FCEIF           | RTCCIF          | FSCMIF          | AD1IF             | OC5IF             | IC5IF              | IC5EIF            | T5IF              | INT4IF          | OC4IF              | IC4IF             | IC4EIF                  | T4IF                             | INT3IF   | OC3IF            | IC3IF           | 0000          |        |      |

| 1030                        | IFS0                            | 15:0          | IC3EIF          | T3IF            | INT2IF          | OC2IF             | IC2IF             | IC2EIF             | T2IF              | INT1IF            | OC1IF           | IC1IF              | IC1EIF            | T1IF                    | INT0IF                           | CS1IF    | CS0IF            | CTIF            | 0000          |        |      |

| 4040                        | IEO4                            | 31:16         | DMA3IF          | DMA2IF          | DMA1IF          | DMA0IF            | CTMUIF            | I2C2MIF            | I2C2SIF           | I2C2BIF           | U2TXIF          | U2RXIF             | U2EIF             | SPI2TXIF                | SPI2RXIF                         | SPI2EIF  | PMPEIF           | PMPIF           | 0000          |        |      |

| 1040                        | IFS1                            | 15:0          | CNCIF           | CNBIF           | CNAIF           | I2C1MIF           | I2C1SIF           | I2C1BIF            | U1TXIF            | U1RXIF            | U1EIF           | SPI1TXIF           | SPI1RXIF          | SPI1EIF                 | USBIF(2)                         | CMP3IF   | CMP2IF           | CMP1IF          | 0000          |        |      |

| 1060                        | IEC0                            | 31:16         | FCEIE           | RTCCIE          | FSCMIE          | AD1IE             | OC5IE             | IC5IE              | IC5EIE            | T5IE              | INT4IE          | OC4IE              | IC4IE             | IC4EIE                  | T4IE                             | INT3IE   | OC3IE            | IC3IE           | 0000          |        |      |

|                             |                                 | 15:0          | IC3EIE          | T3IE            | INT2IE          | OC2IE             | IC2IE             | IC2EIE             | T2IE              | INT1IE            | OC1IE           | IC1IE              | IC1EIE            | T1IE                    | INT0IE                           | CS1IE    | CS0IE            | CTIE            | 0000          |        |      |

| 1070                        | IEC1                            | 31:16<br>15:0 | DMA3IE<br>CNCIE | DMA2IE<br>CNBIE | DMA1IE<br>CNAIE | DMA0IE<br>I2C1MIE | CTMUIE<br>I2C1SIE | I2C2MIE<br>I2C1BIE | I2C2SIE<br>U1TXIE | I2C2BIE<br>U1RXIE | U2TXIE<br>U1EIE | U2RXIE<br>SPI1TXIE | U2EIE<br>SPI1RXIE | SPI2TXIE<br>SPI1EIE     | SPI2RXIE<br>USBIE <sup>(2)</sup> |          | PMPEIE<br>CMP2IE | PMPIE<br>CMP1IE | 0000          |        |      |

|                             |                                 | 31:16         | CNCIE           | CINBIE          | CNAIE           |                   | INT0IP<2:0>       | IZCIBIE            | INTOIS            |                   | UTEIE           | SPITTALE           | SPITRALE          |                         |                                  | CIVIPSIE | CS1IS            | l               | 1             |        |      |

| 1090                        | IPC0                            | 15:0          | _               |                 |                 |                   | CS0IP<2:0>        |                    | CSOIS             | -                 |                 | _                  | _                 | CS1IP<2:0><br>CTIP<2:0> |                                  |          |                  | <1:0>           | 0000          |        |      |

|                             |                                 | 31:16         |                 |                 |                 |                   | INT1IP<2:0>       |                    | INT1IS            |                   |                 |                    | _                 | OC1IP<2:0>              |                                  |          | OC118            |                 | 0000          |        |      |

| 10A0                        | IPC1                            | 15:0          |                 | _               | _               |                   | IC1IP<2:0>        |                    | IC1IS             | -                 |                 | _                  | _                 |                         | T1IP<2:0>                        |          | T1IS-            |                 | 0000          |        |      |

|                             |                                 | 31:16         | _               | _               | _               |                   | INT2IP<2:0>       |                    | INT2IS            | i<1·0>            |                 | _                  | _                 | C                       | C2IP<2:0>                        |          | OC2IS            | S<1:0>          | 0000          |        |      |

| 10B0                        | IPC2                            | 15:0          | _               | _               | _               |                   | IC2IP<2:0>        |                    | IC2IS             | -                 |                 | _                  | _                 |                         | T2IP<2:0>                        |          | T2IS-            |                 | 0000          |        |      |

|                             |                                 | 31:16         | _               | _               | _               |                   | INT3IP<2:0>       |                    | INT3IS            | <1:0>             | _               | _                  | _                 | С                       | C3IP<2:0>                        |          | OC3IS            | S<1:0>          | 0000          |        |      |

| 10C0                        | IPC3                            | 15:0          |                 | _               | _               |                   | IC3IP<2:0>        |                    | IC3IS•            | <1:0>             |                 | _                  | _                 | -                       | T3IP<2:0>                        |          | T3IS-            | <1:0>           | 0000          |        |      |

| 1000                        | IDO (                           | 31:16         | _               | _               | _               |                   | INT4IP<2:0>       |                    | INT4IS            | <1:0>             |                 | _                  | _                 | 00410 :00:              |                                  |          |                  |                 | OC4IS         | S<1:0> | 0000 |

| 10D0                        | IPC4                            | 15:0          | _               | _               | _               |                   | IC4IP<2:0>        |                    | IC4IS             | <1:0>             | _               | _                  | _                 | -                       | T4IP<2:0>                        |          | T4IS-            | <1:0>           | 0000          |        |      |

| 10E0                        | IPC5                            | 31:16         | 1               | _               | _               | AD1IP<2:0>        |                   |                    | AD1IS             | <1:0>             | -               | _                  | _                 | С                       | C5IP<2:0>                        |          | OC5IS            | S<1:0>          | 0000          |        |      |

| IUEU                        | IPC5                            | 15:0          | 1               | _               | _               | IC5IP<2:0>        |                   | IC5IS•             | <1:0>             | 1                 | _               | _                  |                   | T5IP<2:0>               |                                  | T5IS-    | <1:0>            | 0000            |               |        |      |

| 10F0                        | IPC6                            | 31:16         | _               | _               | _               | (                 | CMP1IP<2:0>       |                    |                   | S<1:0>            | _               | _                  | _                 | F                       | CEIP<2:0>                        |          | FCEIS            | S<1:0>          | 0000          |        |      |

| IUFU                        | IFCO                            | 15:0          | -               | _               | _               | F                 | RTCCIP<2:0>       |                    |                   | S<1:0>            | 1               | _                  | _                 | FS                      | SCMIP<2:0                        | >        | FSCMI            | S<1:0>          | 0000          |        |      |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

<sup>2:</sup> These bits are not available on PIC32MX1XX devices.

<sup>3:</sup> This register does not have associated CLR, SET, INV registers.

### 8.1 Oscillator Control Regiters

#### TABLE 8-1: OSCILLATOR CONTROL REGISTER MAP

| ess                         |                                 |           |       |       |          |                                                  |           |       |      |      | Bits    |         |      |      |      |        |      |      | · s        |

|-----------------------------|---------------------------------|-----------|-------|-------|----------|--------------------------------------------------|-----------|-------|------|------|---------|---------|------|------|------|--------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13    | 28/12                                            | 27/11     | 26/10 | 25/9 | 24/8 | 23/7    | 22/6    | 21/5 | 20/4 | 19/3 | 18/2   | 17/1 | 16/0 | All Resets |

| F000                        | OSCCON                          | 31:16     | _     | _     | Р        |                                                  |           |       |      |      |         | x1xx(2) |      |      |      |        |      |      |            |

| F000                        | OSCCON                          | 15:0      | _     |       | COSC<2:0 |                                                  |           |       |      |      |         | xxxx(2) |      |      |      |        |      |      |            |

| E010                        | OSCTUN                          | 31:16     | _     |       | _        | _                                                | -         | _     | _    | _    | _       | _       | -    | _    | _    | _      | _    | _    | 0000       |

| F010                        | OSCIUN                          | 15:0      | _     |       | _        | _                                                | -         | _     | _    | _    | _       | _       |      |      | TUN  | V<5:0> |      |      | 0000       |

| <b>-</b>                    | DEFOCAN                         | 31:16     | _     |       |          |                                                  |           |       |      |      | RODIV<1 | 14:0>   |      |      |      |        |      |      | 0000       |

| F020                        | REFOCON                         | 15:0      | ON    | _     | SIDL     | SIDL OE RSLP — DIVSWEN ACTIVE — — — — ROSEL<3:0> |           |       |      |      |         | 0000    |      |      |      |        |      |      |            |

| F000                        | DEFOTDIM                        | 31:16     |       |       |          | R                                                | OTRIM<8:0 | )>    |      |      |         | _       | _    | _    | _    | _      | _    | _    | 0000       |

| F030                        | REFOTRIM                        | 15:0      | _     | _     | _        | _                                                |           | 1     | _    | 1    |         | _       | _    |      | 1    | _      | -    | _    | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

3: This bit is only available on PIC32MX2XX devices.

#### REGISTER 9-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | -                 | _                 | _                 | _                | _                |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | CHSDIE            | CHSHIE            | CHDDIE            | CHDHIE            | CHBCIE            | CHCCIE            | CHTAIE           | CHERIE           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CHSDIF            | CHSHIF            | CHDDIF            | CHDHIF            | CHBCIF            | CHCCIF            | CHTAIF           | CHERIF           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-24 Unimplemented: Read as '0'

bit 23 CHSDIE: Channel Source Done Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 22 CHSHIE: Channel Source Half Empty Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 21 **CHDDIE:** Channel Destination Done Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 20 **CHDHIE:** Channel Destination Half Full Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 19 CHBCIE: Channel Block Transfer Complete Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 18 CHCCIE: Channel Cell Transfer Complete Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 17 CHTAIE: Channel Transfer Abort Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 16 CHERIE: Channel Address Error Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 15-8 Unimplemented: Read as '0'

bit 7 CHSDIF: Channel Source Done Interrupt Flag bit

1 = Channel Source Pointer has reached end of source (CHSPTR = CHSSIZ)

0 = No interrupt is pending

bit 6 CHSHIF: Channel Source Half Empty Interrupt Flag bit

1 = Channel Source Pointer has reached midpoint of source (CHSPTR = CHSSIZ/2)

0 = No interrupt is pending

bit 5 CHDDIF: Channel Destination Done Interrupt Flag bit

1 = Channel Destination Pointer has reached end of destination (CHDPTR = CHDSIZ)

0 = No interrupt is pending

#### 10.0 USB ON-THE-GO (OTG)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 27. "USB On-The-Go (OTG)"** (DS60001126), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 Full-Speed and Low-Speed embedded host, Full-Speed device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 10-1.

The clock generator provides the 48 MHz clock required for USB Full-Speed and Low-Speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

The PIC32 USB module includes the following features:

- · USB Full-Speed support for Host and Device

- · Low-Speed Host support

- · USB OTG support

- · Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- · Integrated USB transceiver

- · Transaction handshaking performed by hardware

- · Endpoint buffering anywhere in system RAM

- Integrated DMA to access system RAM and Flash

Note:

The implementation and use of the USB specifications, as well as other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc., also referred to as USB-IF (www.usb.org). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

© 2011-2016 Microchip Technology Inc.

TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       |       |       |      |      | Bi    | ts       |       |              |        |        |           |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|-------|----------|-------|--------------|--------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6     | 21/5  | 20/4         | 19/3   | 18/2   | 17/1      | 16/0     | All Resets |

| 5280                        | U1FRML <sup>(3)</sup>           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        | _     | _            | _      | _      | _         | _        | 0000       |

| 3200                        | OTTRIVIE                        | 15:0      |       | _     | _     | _     |       | _     |      | _    |       |          |       | FRML<        | 7:0>   |        |           |          | 0000       |

| 5290                        | U1FRMH <sup>(3)</sup>           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | -     | _        | _     | _            | _      | _      | _         | _        | 0000       |

| 0200                        | OTTTAMIT                        | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        | _     | _            | _      |        | FRMH<2:0> | •        | 0000       |

| 52A0                        | U1TOK                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |       | _        | _     | _            | _      | _      | _         | _        | 0000       |

| 02/10                       | OTTOR                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |       | PID      | <3:0> |              |        | EP     | <3:0>     |          | 0000       |

| 52B0                        | U1SOF                           | 31:16     |       | _     | _     | _     |       | _     |      | _    | _     | _        |       | _            | _      | _      | _         | _        | 0000       |

| 3200                        | 01001                           | 15:0      |       | _     | _     | _     |       | _     |      | _    |       |          |       | CNT<7        | 7:0>   |        |           |          | 0000       |

| 52C0                        | U1BDTP2                         | 31:16     |       | _     | _     | _     |       | _     |      | _    | _     | _        |       | _            | _      | _      | _         | _        | 0000       |

| 3200                        | 0100112                         | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |       |          |       | BDTPTRE      | H<7:0> |        |           |          | 0000       |

| 52D0                        | U1BDTP3                         | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        | _     | _            | _      | _      | _         | _        | 0000       |

| 02D0                        | 0100110                         | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |       |          |       | BDTPTRU      | J<7:0> |        |           |          | 0000       |

| 52E0                        | U1CNFG1                         | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        | _     | _            | _      | _      | _         | _        | 0000       |

| OZLO                        | 01014101                        | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | UTEYE | UOEMON   | _     | USBSIDL      | _      | _      | _         | UASUSPND | 0001       |

| 5300                        | U1EP0                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | ı     | _        | _     | <del>-</del> | _      | _      | ı         | _        | 0000       |

| 0000                        | OTELO                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | LSPD  | RETRYDIS | _     | EPCONDIS     | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5310                        | U1EP1                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        | _     | _            | _      | _      | _         | _        | 0000       |

| 3310                        | O I E I I                       | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        | _     | EPCONDIS     | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5320                        | U1EP2                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        | _     | _            | _      | _      | _         | _        | 0000       |

| 0020                        | 01212                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | -     | _        |       | EPCONDIS     | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5330                        | U1EP3                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        | _     | _            | _      | _      | _         | _        | 0000       |

| 0000                        | 01210                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | -     | _        |       | EPCONDIS     | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5340                        | U1EP4                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        | _     | _            | _      | _      | _         | _        | 0000       |

| 00.0                        |                                 | 15:0      |       | _     | _     | _     | _     | _     | _    | _    | _     | _        |       | EPCONDIS     | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5350                        | U1EP5                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | -     | _        | _     | _            | _      | _      | -         | _        | 0000       |

| 0000                        | 01210                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | -     | _        |       | EPCONDIS     | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5360                        | U1EP6                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |       | _        |       | _            | _      | _      |           | _        | 0000       |

| 3000                        | 0.2.0                           | 15:0      |       | _     | _     | _     | _     | _     |      | _    |       | _        |       | EPCONDIS     | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5370                        | U1EP7                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |       | _        |       | _            | _      | _      |           | _        | 0000       |

| 30.0                        | 0.2.                            | 15:0      |       | _     | _     | _     |       | _     | _    |      |       | _        |       | EPCONDIS     | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5380                        | U1EP8                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |       | _        | _     | _            | _      | _      | -         | _        | 0000       |

| 3000                        | 01210                           | 15:0      |       | _     | _     | _     | _     | _     | _    | _    |       | _        | _     | EPCONDIS     | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

This register does not have associated SET and INV registers.

This register does not have associated CLR, SET and INV registers.

Reset value for this bit is undefined.

#### REGISTER 10-1: U10TGIR: USB OTG INTERRUPT STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 |                   | -                 | -                 | -                 | -                 | -                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | R/WC-0, HS        | U-0              | R/WC-0, HS       |

| 7:0          | IDIF              | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF           | SESENDIF          | _                | VBUSVDIF         |

**Legend:** WC = Write '1' to clear HS = Hardware Settable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 IDIF: ID State Change Indicator bit

1 = A change in the ID state was detected0 = No change in the ID state was detected

bit 6 T1MSECIF: 1 Millisecond Timer bit

1 = 1 millisecond timer has expired0 = 1 millisecond timer has not expired

bit 5 LSTATEIF: Line State Stable Indicator bit

1 = USB line state has been stable for 1 ms, but different from last time

0 = USB line state has not been stable for 1 ms

bit 4 ACTVIF: Bus Activity Indicator bit

1 = Activity on the D+, D-, ID or VBUS pins has caused the device to wake-up

0 = Activity has not been detected

bit 3 **SESVDIF:** Session Valid Change Indicator bit

1 = VBUS voltage has dropped below the session end level

0 = VBUS voltage has not dropped below the session end level

bit 2 SESENDIF: B-Device VBUS Change Indicator bit

1 = A change on the session end input was detected

0 = No change on the session end input was detected

bit 1 Unimplemented: Read as '0'

bit 0 VBUSVDIF: A-Device VBUS Change Indicator bit

1 = A change on the session valid input was detected

0 = No change on the session valid input was detected

#### REGISTER 10-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER (CONTINUED)

bit 1 CRC5EF: CRC5 Host Error Flag bit<sup>(4)</sup>

1 = Token packet rejected due to CRC5 error

0 = Token packet accepted **EOFEF:** EOF Error Flag bit<sup>(3,5)</sup>

1 = An EOF error condition was detected0 = No EOF error condition was detected

bit 0 PIDEF: PID Check Failure Flag bit

1 = PID check failed0 = PID check passed

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- 2: This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

#### REGISTER 10-20: U1CNFG1: USB CONFIGURATION 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | -                 | -                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0            |

| 7:0          | UTEYE             | UOEMON            | _                 | USBSIDL           | _                 | _                 | _                | UASUSPND         |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 UTEYE: USB Eye-Pattern Test Enable bit

1 = Eye-Pattern Test is enabled0 = Eye-Pattern Test is disabled

bit 6 **UOEMON:** USB OE Monitor Enable bit

1 = OE signal is active; it indicates intervals during which the D+/D- lines are driving

0 = OE signal is inactive

bit 5 Unimplemented: Read as '0'

bit 4 USBSIDL: Stop in Idle Mode bit

1 = Discontinue module operation when the device enters Idle mode

0 = Continue module operation when the device enters Idle mode

bit 3-1 Unimplemented: Read as '0'

bit 0 **UASUSPND:** Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (U1PWRC<1>) in Register 10-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (U1PWRC<1>) to suspend the module, including the USB 48 MHz clock.

TABLE 11-4: PORTB REGISTER MAP

| ess                         |                  |           |               |               |               |                              |               |               |              | Bits         |              |                             |              |              |              |              |              |              |            |

|-----------------------------|------------------|-----------|---------------|---------------|---------------|------------------------------|---------------|---------------|--------------|--------------|--------------|-----------------------------|--------------|--------------|--------------|--------------|--------------|--------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range | 31/15         | 30/14         | 29/13         | 28/12                        | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6                        | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All Resets |

| 6100                        | ANSELB           | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | _            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0100                        | ANOLLD           | 15:0      | ANSB15        | ANSB14        | ANSB13        | ANSB12 <sup>(2)</sup>        | _             | _             | _            | _            | -            | _                           | _            | _            | ANSB3        | ANSB2        | ANSB1        | ANSB0        | EOOF       |

| 6110                        | TRISB            | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | _            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0110                        | TITIOD           | 15:0      | TRISB15       | TRISB14       | TRISB13       | TRISB12 <sup>(2)</sup>       | TRISB11       | TRISB10       | TRISB9       | TRISB8       | TRISB7       | TRISB6 <sup>(2)</sup>       | TRISB5       | TRISB4       | TRISB3       | TRISB2       | TRISB1       | TRISB0       | FFFF       |

| 6120                        | PORTB            | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | _            | _                           | _            |              |              |              |              |              | 0000       |

| 0120                        | TOKID            | 15:0      | RB15          | RB14          | RB13          | RB12 <sup>(2)</sup>          | RB11          | RB10          | RB9          | RB8          | RB7          | RC6 <sup>(2)</sup>          | RB5          | RB4          | RB3          | RB2          | RB1          | RB0          | xxxx       |

| 6130                        | LATB             | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | _            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0100                        | LAND             | 15:0      | LATB15        | LATB14        | LATB13        | LATB12 <sup>(2)</sup>        | LATB11        | LATB10        | LATB9        | LATB8        | LATB7        | LATB6 <sup>(2)</sup>        | LATB5        | LATB4        | LATB3        | LATB2        | LATB1        | LATB0        | xxxx       |

| 6140                        | ODCB             | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | _            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0140                        | ODCB             | 15:0      | ODCB15        | ODCB14        | ODCB13        | ODCB12 <sup>(2)</sup>        | ODCB11        | ODCB10        | ODCB9        | ODCB8        | ODCB7        | ODCB6                       | ODCB5        | ODCB4        | ODCB3        | ODCB2        | ODCB1        | ODCB0        | 0000       |

| 6150                        | CNPUB            | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | _            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0130                        | CINFUB           | 15:0      | CNPUB15       | CNPUB14       | CNPUB13       | CNPUB12 <sup>(2)</sup>       | CNPUB11       | CNPUB10       | CNPUB9       | CNPUB8       | CNPUB7       | CNPUB6 <sup>(2)</sup>       | CNPUB5       | CNPUB4       | CNPUB3       | CNPUB2       | CNPUB1       | CNPUB0       | 0000       |

| 6160                        |                  | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | -            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0100                        | CINFUB           | 15:0      | CNPDB15       | CNPDB14       | CNPDB13       | CNPDB12 <sup>(2)</sup>       | CNPDB11       | CNPDB10       | CNPDB9       | CNPDB8       | CNPDB7       | CNPDB6 <sup>(2)</sup>       | CNPDB5       | CNPDB4       | CNPDB3       | CNPDB2       | CNPDB1       | CNPDB0       | 0000       |

| 6170                        | CNCONB           | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | -            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0170                        | CINCOIND         | 15:0      | ON            | _             | SIDL          | _                            | _             | _             | _            | _            | -            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 6180                        | CNENB            | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | -            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0100                        | CINEIND          | 15:0      | CNIEB15       | CNIEB14       | CNIEB13       | CNIEB11 <sup>(2)</sup>       | CNIEB11       | CNIEB10       | CNIEB9       | CNIEB8       | CNIEB7       | CNIEB6 <sup>(2)</sup>       | CNIEB5       | CNIEB4       | CNIEB3       | CNIEB2       | CNIEB1       | CNIEB0       | 0000       |

|                             |                  | 31:16     | _             | _             | -             | _                            | _             | -             | -            | _            | ı            | _                           | _            | -            | -            | -            | _            | _            | 0000       |

| 6190                        | CNSTATB          | 15:0      | CN<br>STATB15 | CN<br>STATB14 | CN<br>STATB13 | CN<br>STATB12 <sup>(2)</sup> | CN<br>STATB11 | CN<br>STATB10 | CN<br>STATB9 | CN<br>STATB8 | CN<br>STATB7 | CN<br>STATB6 <sup>(2)</sup> | CN<br>STATB5 | CN<br>STATB4 | CN<br>STATB3 | CN<br>STATB2 | CN<br>STATB1 | CN<br>STATB0 | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This bit is not available on PIC32MX2XX devices. The reset value for the TRISB register when this bit is not available is 0x0000EFBF.

#### REGISTER 18-1: I2CXCON: I<sup>2</sup>C CONTROL REGISTER

|              | _                 |                   |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |

**Legend:** HC = Cleared in Hardware

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** I<sup>2</sup>C Enable bit<sup>(1)</sup>

1 = Enables the I<sup>2</sup>C module and configures the SDA and SCL pins as serial port pins

$0 = \text{Disables the } I^2\text{C module}$ ; all  $I^2\text{C pins are controlled by PORT functions}$

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Discontinue module operation when the device enters Idle mode

0 = Continue module operation when the device enters Idle mode

bit 12 **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

1 = Release SCLx clock

0 = Hold SCLx clock low (clock stretch)

#### If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception.

#### If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware clear at beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 = Strict I<sup>2</sup>C Reserved Address Rule not enabled

- bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 DISSLW: Disable Slew Rate Control bit

- 1 = Slew rate control disabled

- 0 = Slew rate control enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 21-3: RTCTIME: RTC TIME VALUE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

|              | _                 | _                 | HR10              | <1:0>             | HR01<3:0>         |                   |                  |                  |

| 23:16        | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

|              | _                 | MIN10<2:0>        |                   |                   | MIN01<3:0>        |                   |                  |                  |

| 15:8         | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

|              | _                 | SEC10<2:0>        |                   |                   | SEC01<3:0>        |                   |                  |                  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary-Coded Decimal Value of Hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary-Coded Decimal Value of Hours bits, 1s place digit; contains a value from 0 to 9

bit 23 Unimplemented: Read as '0'

bit 22-20 MIN10<2:0>: Binary-Coded Decimal Value of Minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary-Coded Decimal Value of Minutes bits, 1s place digit; contains a value from 0 to 9

bit 15 Unimplemented: Read as '0'

bit 14-12 SEC10<2:0>: Binary-Coded Decimal Value of Seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary-Coded Decimal Value of Seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

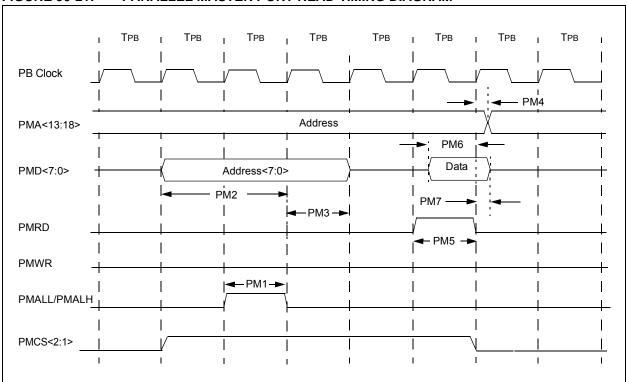

**TABLE 30-37: PARALLEL SLAVE PORT REQUIREMENTS**

| AC CHARACTERISTICS |              |                                                     | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |      |      |       |            |  |

|--------------------|--------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|--|

| Para<br>m.No.      | Symbol       | Characteristics <sup>(1)</sup>                      | Min.                                                                                                                                                                                                                                           | Тур. | Max. | Units | Conditions |  |

| PS1                | TdtV2wr<br>H | Data In Valid before WR or CS Inactive (setup time) | 20                                                                                                                                                                                                                                             |      | _    | ns    | _          |  |

| PS2                | TwrH2dt<br>I | WR or CS Inactive to Data-In Invalid (hold time)    | 40                                                                                                                                                                                                                                             |      | _    | ns    | _          |  |

| PS3                | TrdL2dt<br>V | RD and CS Active to Data-Out Valid                  | _                                                                                                                                                                                                                                              | _    | 60   | ns    | _          |  |

| PS4                | TrdH2dtl     | RD Active or CS Inactive to Data-Out Invalid        | 0                                                                                                                                                                                                                                              | _    | 10   | ns    | _          |  |

| PS5                | Tcs          | CS Active Time                                      | TPB + 40                                                                                                                                                                                                                                       | _    | _    | ns    | _          |  |

| PS6                | Twr          | WR Active Time                                      | TPB + 25                                                                                                                                                                                                                                       |      | _    | ns    | _          |  |

| PS7                | TRD          | RD Active Time                                      | TpB + 25                                                                                                                                                                                                                                       | _    | _    | ns    | _          |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

#### FIGURE 30-21: PARALLEL MASTER PORT READ TIMING DIAGRAM

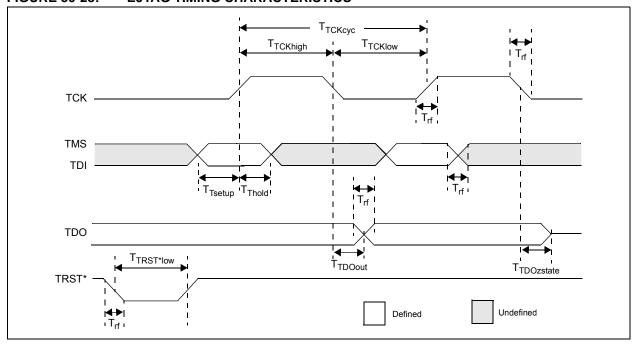

FIGURE 30-23: EJTAG TIMING CHARACTERISTICS

**TABLE 30-42: EJTAG TIMING REQUIREMENTS**

| AC CHARACTERISTICS |            |                                                  |                           | s otherw | ating Co<br>vise state<br>erature | • |  |

|--------------------|------------|--------------------------------------------------|---------------------------|----------|-----------------------------------|---|--|

| Param.<br>No.      | Symbol     | Description <sup>(1)</sup>                       | Min. Max. Units Condition |          | Conditions                        |   |  |

| EJ1                | Ттсксүс    | TCK Cycle Time                                   | 25                        | _        | ns                                | _ |  |

| EJ2                | TTCKHIGH   | TCK High Time                                    | 10                        | _        | ns                                | _ |  |

| EJ3                | TTCKLOW    | TCK Low Time                                     | 10                        | _        | ns                                | _ |  |

| EJ4                | TTSETUP    | TAP Signals Setup Time Before Rising TCK         | 5                         | _        | ns                                | _ |  |

| EJ5                | TTHOLD     | TAP Signals Hold Time After Rising TCK           | 3                         | _        | ns                                | _ |  |

| EJ6                | TTDOOUT    | TDO Output Delay Time from Falling TCK           | _                         | 5        | ns                                | _ |  |

| EJ7                | TTDOZSTATE | TDO 3-State Delay Time from Falling TCK          | _                         | 5        | ns                                | _ |  |

| EJ8                | TTRSTLOW   | TRST Low Time                                    | 25                        | _        | ns                                | _ |  |

| EJ9                | TRF        | TAP Signals Rise/Fall Time, All Input and Output | _                         | _        | ns                                | _ |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

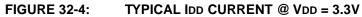

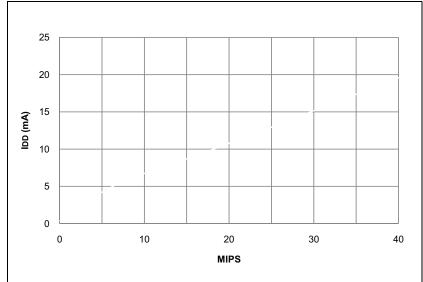

#### **FIGURE 32-5**: TYPICAL IIDLE CURRENT @ VDD = 3.3V

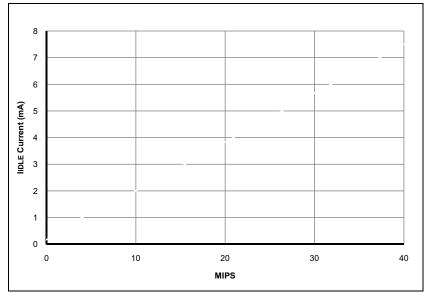

# 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-157C Sheet 1 of 2

### **Revision D (February 2012)**

All occurrences of VUSB were changed to: VUSB3V3. In addition, text and formatting changes were incorporated throughout the document.

All other major changes are referenced by their respective section in Table A-3.

TABLE A-3: MAJOR SECTION UPDATES

| Section                                                                                | Update Description                                                                                                                                                                |  |  |  |  |

|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| "32-bit Microcontrollers (up to 128                                                    | Corrected a part number error in all pin diagrams.                                                                                                                                |  |  |  |  |

| KB Flash and 32 KB SRAM) with Audio and Graphics Interfaces, USB, and Advanced Analog" | Updated the DMA Channels (Programmable/Dedicated) column in the PIC32MX1XX General Purpose Family Features (see Table 1).                                                         |  |  |  |  |

| 1.0 "Device Overview"                                                                  | Added the TQFP and VTLA packages to the 44-pin column heading and updated the pin numbers for the SCL1, SCL2, SDA1, and SDA2 pins in the Pinout I/O Descriptions (see Table 1-1). |  |  |  |  |

| 7.0 "Interrupt Controller"                                                             | Updated the Note that follows the features.                                                                                                                                       |  |  |  |  |

|                                                                                        | Updated the Interrupt Controller Block Diagram (see Figure 7-1).                                                                                                                  |  |  |  |  |