Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K × 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 10x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f256b-v-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

|                     |      |                                    |                  | Rem             | appab                                  | le Pe | riphe                | erals                              |                    |                     |                  |     | (                                        |      | ls)                          |      |          |      |                                 |

|---------------------|------|------------------------------------|------------------|-----------------|----------------------------------------|-------|----------------------|------------------------------------|--------------------|---------------------|------------------|-----|------------------------------------------|------|------------------------------|------|----------|------|---------------------------------|

| Device              | Pins | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins | Timers <sup>(2)</sup> /Capture/Compare | UART  | SPI/I <sup>2</sup> S | External Interrupts <sup>(3)</sup> | Analog Comparators | USB On-The-Go (OTG) | I <sup>2</sup> C | dMq | DMA Channels<br>(Programmable/Dedicated) | CTMU | 10-bit 1 Msps ADC (Channels) | RTCC | I/O Pins | JTAG | Packages                        |

| PIC32MX210F016B     | 28   | 16+3                               | 4                | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX210F016C     | 36   | 16+3                               | 4                | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 25       | Y    | VTLA                            |

| PIC32MX210F016D     | 44   | 16+3                               | 4                | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

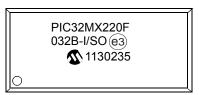

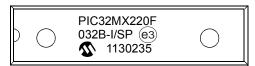

| PIC32MX220F032B     | 28   | 32+3                               | 8                | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX220F032C     | 36   | 32+3                               | 8                | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA                            |

| PIC32MX220F032D     | 44   | 32+3                               | 8                | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX230F064B     | 28   | 64+3                               | 16               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX230F064C     | 36   | 64+3                               | 16               | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA                            |

| PIC32MX230F064D     | 44   | 64+3                               | 16               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX250F128B     | 28   | 128+3                              | 32               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX250F128C     | 36   | 128+3                              | 32               | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA<br>VTLA,                   |

| PIC32MX250F128D     | 44   | 128+3                              | 32               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | TQFP,<br>QFN                    |

| PIC32MX230F256B     | 28   | 256+3                              | 16               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX230F256D     | 44   | 256+3                              | 16               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX270F256B     | 28   | 256+3                              | 64               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX270F256D     | 44   | 256+3                              | 64               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX270F256DB(4) | 44   | 256+3                              | 64               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

#### TABLE 2: PIC32MX2XX 28/36/44-PIN USB FAMILY FEATURES

Note 1: This device features 3 KB of boot Flash memory.

**2:** Four out of five timers are remappable.

3: Four out of five external interrupts are remappable.

4: This PIC32 device is targeted to specific audio software packages that are tracked for licensing royalty purposes. All peripherals and electrical characteristics are identical to their corresponding base part numbers.

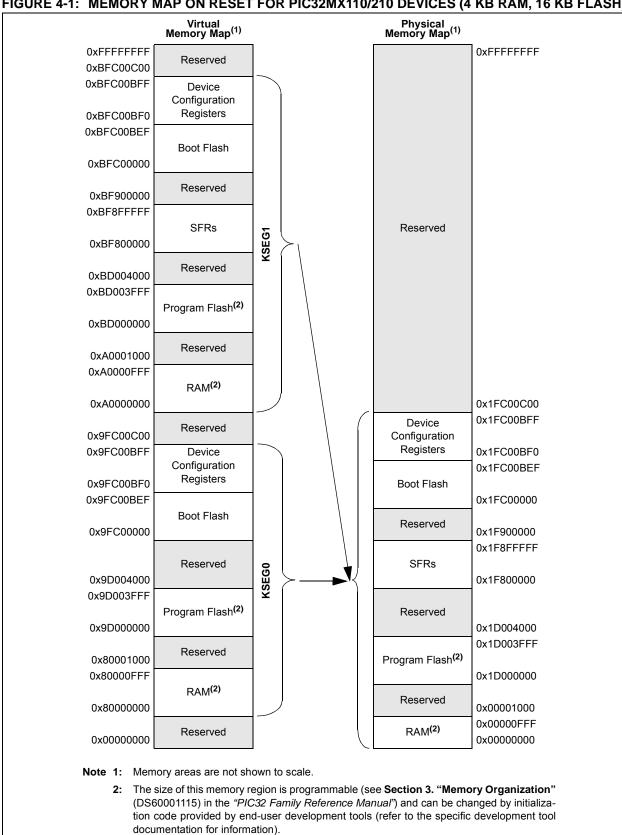

#### FIGURE 4-1: MEMORY MAP ON RESET FOR PIC32MX110/210 DEVICES (4 KB RAM, 16 KB FLASH)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS09            | IFS08            |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          | IFS07             | IFS06             | IFS05             | IFS04             | IFS03             | IFS02             | IFS01            | IFS00            |  |  |

#### REGISTER 7-4: IFSx: INTERRUPT FLAG STATUS REGISTER

#### Legend:

| <b>L</b> ogonan   |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-0 IFS31-IFS00: Interrupt Flag Status bits

- 1 = Interrupt request has occurred

- 0 = No interrupt request has occurred

**Note:** This register represents a generic definition of the IFSx register. Refer to Table 7-1 for the exact bit definitions.

#### REGISTER 7-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC09            | IEC08            |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | IEC07             | IEC06             | IEC05             | IEC04             | IEC03             | IEC02             | IEC01            | IEC00            |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-0 IEC31-IEC00: Interrupt Enable bits

1 = Interrupt is enabled

0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 7-1 for the exact bit definitions.

# 8.1 Oscillator Control Regiters

| TAB                         | BLE 8-1: OSCILLATOR CONTROL REGISTER MAP |           |       |                                               |          |                                                                     |           |       |          |      |         |                      |       |       |                     |                       |        |       |           |

|-----------------------------|------------------------------------------|-----------|-------|-----------------------------------------------|----------|---------------------------------------------------------------------|-----------|-------|----------|------|---------|----------------------|-------|-------|---------------------|-----------------------|--------|-------|-----------|

| ess                         |                                          | 0         | Bits  |                                               |          |                                                                     |           |       |          |      |         |                      |       | ú     |                     |                       |        |       |           |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup>          | Bit Range | 31/15 | 30/14                                         | 29/13    | 28/12                                                               | 27/11     | 26/10 | 25/9     | 24/8 | 23/7    | 22/6                 | 21/5  | 20/4  | 19/3                | 18/2                  | 17/1   | 16/0  | All Reset |

| F000                        | OSCCON                                   | 31:16     | —     | _                                             | Р        | PLLODIV<2:0> FRCDIV<2:0> — SOSCRDY PBDIVRDY PBDIV<1:0> PLLMULT<2:0> |           |       |          |      |         |                      |       | >     | x1xx <sup>(2)</sup> |                       |        |       |           |

| FUUU                        | 030001                                   | 15:0      | —     |                                               | COSC<2:0 | V                                                                   | Ι         |       | NOSC<2:0 | >    | CLKLOCK | ULOCK <sup>(3)</sup> | SLOCK | SLPEN | CF                  | UFRCEN <sup>(3)</sup> | SOSCEN | OSWEN | xxxx(2)   |

| F010                        | OSCTUN                                   | 31:16     | _     | _                                             |          | _                                                                   | _         |       |          | _    | _       | _                    | _     | _     |                     | _                     | —      | _     | 0000      |

| 1010                        | 030101                                   | 15:0      | _     | _                                             |          | _                                                                   | _         |       |          | _    | _       | _                    |       |       | TUN                 | l<5:0>                |        |       | 0000      |

| 5000                        |                                          | 31:16     | _     |                                               |          |                                                                     |           |       |          |      | RODIV<1 | 4:0>                 |       |       |                     |                       |        |       | 0000      |

| F020                        | REFOCON                                  | 15:0      | ON    | ON - SIDL OE RSLP - DIVSWEN ACTIVE ROSEL<3:0> |          |                                                                     |           |       |          |      |         | 0000                 |       |       |                     |                       |        |       |           |

| F000                        | DEEOTDIM                                 | 31:16     |       |                                               |          | R                                                                   | OTRIM<8:0 | )>    |          |      |         | _                    | _     | _     | _                   | _                     | _      | _     | 0000      |

| F030                        | REFOTRIM                                 | 15:0      | _     | _                                             |          | _                                                                   | _         |       |          | -    | _       | _                    | _     | _     |                     | _                     | —      | _     | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

3: This bit is only available on PIC32MX2XX devices.

| Bit<br>Range | Bit<br>31/23/15/7              | Bit<br>30/22/14/6           | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|--------------------------------|-----------------------------|-------------------|-------------------|---------------------|-------------------|------------------|------------------|--|--|--|--|

|              | U-0                            | R/W-0                       | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | — RODIV<14:8> <sup>(1,3)</sup> |                             |                   |                   |                     |                   |                  |                  |  |  |  |  |

|              | R/W-0                          | R/W-0                       | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        |                                | RODIV<7:0> <sup>(1,3)</sup> |                   |                   |                     |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0                          | U-0                         | R/W-0             | R/W-0             | R/W-0               | U-0               | R/W-0, HC        | R-0, HS, HC      |  |  |  |  |

| 15:8         | ON                             | _                           | SIDL              | OE                | RSLP <sup>(2)</sup> | _                 | DIVSWEN          | ACTIVE           |  |  |  |  |

|              | U-0                            | U-0                         | U-0               | U-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                                |                             |                   |                   |                     | ROSEL             | .<3:0>(1)        |                  |  |  |  |  |

#### REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| Legend:           | HC = Hardware Clearable | HS = Hardware Settable   |                    |

|-------------------|-------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |

bit 31 Unimplemented: Read as '0'

| bit 30-16 | RODIV<14:0> Reference Clock Divider bits <sup>(1,3)</sup>                           |

|-----------|-------------------------------------------------------------------------------------|

|           | The value selects the reference clock divider bits. See Figure 8-1 for information. |

| bit 15    | ON: Output Enable bit                                                               |

|           | 1 = Reference Oscillator module is enabled                                          |

|           | 0 = Reference Oscillator module is disabled                                         |

| bit 14    | Unimplemented: Read as '0'                                                          |

| bit 13    | SIDL: Peripheral Stop in Idle Mode bit                                              |

- 1 = Discontinue module operation when the device enters Idle mode

- 0 =Continue module operation when the device enters lide mode

- bit 12 **OE:** Reference Clock Output Enable bit

- 1 = Reference clock is driven out on REFCLKO pin

- 0 = Reference clock is not driven out on REFCLKO pin

- bit 11 RSLP: Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference Oscillator module output continues to run in Sleep

- 0 = Reference Oscillator module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 DIVSWEN: Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- bit 8 ACTIVE: Reference Clock Request Status bit

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- **2:** This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6       | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

|--------------|-------------------|-------------------------|-------------------------|-------------------|----------------------|-------------------|-----------------------|-------------------------|

| 31:24        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 31.24        | —                 | _                       | _                       | _                 | —                    | —                 | -                     | —                       |

| 23:16        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 23.10        | —                 | _                       | _                       | _                 | —                    | —                 | -                     | —                       |

| 15:8         | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 15.6         | —                 | _                       | _                       | _                 | —                    | —                 | -                     | —                       |

|              | R/WC-0, HS        | R/WC-0, HS              | R/WC-0, HS              | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS        | R-0                   | R/WC-0, HS              |

| 7:0          | STALLIF           | ATTACHIF <sup>(1)</sup> | RESUMEIF <sup>(2)</sup> | IDLEIF            | TRNIF <sup>(3)</sup> | SOFIF             | UERRIF <sup>(4)</sup> | URSTIF <sup>(5)</sup>   |

|              | STALLIF           |                         | INE SOMEIFY /           | IDLEIF            |                      | JOFIE             |                       | DETACHIF <sup>(6)</sup> |

### REGISTER 10-6: U1IR: USB INTERRUPT REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settat | ble bit            |

|-------------------|-------------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7       | <b>STALLIF:</b> STALL Handshake Interrupt bit<br>1 = In Host mode a STALL handshake was received during the handshake phase of the transaction<br>In Device mode a STALL handshake was transmitted during the handshake phase of the transaction<br>0 = STALL handshake has not been sent                                                                                                                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6       | ATTACHIF: Peripheral Attach Interrupt bit <sup>(1)</sup><br>1 = Peripheral attachment was detected by the USB module<br>0 = Peripheral attachment was not detected                                                                                                                                                                                                                                                                               |

| bit 5       | <b>RESUMEIF:</b> Resume Interrupt bit <sup>(2)</sup><br>1 = K-State is observed on the D+ or D- pin for 2.5 μs<br>0 = K-State is not observed                                                                                                                                                                                                                                                                                                    |

| bit 4       | IDLEIF: Idle Detect Interrupt bit<br>1 = Idle condition detected (constant Idle state of 3 ms or more)<br>0 = No Idle condition detected                                                                                                                                                                                                                                                                                                         |

| bit 3       | <b>TRNIF:</b> Token Processing Complete Interrupt bit <sup>(3)</sup><br>1 = Processing of current token is complete; a read of the U1STAT register will provide endpoint information<br>0 = Processing of current token not complete                                                                                                                                                                                                             |

| bit 2       | <b>SOFIF:</b> SOF Token Interrupt bit<br>1 = SOF token received by the peripheral or the SOF threshold reached by the host<br>0 = SOF token was not received nor threshold reached                                                                                                                                                                                                                                                               |

| bit 1       | <b>UERRIF</b> : USB Error Condition Interrupt bit <sup>(4)</sup><br>1 = Unmasked error condition has occurred<br>0 = Unmasked error condition has not occurred                                                                                                                                                                                                                                                                                   |

| bit 0       | <pre>URSTIF: USB Reset Interrupt bit (Device mode)<sup>(5)</sup> 1 = Valid USB Reset has occurred 0 = No USB Reset has occurred DETACHIF: USB Detach Interrupt bit (Host mode)<sup>(6)</sup> 1 = Peripheral detachment was detected by the USB module 0 = Peripheral detachment was not detected</pre>                                                                                                                                           |

| 3<br>2<br>5 | <ul> <li>This bit is valid only if the HOSTEN bit is set (see Register 10-11), there is no activity on the USB for 2.5 µs, and the current bus state is not SE0.</li> <li>When not in Suspend mode, this interrupt should be disabled.</li> <li>Clearing this bit will cause the STAT FIFO to advance.</li> <li>Only error conditions enabled through the U1EIE register will set this bit.</li> <li>Device mode.</li> <li>Host mode.</li> </ul> |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |  |  |  |

| 31.24        |                   | —                 |                   | —                 |                   |                   |                  | —                |  |  |  |  |  |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |  |  |  |

| 23.10        |                   | —                 |                   | —                 | -                 |                   |                  | —                |  |  |  |  |  |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |  |  |  |

| 15.0         | -                 | —                 | -                 | —                 | _                 | -                 | —                | —                |  |  |  |  |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |  |  |

| 7.0          | LSPDEN            |                   |                   | D                 | EVADDR<6:0        | >                 | DEVADDR<6:0>     |                  |  |  |  |  |  |  |  |  |  |

## REGISTER 10-12: U1ADDR: USB ADDRESS REGISTER

### Legend:

| U                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7 LSPDEN: Low-Speed Enable Indicator bit

1 = Next token command to be executed at Low-Speed

0 = Next token command to be executed at Full-Speed

bit 6-0 **DEVADDR<6:0>:** 7-bit USB Device Address bits

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | —                 | —                 | —                 | _                 | —                 | _                 | —                |                  |  |  |  |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | —                 | —                 | —                 | _                 | —                 | _                 | —                |                  |  |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 15.0         | —                 | —                 | —                 | -                 | —                 | _                 | —                | -                |  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |

| 7:0          |                   |                   |                   | FRML              | <7:0>             |                   |                  |                  |  |  |  |  |  |

#### REGISTER 10-13: U1FRML: USB FRAME NUMBER LOW REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **FRML<7:0>:** The 11-bit Frame Number Lower bits

The register bits are updated with the current frame number whenever a SOF TOKEN is received.

#### TABLE 11-5: PORTC REGISTER MAP

| ess                         | -                                 |           |       |       |       |       |       |       |          |                       |                         | Bits                  |                       |                         |          |                       |          |          |            |

|-----------------------------|-----------------------------------|-----------|-------|-------|-------|-------|-------|-------|----------|-----------------------|-------------------------|-----------------------|-----------------------|-------------------------|----------|-----------------------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1,2)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9     | 24/8                  | 23/7                    | 22/6                  | 21/5                  | 20/4                    | 19/3     | 18/2                  | 17/1     | 16/0     | All Resets |

| 6200                        | ANSELC                            | 31:16     |       | _     |       |       | —     | —     | _        | -                     | _                       | -                     | _                     | _                       | —        | _                     | —        |          | 0000       |

| 0200                        | ,                                 | 15:0      | —     | —     | —     | —     | —     | —     |          |                       | —                       |                       |                       | _                       | ANSC3(4) | ANSC2 <sup>(3)</sup>  | ANSC1    | ANSC0    | 000F       |

| 6210                        | TRISC                             | 31:16     | _     | _     | —     | —     | —     | —     | —        | —                     | —                       | —                     | —                     | —                       | —        | —                     | —        |          | 0000       |

| 0210                        | 11100                             | 15:0      | _     | _     | —     | —     | —     | —     | TRISC9   | TRISC8 <sup>(3)</sup> | TRISC7 <sup>(3)</sup>   | TRISC6 <sup>(3)</sup> | TRISC5 <sup>(3)</sup> | TRISC4 <sup>(3)</sup>   | TRISC3   | TRISC2 <sup>(3)</sup> | TRISC1   | TRISC0   | 03FF       |

| 6220                        | PORTC                             | 31:16     | —     | —     | —     | —     | —     | —     | _        |                       | _                       |                       | _                     |                         |          |                       |          |          | 0000       |

| 0220                        |                                   | 15:0      | _     | _     | —     | —     | —     | —     | RC9      | RC8 <sup>(3)</sup>    | RC7 <sup>(3)</sup>      | RC6 <sup>(3)</sup>    | RC5 <sup>(3)</sup>    | RC4 <sup>(3)</sup>      | RC3      | RC2 <sup>(3)</sup>    | RC1      | RC0      | xxxx       |

| 6230                        | LATC                              | 31:16     | _     | _     | —     | —     | —     | —     | _        |                       | _                       |                       |                       | _                       | —        |                       | —        | —        | 0000       |

| 0230                        |                                   | 15:0      |       |       | _     | _     | _     | _     | LATC9    | LATC8 <sup>(3)</sup>  | LATC7 <sup>(3)</sup>    | LATC6 <sup>(3)</sup>  | LATC5 <sup>(3)</sup>  | LATC4 <sup>(3)</sup>    | LATC3    | LATC2 <sup>(3)</sup>  | LATC1    | LATC0    | xxxx       |

| 6240                        | ODCC                              | 31:16     |       |       | _     | _     | _     | _     | —        |                       |                         |                       |                       |                         | _        |                       | _        | _        | 0000       |

| 6240                        | ODCC                              | 15:0      |       |       | _     | _     | _     | _     | ODCC9    | ODCC8 <sup>(3)</sup>  | ODCC7 <sup>(3)</sup>    | ODCC6 <sup>(3)</sup>  | ODCC5 <sup>(3)</sup>  | ODCC4 <sup>(3)</sup>    | ODCC3    | ODCC2 <sup>(3)</sup>  | ODCC1    | ODCC0    | 0000       |

| 0050                        |                                   | 31:16     |       |       | —     | —     | —     | -     | —        | -                     | _                       | -                     | —                     | —                       | —        | —                     | —        | —        | 0000       |

| 6250                        | CNPUC                             | 15:0      | _     | _     | _     | _     | —     | —     | CNPUC9   | CNPUC8 <sup>(3)</sup> | CNPUC7 <sup>(3)</sup>   | CNPUC6 <sup>(3)</sup> | CNPUC5 <sup>(3)</sup> | CNPUC4 <sup>(3)</sup>   | CNPUC3   | CNPUC2 <sup>(3)</sup> | CNPUC1   | CNPUC0   | 0000       |

| 0000                        |                                   | 31:16     | _     | _     | _     | _     | _     | _     | —        | _                     | _                       | _                     | _                     | —                       | _        | —                     | _        | _        | 0000       |

| 6260                        | CNPDC                             | 15:0      | _     | _     | —     | —     | —     | —     | CNPDC9   | CNPDC8 <sup>(3)</sup> | CNPDC7 <sup>(3)</sup>   | CNPDC6 <sup>(3)</sup> | CNPDC5 <sup>(3)</sup> | CNPDC4 <sup>(3)</sup>   | CNPDC3   | CNPDC2 <sup>(3)</sup> | CNPDC1   | CNPDC0   | 0000       |

| 0070                        | anaana                            | 31:16     | _     | _     | —     | —     | —     | —     | _        | _                     | _                       | _                     | —                     | —                       | —        | _                     | —        | —        | 0000       |

| 6270                        | CNCONC                            | 15:0      | ON    | _     | SIDL  | _     | —     | —     | _        | _                     | _                       | _                     | _                     | —                       | —        | _                     | —        | —        | 0000       |

|                             |                                   | 31:16     | _     | _     | _     |       | —     | _     |          |                       | _                       |                       | _                     | _                       | _        | _                     | —        | —        | 0000       |

| 6280                        | CNENC                             | 15:0      | _     | _     | _     |       | —     | _     | CNIEC9   | CNIEC8(3)             | CNIEC7 <sup>(3)</sup>   | CNIEC6(3)             | CNIEC5 <sup>(3)</sup> | CNIEC4 <sup>(3)</sup>   | CNIEC3   | CNIEC2 <sup>(3)</sup> | CNIEC1   | CNIEC0   | 0000       |

|                             |                                   | 31:16     | _     | _     | _     | _     | _     | _     | _        |                       | _                       |                       | _                     | _                       | —        |                       | —        | —        | 0000       |

| 6290                        | CNSTATC                           | 15:0      | _     | _     | _     | _     | _     | _     | CNSTATC9 | CNSTATC8(3)           | CNSTATC7 <sup>(3)</sup> | CNSTATC6(3)           | CNSTATC5(3)           | CNSTATC4 <sup>(3)</sup> | CNSTATC3 | CNSTATC2(3)           | CNSTATC1 | CNSTATC0 | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: PORTC is not available on 28-pin devices.

3: This bit is only available on 44-pin devices.

4: This bit is only available on USB-enabled devices with 36 or 44 pins.

#### TABLE 11-7: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP

| SS                          |                      |           |       |       |       |       |       |       |      | Bi   | its  |      |      |      |      |      |       |      |            |

|-----------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|-------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0 | All Resets |

| FB00                        | RPA0R                | 31:16     |       | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | —    | —    | —    | —     | —    | 0000       |

|                             |                      | 15:0      | —     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | —    |      | RPA0 | <3:0> |      | 0000       |

| FB04                        | RPA1R                | 31:16     | —     | —     | -     | —     | —     | _     | —    | —    | _    | —    | —    | —    | —    | —    | —     | —    | 0000       |

| 1 001                       |                      | 15:0      | —     | —     | -     | —     | —     | _     | —    | —    | _    | —    | —    | —    |      | RPA1 | <3:0> |      | 0000       |

| FB08                        | RPA2R                | 31:16     | —     | —     | -     | —     | —     | _     | —    | —    | _    | —    | —    | —    | —    | —    | —     | —    | 0000       |

| 1 000                       | i (i / t <u></u>     | 15:0      | —     | —     | -     | —     | —     | _     | —    | —    | _    | —    | —    | —    |      | RPA2 | <3:0> |      | 0000       |

| FB0C                        | RPA3R                | 31:16     | _     | _     | —     | —     | _     | _     | _    | _    | _    | —    | _    | —    | _    | —    |       | —    | 0000       |

| T BOC                       |                      | 15:0      | _     |       | —     | _     | _     | _     | —    | _    | _    |      | —    | _    |      | RPA3 | <3:0> |      | 0000       |

| FB10                        | RPA4R                | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    |      | _    | _    | _    |      |       | —    | 0000       |

| T D IO                      |                      | 15:0      | —     | —     | —     | —     | _     |       | —    | _    |      | —    | —    | —    |      | RPA4 | <3:0> |      | 0000       |

| FB20                        | RPA8R <sup>(1)</sup> | 31:16     | —     | —     | —     | —     | _     |       | —    | _    |      | —    | —    | —    | _    | —    | —     | —    | 0000       |

| 1 020                       |                      | 15:0      | _     | —     | —     | —     | _     |       | —    | _    |      | —    | —    | —    |      | RPA8 | <3:0> |      | 0000       |

| FB24                        | RPA9R <sup>(1)</sup> | 31:16     | —     | —     | —     | —     | -     |       | _    | -    |      | _    | _    | —    | -    | —    | _     | —    | 0000       |

| 1 D24                       | KFA9K /              | 15:0      | —     | —     | —     | —     | -     |       | _    | -    |      | _    | _    | —    |      | RPA9 | <3:0> |      | 0000       |

| FB2C                        | RPB0R                | 31:16     | _     | _     | —     | —     | _     | -     | _    | _    | -    | —    | _    | —    | _    | _    | _     | —    | 0000       |

| 1 020                       | KF DUK               | 15:0      | _     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | —    |      | RPB0 | <3:0> |      | 0000       |

| FB30                        | RPB1R                | 31:16     | _     | _     | —     | —     |       |       | —    |      |      | —    | —    | —    |      | _    | —     | —    | 0000       |

| FB30                        | REDIR                | 15:0      | _     | _     | —     | —     |       |       | —    |      |      | —    | —    | —    |      | RPB1 | <3:0> |      | 0000       |

| FB34                        | RPB2R                | 31:16     | _     | _     | _     | _     |       |       | _    |      |      | _    | _    | _    |      | _    | _     | —    | 0000       |

| FB34                        | RPBZR                | 15:0      | —     | —     | —     | —     | —     | _     | _    | —    | _    | —    | _    | —    |      | RPB2 | <3:0> |      | 0000       |

| FB38                        | RPB3R                | 31:16     | _     | _     | —     | _     | _     | _     | _    | _    | _    | _    | _    | —    | _    | _    | _     | _    | 0000       |

| FB30                        | RPBJR                | 15:0      | —     | —     | —     | —     | —     | _     | _    | —    | _    | —    | _    | —    |      | RPB3 | <3:0> |      | 0000       |

| <b>FD2C</b>                 |                      | 31:16     | —     | —     | —     | —     | —     | _     | _    | —    | _    | —    | _    | —    | —    | —    | —     | —    | 0000       |

| FB3C                        | RPB4R                | 15:0      | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB4 | <3:0> |      | 0000       |

| ED 40                       |                      | 31:16     |       |       | —     | —     | —     | -     | —    | —    | —    | —    | —    | —    | _    |      |       | —    | 0000       |

| FB40                        | RPB5R                | 15:0      | _     |       | —     |       |       |       |      |      |      |      |      |      |      | RPB5 | <3:0> |      | 0000       |

| 5044                        |                      | 31:16     | _     | —     | _     | —     | —     | _     | _    | _    | _    | —    | _    | —    | _    | _    | _     | —    | 0000       |

| FB44                        | RPB6R <sup>(2)</sup> | 15:0      | _     | —     | _     | —     | _     | _     | _    | _    | _    | —    | _    | —    |      | RPB6 | <3:0> |      | 0000       |

| 50.40                       |                      | 31:16     | _     | —     | _     | —     | _     | _     | _    | _    | _    | —    | _    | —    | _    | _    | _     | —    | 0000       |

| FB48                        | RPB7R                | 15:0      | _     | —     | _     | —     | _     | _     | _    | _    | _    | —    | _    | —    |      | RPB7 | <3:0> |      | 0000       |

DS60001168J-page 138

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register is only available on 44-pin devices. Note 1:

2: This register is only available on PIC32MX1XX devices.

3: This register is only available on 36-pin and 44-pin devices. PIC32MX1XX/2XX 28/36/44-PIN FAMILY

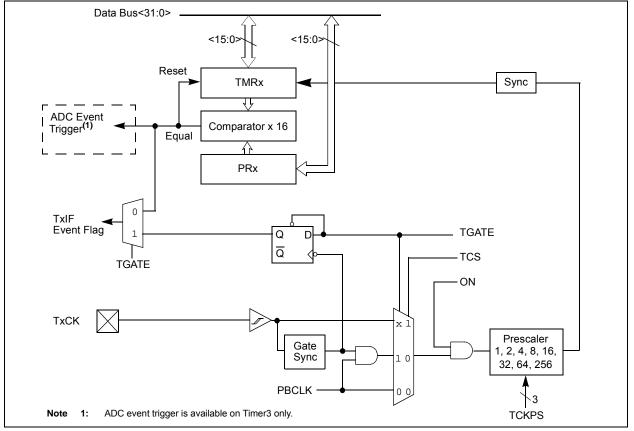

## 13.0 TIMER2/3, TIMER4/5

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features four synchronous 16-bit timers (default) that can operate as a freerunning interval timer for various timing applications and counting external events. The following modes are supported:

- Synchronous internal 16-bit timer

- Synchronous internal 16-bit gated timer

- · Synchronous external 16-bit timer

Two 32-bit synchronous timers are available by combining Timer2 with Timer3 and Timer4 with Timer5. The 32-bit timers can operate in three modes:

- Synchronous internal 32-bit timer

- · Synchronous internal 32-bit gated timer

- Synchronous external 32-bit timer

| Note: | In this chapter, references to registers, |

|-------|-------------------------------------------|

|       | TxCON, TMRx and PRx, use 'x' to           |

|       | represent Timer2 through Timer5 in 16-bit |

|       | modes. In 32-bit modes, 'x' represents    |

|       | Timer2 or Timer4 and 'y' represents       |

|       | Timer3 or Timer5.                         |

### **13.1 Additional Supported Features**

- · Selectable clock prescaler

- Timers operational during CPU idle

- Time base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

- ADC event trigger (Timer3 in 16-bit mode, Timer2/3 in 32-bit mode)

- Fast bit manipulation using CLR, SET and INV registers

Figure 13-1 and Figure 13-2 illustrate block diagrams of Timer2/3 and Timer4/5.

#### FIGURE 13-1: TIMER2-TIMER5 BLOCK DIAGRAM (16-BIT)

#### 15.1 **Input Capture Control Registers**

|                             | TABLE 15-1: INPUT CAPTURE 1-INPUT CAPTURE 5 REGISTER MAP |               |       |       |       |       |       |       |       |        |        |      |      |      |       |      |          |

|-----------------------------|----------------------------------------------------------|---------------|-------|-------|-------|-------|-------|-------|-------|--------|--------|------|------|------|-------|------|----------|

| ess                         |                                                          |               |       |       |       |       |       |       |       | Bi     | ts     |      |      |      |       |      |          |

| Virtual Address<br>(BF80_#) | Register<br>Name                                         | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9  | 24/8   | 23/7   | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1     |

|                             | IC1CON <sup>(1)</sup>                                    | 31:16         |       | _     | —     | —     | —     | —     | _     | —      | —      | —    |      | —    | —     | —    | —        |

| 2000 101                    | 101001                                                   | 15:0          | ON    | —     | SIDL  | —     | —     | —     | FEDGE | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |

| 2010                        | IC1BUF                                                   | 31:16<br>15:0 |       |       |       |       |       |       |       | IC1BUF | <31:0> |      |      |      |       |      |          |

| 2200                        | IC2CON <sup>(1)</sup>                                    | 31:16         |       | —     | _     | —     | —     | —     | —     | —      | _      | —    | _    | —    | _     | —    | —        |

| 2200                        | 1020011                                                  | 15:0          | ON    | —     | SIDL  | —     |       | —     | FEDGE | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |

| 2210                        | IC2BUF                                                   | 31:16<br>15:0 |       |       |       |       |       |       |       | IC2BUF | <31:0> |      |      |      |       |      |          |

| 2400                        | IC3CON <sup>(1)</sup>                                    | 31:16         |       | _     | —     | _     | _     | _     | —     | _      | —      | -    | _    | —    | _     | _    | —        |

| 2400                        | 1030011                                                  | 15:0          | ON    | —     | SIDL  | —     |       | —     | FEDGE | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |

| 2410                        | IC3BUF                                                   | 31:16<br>15:0 |       |       |       |       |       |       |       | IC3BUF | <31:0> |      |      |      |       |      |          |

| 2600                        | IC4CON <sup>(1)</sup>                                    | 31:16         | -     | _     | —     | _     | -     | _     | —     | —      | _      | _    | _    | —    | —     | _    | —        |

| 2000                        | 1040010                                                  | 15:0          | ON    | —     | SIDL  | —     |       | —     | FEDGE | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |

| 2610                        | IC4BUF                                                   | 31:16<br>15:0 |       |       |       |       |       |       |       | IC4BUF | <31:0> |      |      |      |       |      |          |

| 2800                        | IC5CON <sup>(1)</sup>                                    | 31:16         | -     | _     | —     | _     | -     | _     | —     | —      | _      | _    | _    | —    | —     | _    | —        |

| 2000                        | 1030011                                                  | 15:0          | ON    | —     | SIDL  | —     | —     | —     | FEDGE | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |

| 2810                        | IC5BUF                                                   | 31:16<br>15:0 |       |       |       |       |       |       |       | IC5BUF | <31:0> |      |      |      |       |      |          |

#### Т

Legend:

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information. Note 1:

All Resets

0000

0000 xxxx xxxx 0000 0000 xxxx xxxx 0000 0000 xxxx xxxx 0000 0000 xxxx xxxx 0000 0000 xxxx xxxx

16/0

—

# **REGISTER 18-2:** I2CxSTAT: I<sup>2</sup>C STATUS REGISTER (CONTINUED)

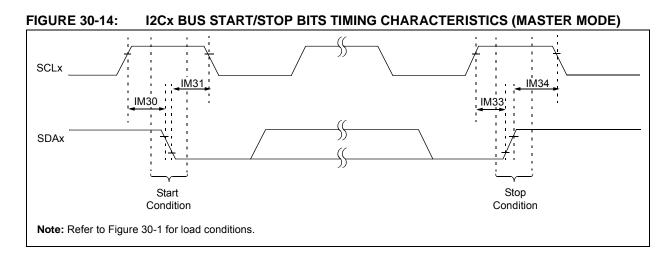

| bit 4 | <b>P:</b> Stop bit<br>1 = Indicates that a Stop bit has been detected last                                                                 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>0 = Stop bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul>         |

| bit 3 | S: Start bit                                                                                                                               |

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul> |

|       | Hardware set or clear when Start, Repeated Start or Stop detected.                                                                         |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                          |

|       | <ul> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave</li> </ul> |

|       | Hardware set or clear after reception of I <sup>2</sup> C device address byte.                                                             |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                        |

|       | 1 = Receive complete, I2CxRCV is full                                                                                                      |

|       | 0 = Receive not complete, I2CxRCV is empty                                                                                                 |

|       | Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.                                       |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                       |

|       | 1 = Transmit in progress, I2CxTRN is full                                                                                                  |

0 = Transmit complete, I2CxTRN is empty

Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0 U-0           |                  | R/W-0            |  |  |  |

| 31:24        |                   | _                 | _                 | _                 | —                 | _                 | _                | ADM_EN           |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | ADDR<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-1              |  |  |  |

| 15:8         | UTXISE            | L<1:0>            | UTXINV            | URXEN             | UTXBRK            | UTXEN             | UTXBF            | TRMT             |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R-1               | R-0               | R-0               | R/W-0            | R-0              |  |  |  |

| 7:0          | URXISE            | L<1:0>            | ADDEN             | RIDLE             | PERR              | FERR              | OERR             | URXDA            |  |  |  |

#### REGISTER 19-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

#### Legend:

| 0                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-25 Unimplemented: Read as '0'

- bit 24 ADM\_EN: Automatic Address Detect Mode Enable bit

- 1 = Automatic Address Detect mode is enabled

- 0 = Automatic Address Detect mode is disabled

- bit 23-16 ADDR<7:0>: Automatic Address Mask bits

When the ADM\_EN bit is '1', this value defines the address character to use for automatic address detection.

- bit 15-14 UTXISEL<1:0>: TX Interrupt Mode Selection bits

- 11 = Reserved, do not use

- 10 = Interrupt is generated and asserted while the transmit buffer is empty

- 01 = Interrupt is generated and asserted when all characters have been transmitted

- 00 = Interrupt is generated and asserted while the transmit buffer contains at least one empty space

#### bit 13 **UTXINV:** Transmit Polarity Inversion bit

If IrDA mode is disabled (i.e., IREN (UxMODE<12>) is '0'):

- 1 = UxTX Idle state is '0'

- 0 = UxTX Idle state is '1'

If IrDA mode is enabled (i.e., IREN (UxMODE<12>) is '1'):

- 1 = IrDA encoded UxTX Idle state is '1'

- 0 = IrDA encoded UxTX Idle state is '0'

- bit 12 URXEN: Receiver Enable bit

- 1 = UARTx receiver is enabled. UxRX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx receiver is disabled. UxRX pin is ignored by the UARTx module. UxRX pin is controlled by port.

#### bit 11 UTXBRK: Transmit Break bit

- 1 = Send Break on next transmission. Start bit followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

- 0 = Break transmission is disabled or completed

- bit 10 UTXEN: Transmit Enable bit

- 1 = UARTx transmitter is enabled. UxTX pin is controlled by UARTx (if ON = 1).

- 0 = UARTx transmitter is disabled. Any pending transmission is aborted and buffer is reset. UxTX pin is controlled by port.

- bit 9 **UTXBF:** Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

- bit 8 TRMT: Transmit Shift Register is Empty bit (read-only)

- 1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed)

- 0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   |                   | _                 | _                 | _                 | -                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | _                 | _                 | -                 | -                 | _                 | _                | —                |

| 45.0         | R-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 15:8         | BUSY              | IRQM              | <1:0>             | INCM              | <1:0>             | _                 | MODE             | <1:0>            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | WAITB             | <1:0> <b>(1)</b>  |                   | WAITM             | WAITE<1:0>(1)     |                   |                  |                  |

#### REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER

#### Legend:

| 3                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **BUSY:** Busy bit (Master mode only)

- 1 = Port is busy

- 0 = Port is not busy

#### bit 14-13 IRQM<1:0>: Interrupt Request Mode bits

- 11 = Reserved, do not use

- 10 = Interrupt generated when Read Buffer 3 is read or Write Buffer 3 is written (Buffered PSP mode) or on a read or write operation when PMA<1:0> =11 (Addressable Slave mode only)

- 01 = Interrupt generated at the end of the read/write cycle

- 00 = No Interrupt generated

#### bit 12-11 INCM<1:0>: Increment Mode bits

- 11 = Slave mode read and write buffers auto-increment (MODE<1:0> = 00 only)

- 10 = Decrement ADDR<10:2> and ADDR<14> by 1 every read/write cycle<sup>(2)</sup>

- 01 = Increment ADDR<10:2> and ADDR<14> by 1 every read/write cycle<sup>(2)</sup>

- 00 = No increment or decrement of address

- bit 10 Unimplemented: Read as '0'

- bit 9-8 MODE<1:0>: Parallel Port Mode Select bits

- 11 = Master mode 1 (PMCS1, PMRD/PMWR, PMENB, PMA<x:0>, and PMD<7:0>)

- 10 = Master mode 2 (PMCS1, PMRD, PMWR, PMA<x:0>, and PMD<7:0>)

- 01 = Enhanced Slave mode, control signals (PMRD, PMWR, PMCS1, PMD<7:0>, and PMA<1:0>)

- 00 = Legacy Parallel Slave Port, control signals (PMRD, PMWR, PMCS1, and PMD<7:0>)

- bit 7-6 WAITB<1:0>: Data Setup to Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Data wait of 4 TPB; multiplexed address phase of 4 TPB

- 10 = Data wait of 3 TPB; multiplexed address phase of 3 TPB

- 01 = Data wait of 2 TPB; multiplexed address phase of 2 TPB

- 00 = Data wait of 1 TPB; multiplexed address phase of 1 TPB (default)

#### bit 5-2 WAITM<3:0>: Data Read/Write Strobe Wait States bits<sup>(1)</sup>

- 1111 = Wait of 16 Трв •

- . 0001 = Wait of 2 Трв 0000 = Wait of 1 Трв (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bit A14 is not subject to auto-increment/decrement if configured as Chip Select CS1.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### REGISTER 21-2: RTCALRM: RTC ALARM CONTROL REGISTER (CONTINUED)

bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits<sup>(2)</sup> 11111111 = Alarm will trigger 256 times

> 00000000 = Alarm will trigger one time The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1.

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

Note: This register is reset only on a Power-on Reset (POR).

### 23.1 Comparator Control Registers

#### TABLE 23-1: COMPARATOR REGISTER MAP

| ess                         |                                 | 0         | Bits  |       |       |       |       |       |      |      |      |        |      |      |      |       |       |       |           |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------|------|------|------|-------|-------|-------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2  | 17/1  | 16/0  | All Reset |

| 4000                        | CM1CON                          | 31:16     | _     | —     | _     | _     | -     | _     |      | -    | —    | —      | -    | —    | —    | —     | _     | _     | 0000      |

| A000                        | CIVITCON                        | 15:0      | ON    | COE   | CPOL  | _     | —     | _     | —    | COUT | EVPO | L<1:0> | —    | CREF | _    | —     | CCH   | <1:0> | 00C3      |

| A010                        | CM2CON                          | 31:16     | —     | -     |       |       | -     |       | -    | -    | —    | —      | -    | —    | —    | —     |       | —     | 0000      |

| AUTO                        | CIVIZCON                        | 15:0      | ON    | COE   | CPOL  | _     |       | _     |      | COUT | EVPO | L<1:0> |      | CREF | _    | _     | CCH   | <1:0> | 00C3      |

| A020                        | CM3CON                          | 31:16     | _     | _     | _     | _     |       | _     |      |      | _    | _      |      | _    | _    | _     | _     | _     | 0000      |

| A020                        | CIVISCON                        | 15:0      | ON    | COE   | CPOL  | _     | —     | _     | —    | COUT | EVPO | L<1:0> | —    | CREF | _    | —     | CCH   | <1:0> | 00C3      |

| A060                        | CMSTAT                          | 31:16     | —     | _     | _     | _     | -     | _     | _    | -    | —    | —      | _    | —    | _    | —     | _     | —     | 0000      |

| 7000                        | CIVISTAI                        | 15:0      | _     | _     | SIDL  | _     |       | _     |      |      | -    | _      |      | _    |      | C3OUT | C2OUT | C10UT | 0000      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

# 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

### 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.