Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                    |                                                                                |

|---------------------------|--------------------------------------------------------------------------------|

| roduct Status             | Active                                                                         |

|                           |                                                                                |

| ore Processor             | MIPS32® M4K™                                                                   |

| ore Size                  | 32-Bit Single-Core                                                             |

| peed                      | 40MHz                                                                          |

| onnectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| eripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                |

| umber of I/O              | 21                                                                             |

| rogram Memory Size        | 256KB (256K x 8)                                                               |

| rogram Memory Type        | FLASH                                                                          |

| EPROM Size                | -                                                                              |

| AM Size                   | 16K x 8                                                                        |

| oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| ata Converters            | A/D 10x10b                                                                     |

| scillator Type            | Internal                                                                       |

| perating Temperature      | -40°C ~ 105°C (TA)                                                             |

| ounting Type              | Surface Mount                                                                  |

| ackage / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| upplier Device Package    | 28-SSOP                                                                        |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f256b-v-ss |

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32 $^{\circledR}$  architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then

adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

# 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e, is also available by accessing the CP0 registers, listed in Table 3-2.

TABLE 3-2: COPROCESSOR 0 REGISTERS

| Register<br>Number | Register<br>Name        | Function                                                                 |

|--------------------|-------------------------|--------------------------------------------------------------------------|

| 0-6                | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 7                  | HWREna                  | Enables access via the RDHWR instruction to selected hardware registers. |

| 8                  | BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.       |

| 9                  | Count <sup>(1)</sup>    | Processor cycle count.                                                   |

| 10                 | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 11                 | Compare <sup>(1)</sup>  | Timer interrupt control.                                                 |

| 12                 | Status <sup>(1)</sup>   | Processor status and control.                                            |

| 12                 | IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                     |

| 12                 | SRSCtl <sup>(1)</sup>   | Shadow register set status and control.                                  |

| 12                 | SRSMap <sup>(1)</sup>   | Provides mapping from vectored interrupt to a shadow set.                |

| 13                 | Cause <sup>(1)</sup>    | Cause of last general exception.                                         |

| 14                 | EPC <sup>(1)</sup>      | Program counter at last exception.                                       |

| 15                 | PRId                    | Processor identification and revision.                                   |

| 15                 | EBASE                   | Exception vector base register.                                          |

| 16                 | Config                  | Configuration register.                                                  |

| 16                 | Config1                 | Configuration Register 1.                                                |

| 16                 | Config2                 | Configuration Register 2.                                                |

| 16                 | Config3                 | Configuration Register 3.                                                |

| 17-22              | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status.                                      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                 |

| 25-29              | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error.                                           |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                       |

Note 1: Registers used in exception processing.

2: Registers used during debug.

| PIC32M | X1XX/2X | X 28/36 | 5/44-PIN | IFAMIL | . <b>Y</b> |  |

|--------|---------|---------|----------|--------|------------|--|

| NOTES: |         |         |          |        |            |  |

|        |         |         |          |        |            |  |

|        |         |         |          |        |            |  |

|        |         |         |          |        |            |  |

|        |         |         |          |        |            |  |

|        |         |         |          |        |            |  |

|        |         |         |          |        |            |  |

|        |         |         |          |        |            |  |

|        |         |         |          |        |            |  |

|        |         |         |          |        |            |  |

|        |         |         |          |        |            |  |

|        |         |         |          |        |            |  |

|        |         |         |          |        |            |  |

|        |         |         |          |        |            |  |

|        |         |         |          |        |            |  |

|        |         |         |          |        |            |  |

#### REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|---------------------|-------------------|-----------------------|------------------|--|--|--|--|--|

| 04.04        | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0                 | R/W-0            |  |  |  |  |  |

| 31:24        | _                 |                   |                   | R                 | ODIV<14:8>          | 1,3)              |                       |                  |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0                 | R/W-0            |  |  |  |  |  |

| 23:16        | RODIV<7:0>(1,3)   |                   |                   |                   |                     |                   |                       |                  |  |  |  |  |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0               | U-0               | R/W-0, HC             | R-0, HS, HC      |  |  |  |  |  |

| 15:8         | ON                |                   | SIDL              | OE                | RSLP <sup>(2)</sup> |                   | DIVSWEN               | ACTIVE           |  |  |  |  |  |

|              | U-0               | U-0               | U-0               | U-0               | R/W-0               | R/W-0             | R/W-0                 | R/W-0            |  |  |  |  |  |

| 7:0          | _                 | _                 |                   | -                 |                     | ROSEL             | .<3:0> <sup>(1)</sup> |                  |  |  |  |  |  |

**Legend:** HC = Hardware Clearable HS = Hardware Settable

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 Unimplemented: Read as '0'

bit 30-16 RODIV<14:0> Reference Clock Divider bits(1,3)

The value selects the reference clock divider bits. See Figure 8-1 for information.

bit 15 **ON:** Output Enable bit

1 = Reference Oscillator module is enabled

0 = Reference Oscillator module is disabled

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Peripheral Stop in Idle Mode bit

1 = Discontinue module operation when the device enters Idle mode

0 = Continue module operation when the device enters Idle mode

bit 12 **OE:** Reference Clock Output Enable bit

1 = Reference clock is driven out on REFCLKO pin

0 = Reference clock is not driven out on REFCLKO pin

bit 11 RSLP: Reference Oscillator Module Run in Sleep bit (2)

1 = Reference Oscillator module output continues to run in Sleep

0 = Reference Oscillator module output is disabled in Sleep

bit 10 Unimplemented: Read as '0'

bit 9 **DIVSWEN:** Divider Switch Enable bit

1 = Divider switch is in progress

0 = Divider switch is complete

bit 8 ACTIVE: Reference Clock Request Status bit

1 = Reference clock request is active

0 = Reference clock request is not active

bit 7-4 Unimplemented: Read as '0'

Note 1: The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

2: This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

### 9.1 DMA Control Registers

### TABLE 9-1: DMA GLOBAL REGISTER MAP

| ess                         |                                 |           |       |       |       |         |         |       |      | Bi       | ts      |      |      |      |      |      |           |      | ω,         |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|---------|---------|-------|------|----------|---------|------|------|------|------|------|-----------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12   | 27/11   | 26/10 | 25/9 | 24/8     | 23/7    | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1      | 16/0 | All Resets |

| 2000                        | DMACON                          | 31:16     | _     | _     | _     | _       | _       | _     | _    | _        | _       | _    | _    | _    | _    | _    | _         | _    | 0000       |

| 3000                        | DIVIACON                        | 15:0      | ON    | -     | _     | SUSPEND | DMABUSY |       | _    | _        | _       | _    | _    | -    | -    | _    | _         | _    | 0000       |

| 3010                        | DMASTAT                         | 31:16     | _     |       | _     | _       | _       | _     | I    | I        | I       | _    | _    |      |      | I    | _         |      | 0000       |

| 3010                        | DIVIASTAT                       | 15:0      | _     | ı     | 1     | _       | _       |       | I    | I        | I       | _    |      | I    | RDWR | DI   | MACH<2:0> | (2)  | 0000       |

| 3020                        | DMAADDR                         | 31:16     |       |       |       |         |         |       |      | DMAADD   | D<31·0> |      |      |      |      |      |           |      | 0000       |

| 3020                        | DIVIDADDIX                      | 15:0      |       |       |       |         |         |       |      | DIVIANDE | 11.07   |      |      |      |      |      |           |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information

#### TABLE 9-2: DMA CRC REGISTER MAP

| ess                         |                                 |           |       |               |               |                |       |           |      | Ві     | ts        |        |        |      |      |      |          |      |            |

|-----------------------------|---------------------------------|-----------|-------|---------------|---------------|----------------|-------|-----------|------|--------|-----------|--------|--------|------|------|------|----------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14         | 29/13         | 28/12          | 27/11 | 26/10     | 25/9 | 24/8   | 23/7      | 22/6   | 21/5   | 20/4 | 19/3 | 18/2 | 17/1     | 16/0 | All Resets |

| 2020                        | DCRCCON                         | 31:16     | _     | _             | BYTO          | <1:0>          | WBO   | _         | _    | BITO   | _         | _      | _      | _    | _    | _    | _        | _    | 0000       |

| 3030                        | DCRCCON                         | 15:0      | _     | _             | _             |                |       | PLEN<4:0> |      |        | CRCEN     | CRCAPP | CRCTYP | _    | _    | C    | RCCH<2:0 | >    | 0000       |

| 2040                        | DCRCDATA                        | 31:16     |       |               |               |                |       |           |      | DCBCDA | TA ~21:0> |        |        |      |      |      |          |      | 0000       |

| 3040                        | DCKCDAIA                        | 15:0      |       |               |               | DCRCDATA<31:0> |       |           |      |        |           |        |        |      |      | 0000 |          |      |            |

| 3050                        | DCRCXOR                         | 31:16     |       |               | DCDCYOD<31:0> |                |       |           |      |        |           |        |        |      | 0000 |      |          |      |            |

| 3030                        | DCKCXOK                         | 15:0      |       | DCRCXOR<31:0> |               |                |       |           |      |        |           |        |        |      |      |      |          |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| TABLE 9-3: DMA CHANNELS 0-3 REGISTER MAP (CONTINUE) |

|-----------------------------------------------------|

|-----------------------------------------------------|

| sse                         |                                 |               |        |       |       |       | •      |       |      | Bi       | ts           |        |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|---------------|--------|-------|-------|-------|--------|-------|------|----------|--------------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8     | 23/7         | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

|                             | DCH2CPTR                        | 31:16         | _      | _     | _     | _     | ı      | _     |      | _        | ı            | ı      | _      | _      | I      | ı      | _      | ı      | 0000       |

| 3200                        | DCH2CFTR                        | 15:0          |        |       |       |       |        |       |      | CHCPT    | R<15:0>      |        |        |        |        |        |        |        | 0000       |

| 2200                        | DCH2DAT                         | 31:16         | _      | _     | _     | _     | ı      | _     | -    | _        | -            | ı      | _      | _      | ı      | ı      | _      | ı      | 0000       |

| 3290                        | DCHZDAI                         | 15:0          | _      |       | _     | -     | 1      | _     | -    | 1        |              |        |        | CHPDA  | T<7:0> |        |        |        | 0000       |

| 2240                        | DCH3CON                         | 31:16         | _      | _     | _     | _     | _      | _     | _    | _        | _            | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 32AU                        | DCH3CON                         | 15:0          | CHBUSY | _     | _     | _     | -      | _     | _    | CHCHNS   | CHEN         | CHAED  | CHCHN  | CHAEN  | -      | CHEDET | CHPR   | I<1:0> | 0000       |

| 32B0                        | DCH3ECON                        | 31:16         | _      | _     | _     | _     | _      | _     | _    | _        |              |        |        | CHAIR  | Q<7:0> |        |        |        | 00FF       |

| 3200                        | DOI IOLOON                      | 15:0          |        |       |       | CHSIR | Q<7:0> |       |      |          | CFORCE       | CABORT | PATEN  | SIRQEN | AIRQEN |        | _      |        | FF00       |

| 32C0                        | DCH3INT                         | 31:16         | _      | _     | _     | _     | ı      | _     | _    | _        | CHSDIE       | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE |            |

| 0200                        | DOTIONAL                        | 15:0          | _      | _     | _     | _     | _      | _     | _    | _        | CHSDIF       | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF |            |

| 32D0                        | DCH3SSA                         | 31:16         |        |       |       |       |        |       |      | CHSSA    | <31:0>       |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 15:0          |        |       |       |       |        |       |      |          |              |        |        |        |        |        |        |        | 0000       |

| 32E0                        | DCH3DSA                         | 31:16<br>15:0 |        |       |       |       |        |       |      | CHDSA    | <31:0>       |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16         |        |       |       |       |        |       |      |          |              |        |        |        |        |        |        |        | 0000       |

| 32F0                        | DCH3SSIZ                        | 15:0          | _      | _     | _     | _     |        | _     |      | CHSSIZ   | ~<br>?<15:0> |        | _      |        |        |        | _      |        | 0000       |

|                             |                                 | 31:16         | _      | _     | _     | _     | _      | _     | _    | —        |              | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3300                        | DCH3DSIZ                        | 15:0          |        |       |       |       |        |       |      | CHDSIZ   | Z<15:0>      |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16         | _      | _     | _     | _     | _      | _     | _    | _        | _            | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3310                        | DCH3SPTR                        | 15:0          |        |       |       |       |        |       |      | CHSPT    | R<15:0>      |        |        |        |        |        |        |        | 0000       |

| 2000                        | DOLLODDED                       | 31:16         | _      | _     | _     | _     | _      | _     | _    | _        | _            | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3320                        | DCH3DPTR                        | 15:0          |        |       |       |       |        |       |      | CHDPTI   | R<15:0>      |        |        |        |        |        |        |        | 0000       |

| 2220                        | DCH3CSIZ                        | 31:16         | _      | _     | _     | _     | _      | _     | _    | _        | _            | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3330                        | DCH3C3IZ                        | 15:0          |        |       |       |       |        |       |      | CHCSIZ   | Z<15:0>      |        |        |        |        |        |        |        | 0000       |

| 3340                        | DCH3CPTR                        | 31:16         |        | _     | _     | _     | _      | _     | _    |          | _            | _      | _      | _      | _      | _      | _      |        | 0000       |

| JJ-0                        | POLIDOL IK                      | 15:0          |        |       |       |       |        |       |      | CHCPTI   | R<15:0>      |        |        |        |        |        |        |        | 0000       |

| 3350                        | DCH3DAT                         | 31:16         | _      | _     | _     | _     | -      | _     | _    | _        | 1            | -      | _      | _      | -      | -      | _      | -      | 0000       |

| 0000                        | DONODAI                         | 15:0          | — I    | _     | _     | _     |        | _     |      | <u> </u> |              |        |        | CHPDA  | T<7:0> |        |        |        | 0000       |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information. Note 1:

#### REGISTER 9-18: DCHxDAT: DMA CHANNEL 'x' PATTERN DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | -                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |  |  |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 15:8         | -                 | _                 | _                 | -                 | _                 | _                 | -                | _                |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          | CHPDAT<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-0 CHPDAT<7:0>: Channel Data Register bits

Pattern Terminate mode:

Data to be matched must be stored in this register to allow a "terminate on match".

All other modes: Unused.

#### REGISTER 12-1: T1CON: TYPE A TIMER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | -                 | _                 | -                 | -                | _                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | U-0              | U-0              |

| 15.6         | ON <sup>(1)</sup> | _                 | SIDL              | TWDIS             | TWIP              | _                 | _                | _                |

| 7:0          | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7:0          | TGATE             | _                 | TCKPS             | S<1:0>            | _                 | TSYNC             | TCS              | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Timer On bit<sup>(1)</sup>

1 = Timer is enabled

0 = Timer is disabled

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

${\tt 1}$  = Discontinue module operation when the device enters Idle mode

0 = Continue module operation when the device enters Idle mode

bit 12 **TWDIS:** Asynchronous Timer Write Disable bit

1 = Writes to Timer1 are ignored until pending write operation completes

0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)

bit 11 TWIP: Asynchronous Timer Write in Progress bit

In Asynchronous Timer mode:

1 = Asynchronous write to the Timer1 register in progress

0 = Asynchronous write to Timer1 register is complete

In Synchronous Timer mode:

This bit is read as '0'.

bit 10-8 Unimplemented: Read as '0'

bit 7 TGATE: Timer Gated Time Accumulation Enable bit

$\frac{\text{When TCS} = 1:}{\text{This bit is ignored.}}$

When TCS = 0:

1 = Gated time accumulation is enabled

0 = Gated time accumulation is disabled

bit 6 **Unimplemented:** Read as '0'

bit 5-4 TCKPS<1:0>: Timer Input Clock Prescale Select bits

11 = 1:256 prescale value

10 = 1:64 prescale value

01 = 1:8 prescale value

00 = 1:1 prescale value

**Note 1:** When using 1:1 PBCmLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

### REGISTER 18-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER (CONTINUED)

- bit 4 **P:** Stop bit

- 1 = Indicates that a Stop bit has been detected last

- 0 = Stop bit was not detected last

Hardware set or clear when Start, Repeated Start or Stop detected.

- bit 3 S: Start bit

- 1 = Indicates that a Start (or Repeated Start) bit has been detected last

- 0 = Start bit was not detected last

Hardware set or clear when Start, Repeated Start or Stop detected.

- bit 2  $R_W$ : Read/Write Information bit (when operating as  $I^2C$  slave)

- 1 = Read indicates data transfer is output from slave

- 0 = Write indicates data transfer is input to slave

Hardware set or clear after reception of I<sup>2</sup>C device address byte.

- bit 1 RBF: Receive Buffer Full Status bit

- 1 = Receive complete, I2CxRCV is full

- 0 = Receive not complete, I2CxRCV is empty

Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.

- bit 0 TBF: Transmit Buffer Full Status bit

- 1 = Transmit in progress, I2CxTRN is full

- 0 = Transmit complete, I2CxTRN is empty

Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.

#### REGISTER 19-2: UXSTA: UARTX STATUS AND CONTROL REGISTER (CONTINUED)

- bit 7-6 URXISEL<1:0>: Receive Interrupt Mode Selection bit

- 11 = Reserved; do not use

- 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (i.e., has 6 or more data characters)

- 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (i.e., has 4 or more data characters)

- 00 = Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character)

- bit 5 **ADDEN:** Address Character Detect bit (bit 8 of received data = 1)

- 1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect.

- 0 = Address Detect mode is disabled

- bit 4 RIDLE: Receiver Idle bit (read-only)

- 1 = Receiver is Idle

- 0 = Data is being received

- bit 3 **PERR:** Parity Error Status bit (read-only)

- 1 = Parity error has been detected for the current character

- 0 = Parity error has not been detected

- bit 2 **FERR:** Framing Error Status bit (read-only)

- 1 = Framing error has been detected for the current character

- 0 = Framing error has not been detected

- bit 1 **OERR:** Receive Buffer Overrun Error Status bit.

This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and the RSR to an empty state.

- 1 = Receive buffer has overflowed

- 0 = Receive buffer has not overflowed

- bit 0 URXDA: Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

#### REGISTER 20-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6                           | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|---------------------------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0                                         | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | _                                           | _                 | _                 | _                 | _                 | _                | _                |  |

| 00.40        | U-0               | U-0                                         | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | _                 | _                                           | _                 | _                 | _                 | _                 | _                | _                |  |

|              | U-0               | R/W-0                                       | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | _                 | CS1 <sup>(1)</sup><br>ADDR14 <sup>(2)</sup> | _                 | _                 | _                 | ADDR<10:8>        |                  |                  |  |

| 7:0          | R/W-0             | R/W-0                                       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              | ADDR<7:0>         |                                             |                   |                   |                   |                   |                  |                  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-15 Unimplemented: Read as '0'

bit 14 **CS1**: Chip Select 1 bit<sup>(1)</sup>

1 = Chip Select 1 is active 0 = Chip Select 1 is inactive

bit 14 ADDR<14>: Destination Address bit 14<sup>(2)</sup>

bit 13-11 Unimplemented: Read as '0'

bit 10-0 ADDR<10:0>: Destination Address bits

**Note 1:** When the CSF<1:0> bits (PMCON<7:6>) = 10.

**2:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

#### REGISTER 21-4: RTCDATE: RTC DATE VALUE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31:24        |                   | YEAR1             | 0<3:0>            |                   |                   | YEAR0             | 1<3:0>           |                  |

| 22.40        | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16        | _                 | _                 | _                 | MONTH10           |                   | MONTH             | 01<3:0>          |                  |

| 45.0         | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         | _                 | _                 | DAY10             | )<1:0>            |                   | DAY01             | <3:0>            |                  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x            | R/W-x            |

| 7:0          | _                 | _                 | _                 | _                 | _                 | ٧                 | VDAY01<2:0       | >                |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10s place digit; contains a value from 0 to 9

bit 27-24 YEAR01<3:0>: Binary-Coded Decimal Value of Years bits, 1s place digit; contains a value from 0 to 9

bit 23-21 Unimplemented: Read as '0'

bit 20 MONTH10: Binary-Coded Decimal Value of Months bits, 10s place digit; contains a value of 0 or 1

bit 19-16 MONTH01<3:0>: Binary-Coded Decimal Value of Months bits, 1s place digit; contains a value from 0 to 9

bit 15-14 Unimplemented: Read as '0'

bit 13-12 DAY10<1:0>: Binary-Coded Decimal Value of Days bits, 10s place digit; contains a value of 0 to 3

bit 11-8 DAY01<3:0>: Binary-Coded Decimal Value of Days bits, 1s place digit; contains a value from 0 to 9

bit 7-3 Unimplemented: Read as '0'

bit 2-0 WDAY01<2:0>: Binary-Coded Decimal Value of Weekdays bits; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

#### REGISTER 21-5: ALRMTIME: ALARM TIME VALUE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31.24        | 31:24             |                   | HR10<1:0>         |                   | HR01<3:0>         |                   |                  |                  |

| 22.40        | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16        | _                 |                   | MIN10<2:0>        |                   | MIN01<3:0>        |                   |                  |                  |

| 45.0         | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         | _                 | SEC10<2:0>        |                   |                   | SEC01<3:0>        |                   |                  |                  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary Coded Decimal value of hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary Coded Decimal value of hours bits, 1s place digit; contains a value from 0 to 9

bit 23 Unimplemented: Read as '0'

bit 22-20 MIN10<2:0>: Binary Coded Decimal value of minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary Coded Decimal value of minutes bits, 1s place digit; contains a value from 0 to 9

bit 15 Unimplemented: Read as '0'

bit 14-12 SEC10<2:0>: Binary Coded Decimal value of seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary Coded Decimal value of seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 22-5: AD1CSSL: ADC INPUT SCAN SELECT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 | _                 | _                 |                   |                   | _                | _                |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | _                 | _                 | -                 | _                 | -                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | CSSL15            | CSSL14            | CSSL13            | CSSL12            | CSSL11            | CSSL10            | CSSL9            | CSSL8            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CSSL7             | CSSL6             | CSSL5             | CSSL4             | CSSL3             | CSSL2             | CSSL1            | CSSL0            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CSSL<15:0>: ADC Input Pin Scan Selection bits<sup>(1,2)</sup>

1 = Select ANx for input scan0 = Skip ANx for input scan

**Note 1:** CSSL = ANx, where 'x' = 0-12; CSSL13 selects CTMU input for scan; CSSL14 selects IVREF for scan; CSSL15 selects VSS for scan.

2: On devices with less than 13 analog inputs, all CSSLx bits can be selected; however, inputs selected for scan without a corresponding input on the device will convert to VREFL.

#### REGISTER 24-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | _                 | _                 | _                 | -                 |                   | _                 | _                | _                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | _                 | _                 | _                 | -                 |                   |                   | _                | _                |  |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         | ON <sup>(1)</sup> | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | _                 | CVROE             | CVRR              | CVRSS             | CVR<3:0>          |                   |                  |                  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Comparator Voltage Reference On bit<sup>(1)</sup>

1 = Module is enabled

Setting this bit does not affect other bits in the register.

0 = Module is disabled and does not consume current.Clearing this bit does not affect the other bits in the register.

bit 14-7 Unimplemented: Read as '0'

bit 6 CVROE: CVREFOUT Enable bit

1 = Voltage level is output on CVREFOUT pin

0 = Voltage level is disconnected from CVREFOUT pin

bit 5 CVRR: CVREF Range Selection bit

1 = 0 to 0.67 CVRSRC, with CVRSRC/24 step size

0 = 0.25 CVRSRC to 0.75 CVRSRC, with CVRSRC/32 step size

bit 4 CVRSS: CVREF Source Selection bit

1 = Comparator voltage reference source, CVRSRC = (VREF+) - (VREF-)

0 = Comparator voltage reference source, CVRSRC = AVDD - AVSS

bit 3-0 **CVR<3:0>:** CVREF Value Selection  $0 \le CVR < 3:0 > \le 15$  bits

When CVRR = 1:

CVREF = (CVR<3:0>/24) • (CVRSRC)

When CVRR = 0:

CVREF = 1/4 • (CVRSRC) + (CVR<3:0>/32) • (CVRSRC)

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| OTES: | PIC32MX1XX/ | ZXX 28/3 | 6/44-PIN | FAMILY |  |

|-------|-------------|----------|----------|--------|--|

|       | NOTES:      |          |          |        |  |

|       |             |          |          |        |  |

|       |             |          |          |        |  |

|       |             |          |          |        |  |

|       |             |          |          |        |  |

|       |             |          |          |        |  |

|       |             |          |          |        |  |

|       |             |          |          |        |  |

|       |             |          |          |        |  |

|       |             |          |          |        |  |

|       |             |          |          |        |  |

|       |             |          |          |        |  |

|       |             |          |          |        |  |

|       |             |          |          |        |  |

|       |             |          |          |        |  |

|       |             |          |          |        |  |

|       |             |          |          |        |  |

|       |             |          |          |        |  |

|       |             |          |          |        |  |

|       |             |          |          |        |  |

|       |             |          |          |        |  |

|       |             |          |          |        |  |

TABLE 30-32: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHA        | RACTER  | іѕтісѕ                   |                        | Standard Operatin<br>(unless otherwise<br>Operating tempera | e stated)<br>ature -40 | O°C ≤ TA ≤ | SV to 3.6V<br>= +85°C for Industrial<br>= +105°C for V-temp |

|---------------|---------|--------------------------|------------------------|-------------------------------------------------------------|------------------------|------------|-------------------------------------------------------------|

| Param.<br>No. | Symbol  | Charact                  | eristics               | Min. <sup>(1)</sup>                                         | Max.                   | Units      | Conditions                                                  |

| IM10          | TLO:SCL | Clock Low Time           | 100 kHz mode           | TPB * (BRG + 2)                                             | _                      | μS         | _                                                           |

|               |         |                          | 400 kHz mode           | Трв * (BRG + 2)                                             | _                      | μS         | _                                                           |

|               |         |                          | 1 MHz mode<br>(Note 2) | Трв * (BRG + 2)                                             | _                      | μS         | _                                                           |

| IM11          | THI:SCL | Clock High Time          | 100 kHz mode           | Трв * (BRG + 2)                                             | _                      | μS         | _                                                           |

|               |         |                          | 400 kHz mode           | Трв * (BRG + 2)                                             | _                      | μS         | _                                                           |

|               |         |                          | 1 MHz mode<br>(Note 2) | Трв * (BRG + 2)                                             | _                      | μS         | _                                                           |

| IM20          | TF:SCL  | SDAx and SCLx            | 100 kHz mode           | _                                                           | 300                    | ns         | CB is specified to be                                       |

|               |         | Fall Time                | 400 kHz mode           | 20 + 0.1 Св                                                 | 300                    | ns         | from 10 to 400 pF                                           |

|               |         |                          | 1 MHz mode<br>(Note 2) | _                                                           | 100                    | ns         |                                                             |

| IM21          | TR:SCL  | SDAx and SCLx            | 100 kHz mode           | _                                                           | 1000                   | ns         | CB is specified to be                                       |

|               |         | Rise Time                | 400 kHz mode           | 20 + 0.1 CB                                                 | 300                    | ns         | from 10 to 400 pF                                           |

|               |         |                          | 1 MHz mode<br>(Note 2) | _                                                           | 300                    | ns         |                                                             |

| IM25          | TSU:DAT | Data Input<br>Setup Time | 100 kHz mode           | 250                                                         |                        | ns         | _                                                           |

|               |         |                          | 400 kHz mode           | 100                                                         |                        | ns         |                                                             |

|               |         |                          | 1 MHz mode<br>(Note 2) | 100                                                         | _                      | ns         |                                                             |

| IM26          | THD:DAT | Data Input               | 100 kHz mode           | 0                                                           |                        | μS         | _                                                           |

|               |         | Hold Time                | 400 kHz mode           | 0                                                           | 0.9                    | μS         |                                                             |

|               |         |                          | 1 MHz mode<br>(Note 2) | 0                                                           | 0.3                    | μS         |                                                             |

| IM30          | Tsu:sta | Start Condition          | 100 kHz mode           | Трв * (BRG + 2)                                             | _                      | μS         | Only relevant for                                           |

|               |         | Setup Time               | 400 kHz mode           | Трв * (BRG + 2)                                             | _                      | μS         | Repeated Start condition                                    |

|               |         |                          | 1 MHz mode<br>(Note 2) | Трв * (BRG + 2)                                             | _                      | μS         | Condition                                                   |

| IM31          | THD:STA | Start Condition          | 100 kHz mode           | Трв * (BRG + 2)                                             | _                      | μS         | After this period, the                                      |

|               |         | Hold Time                | 400 kHz mode           | Трв * (BRG + 2)                                             | _                      | μS         | first clock pulse is                                        |

|               |         |                          | 1 MHz mode<br>(Note 2) | Трв * (BRG + 2)                                             | _                      | μS         | generated                                                   |

| IM33 Tsu:st   | Tsu:sto | Stop Condition           | 100 kHz mode           | Трв * (BRG + 2)                                             | _                      | μS         |                                                             |

|               |         | Setup Time               | 400 kHz mode           | Трв * (BRG + 2)                                             | _                      | μS         |                                                             |

|               |         |                          | 1 MHz mode (Note 2)    | Трв * (BRG + 2)                                             | _                      | μS         |                                                             |

| IM34          | THD:STO | Stop Condition           | 100 kHz mode           | Трв * (BRG + 2)                                             | _                      | ns         | _                                                           |

|               |         | Hold Time                | 400 kHz mode           | TPB * (BRG + 2)                                             | _                      | ns         |                                                             |

|               |         |                          | 1 MHz mode<br>(Note 2) | Трв * (BRG + 2)                                             | _                      | ns         |                                                             |

**Note 1:** BRG is the value of the I<sup>2</sup>C Baud Rate Generator.

<sup>2:</sup> Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**<sup>3:</sup>** The typical value for this parameter is 104 ns.

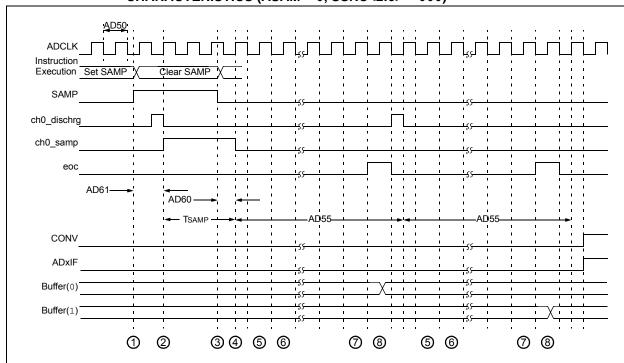

FIGURE 30-18: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000)

- 1 Software sets ADxCON. SAMP to start sampling.

- 2 Sampling starts after discharge period. TSAMP is described in Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104) in the "PIC32 Family Reference Manual".

- (3) Software clears ADxCON. SAMP to start conversion.

- 4 Sampling ends, conversion sequence starts.

- (5) Convert bit 9.

- 6 Convert bit 8.

- 7 Convert bit 0.

- (8) One TAD for end of conversion.

**TABLE 30-41: CTMU CURRENT SOURCE SPECIFICATIONS**

| DC CHARACTERISTICS |                         |                                                    | (unless              | otherwis | e stated)<br>ature -4 | 0°C ≤ T/ | ee Note 3):2.3V to 3.6V<br>A ≤ +85°C for Industrial<br>≤ +105°C for V-temp |  |

|--------------------|-------------------------|----------------------------------------------------|----------------------|----------|-----------------------|----------|----------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol                  | Characteristic                                     | Min. Typ. Max. Units |          | Conditions            |          |                                                                            |  |

| CTMU CUR           | CTMU CURRENT SOURCE     |                                                    |                      |          |                       |          |                                                                            |  |

| CTMUI1             | IOUT1                   | Base Range <sup>(1)</sup>                          | _                    | 0.55     | _                     | μA       | CTMUCON<9:8> = 01                                                          |  |

| CTMUI2             | Іоит2                   | 10x Range <sup>(1)</sup>                           | _                    | 5.5      | _                     | μA       | CTMUCON<9:8> = 10                                                          |  |

| CTMUI3             | Іоит3                   | 100x Range <sup>(1)</sup>                          | _                    | 55       | _                     | μA       | CTMUCON<9:8> = 11                                                          |  |

| CTMUI4             | Iout4                   | 1000x Range <sup>(1)</sup>                         | _                    | 550      | _                     | μA       | CTMUCON<9:8> = 00                                                          |  |

| CTMUFV1            | VF                      | Temperature Diode Forward Voltage <sup>(1,2)</sup> |                      | 0.598    | _                     | V        | TA = +25°C,<br>CTMUCON<9:8> = 01                                           |  |

|                    |                         |                                                    | _                    | 0.658    | _                     | V        | TA = +25°C,<br>CTMUCON<9:8> = 10                                           |  |

|                    |                         |                                                    |                      | 0.721    |                       | V        | TA = +25°C,<br>CTMUCON<9:8> = 11                                           |  |

| CTMUFV2            | VFVR                    | Temperature Diode Rate of                          | _                    | -1.92    | _                     | mV/°C    | CTMUCON<9:8> = 01                                                          |  |

|                    | Change <sup>(1,2)</sup> |                                                    | _                    | -1.74    | _                     | mV/°C    | CTMUCON<9:8> = 10                                                          |  |

|                    |                         |                                                    | _                    | -1.56    | _                     | mV/°C    | CTMUCON<9:8> = 11                                                          |  |

- Note 1: Nominal value at center point of current trim range (CTMUCON<15:10> = 000000).

- 2: Parameters are characterized but not tested in manufacturing. Measurements taken with the following conditions:

- VREF+ = AVDD = 3.3V

- ADC module configured for conversion speed of 500 ksps

- All PMD bits are cleared (PMDx = 0)

- Executing a while(1) statement

- · Device operating from the FRC with no PLL

- **3:** The CTMU module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

| PIC32WX1XX/2XX 28/36/44-PIN FAMILY |  |                |                      |                            |                             |

|------------------------------------|--|----------------|----------------------|----------------------------|-----------------------------|

|                                    |  |                |                      |                            |                             |

|                                    |  |                |                      |                            |                             |

|                                    |  |                |                      |                            |                             |

|                                    |  |                |                      |                            |                             |

|                                    |  |                |                      |                            |                             |

|                                    |  |                |                      |                            |                             |

|                                    |  |                |                      |                            |                             |

|                                    |  |                |                      |                            |                             |

|                                    |  |                |                      |                            |                             |

|                                    |  |                |                      |                            |                             |

|                                    |  |                |                      |                            |                             |

|                                    |  |                |                      |                            |                             |

|                                    |  |                |                      |                            |                             |

|                                    |  | 1XX/2XX 28/36/ | 1XX/2XX 28/36/44-PIN | 1XX/2XX 28/36/44-PIN FAMIL | 1XX/2XX 28/36/44-PIN FAMILY |

### APPENDIX A: REVISION HISTORY

#### Revision A (May 2011)

This is the initial released version of this document.

### **Revision B (October 2011)**

The following two global changes are included in this revision:

- All packaging references to VLAP have been changed to VTLA throughout the document

- · All references to VCORE have been removed

- All occurrences of the ASCL1, ASCL2, ASDA1, and ASDA2 pins have been removed

- V-temp temperature range (-40°C to +105°C) was added to all electrical specification tables

This revision includes the addition of the following devices:

- PIC32MX130F064B

- PIC32MX230F064B

- PIC32MX130F064C

- PIC32MX230F064C

- PIC32MX130F064D

- PIC32MX230F064D

- PIC32MX150F128B

- PIC32MX250F128B

- PIC32MX150F128C

- PIC32MX250F128C

- PIC32MX150F128D

- PIC32MX250F128D

Text and formatting changes were incorporated throughout the document.

All other major changes are referenced by their respective section in Table A-1.

#### TABLE A-1: MAJOR SECTION UPDATES

| Section                                                                 | Update Description                                                                                                                                                        |

|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to 128 KB Flash and 32 KB SRAM) with Audio | Split the existing Features table into two: PIC32MX1XX General Purpose Family Features (Table 1) and PIC32MX2XX USB Family Features (Table 2).                            |

| and Graphics Interfaces, USB, and Advanced Analog"                      | Added the SPDIP package reference (see Table 1, Table 2, and "Pin Diagrams").                                                                                             |

|                                                                         | Added the new devices to the applicable pin diagrams.                                                                                                                     |

|                                                                         | Changed PGED2 to PGED1 on pin 35 of the 36-pin VTLA diagram for PIC32MX220F032C, PIC32MX220F016C, PIC32MX230F064C, and PIC32MX250F128C devices.                           |

| 1.0 "Device Overview"                                                   | Added the SPDIP package reference and updated the pin number for AN12 for 44-pin QFN devices in the Pinout I/O Descriptions (see Table 1-1).                              |

|                                                                         | Added the PGEC4/PGED4 pin pair and updated the C1INA-C1IND and C2INA-C2IND pin numbers for 28-pin SSOP/SPDIP/SOIC devices in the Pinout I/O Descriptions (see Table 1-1). |

| 2.0 "Guidelines for Getting Started with 32-bit Microcontrollers"       | Updated the Recommended Minimum Connection diagram (see Figure 2-1).                                                                                                      |