Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                 |

|---------------------------|---------------------------------------------------------------------------------|

| Product Status            | Active                                                                          |

| Core Processor            | MIPS32® M4K™                                                                    |

| Core Size                 | 32-Bit Single-Core                                                              |

| Speed                     | 40MHz                                                                           |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals               | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O             | 21                                                                              |

| Program Memory Size       | 256KB (256K x 8)                                                                |

| Program Memory Type       | FLASH                                                                           |

| EEPROM Size               | -                                                                               |

| RAM Size                  | 16K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters           | A/D 10x10b                                                                      |

| Oscillator Type           | Internal                                                                        |

| perating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type             | Surface Mount                                                                   |

| Package / Case            | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package   | 28-SSOP                                                                         |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f256bt-i-ss |

### 6.1 Reset Control Registers

### TABLE 6-1: RESET CONTROL REGISTER MAP

| ess                       |                                 |           |       |       |       |       |       |       |      |       | Bits |      |      |      |       |      |      |       | 8          |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|-------|------|------|------|------|-------|------|------|-------|------------|

| Virtual Addrı<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7 | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1 | 16/0  | All Resets |

| F600                      | RCON                            | 31:16     | _     | _     |       | _     | _     | _     |      | _     | _    | _    |      |      |       |      | _    | _     | 0000       |

| F600                      | RCON                            | 15:0      |       | _     | _     | _     | _     | _     | CMR  | VREGS | EXTR | SWR  | _    | WDTO | SLEEP | IDLE | BOR  | POR   | XXXX(2)    |

| F640                      | RSWRST                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _     | _    | _    | _    | _    | _     | _    | _    | _     | 0000       |

| F010                      | KSWKSI                          | 15:0      | _     | _     | _     | _     | _     | _     | I    | _     | _    | _    |      | _    | _     | _    | _    | SWRST | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

#### REGISTER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | _                 | _                 | _                 |                   | IP03<2:0>         |                   | IS03             | <1:0>            |

| 23:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | _                 | _                 | _                 |                   | IP02<2:0>         |                   | IS02             | <1:0>            |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 13.6         | _                 | _                 | _                 |                   | IP01<2:0>         |                   | IS01             | <1:0>            |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | _                 | _                 | _                 |                   | IP00<2:0>         |                   | IS00             | <1:0>            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-29 Unimplemented: Read as '0'

bit 28-26 **IP03<2:0>:** Interrupt Priority bits

111 = Interrupt priority is 7

:

•

010 = Interrupt priority is 2

001 = Interrupt priority is 1

000 = Interrupt is disabled

bit 25-24 IS03<1:0>: Interrupt Subpriority bits

11 = Interrupt subpriority is 3

10 = Interrupt subpriority is 2

01 = Interrupt subpriority is 1

00 = Interrupt subpriority is 0

bit 23-21 Unimplemented: Read as '0'

bit 20-18 IP02<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

•

010 = Interrupt priority is 2

001 = Interrupt priority is 1

000 = Interrupt is disabled

bit 17-16 IS02<1:0>: Interrupt Subpriority bits

11 = Interrupt subpriority is 3

10 = Interrupt subpriority is 2

01 = Interrupt subpriority is 1

00 = Interrupt subpriority is 0

bit 15-13 Unimplemented: Read as '0'

bit 12-10 IP01<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

•

010 = Interrupt priority is 2

001 = Interrupt priority is 1

000 = Interrupt is disabled

**Note:** This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions.

| <b>TABLE 9-3:</b> | DMA CHANNE | -I S 0-3 | REGISTER | MAP |

|-------------------|------------|----------|----------|-----|

|                   |            |          |          |     |

| ess                         |                                 | 0             | Bits        |       |       |       |             |       |           |             |         |         |        |                 |                  |          |        |        |              |

|-----------------------------|---------------------------------|---------------|-------------|-------|-------|-------|-------------|-------|-----------|-------------|---------|---------|--------|-----------------|------------------|----------|--------|--------|--------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15       | 30/14 | 29/13 | 28/12 | 27/11       | 26/10 | 25/9      | 24/8        | 23/7    | 22/6    | 21/5   | 20/4            | 19/3             | 18/2     | 17/1   | 16/0   | All Resets   |

| 3060                        | DCH0CON                         | 31:16         | _           | _     | _     | 1     | ı           | ı     | _         | _           | _       | _       | _      | 1               | _                | _        | _      | _      | 0000         |

| 3060                        | DCHUCON                         | 15:0          | CHBUSY      | _     | _     | _     | _           | _     | _         | CHCHNS      | CHEN    | CHAED   | CHCHN  | CHAEN           | _                | CHEDET   | CHPR   | l<1:0> | 0000         |

| 3070                        | DCH0ECON                        | 31:16         | _           | _     | _     | _     | _           | _     | _         | _           |         |         |        | CHAIR           |                  |          |        |        | 00FF         |

|                             |                                 | 15:0          |             |       |       | CHSIR | Q<7:0>      |       | 1         |             | CFORCE  | CABORT  | PATEN  | SIRQEN          | AIRQEN           | _        | _      | _      | FF00         |

| 3080                        | DCH0INT                         | 31:16         | _           |       | _     | _     | _           | _     | _         | _           | CHSDIE  | CHSHIE  | CHDDIE | CHDHIE          | CHBCIE           | CHCCIE   | CHTAIE | CHERIE | 0000         |

|                             |                                 | 15:0          | _           |       | _     | _     | _           | _     | _         | _           | CHSDIF  | CHSHIF  | CHDDIF | CHDHIF          | CHBCIF           | CHCCIF   | CHTAIF | CHERIF | 0000         |

| 3090                        | DCH0SSA                         | 31:16<br>15:0 |             |       |       |       |             |       |           | CHSSA       | <31:0>  |         |        |                 |                  |          |        |        | 0000         |

|                             |                                 | 31:16         |             |       |       |       |             |       |           |             |         |         |        |                 |                  |          |        |        | 0000         |

| 30A0                        | DCH0DSA                         | 15:0          |             |       |       |       |             |       |           | CHDSA       | A<31:0> |         |        |                 |                  |          |        |        | 0000         |

|                             |                                 | 31:16         | _           | _     | _     | _     | _           | _     | _         | _           | _       | _       | _      | _               | _                | _        | _      | _      | 0000         |

| 30B0                        | DCH0SSIZ                        | 15:0          |             |       |       |       |             |       |           | CHSSIZ      | Z<15:0> |         |        |                 |                  |          |        |        | 0000         |

|                             |                                 | 31:16         | _           | _     | _     | _     | _           | _     | _         | _           | _       | _       | _      | _               | _                | _        | _      | _      | 0000         |

| 30C0                        | DCH0DSIZ                        | 15:0          |             |       |       |       |             |       |           | CHDSIZ      | Z<15:0> |         |        |                 |                  |          |        |        | 0000         |

| 0000                        | DOLLOODED                       | 31:16         | _           | _     | _     | _     | _           | _     | _         | _           | _       | _       | _      | _               | _                | _        | _      | _      | 0000         |

| 3000                        | DCH0SPTR                        | 15:0          | •           |       |       |       |             |       | •         | CHSPTI      | R<15:0> | •       | •      |                 | •                |          | •      | •      | 0000         |

| 30E0                        | DCH0DPTR                        | 31:16         | _           | _     | _     | _     | _           | _     | _         | _           | _       | _       | _      | _               | _                | _        | _      | _      | 0000         |

| 30E0                        | DCHUDFIK                        | 15:0          |             |       |       |       |             |       |           | CHDPT       | R<15:0> |         |        |                 |                  |          |        |        | 0000         |

| 30F0                        | DCH0CSIZ                        | 31:16         | _           |       | _     | _     | _           | _     | _         | _           | _       | _       | _      | _               | _                | _        | _      | _      | 0000         |

| 001 0                       | DOI 100012                      | 15:0          |             |       |       |       |             |       |           | CHCSIZ      | Z<15:0> |         |        |                 |                  |          |        |        | 0000         |

| 3100                        | DCH0CPTR                        | 31:16         | _           | _     | _     | _     | _           | _     | _         | _           | _       | _       | _      | _               | _                | _        | _      | _      | 0000         |

|                             |                                 | 15:0          |             |       |       |       |             |       |           | CHCPT       | R<15:0> |         |        |                 |                  |          |        |        | 0000         |

| 3110                        | DCH0DAT                         | 31:16         | _           |       | _     | _     | _           | _     | _         | _           | _       | _       | _      |                 |                  | _        | _      | _      | 0000         |

|                             |                                 | 15:0          | _           |       | _     |       |             |       | _         | _           |         |         |        | CHPDA           |                  |          |        |        | 0000         |

| 3120                        | DCH1CON                         | 31:16         | - CLIBLION  |       | _     | _     | _           |       | _         | -           | - CLIEN | - CHAFD | -      | - CLIATAL       | _                | - CHEDET |        | -      | 0000         |

|                             |                                 | 15:0          | CHBUSY      |       | _     | _     | _           | _     | _         | CHCHNS      | CHEN    | CHAED   | CHCHN  | CHAEN           | —<br>O 47:05     | CHEDET   | CHPR   | 1<1:0> | 0000         |

| 3130                        | DCH1ECON                        | 31:16<br>15:0 | _           |       | _     | CHSIR | —<br>O<7:0> | _     | _         | _           | CFORCE  | CABORT  | PATEN  | CHAIR<br>SIRQEN | Q<7:0><br>AIRQEN | _        |        |        | 00FF<br>FF00 |

|                             |                                 | 31:16         | _           |       | _     | CHOIR | Q~1.U~      | _     |           | _           | CHSDIE  | CHSHIE  | CHDDIE | CHDHIE          | CHBCIE           | CHCCIE   | CHTAIE | CHERIE | 0000         |

| 3140                        | DCH1INT                         | 15:0          | _           |       |       |       |             |       |           |             | CHSDIF  | CHSHIF  | CHDDIF | CHDHIF          | CHBCIE           | CHCCIE   | CHTAIL | CHERIF | 0000         |

|                             |                                 | 31:16         | 6           |       |       |       |             |       |           |             |         |         |        |                 |                  |          |        |        |              |

| 3150                        | DCH1SSA                         | 15:0          | CHSSA<31:05 |       |       |       |             |       |           |             |         |         |        |                 | 0000             |          |        |        |              |

| <u> </u>                    |                                 | 31:16         |             |       |       |       |             |       |           |             |         |         |        |                 |                  |          |        |        | 0000         |

| 3160                        | DCH1DSA                         | 15:0          | CHDSA<31:0> |       |       |       |             |       |           |             |         |         |        |                 |                  |          |        |        |              |

| Legen                       |                                 |               |             |       |       |       | - (o) D     |       | - la ! la | nevadecimal |         |         |        |                 |                  |          |        |        | 12220        |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

REGISTER 9-1: DMACON: DMA CONTROLLER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 |                   |                   | _                 | -                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | _                 | SUSPEND           | DMABUSY           | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** DMA On bit<sup>(1)</sup>

1 = DMA module is enabled0 = DMA module is disabled

bit 14-13 **Unimplemented:** Read as '0' bit 12 **SUSPEND:** DMA Suspend bit

1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

0 = DMA operates normally

bit 11 DMABUSY: DMA Module Busy bit

1 = DMA module is active

0 = DMA module is disabled and not actively transferring data

bit 10-0 Unimplemented: Read as '0'

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 10-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1     | Bit<br>24/16/8/0 |        |         |                       |       |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------------|------------------|--------|---------|-----------------------|-------|

| 24.24        | U-0                  | U-0              |        |         |                       |       |

| 31:24        |                   | _                 | _                 | _                 | _                 | _                 | _                    | _                |        |         |                       |       |

| 23:16        | U-0                  | U-0              |        |         |                       |       |

| 23.10        |                   | _                 | _                 | _                 | _                 | -                 | _                    | _                |        |         |                       |       |

| 15:8         | U-0                  | U-0              |        |         |                       |       |

| 15.6         |                   | _                 | _                 | _                 | _                 | _                 | _                    | _                |        |         |                       |       |

|              | R/W-0                | R/W-0            |        |         |                       |       |

| 7:0          | BTSEE             | RTSEE             | RTSEE             | RTSEE             | RTSEE R           | BTSEE BMXEE       | DMAEE                | BTOEE            | DFN8EE | CRC16EE | CRC5EE <sup>(1)</sup> | PIDEE |

|              | DISEL             | DIVINEE           | DIVIALE           | DIOEE             | DINOEE            | ONO IDEE          | EOFEE <sup>(2)</sup> | IIDEE            |        |         |                       |       |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 BTSEE: Bit Stuff Error Interrupt Enable bit

1 = BTSEF interrupt is enabled0 = BTSEF interrupt is disabled

bit 6 BMXEE: Bus Matrix Error Interrupt Enable bit

1 = BMXEF interrupt is enabled0 = BMXEF interrupt is disabled

bit 5 DMAEE: DMA Error Interrupt Enable bit

1 = DMAEF interrupt is enabled0 = DMAEF interrupt is disabled

bit 4 BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit

1 = BTOEF interrupt is enabled0 = BTOEF interrupt is disabled

bit 3 DFN8EE: Data Field Size Error Interrupt Enable bit

1 = DFN8EF interrupt is enabled0 = DFN8EF interrupt is disabled

bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

1 = CRC16EF interrupt is enabled0 = CRC16EF interrupt is disabled

bit 1 CRC5EE: CRC5 Host Error Interrupt Enable bit (1)

1 = CRC5EF interrupt is enabled 0 = CRC5EF interrupt is disabled

**EOFEE:** EOF Error Interrupt Enable bit<sup>(2)</sup>

1 = EOF interrupt is enabled0 = EOF interrupt is disabled

bit 0 PIDEE: PID Check Failure Interrupt Enable bit

1 = PIDEF interrupt is enabled0 = PIDEF interrupt is disabled

Note 1: Device mode.

2: Host mode.

Note: For an interrupt to propagate the USBIF register, the UERRIE (U1IE<1>) bit must be set.

#### REGISTER 10-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -                 | _                 | _                 | 1                 | -                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | 1                 | -                 | 1                 |                   | 1                 | 1                 | 1                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |

| 7.0          | _                 | _                 | _                 | _                 | _                 |                   | FRMH<2:0>        |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-3 Unimplemented: Read as '0'

bit 2-0 FRMH<2:0>: The Upper 3 bits of the Frame Numbers bits

The register bits are updated with the current frame number whenever a SOF TOKEN is received.

#### **REGISTER 10-15: U1TOK: USB TOKEN REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -                   | _                 | -                 | _                 | -                | _                |

| 23:16        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                   | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | -                 | _                 | -                   | _                 | -                 | _                 | -                | -                |

| 7:0          | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   | PID<              | 3:0> <sup>(1)</sup> |                   |                   | EP<               | 3:0>             |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR  $(1)^2$  = Bit is set  $(0)^2$  = Bit is cleared  $(0)^2$  = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-4 PID<3:0>: Token Type Indicator bits<sup>(1)</sup>

1101 = SETUP (TX) token type transaction 1001 = IN (RX) token type transaction

0001 = OUT (TX) token type transaction

Note: All other values are reserved and must not be used.

bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits

The four bit value must specify a valid endpoint.

Note 1: All other values are reserved and must not be used.

**TABLE 11-6:** PERIPHERAL PIN SELECT INPUT REGISTER MAP

| SS                          |                  |           | Bits  |       |       |       |       |       |      |      |      |      |      |      |      |       |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| FA04                        | INT1R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FAU4                        | INTIK            | 15:0      | _     | _     | _     | _     | _     | _     |      | _    | _    | _    |      | _    |      | INT1F | R<3:0> |      | 0000       |

| FA08                        | INT2R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 17100                       | IIVIZIX          | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | INT2F | R<3:0> |      | 0000       |

| FA0C                        | INT3R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 17.00                       | IIIII            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | INT3F | R<3:0> |      | 0000       |

| FA10                        | INT4R            | 31:16     |       |       | _     | _     | _     |       |      |      |      |      |      |      | _    | _     | _      | _    | 0000       |

| .,                          |                  | 15:0      |       |       |       | _     |       |       |      |      |      | _    |      |      |      | INT4F | R<3:0> | ı    | 0000       |

| FA18                        | T2CKR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T2CKI | R<3:0> |      | 0000       |

| FA1C                        | T3CKR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      |       |       | _     | _     | _     | _     |      |      |      | _    |      |      |      | T3CKI | R<3:0> | ı    | 0000       |

| FA20                        | T4CKR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T4CKI | R<3:0> |      | 0000       |

| FA24                        | T5CKR            | 31:16     |       |       | _     |       | _     |       |      | _    |      | _    |      | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     |       |       | _     |      | _    | _    | _    | _    | _    |      | T5CKI | R<3:0> |      | 0000       |

| FA28                        | IC1R             | 31:16     | _     | _     | _     |       |       | _     |      | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             | _                | 15:0      | _     | _     | _     |       |       | _     |      | _    | _    | _    | _    | _    |      | IC1R  | <3:0>  |      | 0000       |

| FA2C                        | IC2R             | 31:16     | _     | _     | _     |       |       | _     |      | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             | _                | 15:0      | _     | _     | _     |       |       | _     |      | _    |      | _    |      | _    |      | IC2R  | <3:0>  |      | 0000       |

| FA30                        | IC3R             | 31:16     | _     | _     | _     |       |       | _     |      | _    |      | _    |      | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      |       | _     |       |       |       | _     |      | _    |      | _    |      | _    |      | IC3R  | <3:0>  |      | 0000       |

| FA34                        | IC4R             | 31:16     |       |       |       |       |       |       |      |      |      |      |      |      |      |       |        | _    | 0000       |

|                             |                  | 15:0      |       |       |       |       |       |       |      |      |      |      |      |      |      | IC4R  | <3:0>  |      | 0000       |

| FA38                        | IC5R             | 31:16     |       | _     |       |       |       | _     |      | _    |      | _    |      | _    | _    | _     |        | _    | 0000       |

|                             |                  | 15:0      | _     | _     |       |       |       | _     |      | _    |      | _    |      | _    |      | IC5R  | <3:0>  |      | 0000       |

| FA48                        | OCFAR            | 31:16     | _     | _     | _     | _     | _     | _     |      | _    | _    | _    |      | _    | _    | _     |        | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     |      | _    | _    | _    |      | _    |      | OCFA  | R<3:0> |      | 0000       |

| FA4C                        | OCFBR            | 31:16     |       | _     | _     | _     | _     | _     |      |      |      | _    |      |      | _    | _     |        | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | OCFB  | R<3:0> |      | 0000       |

| FA50                        | U1RXR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             | •                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U1RX  | R<3:0> |      | 0000       |

### 18.1 I2C Control Registers

### TABLE 18-1: I2C1 AND I2C2 REGISTER MAP

| ess                         |                                 |               |         | Bits   |       |        |        |       |        |       |          |             |            |              |           |      |      |      |            |

|-----------------------------|---------------------------------|---------------|---------|--------|-------|--------|--------|-------|--------|-------|----------|-------------|------------|--------------|-----------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14  | 29/13 | 28/12  | 27/11  | 26/10 | 25/9   | 24/8  | 23/7     | 22/6        | 21/5       | 20/4         | 19/3      | 18/2 | 17/1 | 16/0 | All Resets |

| 5000                        | I2C1CON                         | 31:16         |         | _      | _     | _      | _      | _     | _      | _     |          | _           |            | _            |           | _    | _    | _    | 0000       |

|                             |                                 | 15:0          | ON      |        | SIDL  | SCLREL | STRICT | A10M  | DISSLW | SMEN  | GCEN     | STREN       | ACKDT      | ACKEN        | RCEN      | PEN  | RSEN | SEN  | 1000       |

| 5010                        | I2C1STAT                        | 31:16         |         |        |       | _      |        | _     | -      | -     |          | -           |            | _            | _         | -    | _    |      | 0000       |

|                             |                                 |               | ACKSTAT | TRSTAT |       | _      |        | BCL   | GCSTAT | ADD10 | IWCOL    | I2COV       | D_A        | Р            | S         | R_W  | RBF  | TBF  | 0000       |

| 5020                        | I2C1ADD                         | 31:16         | _       |        |       | _      |        |       | _      | _     | _        | _           | <u> </u>   | <u> </u>     | _         | _    | _    | _    | 0000       |

|                             |                                 | 15:0          | _       |        |       | _      |        |       |        |       |          |             | Address    | Register     |           |      |      |      | 0000       |

| 5030                        | I2C1MSK                         | 31:16<br>15:0 |         | _      | _     | _      | _      | _     | _      | _     | _        | _           |            | —<br>!-D!-t  | _         | _    | _    | _    | 0000       |

|                             |                                 | 31:16         | _       | _      | _     | _      | _      | _     |        |       |          |             | Address Ma | ask Register |           |      |      |      | 0000       |

| 5040                        | I2C1BRG                         | 15:0          | _       |        | _     | _      | _      | _     | _      |       |          | d Bata Car  | orator Boa | inter        |           | _    | _    | _    | 0000       |

|                             |                                 | 31:16         | _       | _      |       | _      |        |       | _      | _     | Бац      | id Rate Ger | erator Reg | Islei        |           |      |      | _    | 0000       |

| 5050                        | I2C1TRN                         | 15:0          | _       |        |       |        |        | _     |        |       |          | _           |            | Transmit     | Pogistor. | _    | _    | _    | 0000       |

|                             |                                 | 31:16         | _       |        |       | _      |        |       | _      |       | _        | _           | _          |              | Register  | _    | _    | _    | 0000       |

| 5060                        | I2C1RCV                         | 15:0          | _       |        |       |        |        |       |        |       | <u> </u> | _           |            | Receive      | Pegister  |      |      |      | 0000       |

|                             |                                 | 31:16         |         |        |       |        |        |       |        |       |          | _           | _          |              | —         | _    | _    | _    | 0000       |

| 5100                        | I2C2CON                         | 15:0          | ON      |        | SIDL  | SCLREL | STRICT | A10M  | DISSLW | SMEN  | GCEN     | STREN       | ACKDT      | ACKEN        | RCEN      | PEN  | RSEN | SEN  | 1000       |

|                             |                                 | 31:16         |         |        | —     |        | _      | _     |        | _     | _        | —           | _          |              | _         | _    | _    | _    | 0000       |

| 5110                        | I2C2STAT                        |               | ACKSTAT | TRSTAT |       | _      |        | BCL   | GCSTAT | ADD10 | IWCOL    | I2COV       | DΑ         | Р            | S         | R W  | RBF  | TBF  | 0000       |

|                             |                                 | 31:16         |         | _      | _     | _      | _      |       | _      | _     | _        | _           |            | _            | _         |      | _    | _    | 0000       |

| 5120                        | I2C2ADD                         | 15:0          | _       |        |       | _      |        | _     |        |       |          |             | Address    | Register     |           |      |      |      | 0000       |

|                             |                                 | 31:16         | _       | _      | _     | _      | _      | _     | _      | _     | _        | _           | _          | _            | _         | _    | _    | _    | 0000       |

| 5130                        | I2C2MSK                         | 15:0          | _       | _      | _     | _      |        | _     |        |       |          |             | Address Ma | sk Register  |           |      |      |      | 0000       |

| 5440                        | 1000000                         | 31:16         | _       | 1      | _     | _      | -      | _     | _      | _     | _        | _           | _          | _            | _         | _    | _    | _    | 0000       |

| 5140                        | I2C2BRG                         | 15:0          | _       |        | _     | _      |        | •     | •      |       | Bau      | id Rate Ger | erator Reg | ister        |           |      |      |      | 0000       |

| 5150                        | I2C2TRN                         | 31:16         | _       |        |       | _      | ı      | _     | _      | _     | _        | _           | _          | _            | _         | _    | _    | _    | 0000       |

| 5 150                       | 12021KN                         | 15:0          | _       |        |       | _      |        |       |        | _     |          |             |            | Transmit     | Register  |      |      |      | 0000       |

| 5160                        | I2C2RCV                         | 31:16         | _       | _      | _     | _      | -      | _     | _      | _     |          | _           | _          | _            |           |      | _    | _    | 0000       |

| 3 100                       | IZUZRUV                         | 15:0          | _       | _      |       |        |        |       |        |       |          |             |            |              |           |      |      |      |            |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

### REGISTER 18-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER (CONTINUED)

- bit 7 **GCEN:** General Call Enable bit (when operating as I<sup>2</sup>C slave)

- 1 = Enable interrupt when a general call address is received in the I2CxRSR (module is enabled for reception)

- 0 = General call address is disabled

- bit 6 **STREN:** SCLx Clock Stretch Enable bit (when operating as I<sup>2</sup>C slave)

Used in conjunction with SCLREL bit.

- 1 = Enable software or receive clock stretching

- 0 = Disable software or receive clock stretching

- bit 5 **ACKDT:** Acknowledge Data bit (when operating as I<sup>2</sup>C master, applicable during master receive)

Value that is transmitted when the software initiates an Acknowledge sequence.

- 1 = Send a NACK during an Acknowledge sequence

- 0 = Send an ACK during an Acknowledge sequence

- bit 4 **ACKEN:** Acknowledge Sequence Enable bit (when operating as I<sup>2</sup>C master, applicable during master receive)

- 1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit. Hardware clear at end of master Acknowledge sequence.

- 0 = Acknowledge sequence not in progress

- bit 3 **RCEN:** Receive Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Enables Receive mode for I<sup>2</sup>C. Hardware clear at end of eighth bit of master receive data byte.

- 0 = Receive sequence not in progress

- bit 2 **PEN:** Stop Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence.

- 0 = Stop condition not in progress

- bit 1 **RSEN:** Repeated Start Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master Repeated Start sequence.

- 0 = Repeated Start condition not in progress

- bit 0 **SEN:** Start Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence.

- 0 = Start condition not in progress

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

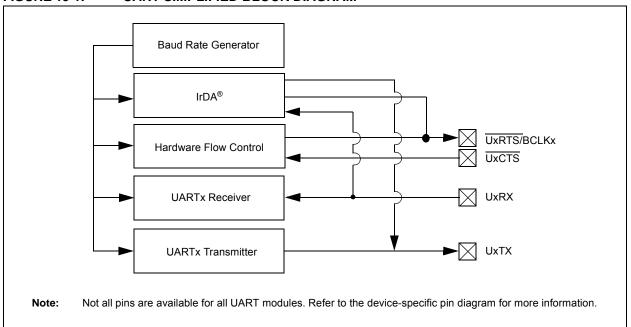

# 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 21.** "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The UART module is one of the serial I/O modules available in PIC32MX1XX/2XX 28/36/44-pin Family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN, and IrDA®. The UART module also supports the hardware flow control option, with UxCTS and UxRTS pins, and also includes an IrDA encoder and decoder.

Key features of the UART module include:

- Full-duplex. 8-bit or 9-bit data transmission

- Even, Odd or No Parity options (for 8-bit data)

- · One or two Stop bits

- · Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 38 bps to 12.5 Mbps at 50 MHz

- 8-level deep First In First Out (FIFO) transmit data buffer

- · 8-level deep FIFO receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (9th bit = 1)

- · Separate transmit and receive interrupts

- · Loopback mode for diagnostic support

- · LIN protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 19-1 illustrates a simplified block diagram of the UART module.

FIGURE 19-1: UART SIMPLIFIED BLOCK DIAGRAM

#### REGISTER 19-1: UxMODE: UARTX MODE REGISTER (CONTINUED)

- bit 5 ABAUD: Auto-Baud Enable bit

- 1 = Enable baud rate measurement on the next character requires reception of Sync character (0x55); cleared by hardware upon completion

- 0 = Baud rate measurement disabled or completed

- bit 4 RXINV: Receive Polarity Inversion bit

- 1 = UxRX Idle state is '0'

- 0 = UxRX Idle state is '1'

- bit 3 BRGH: High Baud Rate Enable bit

- 1 = High-Speed mode 4x baud clock enabled

- 0 = Standard Speed mode 16x baud clock enabled

- bit 2-1 PDSEL<1:0>: Parity and Data Selection bits

- 11 = 9-bit data, no parity

- 10 = 8-bit data, odd parity

- 01 = 8-bit data, even parity

- 00 = 8-bit data, no parity

- bit 0 STSEL: Stop Selection bit

- 1 = 2 Stop bits

- 0 = 1 Stop bit

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 19-2: UxSTA: UARTX STATUS AND CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |  |  |

| 31:24        |                   | _                 | _                 | -                 | _                 | -                 | _                | ADM_EN           |  |  |

| 22.46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | ADDR<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-1              |  |  |

| 15:8         | UTXISE            | L<1:0>            | UTXINV            | URXEN             | UTXBRK            | UTXEN             | UTXBF            | TRMT             |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R-1               | R-0               | R-0               | R/W-0            | R-0              |  |  |

| 7:0          | URXISEL<1:0>      |                   | ADDEN             | RIDLE             | PERR              | FERR              | OERR             | URXDA            |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-25 Unimplemented: Read as '0'

bit 24 ADM\_EN: Automatic Address Detect Mode Enable bit

1 = Automatic Address Detect mode is enabled

0 = Automatic Address Detect mode is disabled

bit 23-16 ADDR<7:0>: Automatic Address Mask bits

When the ADM\_EN bit is '1', this value defines the address character to use for automatic address detection.

bit 15-14 UTXISEL<1:0>: TX Interrupt Mode Selection bits

11 = Reserved, do not use

10 = Interrupt is generated and asserted while the transmit buffer is empty

01 = Interrupt is generated and asserted when all characters have been transmitted

00 = Interrupt is generated and asserted while the transmit buffer contains at least one empty space

bit 13 **UTXINV:** Transmit Polarity Inversion bit

If IrDA mode is disabled (i.e., IREN (UxMODE<12>) is '0'):

1 = UxTX Idle state is '0'

0 = UxTX Idle state is '1'

#### If IrDA mode is enabled (i.e., IREN (UxMODE<12>) is '1'):

1 = IrDA encoded UxTX Idle state is '1'

0 = IrDA encoded UxTX Idle state is '0'

bit 12 URXEN: Receiver Enable bit

1 = UARTx receiver is enabled. UxRX pin is controlled by UARTx (if ON = 1)

0 = UARTx receiver is disabled. UxRX pin is ignored by the UARTx module. UxRX pin is controlled by port.

bit 11 UTXBRK: Transmit Break bit

1 = Send Break on next transmission. Start bit followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

0 = Break transmission is disabled or completed

bit 10 UTXEN: Transmit Enable bit

1 = UARTx transmitter is enabled. UxTX pin is controlled by UARTx (if ON = 1).

0 = UARTx transmitter is disabled. Any pending transmission is aborted and buffer is reset. UxTX pin is controlled by port.

bit 9 UTXBF: Transmit Buffer Full Status bit (read-only)

1 = Transmit buffer is full

0 = Transmit buffer is not full, at least one more character can be written

bit 8 **TRMT:** Transmit Shift Register is Empty bit (read-only)

1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed)

0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer

### REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

- bit 1-0 WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits(1)

- 11 = Wait of 4 TPB

- 10 = Wait of 3 TPB

- 01 = Wait of 2 TPB

- 00 = Wait of 1 TPB (default)

#### For Read operations:

- 11 = Wait of 3 TPB

- 10 = Wait of 2 TPB

- 01 = Wait of 1 TPB

- 00 = Wait of 0 TPB (default)

- Note 1: Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 ΤΡΒCLK cycle for a write operation; WAITB = 1 ΤΡΒCLK cycle, WAITE = 0 ΤΡΒCLK cycles for a read operation.

- 2: Address bit A14 is not subject to auto-increment/decrement if configured as Chip Select CS1.

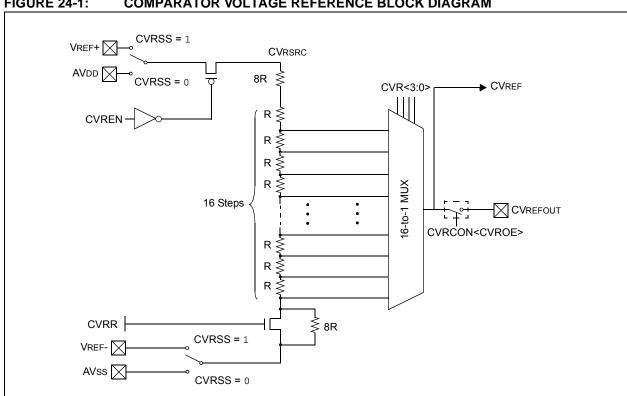

#### **COMPARATOR VOLTAGE** 24.0 REFERENCE (CVREF)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The CVREF module is a 16-tap, resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it also may be used independently of them.

The resistor ladder is segmented to provide two ranges of voltage reference values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/Vss or an external voltage reference. The CVREF output is available for the comparators and typically available for pin output.

The comparator voltage reference has the following features:

- · High and low range selection

- · Sixteen output levels available for each range

- · Internally connected to comparators to conserve device pins

- Output can be connected to a pin

A block diagram of the module is shown in Figure 24-1.

**FIGURE 24-1:** COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

### 25.1 CTMU Control Registers

### TABLE 25-1: CTMU REGISTER MAP

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range |         | Bits    |              |       |       |          |          |          |         |         |                    |       |      |      | (0   |       |            |

|-----------------------------|---------------------------------|-----------|---------|---------|--------------|-------|-------|----------|----------|----------|---------|---------|--------------------|-------|------|------|------|-------|------------|

|                             |                                 |           | 31/15   | 30/14   | 29/13        | 28/12 | 27/11 | 26/10    | 25/9     | 24/8     | 23/7    | 22/6    | 21/5               | 20/4  | 19/3 | 18/2 | 17/1 | 16/0  | All Resets |

| 4000                        | CTMUCON                         | 31:16     | EDG1MOD | EDG1POL | EDG1SEL<3:0> |       |       |          | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL | G2POL EDG2SEL<3:0> |       |      |      | _    | _     | 0000       |

| A200                        |                                 | 15:0      | ON      | _       | CTMUSIDL     | TGEN  | EDGEN | EDGSEQEN | IDISSEN  | CTTRIG   |         |         | ITRIM•             | <5:0> |      |      | IRNG | <1:0> | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### 26.0 POWER-SAVING FEATURES

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 10.** "**Power-Saving Features**" (DS60001130), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This section describes power-saving features for the PIC32MX1XX/2XX 28/36/44-pin Family. The PIC32 devices offer a total of nine methods and modes, organized into two categories, that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

### 26.1 Power Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the PBCLK and by individually disabling modules. These methods are grouped into the following categories:

- FRC Run mode: the CPU is clocked from the FRC clock source with or without postscalers

- LPRC Run mode: the CPU is clocked from the LPRC clock source

- Sosc Run mode: the CPU is clocked from the Sosc clock source

In addition, the Peripheral Bus Scaling mode is available where peripherals are clocked at the programmable fraction of the CPU clock (SYSCLK).

#### 26.2 CPU Halted Methods

The device supports two power-saving modes, Sleep and Idle, both of which Halt the clock to the CPU. These modes operate with all clock sources, as follows:

- Posc Idle mode: the system clock is derived from the Posc. The system clock source continues to operate. Peripherals continue to operate, but can optionally be individually disabled.

- FRC Idle mode: the system clock is derived from the FRC with or without postscalers. Peripherals continue to operate, but can optionally be individually disabled.

- Sosc Idle mode: the system clock is derived from the Sosc. Peripherals continue to operate, but can optionally be individually disabled.

- LPRC Idle mode: the system clock is derived from the LPRC. Peripherals continue to operate, but can optionally be individually disabled. This is the lowest power mode for the device with a clock running.

- Sleep mode: the CPU, the system clock source and any peripherals that operate from the system clock source are Halted. Some peripherals can operate in Sleep using specific clock sources. This is the lowest power mode for the device.

### 26.3 Power-Saving Operation

Peripherals and the CPU can be Halted or disabled to further reduce power consumption.

#### 26.3.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are Halted. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- · The CPU is halted

- The system clock source is typically shutdown.

See Section 26.3.3 "Peripheral Bus Scaling Method" for specific information.

- There can be a wake-up delay based on the oscillator selection

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode

- The BOR circuit remains operative during Sleep mode

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep

- The USB module can override the disabling of the Posc or FRC. Refer to the USB section for specific details.

- Modules can be individually disabled by software prior to entering Sleep in order to further reduce consumption

# 26.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to enabled or disabled peripherals:

- · Control register lock sequence

- · Configuration bit select lock

#### 26.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the Configuration bit, PMDLOCK (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes.

To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 6. "Oscillator"** (DS60001112) in the "PIC32 Family Reference Manual" for details.

### 26.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The Configuration bit, PMDL1WAY (DEVCFG3<28>), blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

### REGISTER 27-3: DEVCFG2: DEVICE CONFIGURATION WORD 2 (CONTINUED)

bit 2-0 FPLLIDIV<2:0>: PLL Input Divider bits

111 = 12x divider

110 = 10x divider

101 = 6x divider

100 = 5x divider

011 = 4x divider

010 = 3x divider

001 = 2x divider

000 = 1x divider

Note 1: This bit is only available on PIC32MX2XX devices.

#### REGISTER 27-5: CFGCON: CONFIGURATION CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5     | Bit<br>28/20/12/4      | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-----------------------|------------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                     | _                      | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | -                 | -                     | _                      | _                 | _                 | _                | _                |

| 45.0         | U-0               | U-0               | R/W-0                 | R/W-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 |                   | IOLOCK <sup>(1)</sup> | PMDLOCK <sup>(1)</sup> | _                 | _                 |                  | _                |

| 7.0          | U-0               | U-0               | U-0                   | U-0                    | R/W-1             | U-0               | U-1              | R/W-1            |

| 7:0          | _                 |                   |                       | _                      | JTAGEN            | _                 |                  | TDOEN            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-14 Unimplemented: Read as '0'

bit 13 **IOLOCK:** Peripheral Pin Select Lock bit<sup>(1)</sup>

${\tt 1}$  = Peripheral Pin Select is locked. Writes to PPS registers is not allowed.

0 = Peripheral Pin Select is not locked. Writes to PPS registers is allowed.

bit 12 **PMDLOCK:** Peripheral Module Disable bit<sup>(1)</sup>

1 = Peripheral module is locked. Writes to PMD registers is not allowed.

0 = Peripheral module is not locked. Writes to PMD registers is allowed.

bit 11-4 Unimplemented: Read as '0'

bit 3 JTAGEN: JTAG Port Enable bit

1 = Enable the JTAG port

0 = Disable the JTAG port

bit 2-1 Unimplemented: Read as '1'

bit 0 TDOEN: TDO Enable for 2-Wire JTAG bit

1 = 2-wire JTAG protocol uses TDO

0 = 2-wire JTAG protocol does not use TDO

**Note 1:** To change this bit, the unlock sequence must be performed. Refer to **Section 6. "Oscillator"** (DS60001112) in the "PIC32 Family Reference Manual" for details.

### 28.0 INSTRUCTION SET

The PIC32MX1XX/2XX family instruction set complies with the MIPS32® Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- · Core extend instructions

- · Coprocessor 1 instructions

- · Coprocessor 2 instructions

Note: Refer to "MIPS32® Architecture for Programmers Volume II: The MIPS32® Instruction Set" at www.imgtec.com for more information.