Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Dectano                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K <sup>™</sup>                                                         |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K × 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f256d-50i-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

| Exception | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                               |

| DSS       | EJTAG debug single step.                                                                                                                |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                                |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                            |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                         |

| AdEL      | Fetch address alignment error.<br>Fetch reference to protected address.                                                                 |

| IBE       | Instruction fetch bus error.                                                                                                            |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                                      |

| Sys       | Execution of SYSCALL instruction.                                                                                                       |

| Вр        | Execution of BREAK instruction.                                                                                                         |

| RI        | Execution of a reserved instruction.                                                                                                    |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                           |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled.                                                                     |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                                 |

| Tr        | Execution of a trap (when trap condition is true).                                                                                      |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                           |

| AdEL      | Load address alignment error.<br>Load reference to protected address.                                                                   |

| AdES      | Store address alignment error.<br>Store to protected address.                                                                           |

| DBE       | Load or store bus error.                                                                                                                |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                            |

## TABLE 3-3: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE EXCEPTION TYPES

## 3.3 Power Management

The MIPS M4K processor core offers many power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or Halting the clocks, which reduces system power consumption during Idle periods.

## 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see Section 26.0 "Power-Saving Features".

## 3.4 EJTAG Debug Support

The MIPS M4K processor core provides an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the M4K core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used.

## TABLE 4-1: SFR MEMORY MAP

|                           | Virtual A | ddress          |  |  |  |

|---------------------------|-----------|-----------------|--|--|--|

| Peripheral                | Base      | Offset<br>Start |  |  |  |

| Watchdog Timer            |           | 0x0000          |  |  |  |

| RTCC                      |           | 0x0200          |  |  |  |

| Timer1-5                  |           | 0x0600          |  |  |  |

| Input Capture 1-5         |           | 0x2000          |  |  |  |

| Output Compare 1-5        |           | 0x3000          |  |  |  |

| IC1 and IC2               |           | 0x5000          |  |  |  |

| SPI1 and SPI2             |           | 0x5800          |  |  |  |

| UART1 and UART2           |           | 0x6000          |  |  |  |

| PMP                       |           | 0x7000          |  |  |  |

| ADC                       | 0xBF80    | 0x9000          |  |  |  |

| CVREF                     |           | 0x9800          |  |  |  |

| Comparator                |           | 0xA000          |  |  |  |

| CTMU                      |           | 0xA200          |  |  |  |

| Oscillator                |           | 0xF000          |  |  |  |

| Device and Revision ID    |           | 0xF220          |  |  |  |

| Peripheral Module Disable |           | 0xF240          |  |  |  |

| Flash Controller          |           | 0xF400          |  |  |  |

| Reset                     |           | 0xF600          |  |  |  |

| PPS                       |           | 0xFA04          |  |  |  |

| Interrupts                |           | 0x1000          |  |  |  |

| Bus Matrix                |           | 0x2000          |  |  |  |

| DMA                       | 0xBF88    | 0x3000          |  |  |  |

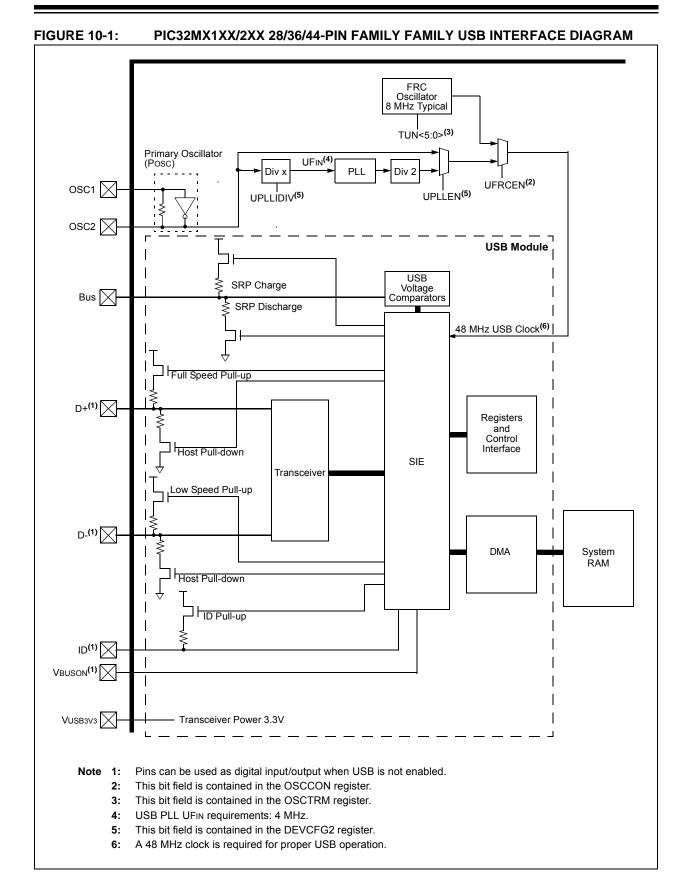

| USB                       |           | 0x5050          |  |  |  |

| PORTA-PORTC               |           | 0x6000          |  |  |  |

| Configuration             | 0xBFC0    | 0x0BF0          |  |  |  |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 |                   | —                | —                |  |  |  |  |  |  |

|              | U-0               | U-0               | U-0               | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |  |  |

| 23:16        | _                 | —                 | _                 | BMX<br>ERRIXI     | BMX<br>ERRICD     | BMX<br>ERRDMA     | BMX<br>ERRDS     | BMX<br>ERRIS     |  |  |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0 U-0           |                   | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 15:8         | —                 | —                 | —                 | -                 | —                 | _                 |                  | —                |  |  |  |  |  |  |

|              | U-0               | R/W-1             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-1            |  |  |  |  |  |  |

| 7:0          | _                 | BMX<br>WSDRM      | _                 | _                 | _                 | BMXARB<2:0>       |                  |                  |  |  |  |  |  |  |

## REGISTER 4-1: BMXCON: BUS MATRIX CONFIGURATION REGISTER

## Legend:

| 5                 |                  |                                    |

|-------------------|------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

## bit 31-21 Unimplemented: Read as '0'

|          | Ommplemented. Read as 0                                                                                                                                                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 20   | BMXERRIXI: Enable Bus Error from IXI bit                                                                                                                                                                                              |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> </ul>                 |

| bit 19   | BMXERRICD: Enable Bus Error from ICD Debug Unit bit                                                                                                                                                                                   |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from ICD</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from ICD</li> </ul>                                       |

| bit 18   | BMXERRDMA: Bus Error from DMA bit                                                                                                                                                                                                     |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from DMA</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from DMA</li> </ul>                                       |

| bit 17   | BMXERRDS: Bus Error from CPU Data Access bit (disabled in Debug mode)                                                                                                                                                                 |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU data access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU data access</li> </ul>               |

| bit 16   | BMXERRIS: Bus Error from CPU Instruction Access bit (disabled in Debug mode)                                                                                                                                                          |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> </ul> |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 6    | BMXWSDRM: CPU Instruction or Data Access from Data RAM Wait State bit                                                                                                                                                                 |

|          | <ul> <li>1 = Data RAM accesses from CPU have one wait state for address setup</li> <li>0 = Data RAM accesses from CPU have zero wait states for address setup</li> </ul>                                                              |

| bit 5-3  | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 2-0  | BMXARB<2:0>: Bus Matrix Arbitration Mode bits                                                                                                                                                                                         |

|          | 111 = Reserved (using these Configuration modes will produce undefined behavior)                                                                                                                                                      |

|          | •                                                                                                                                                                                                                                     |

|          | •                                                                                                                                                                                                                                     |

|          | <ul><li>011 = Reserved (using these Configuration modes will produce undefined behavior)</li><li>010 = Arbitration Mode 2</li></ul>                                                                                                   |

|          | 001 = Arbitration Mode 1 (default)<br>000 = Arbitration Mode 0                                                                                                                                                                        |

|          |                                                                                                                                                                                                                                       |

|              |                   |                      | OULEAIO           |                   | EILEOIOIE         |                       |                  |                  |  |  |

|--------------|-------------------|----------------------|-------------------|-------------------|-------------------|-----------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 24.24        | U-0 U-0           |                      | R/W-y             | R/W-y             | R/W-y             | R/W-0                 | R/W-0            | R/W-1            |  |  |

| 31:24        | —                 | —                    | Р                 | <b>`</b>          | FRCDIV<2:0>       |                       |                  |                  |  |  |

| 00.40        | U-0 R-0           |                      | R-1 R/W-y         |                   | R/W-y             | R/W-y                 | R/W-y            | R/W-y            |  |  |

| 23:16        | —                 | SOSCRDY              | PBDIVRDY          | PBDI              | /<1:0>            | PLLMULT<2:0>          |                  |                  |  |  |

| 45.0         | U-0               | R-0                  | R-0               | R-0               | U-0               | R/W-y                 | R/W-y            | R/W-y            |  |  |

| 15:8         | —                 |                      | COSC<2:0>         |                   | —                 | NOSC<2:0>             |                  |                  |  |  |

| 7:0          | R/W-0             | R-0                  | R-0 R/W-0         |                   | R/W-0             | R/W-0                 | R/W-y            | R/W-0            |  |  |

| 7:0          | CLKLOCK           | ULOCK <sup>(1)</sup> | SLOCK             | SLPEN             | CF                | UFRCEN <sup>(1)</sup> | SOSCEN           | OSWEN            |  |  |

## REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| Legend:         y = Value set from Configuration bits on POR |                  |                      |                    |  |  |  |  |  |

|--------------------------------------------------------------|------------------|----------------------|--------------------|--|--|--|--|--|

| R = Readable bit                                             | W = Writable bit | U = Unimplemented bi | t, read as '0'     |  |  |  |  |  |

| -n = Value at POR                                            | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |  |  |  |  |

## bit 31-30 **Unimplemented:** Read as '0'

#### bit 29-27 **PLLODIV<2:0>:** Output Divider for PLL

- 111 = PLL output divided by 256

- 110 = PLL output divided by 64

- 101 = PLL output divided by 32

- 100 = PLL output divided by 16

- 011 = PLL output divided by 8

- 010 = PLL output divided by 4

- 001 = PLL output divided by 2

- 000 = PLL output divided by 1

#### bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2 (default setting)

- 000 = FRC divided by 1

- bit 23 Unimplemented: Read as '0'

- bit 22 SOSCRDY: Secondary Oscillator (Sosc) Ready Indicator bit

- 1 = The Secondary Oscillator is running and is stable

- 0 = The Secondary Oscillator is still warming up or is turned off

- bit 21 **PBDIVRDY:** Peripheral Bus Clock (PBCLK) Divisor Ready bit

- 1 = PBDIV<1:0> bits can be written

- 0 = PBDIV<1:0> bits cannot be written

- bit 20-19 **PBDIV<1:0>:** Peripheral Bus Clock (PBCLK) Divisor bits

- 11 = PBCLK is SYSCLK divided by 8 (default)

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

Note 1: This bit is only available on PIC32MX2XX devices.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

## TABLE 9-3: DMA CHANNELS 0-3 REGISTER MAP

| ess                         |                                 |                               |                   |            |            |             |             |            |            | Bi          | its     |        |        |        |         |        |        |        |            |

|-----------------------------|---------------------------------|-------------------------------|-------------------|------------|------------|-------------|-------------|------------|------------|-------------|---------|--------|--------|--------|---------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range                     | 31/15             | 30/14      | 29/13      | 28/12       | 27/11       | 26/10      | 25/9       | 24/8        | 23/7    | 22/6   | 21/5   | 20/4   | 19/3    | 18/2   | 17/1   | 16/0   | All Resets |

| 3060                        | DCH0CON                         | 31:16                         | _                 | _          | _          | —           | _           |            | _          | —           | _       | _      | _      | —      | _       | _      |        | -      | 0000       |

| 3000                        | DCHUCON                         | 15:0                          | CHBUSY            | _          | —          | —           | —           |            | —          | CHCHNS      | CHEN    | CHAED  | CHCHN  | CHAEN  | _       | CHEDET | CHPR   | l<1:0> | 0000       |

| 3070                        | DCH0ECON                        | 31:16                         | _                 | _          | —          |             |             | _          | —          | —           |         | •      |        | CHAIR  | Q<7:0>  |        |        |        | 00FF       |

| 3070                        | Denieleon                       | 15:0                          |                   |            |            | CHSIR       | Q<7:0>      |            |            |             | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN  | —      | _      |        | FF00       |

| 3080                        | DCH0INT                         | 31:16                         | —                 | _          | —          | —           | —           | _          | —          | —           | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| 5000                        | DCHOINT                         | 15:0                          | _                 | _          | —          | —           | —           | _          | —          | —           | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3090                        | DCH0SSA                         | 31:16                         |                   |            |            |             |             |            |            | СНАЗА       | <31:0>  |        |        |        |         |        |        |        | 0000       |

| 0000                        | Donooon                         | 15:0                          | 0000              |            |            |             |             |            |            |             |         |        |        |        |         |        |        |        |            |

| 3040                        | DCH0DSA                         | 31:16                         |                   |            |            |             |             |            |            | CHDSA       | \<31·0> |        |        |        |         |        |        |        | 0000       |

| 3070                        | DOI 10DOA                       | DSA 01.10<br>15:0 CHDSA<31:0> |                   |            |            |             |             |            |            |             |         |        | 0000   |        |         |        |        |        |            |

| 30B0                        | DCH0SSIZ                        | 31:16                         | —                 | —          | —          | —           |             | _          | —          | —           | —       | —      | —      |        | —       | —      | —      | —      | 0000       |

| 0000                        | DOI100012                       | 15:0 CHSSIZ<15:0>             |                   |            |            |             |             |            |            |             |         | 0000   |        |        |         |        |        |        |            |

| 3000                        | DCH0DSIZ                        |                               |                   |            |            |             |             |            |            | —           | 0000    |        |        |        |         |        |        |        |            |

| 0000                        | DOMODOL                         | 15:0                          | CHDSIZ<15:0> 0000 |            |            |             |             |            |            |             |         |        |        |        |         |        |        |        |            |

| 3000                        | DCH0SPTR                        | 31:16                         | —                 | —          | —          | —           |             | _          | —          | —           | —       | —      | —      |        | —       | —      | —      | —      | 0000       |

| 0000                        | Donioor IIX                     | 15:0                          |                   |            |            |             |             |            |            | CHSPTI      | R<15:0> |        |        |        |         |        |        |        | 0000       |

| 30E0                        | DCH0DPTR                        | 31:16                         | _                 | _          | —          | —           |             |            | —          | —           | —       | —      | —      | —      | —       | —      | _      | —      | 0000       |

| OOLO                        |                                 | 15:0                          |                   |            |            |             |             |            |            | CHDPT       | R<15:0> |        |        |        |         |        |        |        | 0000       |

| 30E0                        | DCH0CSIZ                        | 31:16                         | _                 | _          | —          | —           |             |            | —          | —           | —       | —      | —      | —      | —       | —      | _      | —      | 0000       |

| 001 0                       | DOI100012                       | 15:0                          |                   |            |            |             |             |            |            | CHCSIZ      | Z<15:0> |        |        |        |         |        |        |        | 0000       |

| 3100                        | DCH0CPTR                        | 31:16                         | _                 | _          | —          | —           |             |            | —          | —           | —       | —      | —      | —      | —       | —      | _      | —      | 0000       |

| 0100                        | Donioor IIX                     | 15:0                          |                   |            |            |             |             |            |            | CHCPT       | R<15:0> |        |        |        |         |        |        |        | 0000       |

| 3110                        | DCH0DAT                         | 31:16                         |                   | _          | —          |             |             |            | —          | —           | —       | —      | —      | —      | —       | —      | _      | —      | 0000       |

| 0110                        | DOITODAT                        | 15:0                          | —                 | —          | —          |             |             |            | —          | —           |         |        |        | CHPDA  | \T<7:0> |        |        |        | 0000       |

| 3120                        | DCH1CON                         | 31:16                         |                   | _          | —          |             |             |            | —          | —           | —       | —      | —      |        | —       | —      |        | —      | 0000       |

| 0120                        | Donnoon                         | 15:0                          | CHBUSY            | —          | —          |             |             |            | —          | CHCHNS      | CHEN    | CHAED  | CHCHN  | CHAEN  | —       | CHEDET | CHPR   | l<1:0> | 0000       |

| 3130                        | DCH1ECON                        | 31:16                         | —                 | _          | —          | —           | —           | _          | —          | —           |         |        |        | CHAIR  | Q<7:0>  |        |        |        | OOFF       |

| 5150                        | DOITILOON                       | 15:0                          |                   |            |            | CHSIR       | Q<7:0>      |            |            |             | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN  | —      | —      | _      | FF00       |

| 3140                        | DCH1INT                         | 31:16                         | _                 | _          | —          |             |             | _          | —          | —           | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| 5140                        | DOLLING                         | 15:0                          | _                 | _          | _          | _           | —           | _          | _          | —           | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3150                        | DCH1SSA                         | 31:16                         |                   |            |            |             |             |            |            | CHSSA       | <31.0>  |        |        |        |         |        |        |        | 0000       |

| 5150                        | DOITIOGA                        | 15:0                          |                   |            |            |             |             |            |            | 0100        |         |        |        |        |         |        |        |        | 0000       |

| 3160                        | DCH1DSA                         | 31:16                         |                   |            |            |             |             |            |            | CHDSA       | 1<31.0> |        |        |        |         |        |        |        | 0000       |

| 3100                        | DONIDSA                         | 15:0                          |                   |            |            |             |             |            |            |             | ~~~~    |        |        |        |         |        |        |        | 0000       |

| Leger                       | od∙ v=u                         | nknown                        | value on R        | leset: — = | unimplemer | nted read a | s '0' Reset | values are | shown in h | nexadecimal |         |        |        |        |         |        |        |        |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

## REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER (CONTINUED)

bit 6 **CRCAPP:** CRC Append Mode bit<sup>(1)</sup>

- 1 = The DMA transfers data from the source into the CRC but NOT to the destination. When a block transfer completes the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC obeying WBO as it writes the data to the destination

- bit 5 **CRCTYP:** CRC Type Selection bit

- 1 = The CRC module will calculate an IP header checksum

- 0 = The CRC module will calculate a LFSR CRC

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 CRCCH<2:0>: CRC Channel Select bits

- 111 = CRC is assigned to Channel 7

- 110 = CRC is assigned to Channel 6

- 101 = CRC is assigned to Channel 5

- 100 = CRC is assigned to Channel 4

- 011 = CRC is assigned to Channel 3

- 010 = CRC is assigned to Channel 2

- 001 = CRC is assigned to Channel 1

- 000 = CRC is assigned to Channel 0

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0                       |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                                    |  |

| 31.24        |                   | _                 |                   | —                 | —                 |                   |                  | _                                      |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                                    |  |

| 23:16        |                   | _                 |                   | —                 | —                 |                   | -                | —                                      |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                                    |  |

| 15.0         | _                 | —                 | _                 | —                 | —                 | -                 | -                | /1 24/16/8/0<br>U-0<br>—<br>U-0<br>U-0 |  |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0                                  |  |

| 7:0          | UTEYE             | UOEMON            | _                 | USBSIDL           | _                 | _                 | _                | UASUSPND                               |  |

## REGISTER 10-20: U1CNFG1: USB CONFIGURATION 1 REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

bit 7 UTEYE: USB Eye-Pattern Test Enable bit

- 1 = Eye-Pattern Test is enabled

- 0 = Eye-Pattern Test is disabled

#### bit 6 **UOEMON:** USB OE Monitor Enable bit

1 = OE signal is active; it indicates intervals during which the D+/D- lines are driving

0 = OE signal is inactive

#### bit 5 Unimplemented: Read as '0'

- bit 4 USBSIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

#### bit 3-1 Unimplemented: Read as '0'

## bit 0 UASUSPND: Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (U1PWRC<1>) in Register 10-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (U1PWRC<1>) to suspend the module, including the USB 48 MHz clock.

## 12.2 Timer1 Control Registers

## TABLE 12-1: TIMER1 REGISTER MAP

| ess                       |                                               | 0         |       | Bits  |       |       |       |       |      |      |        |      |       |        |      |       | s    |      |            |

|---------------------------|-----------------------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|--------|------|-------|--------|------|-------|------|------|------------|

| Virtual Addre<br>(BF80_#) | tual /<br>(BF8<br>(BF8<br>Reg<br>Nan<br>Bit R | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7   | 22/6 | 21/5  | 20/4   | 19/3 | 18/2  | 17/1 | 16/0 | All Resets |

| 0600                      | T1CON                                         | 31:16     | —     | _     | _     | _     | _     | —     | _    | —    | _      | —    | —     | —      | _    | —     | _    | _    | 0000       |

| 0600                      | TICON                                         | 15:0      | ON    | —     | SIDL  | TWDIS | TWIP  | —     | _    | —    | TGATE  | _    | TCKPS | S<1:0> | —    | TSYNC | TCS  | _    | 0000       |

| 0610                      | TMR1                                          | 31:16     | —     | -     | —     | —     | —     | —     | —    | —    | —      | —    | _     | _      | —    | —     | —    | —    | 0000       |

| 0010                      |                                               | 15:0      |       |       |       |       |       |       |      | TMR1 | <15:0> |      |       |        |      |       |      |      | 0000       |

| 0620                      | PR1                                           | 31:16     | —     | _     | _     | _     | _     | —     | -    | —    | —      | _    | —     | _      | _    | _     | _    |      | 0000       |

| 0020                      | FRI                                           | 15:0      |       |       |       |       |       |       |      | PR1< | :15:0> |      |       |        |      |       |      |      | FFFF       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |  |  |  |

|--------------|----------------------|-------------------|---------------------|-------------------|--------------------|-------------------|--------------------|------------------|--|--|--|

| 04.04        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |  |  |  |

| 31:24        | —                    |                   | _                   | —                 | —                  | -                 | —                  | —                |  |  |  |

| 00.40        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |  |  |  |

| 23:16        | —                    | -                 | _                   | —                 | _                  | _                 | —                  | —                |  |  |  |

| 45.0         | R/W-0                | U-0               | R/W-0               | U-0               | U-0                | U-0               | U-0                | U-0              |  |  |  |

| 15:8         | ON <sup>(1,3)</sup>  | _                 | SIDL <sup>(4)</sup> | —                 | —                  | —                 | —                  | —                |  |  |  |

| 7.0          | R/W-0                | R/W-0             | R/W-0               | R/W-0             | R/W-0              | U-0               | R/W-0              | U-0              |  |  |  |

| 7:0          | TGATE <sup>(3)</sup> | Т                 | CKPS<2:0>(3         | 3)                | T32 <sup>(2)</sup> | —                 | TCS <sup>(3)</sup> | —                |  |  |  |

## REGISTER 13-1: TXCON: TYPE B TIMER CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

## bit 31-16 **Unimplemented:** Read as '0'

- bit 15 **ON:** Timer On bit<sup>(1,3)</sup>

- 1 = Module is enabled

- 0 = Module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit<sup>(4)</sup>

- 1 = Discontinue module operation when the device enters Idle mode0 = Continue module operation when the device enters Idle mode

#### bit 12-8 Unimplemented: Read as '0'

- bit 7 **TGATE:** Timer Gated Time Accumulation Enable bit<sup>(3)</sup>

- When TCS = 1:

This bit is ignored and is read as '0'.

When TCS = 0:

1 = Gated time accumulation is enabled

0 = Gated time accumulation is disabled

#### bit 6-4 **TCKPS<2:0>:** Timer Input Clock Prescale Select bits<sup>(3)</sup>

- 111 = 1:256 prescale value

- 110 = 1:64 prescale value

- 101 = 1:32 prescale value

- 100 = 1:16 prescale value

- 011 = 1:8 prescale value

- 010 = 1:4 prescale value

- 001 = 1:2 prescale value

## 000 = 1:1 prescale value

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3, and Timer5). All timer functions are set through the even numbered timers.

- 4: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

NOTES:

## REGISTER 17-3: SPIxSTAT: SPI STATUS REGISTER

bit 3 SPITBE: SPI Transmit Buffer Empty Status bit 1 = Transmit buffer, SPIxTXB is empty 0 = Transmit buffer, SPIxTXB is not empty Automatically set in hardware when SPI transfers data from SPIxTXB to SPIxSR. Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB. bit 2 Unimplemented: Read as '0' bit 1 SPITBF: SPI Transmit Buffer Full Status bit 1 = Transmit not yet started, SPITXB is full 0 = Transmit buffer is not full Standard Buffer Mode: Automatically set in hardware when the core writes to the SPIBUF location, loading SPITXB. Automatically cleared in hardware when the SPI module transfers data from SPITXB to SPISR. Enhanced Buffer Mode: Set when CWPTR + 1 = SRPTR; cleared otherwise bit 0 SPIRBF: SPI Receive Buffer Full Status bit 1 = Receive buffer, SPIxRXB is full

0 = Receive buffer, SPIxRXB is not full

#### Standard Buffer Mode:

Automatically set in hardware when the SPI module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

#### Enhanced Buffer Mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise

## **REGISTER 18-2:** I2CxSTAT: I<sup>2</sup>C STATUS REGISTER (CONTINUED)

| bit 4 | <ul> <li>P: Stop bit</li> <li>1 = Indicates that a Stop bit has been detected last</li> </ul>                                              |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>0 = Stop bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul>         |

| bit 3 | S: Start bit                                                                                                                               |

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul> |

|       | Hardware set or clear when Start, Repeated Start or Stop detected.                                                                         |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                          |

|       | <ul> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave</li> </ul> |

|       | Hardware set or clear after reception of I <sup>2</sup> C device address byte.                                                             |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                        |

|       | 1 = Receive complete, I2CxRCV is full                                                                                                      |

|       | 0 = Receive not complete, I2CxRCV is empty                                                                                                 |

|       | Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.                                       |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                       |

|       | 1 = Transmit in progress, I2CxTRN is full                                                                                                  |

0 = Transmit complete, I2CxTRN is empty

Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.

## 20.1 PMP Control Registers

## TABLE 20-1: PARALLEL MASTER PORT REGISTER MAP

| ess                         |                                 |               | Bits                          |                          |       |       |         |        |                                       |        |      |       |           |       |      |      |      |      |            |

|-----------------------------|---------------------------------|---------------|-------------------------------|--------------------------|-------|-------|---------|--------|---------------------------------------|--------|------|-------|-----------|-------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15                         | 30/14                    | 29/13 | 28/12 | 27/11   | 26/10  | 25/9                                  | 24/8   | 23/7 | 22/6  | 21/5      | 20/4  | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 7000                        | PMCON                           | 31:16         | —                             | —                        | -     | _     |         |        | -                                     | _      | —    | —     | —         |       |      | —    | —    | _    | 0000       |

| 7000                        | 15:0 PMCON                      |               | ON                            | _                        | SIDL  | ADRML | IX<1:0> | PMPTTL | PTWREN                                | PTRDEN | CSF∙ | <1:0> | ALP       |       | CS1P | _    | WRSP | RDSP | 0000       |

| 7010                        | PMMODE                          | 31:16         | —                             | _                        |       | _     | _       |        | _                                     | _      | —    | _     | —         |       | -    | _    | —    | _    | 0000       |

| 7010                        | FININODE                        | 15:0          | BUSY                          | BUSY IRQM<1:0> INCM<1:0> |       |       |         |        | - MODE<1:0> WAITB<1:0> WAITM<3:0> WAI |        |      |       | WAITE     | <1:0> | 0000 |      |      |      |            |

|                             |                                 | 31:16         | _                             | —                        | _     | _     | —       | _      | —                                     | _      | _    | _     | _         | —     | —    | _    | _    | —    | 0000       |

| 7020                        | PMADDR                          | 15:0          | _                             | CS1<br>ADDR14            | _     | _     | _       |        |                                       |        |      | /     | ADDR<10:0 | >     |      |      |      |      | 0000       |

| 7030                        | PMDOUT                          | 31:16<br>15:0 |                               | DATAOUT<31.0>            |       |       |         |        |                                       |        |      |       |           |       | 0000 |      |      |      |            |

| 7040                        | PMDIN                           | 31:16<br>15:0 | DATAIN<31:0>                  |                          |       |       |         |        |                                       |        |      | 0000  |           |       |      |      |      |      |            |

| 7050                        |                                 | 31:16         | _                             | _                        |       | _     | -       |        | -                                     | _      | _    | _     | —         |       |      | _    | _    |      | 0000       |

| 7050                        | PMAEN                           | 15:0          | 5:0 — PTEN14 — — — PTEN<10:0> |                          |       |       |         |        |                                       |        |      | 0000  |           |       |      |      |      |      |            |

| 7060                        | PMSTAT                          | 31:16         |                               | —                        | _     |       | _       | _      | —                                     | _      |      |       | —         | _     | —    |      | —    | _    | 0000       |

| 1000                        | FINISTAT                        | 15:0          | IBF                           | IBOV                     | _     | _     | IB3F    | IB2F   | IB1F                                  | IB0F   | OBE  | OBUF  | —         | _     | OB3E | OB2E | OB1E | OB0E | 008F       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

## REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

- bit 1-0 WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Wait of 4 Трв

- 10 = Wait of 3 Трв

- 01 = Wait of 2 TPB

- 00 = Wait of 1 TPB (default)

For Read operations:

- 11 = Wait of 3 TPB

- 10 = Wait of 2 TPB

- 01 = Wait of 1 ТРВ

- 00 = Wait of 0 TPB (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bit A14 is not subject to auto-increment/decrement if configured as Chip Select CS1.

## 27.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Configuration" Section 32. Section (DS60001124) and 33. "Programming and **Diagnostics**" (DS60001129), which are available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family devices include the following features intended to maximize application flexibility, reliability and minimize cost through elimination of external components.

- Flexible device configuration

- Joint Test Action Group (JTAG) interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

## 27.1 Configuration Bits

The Configuration bits can be programmed using the following registers to select various device configurations.

- DEVCFG0: Device Configuration Word 0

- DEVCFG1: Device Configuration Word 1

- DEVCFG2: Device Configuration Word 2

- DEVCFG3: Device Configuration Word 3

- · CFGCON: Configuration Control Register

In addition, the DEVID register (Register 27-6) provides device and revision information.

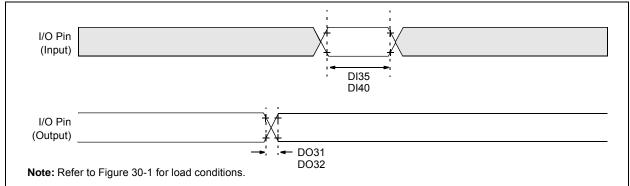

## FIGURE 30-3: I/O TIMING CHARACTERISTICS

## TABLE 30-21: I/O TIMING REQUIREMENTS

| AC CHAP       | RACTERIS | STICS                | Standard Ope<br>(unless other<br>Operating terr | wise state |                        | ≤ +85°C fc | or Industria |            |

|---------------|----------|----------------------|-------------------------------------------------|------------|------------------------|------------|--------------|------------|

| Param.<br>No. | Symbol   | Characteris          | stics <sup>(2)</sup>                            | Min.       | Typical <sup>(1)</sup> | Max.       | Units        | Conditions |

| DO31          | TIOR     | Port Output Rise Tir |                                                 | 5          | 15                     | ns         | Vdd < 2.5V   |            |

|               |          |                      |                                                 | 5          | 10                     | ns         | Vdd > 2.5V   |            |

| DO32          | TIOF     | Port Output Fall Tim | е                                               | _          | 5                      | 15         | ns           | Vdd < 2.5V |

|               |          |                      |                                                 |            | 5                      | 10         | ns           | VDD > 2.5V |

| DI35          | Tinp     | INTx Pin High or Lo  | 10                                              | _          | _                      | ns         | _            |            |

| DI40          | Trbp     | CNx High or Low Tir  | me (input)                                      | 2          | _                      |            | TSYSCLK      |            |

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: This parameter is characterized, but not tested in manufacturing.

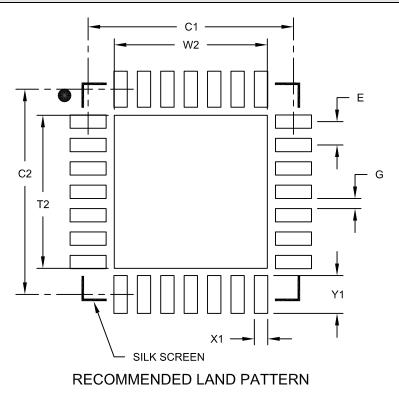

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS     |      |      |      |  |

|----------------------------|-----------------|------|------|------|--|

| Dimensi                    | MIN             | NOM  | MAX  |      |  |

| Contact Pitch              | Contact Pitch E |      |      |      |  |

| Optional Center Pad Width  | W2              |      |      | 4.25 |  |

| Optional Center Pad Length | T2              |      |      | 4.25 |  |

| Contact Pad Spacing        | C1              |      | 5.70 |      |  |

| Contact Pad Spacing        | C2              |      | 5.70 |      |  |

| Contact Pad Width (X28)    | X1              |      |      | 0.37 |  |

| Contact Pad Length (X28)   | Y1              |      |      | 1.00 |  |

| Distance Between Pads      | G               | 0.20 |      |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A

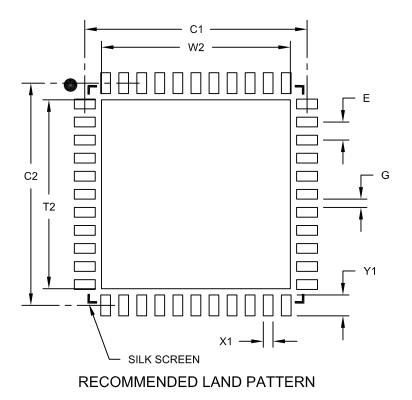

## 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |          |      |      |  |

|----------------------------|-------------|----------|------|------|--|

| Dimensior                  | MIN         | NOM      | MAX  |      |  |

| Contact Pitch              |             | 0.65 BSC |      |      |  |

| Optional Center Pad Width  | W2          |          |      | 6.80 |  |

| Optional Center Pad Length | T2          |          |      | 6.80 |  |

| Contact Pad Spacing        | C1          |          | 8.00 |      |  |

| Contact Pad Spacing        | C2          |          | 8.00 |      |  |

| Contact Pad Width (X44)    | X1          |          |      | 0.35 |  |

| Contact Pad Length (X44)   | Y1          |          |      | 0.80 |  |

| Distance Between Pads      | G           | 0.25     |      |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103A