#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

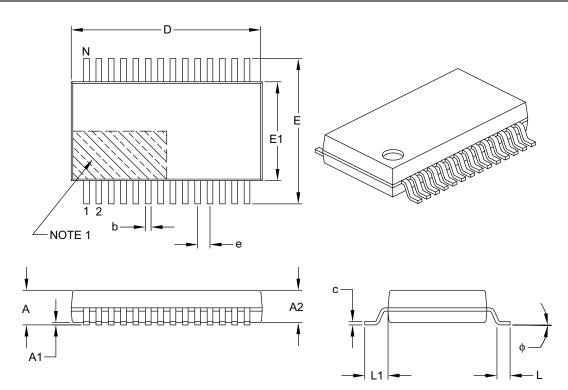

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f256d-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 13: PIN NAMES FOR 44-PIN GENERAL PURPOSE DEVICES

# 44-PIN VTLA (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX110F016D PIC32MX120F032D PIC32MX130F064D PIC32MX130F256D PIC32MX150F128D PIC32MX170F256D

| Pin # | Full Pin Name                                  | Pin # | Full Pin Name                        |

|-------|------------------------------------------------|-------|--------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                       | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 |

| 2     | RPC6/PMA1/RC6                                  | 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3   |

| 3     | RPC7/PMA0/RC7                                  | 25    | AN6/RPC0/RC0                         |

| 4     | RPC8/PMA5/RC8                                  | 26    | AN7/RPC1/RC1                         |

| 5     | RPC9/CTED7/PMA6/RC9                            | 27    | AN8/RPC2/PMA2/RC2                    |

| 6     | Vss                                            | 28    | VDD                                  |

| 7     | VCAP                                           | 29    | Vss                                  |

| 8     | PGED2/RPB10/CTED11/PMD2/RB10                   | 30    | OSC1/CLKI/RPA2/RA2                   |

| 9     | PGEC2/RPB11/PMD1/RB11                          | 31    | OSC2/CLKO/RPA3/RA3                   |

| 10    | AN12/PMD0/RB12                                 | 32    | TDO/RPA8/PMA8/RA8                    |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                     | 33    | SOSCI/RPB4/RB4                       |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10           | 34    | SOSCO/RPA4/T1CK/CTED9/RA4            |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7       | 35    | TDI/RPA9/PMA9/RA9                    |

| 14    | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 | 36    | RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          | 37    | RPC4/PMA4/RC4                        |

| 16    | AVss                                           | 38    | RPC5/PMA3/RC5                        |

| 17    | AVDD                                           | 39    | Vss                                  |

| 18    | MCLR                                           | 40    | VDD                                  |

| 19    | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          | 41    | PGED3/RPB5/PMD7/RB5                  |

| 20    | Vref-/CVref-/AN1/RPA1/CTED2/RA1                | 42    | PGEC3/RPB6/PMD6/RB6                  |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0           | 43    | RPB7/CTED3/PMD5/INT0/RB7             |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1          | 44    | RPB8/SCL1/CTED10/PMD4/RB8            |

44

1

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

5: Shaded pins are 5V tolerant.

# 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUs

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

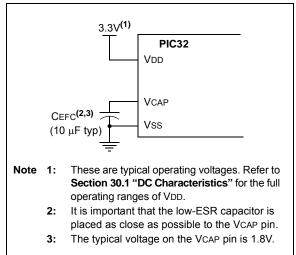

# 2.1 Basic Connection Requirements

Getting started with the PIC32MX1XX/2XX 28/36/44pin Family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

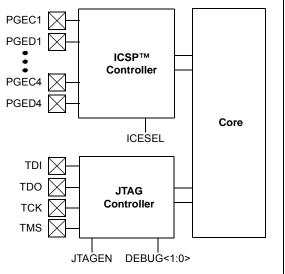

- PGECx/PGEDx pins, used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes (see **2.5** "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.7 "External Oscillator Pins")

The following pins may be required:

• VREF+/VREF- pins – used when external voltage reference for the ADC module is implemented

Note: The AVDD and AVss pins must be connected, regardless of ADC use and the ADC voltage reference source.

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1  $\mu$ F (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

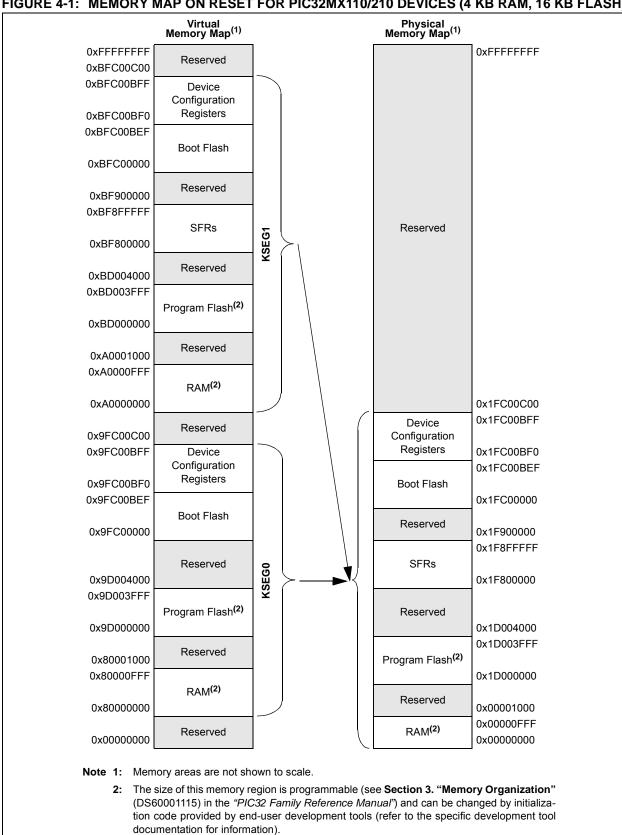

### FIGURE 4-1: MEMORY MAP ON RESET FOR PIC32MX110/210 DEVICES (4 KB RAM, 16 KB FLASH)

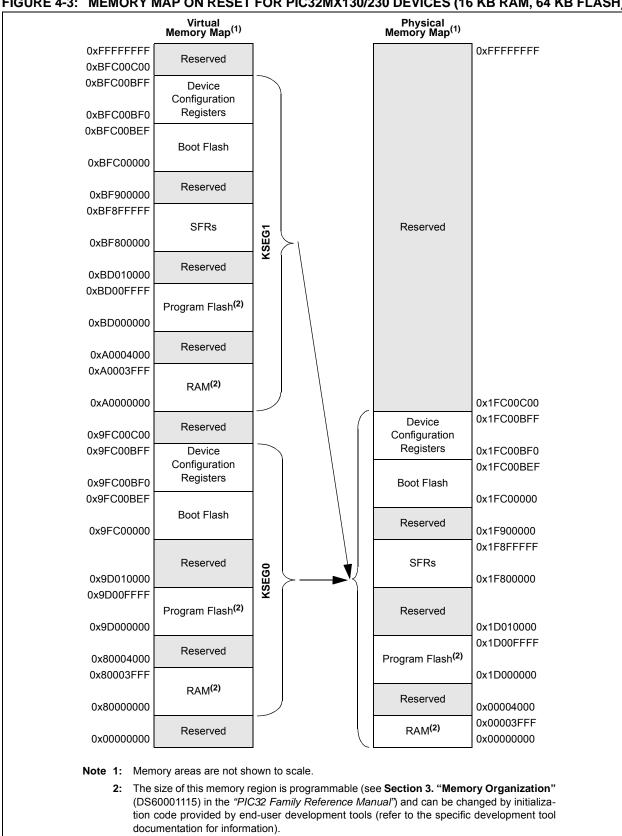

#### FIGURE 4-3: MEMORY MAP ON RESET FOR PIC32MX130/230 DEVICES (16 KB RAM, 64 KB FLASH)

# TABLE 9-3: DMA CHANNELS 0-3 REGISTER MAP (CONTINUED)

| ess                         |                                 | ē             |       |       |       |       | -      |       |      | Bi     | ts      |        |        |        |              |        |        |        | s          |

|-----------------------------|---------------------------------|---------------|-------|-------|-------|-------|--------|-------|------|--------|---------|--------|--------|--------|--------------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7    | 22/6   | 21/5   | 20/4   | 19/3         | 18/2   | 17/1   | 16/0   | All Resets |

| 3280                        | DCH2CPTR                        | 31:16         | —     | _     | _     | _     |        | _     |      | —      |         | _      | _      |        |              | _      | _      |        | 0000       |

| 5200                        | DONZOFIK                        | 15:0          |       |       |       |       |        |       |      |        |         |        |        |        |              |        |        |        | 0000       |

| 3290                        | DCH2DAT                         | 31:16         | _     | _     | —     | —     |        | _     |      | —      | _       | _      | —      | _      | —            | _      | _      |        | 0000       |

| 3290                        | DCHZDAI                         | 15:0          | _     |       | _     | _     |        | -     |      | -      |         |        |        | CHPDA  | AT<7:0>      |        |        |        | 0000       |

| 2240                        | DCH3CON                         | 31:16         | _     | _     | _     | _     | _      | _     | _    | _      | _       | _      | _      | _      | _            | _      | _      | _      | 0000       |

| 32A0                        | DCH3CON                         | 15:0          |       |       |       |       |        |       |      |        |         |        | l<1:0> | 0000   |              |        |        |        |            |

| 3280                        | 2B0 DCH3ECON 31:16 CHAIRQ<7:0>  |               |       |       |       |       |        |       |      |        |         | OOFF   |        |        |              |        |        |        |            |

| 5200                        |                                 | 15:0          |       |       |       | CHSIR | Q<7:0> |       |      |        | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN       | _      | _      | _      | FF00       |

| 32C0                        | DCH3INT                         | 31:16         | —     | —     | —     | —     | -      | _     | -    | —      | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE       | CHCCIE | CHTAIE | CHERIE | 0000       |

| 0200                        |                                 | 15:0          | —     |       |       | _     | —      | _     | —    | —      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF       | CHCCIF | CHTAIF | CHERIF | 0000       |

| 32D0                        | DCH3SSA                         | 31:16<br>15:0 |       |       |       |       |        |       |      | CHSSA  | <31:0>  |        |        |        |              |        |        |        | 0000       |

|                             |                                 | 31:16         |       |       |       |       |        |       |      |        |         |        |        |        |              |        |        |        | 0000       |

| 32E0                        | DCH3DSA                         | 15:0          |       |       |       |       |        |       |      | CHDSA  | <31:0>  |        |        |        |              |        |        |        | 0000       |

| 0050                        | 00100017                        | 31:16         |       | _     |       |       | _      | _     | _    |        |         |        |        |        |              | _      |        | _      | 0000       |

| 32FU                        | DCH3SSIZ                        | 15:0          |       |       |       |       |        |       |      | CHSSIZ | 2<15:0> |        |        |        |              |        |        |        | 0000       |

| 2200                        | DCH3DSIZ                        | 31:16         | —     | —     | —     | —     | _      | —     | _    | —      | _       | —      | —      | —      | —            | _      | —      | _      | 0000       |

| 3300                        | DCH3D3IZ                        | 15:0          |       |       |       |       |        |       |      | CHDSIZ | 2<15:0> |        |        |        |              |        |        |        | 0000       |

| 3310                        | DCH3SPTR                        | 31:16         | —     | _     | —     | _     |        |       |      | _      | —       |        | _      |        | _            |        |        |        | 0000       |

| 3310                        | DOI IJOF I K                    | 15:0          |       |       |       |       |        |       |      | CHSPTF | ۲<15:0> |        |        |        |              |        |        |        | 0000       |

| 3320                        | DCH3DPTR                        | 31:16         | —     | —     | —     | —     | _      | _     | _    | —      | _       | _      | —      | —      | —            | _      | —      | _      | 0000       |

| 0020                        |                                 | 15:0          |       |       |       |       |        |       |      | CHDPT  | R<15:0> |        |        |        |              |        |        |        | 0000       |

| 3330                        | <b>DCH3CSIZ</b>                 | 31:16         | —     | _     | —     | —     | —      | —     | —    | —      | —       | —      | —      | —      | —            | —      | —      | —      | 0000       |

|                             |                                 | 15:0          |       |       |       |       |        |       |      | CHCSIZ | 2<15:0> |        |        |        |              |        |        |        | 0000       |

| 3340                        | DCH3CPTR                        | 31:16         | _     | —     | —     | —     | _      | —     | _    | —      | —       | —      | —      | —      | —            | —      | —      | _      | 0000       |

|                             |                                 | 15:0          |       |       |       |       |        |       |      | CHCPT  | ≺<15:0> |        |        |        |              |        |        |        | 0000       |

| 3350                        | DCH3DAT                         | 31:16         | —     | _     | —     | _     | _      | _     | —    | _      | _       | —      | —      | -      | —<br>T :7 0: | —      | —      | —      | 0000       |

| <u> </u>                    |                                 | 15:0          | —     | —     | —     | —     | —      | —     | —    | _      |         |        |        | CHPDA  | AT<7:0>      |        |        |        | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

# REGISTER 10-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 **PPBRST:** Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the EVEN Buffer Descriptor banks

- 0 = Even/Odd buffer pointers are not Reset

- bit 0 USBEN: USB Module Enable bit<sup>(4)</sup>

- 1 = USB module and supporting circuitry is enabled

- 0 = USB module and supporting circuitry is disabled

SOFEN: SOF Enable bit<sup>(5)</sup>

- 1 = SOF token is sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   | —                 |                   |                   |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 |                   | —                 | -                 |                   |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | -                 | —                 | -                 | —                 | _                 | -                 | -                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | LSPDEN            |                   |                   | D                 | EVADDR<6:0        | >                 |                  |                  |

# REGISTER 10-12: U1ADDR: USB ADDRESS REGISTER

# Legend:

| U                 |                  |                                    |                    |  |  |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |  |  |

bit 31-8 Unimplemented: Read as '0'

bit 7 LSPDEN: Low-Speed Enable Indicator bit

1 = Next token command to be executed at Low-Speed

0 = Next token command to be executed at Full-Speed

bit 6-0 **DEVADDR<6:0>:** 7-bit USB Device Address bits

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |  |

| 31:24        | —                 | —                 | —                 | _                 | —                 | _                 | —                |                  |  |  |  |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |  |

| 23.10        | —                 | —                 | —                 | _                 | —                 | _                 | —                |                  |  |  |  |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |  |

| 15.0         | —                 | —                 | —                 | -                 | —                 | _                 | —                | -                |  |  |  |  |  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |  |  |

|              |                   |                   |                   | FRML              | <7:0>             |                   |                  |                  |  |  |  |  |  |  |  |

#### REGISTER 10-13: U1FRML: USB FRAME NUMBER LOW REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **FRML<7:0>:** The 11-bit Frame Number Lower bits

The register bits are updated with the current frame number whenever a SOF TOKEN is received.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| REGISTE      | N 15-1. IX           | CON. TIFL         |                     |                   | LOISTEN            |                   |                    |                  |

|--------------|----------------------|-------------------|---------------------|-------------------|--------------------|-------------------|--------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |

| 21.24        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |

| 31:24        | —                    |                   | —                   | -                 | —                  | -                 | —                  | —                |

| 00.40        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |

| 23:16        | —                    | -                 | —                   | _                 | _                  | _                 | —                  | —                |

| 45.0         | R/W-0                | U-0               | R/W-0               | U-0               | U-0                | U-0               | U-0                | U-0              |

| 15:8         | ON <sup>(1,3)</sup>  | _                 | SIDL <sup>(4)</sup> | _                 | —                  | —                 | —                  | —                |

| 7:0          | R/W-0                | R/W-0             | R/W-0               | R/W-0             | R/W-0              | U-0               | R/W-0              | U-0              |

| 7:0          | TGATE <sup>(3)</sup> | Т                 | CKPS<2:0>(          | 3)                | T32 <sup>(2)</sup> | —                 | TCS <sup>(3)</sup> | —                |

### REGISTER 13-1: TXCON: TYPE B TIMER CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

#### bit 31-16 **Unimplemented:** Read as '0'

- bit 15 **ON:** Timer On bit<sup>(1,3)</sup>

- 1 = Module is enabled

- 0 = Module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit<sup>(4)</sup>

- 1 = Discontinue module operation when the device enters Idle mode0 = Continue module operation when the device enters Idle mode

#### bit 12-8 Unimplemented: Read as '0'

- bit 7 **TGATE:** Timer Gated Time Accumulation Enable bit<sup>(3)</sup>

- When TCS = 1:

This bit is ignored and is read as '0'.

When TCS = 0:

1 = Gated time accumulation is enabled

0 = Gated time accumulation is disabled

#### bit 6-4 **TCKPS<2:0>:** Timer Input Clock Prescale Select bits<sup>(3)</sup>

- 111 = 1:256 prescale value

- 110 = 1:64 prescale value

- 101 = 1:32 prescale value

- 100 = 1:16 prescale value

- 011 = 1:8 prescale value

- 010 = 1:4 prescale value

- 001 = 1:2 prescale value

#### 000 = 1:1 prescale value

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3, and Timer5). All timer functions are set through the even numbered timers.

- 4: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

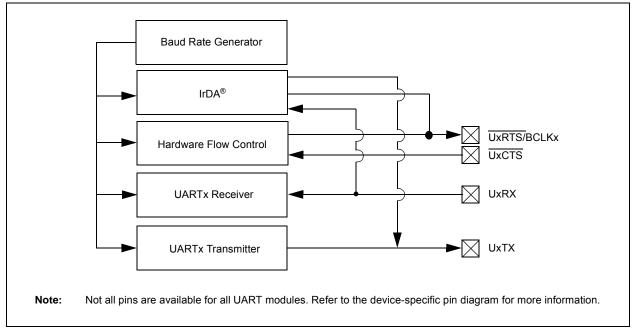

# 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The UART module is one of the serial I/O modules available in PIC32MX1XX/2XX 28/36/44-pin Family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN, and IrDA<sup>®</sup>. The UART module also supports the hardware flow control option, with UXCTS and UXRTS pins, and also includes an IrDA encoder and decoder.

Key features of the UART module include:

- Full-duplex, 8-bit or 9-bit data transmission

- Even, Odd or No Parity options (for 8-bit data)

- · One or two Stop bits

- Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 38 bps to 12.5 Mbps at 50 MHz

- 8-level deep First In First Out (FIFO) transmit data buffer

- 8-level deep FIFO receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (9th bit = 1)

- · Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- · LIN protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 19-1 illustrates a simplified block diagram of the UART module.

#### FIGURE 19-1: UART SIMPLIFIED BLOCK DIAGRAM

# 19.1 UART Control Registers

# TABLE 19-1: UART1 AND UART2 REGISTER MAP

| np for point | ess                         |                  | 6                                   |                                    |        |        |       |        |       |                  | Bi          | ts          |         |        |             |       |       |        |       | 6          |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------|-------------------------------------|------------------------------------|--------|--------|-------|--------|-------|------------------|-------------|-------------|---------|--------|-------------|-------|-------|--------|-------|------------|--|--|

| 6000      0 MODE      15.0      ON      -      SIDL      IREN      RTSMD      -      UEN<1:0>      WAKE      LPBACK      ABAUD      RXINV      BRGH      PDEL<1:0>      STSL      0.00        610      U1STA(1)      31:16      -      -      -      -      ADM_EN      VERSE      LPBACK      ABAUD      RXINV      BRGH      PDEL<1:0>      STSL      0.00        600      U1STA(1)      15.0      UTXINV      URXEN      UTXENK      UTXEN      TRM      URXEN      TRMT      URXEN      ADDEN      RIDE      PERR      PERR      OER      URXDA      0100        600      U1TXREG      31:16      -      -      -      -      -      -      -      -      0000        6100      U1RXREG      31:16      -      -      -      -      -      -      -      -      -      0000        6100      U1RXREG      31:16      -      -      -      -      -      -      -      -      0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range                           | 31/15                              | 30/14  | 29/13  | 28/12 | 27/11  | 26/10 | 25/9             | 24/8        | 23/7        | 22/6    | 21/5   | 20/4        | 19/3  | 18/2  | 17/1   | 16/0  | All Resets |  |  |

| 610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610      610 <td>6000</td> <td></td> <td>31:16</td> <td></td> <td></td> <td>_</td> <td>_</td> <td>—</td> <td>_</td> <td></td> <td>_</td> <td>_</td> <td>—</td> <td></td> <td></td> <td>—</td> <td>_</td> <td>_</td> <td>_</td> <td>0000</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6000                        |                  | 31:16                               |                                    |        | _      | _     | —      | _     |                  | _           | _           | —       |        |             | —     | _     | _      | _     | 0000       |  |  |

| 600      UTXIST      15.0      UTXIST      UTXINV      UTXRNV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0000                        | OTWODE           | 15:0                                | ON                                 |        | SIDL   | IREN  | RTSMD  | —     | UEN              | -           | WAKE        | LPBACK  | ABAUD  | RXINV       | BRGH  | PDSEI | L<1:0> | STSEL | 0000       |  |  |

| 15:0      15:0      01XBE      0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6010                        | 111STA(1)        | 31:16                               | _                                  | _      | _      | —     | —      | _     | ADM_EN ADDR<7:0> |             |             |         | 2<7:0> |             |       |       | 0000   |       |            |  |  |

| 600      UTXRE      1      -      -      -      -      -      -      -      -      -      -      000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000      0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0010                        | UIUIA            | 15:0                                | UTXISE                             | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF            | TRMT        | URXIS       | EL<1:0> | ADDEN  | RIDLE       | PERR  | FERR  | OERR   | URXDA | 0110       |  |  |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6020                        |                  | 31:16                               | —                                  | -      | —      | _     | —      | —     | -                | —           | _           | —       | —      | _           | _     | _     | —      | _     | 0000       |  |  |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0020                        | UTTAKLG          | 15:0                                | _                                  |        | _      |       | _      | -     |                  |             |             |         | Tra    | nsmit Regis | ster  |       |        |       | 0000       |  |  |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6030                        |                  | 31:16                               | _                                  |        | _      |       | _      | -     |                  | _           |             |         |        |             |       | 0000  |        |       |            |  |  |

| 600    11    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    1.50    <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0030                        | UINAREG          | 15:0                                | _                                  |        | _      |       | _      | -     |                  |             |             |         | Re     | ceive Regis | ster  |       |        |       | 0000       |  |  |

| 15:0      Bale Rate Generator Present      1000        6200      16:0 $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6040                        | 01               | 31:16                               | -                                  |        | -      |       | _      | -     |                  | —           |             | _       | -      |             | -     |       | -      |       | 0000       |  |  |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00+0                        | 0 IDIXO          | 15:0                                |                                    |        |        |       |        |       | Bau              | d Rate Gene | erator Pres | caler   |        |             |       | 0     |        |       |            |  |  |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6200                        | 112MODE(1)       | 31:16                               | _                                  | _      | _      | —     | —      | _     | _                | —           | -           | —       | _      | -           | —     | _     | —      | _     | 0000       |  |  |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0200                        | OZINODL          | 15:0                                | ON                                 |        | SIDL   | IREN  | RTSMD  | —     | UEN              | <1:0>       | WAKE        | LPBACK  | ABAUD  | RXINV       | BRGH  | PDSE  | L<1:0> | STSEL | 0000       |  |  |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6210                        | 112974(1)        | 31:16                               | _                                  |        | _      |       | _      | -     |                  | ADM_EN      |             |         |        | ADDR        | <7:0> |       |        |       | 0000       |  |  |

| 6220  U2TXREG  15:0  -  -  -  -  -  -  -  -  000    6230  U2RXREG  31:16  -  -  -  -  -  -  -  -  0000    6230  U2RXREG  31:16  -  -  -  -  -  -  -  -  0000    6240  U2BRG(1)  31:16  -  -  -  -  -  -  -  0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0210                        | 0231A. /         | 15:0                                | UTXISE                             | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF            | TRMT        | URXISE      | EL<1:0> | ADDEN  | RIDLE       | PERR  | FERR  | OERR   | URXDA | 0110       |  |  |

| 150  -  -  -  -  -  -  -  -  000    620  U2RXEG  31:16  -  -  -  -  -  -  -  -  000    620  U2BRG(1)  31:16  -  -  -  -  -  -  -  -  -  000    6240  U2BRG(1)  31:16  -  -  -  -  -  -  -  -  000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6220                        |                  | 31:16                               | _                                  |        | _      |       | _      | -     |                  | _           |             | _       | _      |             | -     |       | _      |       | 0000       |  |  |

| 6230  U2RXREG  -  -  -  -  -  -  -  0000    6240  U2BRG(1)  31:16  -  -  -  -  -  -  -  0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0220                        | UZTARLO          | 15:0                                | _                                  |        | _      |       | _      | _     |                  |             |             |         | Tra    | nsmit Regis | ster  |       |        |       | 0000       |  |  |

| 150    -    -    -    -    -    -    -    0000      6240    U2BRG <sup>(1)</sup> 31:16    -    -    -    -    -    -    -    -    0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6230                        |                  | 31:16                               | _                                  | _      | _      | _     | _      | _     | _                | _           | _           | _       | _      | _           | _     | _     | _      | _     | 0000       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0230                        | UZNAREG          | 15:0 — — — — — — — Receive Register |                                    |        |        |       |        |       | 0000             |             |             |         |        |             |       |       |        |       |            |  |  |

| 02240  02000  15:0  Baud Rate Generator Prescaler  0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6240                        |                  | 31:16                               | _                                  | _      | _      | _     | _      | _     | _                | _           | _           | _       | _      | _           | _     | _     | _      | _     | 0000       |  |  |