Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f256d-v-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 10: PIN NAMES FOR 44-PIN USB DEVICES

#### 44-PIN QFN (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX210F016D PIC32MX220F032D PIC32MX230F064D PIC32MX230F256D PIC32MX250F128D PIC32MX270F256D

|       |                                                  |       | 44 1                                      |

|-------|--------------------------------------------------|-------|-------------------------------------------|

| Pin # | Full Pin Name                                    | Pin # | Full Pin Name                             |

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                         | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 2     | RPC6/PMA1/RC6                                    | 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 3     | RPC7/PMA0/RC7                                    | 25    | AN6/RPC0/RC0                              |

| 4     | RPC8/PMA5/RC8                                    | 26    | AN7/RPC1/RC1                              |

| 5     | RPC9/CTED7/PMA6/RC9                              | 27    | AN8/RPC2/PMA2/RC2                         |

| 6     | Vss                                              | 28    | Vdd                                       |

| 7     | VCAP                                             | 29    | Vss                                       |

| 8     | PGED2/RPB10/D+/CTED11/RB10                       | 30    | OSC1/CLKI/RPA2/RA2                        |

| 9     | PGEC2/RPB11/D-/RB11                              | 31    | OSC2/CLKO/RPA3/RA3                        |

| 10    | VUSB3V3                                          | 32    | TDO/RPA8/PMA8/RA8                         |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                       | 33    | SOSCI/RPB4/RB4                            |

| 12    | PGED4/TMS/PMA10/RA10                             | 34    | SOSCO/RPA4/T1CK/CTED9/RA4                 |

| 13    | PGEC4/TCK/CTED8/PMA7/RA7                         | 35    | TDI/RPA9/PMA9/RA9                         |

| 14    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 | 36    | AN12/RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            | 37    | RPC4/PMA4/RC4                             |

| 16    | AVss                                             | 38    | RPC5/PMA3/RC5                             |

| 17    | AVDD                                             | 39    | Vss                                       |

| 18    | MCLR                                             | 40    | Vdd                                       |

| 19    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 | 41    | RPB5/USBID/RB5                            |

| 20    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       | 42    | VBUS                                      |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        | 43    | RPB7/CTED3/PMD5/INT0/RB7                  |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       | 44    | RPB8/SCL1/CTED10/PMD4/RB8                 |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

5: Shaded pins are 5V tolerant.

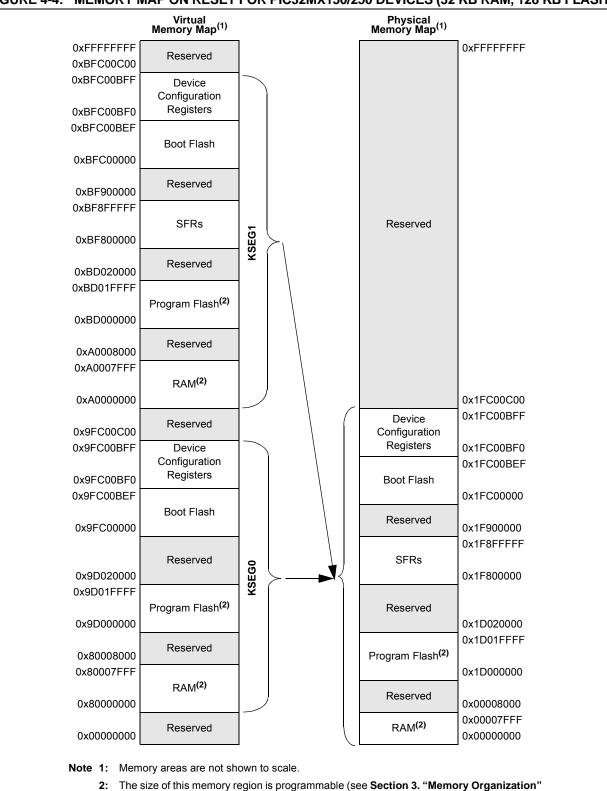

#### FIGURE 4-4: MEMORY MAP ON RESET FOR PIC32MX150/250 DEVICES (32 KB RAM, 128 KB FLASH)

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS60001115) in the "*PIC32 Family Reference Manual*") and can be changed by initialization code provided by end-user development tools (refer to the specific development tool documentation for information).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 |                   | —                | —                |  |

|              | U-0               | U-0               | U-0               | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |

| 23:16        | _                 | —                 | _                 | BMX<br>ERRIXI     | BMX<br>ERRICD     | BMX<br>ERRDMA     | BMX<br>ERRDS     | BMX<br>ERRIS     |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         | —                 | —                 | —                 | -                 | —                 | _                 |                  | —                |  |

|              | U-0               | R/W-1             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-1            |  |

| 7:0          | _                 | BMX<br>WSDRM      | _                 | _                 | _                 | E                 | 3MXARB<2:0       | >                |  |

## REGISTER 4-1: BMXCON: BUS MATRIX CONFIGURATION REGISTER

#### Legend:

| 5                 |                  |                                    |

|-------------------|------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

## bit 31-21 Unimplemented: Read as '0'

|          | Ommplemented. Read as 0                                                                                                                                                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 20   | BMXERRIXI: Enable Bus Error from IXI bit                                                                                                                                                                                              |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> </ul>                 |

| bit 19   | BMXERRICD: Enable Bus Error from ICD Debug Unit bit                                                                                                                                                                                   |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from ICD</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from ICD</li> </ul>                                       |

| bit 18   | BMXERRDMA: Bus Error from DMA bit                                                                                                                                                                                                     |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from DMA</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from DMA</li> </ul>                                       |

| bit 17   | BMXERRDS: Bus Error from CPU Data Access bit (disabled in Debug mode)                                                                                                                                                                 |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU data access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU data access</li> </ul>               |

| bit 16   | BMXERRIS: Bus Error from CPU Instruction Access bit (disabled in Debug mode)                                                                                                                                                          |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> </ul> |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 6    | BMXWSDRM: CPU Instruction or Data Access from Data RAM Wait State bit                                                                                                                                                                 |

|          | <ul> <li>1 = Data RAM accesses from CPU have one wait state for address setup</li> <li>0 = Data RAM accesses from CPU have zero wait states for address setup</li> </ul>                                                              |

| bit 5-3  | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 2-0  | BMXARB<2:0>: Bus Matrix Arbitration Mode bits                                                                                                                                                                                         |

|          | 111 = Reserved (using these Configuration modes will produce undefined behavior)                                                                                                                                                      |

|          | •                                                                                                                                                                                                                                     |

|          | •                                                                                                                                                                                                                                     |

|          | <ul><li>011 = Reserved (using these Configuration modes will produce undefined behavior)</li><li>010 = Arbitration Mode 2</li></ul>                                                                                                   |

|          | 001 = Arbitration Mode 1 (default)<br>000 = Arbitration Mode 0                                                                                                                                                                        |

|          |                                                                                                                                                                                                                                       |

## 5.1 Flash Controller Control Registers

## TABLE 5-1: FLASH CONTROLLER REGISTER MAP

| ess                         |                        | 0         |       |                  |       |        |         |       |      | Bit     | s       |      |      |      |      |      |        |      | 6          |

|-----------------------------|------------------------|-----------|-------|------------------|-------|--------|---------|-------|------|---------|---------|------|------|------|------|------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range | 31/15 | 30/14            | 29/13 | 28/12  | 27/11   | 26/10 | 25/9 | 24/8    | 23/7    | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| F400                        | NVMCON <sup>(1)</sup>  | 31:16     | —     | —                | -     | —      | —       | —     | _    | -       | —       | _    | —    | _    | —    | —    | -      | -    | 0000       |

| F400                        | INVIVICOIN**           | 15:0      | WR    | WREN             | WRERR | LVDERR | LVDSTAT | _     |      | —       |         | —    | —    | —    |      | NVMO | P<3:0> |      | 0000       |

| F410                        | NVMKEY                 | 31:16     |       |                  |       |        |         |       |      | NVMKEY  | <31·0>  |      |      |      |      |      |        |      | 0000       |

| 1410                        |                        | 15:0      |       |                  |       |        |         |       |      |         | ~51.02  |      |      |      |      |      |        |      | 0000       |

| F420                        | NVMADDR <sup>(1)</sup> | 31:16     |       |                  |       |        |         |       |      | NVMADD  | P<31.0> |      |      |      |      |      |        |      | 0000       |

| 1 420                       | NVINADDR               | 15:0      |       |                  |       |        |         |       |      | NVINADD | N~51.02 |      |      |      |      |      |        |      | 0000       |

| F430                        | NVMDATA                | 31:16     |       |                  |       |        |         |       |      |         |         |      | 0000 |      |      |      |        |      |            |

| 1 430                       |                        | 15:0      |       | NVMDATA<31:0>    |       |        |         |       |      |         |         |      | 0000 |      |      |      |        |      |            |

| E440                        | NVMSRCADDR             | 31:16     |       |                  |       |        |         |       |      |         |         | 0000 |      |      |      |      |        |      |            |

| 1 440                       | NVINGRCADDR            | 15:0      |       | NVMSRCADDR<31:0> |       |        |         |       |      |         |         | 0000 |      |      |      |      |        |      |            |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| 24.04        | U-0                | U-0                |

| 31:24        | _                 | _                 | _                 | _                 | _                 |                   | -                  | —                  |

| 22:16        | U-0                | U-0                |

| 23:16        | _                 | _                 | _                 | _                 | _                 |                   | -                  | —                  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS          | R/W-0              |

| 15:8         |                   | _                 | _                 | -                 | _                 | _                 | CMR                | VREGS              |

| 7.0          | R/W-0, HS         | R/W-0, HS         | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-1, HS          | R/W-1, HS          |

| 7:0          | EXTR              | SWR               | _                 | WDTO              | SLEEP             | IDLE              | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |

### REGISTER 6-1: RCON: RESET CONTROL REGISTER

| Legend:           | HS = Set by hardware |                           |                    |

|-------------------|----------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-10 Unimplemented: Read as '0'

| bit 9 | CMR: Configuration Mismatch Reset Flag bit             |

|-------|--------------------------------------------------------|

|       | 1 = Configuration mismatch Reset has occurred          |

|       | 0 = Configuration mismatch Reset has not occurred      |

| bit 8 | VREGS: Voltage Regulator Standby Enable bit            |

|       | 1 = Regulator is enabled and is on during Sleep mode   |

|       | 0 = Regulator is disabled and is off during Sleep mode |

| bit 7 | EXTR: External Reset (MCLR) Pin Flag bit               |

|       | 1 = Master Clear (pin) Reset has occurred              |

|       | 0 = Master Clear (pin) Reset has not occurred          |

| bit 6 | SWR: Software Reset Flag bit                           |

|       | 1 = Software Reset was executed                        |

|       | 0 = Software Reset as not executed                     |

| bit 5 | Unimplemented: Read as '0'                             |

| bit 4 | WDTO: Watchdog Timer Time-out Flag bit                 |

|       | 1 = WDT Time-out has occurred                          |

|       | 0 = WDT Time-out has not occurred                      |

| bit 3 | SLEEP: Wake From Sleep Flag bit                        |

|       | 1 = Device was in Sleep mode                           |

|       | 0 = Device was not in Sleep mode                       |

| bit 2 | IDLE: Wake From Idle Flag bit                          |

|       | 1 = Device was in Idle mode                            |

|       | 0 = Device was not in Idle mode                        |

| bit 1 | BOR: Brown-out Reset Flag bit <sup>(1)</sup>           |

|       | 1 = Brown-out Reset has occurred                       |

|       | 0 = Brown-out Reset has not occurred                   |

| bit 0 | POR: Power-on Reset Flag bit <sup>(1)</sup>            |

|       | 1 = Power-on Reset has occurred                        |

|       | 0 = Power-on Reset has not occurred                    |

|       |                                                        |

**Note 1:** User software must clear this bit to view next detection.

## TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION

| (1)                                 | IRQ | Vector |          | Persistent |             |              |           |  |  |

|-------------------------------------|-----|--------|----------|------------|-------------|--------------|-----------|--|--|

| Interrupt Source <sup>(1)</sup>     | #   | #      | Flag     | Enable     | Priority    | Sub-priority | Interrupt |  |  |

| Highest Natural Order Priority      |     |        |          |            |             |              |           |  |  |

| CT – Core Timer Interrupt           | 0   | 0      | IFS0<0>  | IEC0<0>    | IPC0<4:2>   | IPC0<1:0>    | No        |  |  |

| CS0 – Core Software Interrupt 0     | 1   | 1      | IFS0<1>  | IEC0<1>    | IPC0<12:10> | IPC0<9:8>    | No        |  |  |

| CS1 – Core Software Interrupt 1     | 2   | 2      | IFS0<2>  | IEC0<2>    | IPC0<20:18> | IPC0<17:16>  | No        |  |  |

| INT0 – External Interrupt           | 3   | 3      | IFS0<3>  | IEC0<3>    | IPC0<28:26> | IPC0<25:24>  | No        |  |  |

| T1 – Timer1                         | 4   | 4      | IFS0<4>  | IEC0<4>    | IPC1<4:2>   | IPC1<1:0>    | No        |  |  |

| IC1E – Input Capture 1 Error        | 5   | 5      | IFS0<5>  | IEC0<5>    | IPC1<12:10> | IPC1<9:8>    | Yes       |  |  |

| IC1 – Input Capture 1               | 6   | 5      | IFS0<6>  | IEC0<6>    | IPC1<12:10> | IPC1<9:8>    | Yes       |  |  |

| OC1 – Output Compare 1              | 7   | 6      | IFS0<7>  | IEC0<7>    | IPC1<20:18> | IPC1<17:16>  | No        |  |  |

| INT1 – External Interrupt 1         | 8   | 7      | IFS0<8>  | IEC0<8>    | IPC1<28:26> | IPC1<25:24>  | No        |  |  |

| T2 – Timer2                         | 9   | 8      | IFS0<9>  | IEC0<9>    | IPC2<4:2>   | IPC2<1:0>    | No        |  |  |

| IC2E – Input Capture 2              | 10  | 9      | IFS0<10> | IEC0<10>   | IPC2<12:10> | IPC2<9:8>    | Yes       |  |  |

| IC2 – Input Capture 2               | 11  | 9      | IFS0<11> | IEC0<11>   | IPC2<12:10> | IPC2<9:8>    | Yes       |  |  |

| OC2 – Output Compare 2              | 12  | 10     | IFS0<12> | IEC0<12>   | IPC2<20:18> | IPC2<17:16>  | No        |  |  |

| INT2 – External Interrupt 2         | 13  | 11     | IFS0<13> | IEC0<13>   | IPC2<28:26> | IPC2<25:24>  | No        |  |  |

| T3 – Timer3                         | 14  | 12     | IFS0<14> | IEC0<14>   | IPC3<4:2>   | IPC3<1:0>    | No        |  |  |

| IC3E – Input Capture 3              | 15  | 13     | IFS0<15> | IEC0<15>   | IPC3<12:10> | IPC3<9:8>    | Yes       |  |  |

| IC3 – Input Capture 3               | 16  | 13     | IFS0<16> | IEC0<16>   | IPC3<12:10> | IPC3<9:8>    | Yes       |  |  |

| OC3 – Output Compare 3              | 17  | 14     | IFS0<17> | IEC0<17>   | IPC3<20:18> | IPC3<17:16>  | No        |  |  |

| INT3 – External Interrupt 3         | 18  | 15     | IFS0<18> | IEC0<18>   | IPC3<28:26> | IPC3<25:24>  | No        |  |  |

| T4 – Timer4                         | 19  | 16     | IFS0<19> | IEC0<19>   | IPC4<4:2>   | IPC4<1:0>    | No        |  |  |

| IC4E – Input Capture 4 Error        | 20  | 17     | IFS0<20> | IEC0<20>   | IPC4<12:10> | IPC4<9:8>    | Yes       |  |  |

| IC4 – Input Capture 4               | 21  | 17     | IFS0<21> | IEC0<21>   | IPC4<12:10> | IPC4<9:8>    | Yes       |  |  |

| OC4 – Output Compare 4              | 22  | 18     | IFS0<22> | IEC0<22>   | IPC4<20:18> | IPC4<17:16>  | No        |  |  |

| INT4 – External Interrupt 4         | 23  | 19     | IFS0<23> | IEC0<23>   | IPC4<28:26> | IPC4<25:24>  | No        |  |  |

| T5 – Timer5                         | 24  | 20     | IFS0<24> | IEC0<24>   | IPC5<4:2>   | IPC5<1:0>    | No        |  |  |

| IC5E – Input Capture 5 Error        | 25  | 21     | IFS0<25> | IEC0<25>   | IPC5<12:10> | IPC5<9:8>    | Yes       |  |  |

| IC5 – Input Capture 5               | 26  | 21     | IFS0<26> | IEC0<26>   | IPC5<12:10> | IPC5<9:8>    | Yes       |  |  |

| OC5 – Output Compare 5              | 27  | 22     | IFS0<27> | IEC0<27>   | IPC5<20:18> | IPC5<17:16>  | No        |  |  |

| AD1 – ADC1 Convert done             | 28  | 23     | IFS0<28> | IEC0<28>   | IPC5<28:26> | IPC5<25:24>  | Yes       |  |  |

| FSCM – Fail-Safe Clock Monitor      | 29  | 24     | IFS0<29> | IEC0<29>   | IPC6<4:2>   | IPC6<1:0>    | No        |  |  |

| RTCC – Real-Time Clock and Calendar | 30  | 25     | IFS0<30> | IEC0<30>   | IPC6<12:10> | IPC6<9:8>    | No        |  |  |

| FCE – Flash Control Event           | 31  | 26     | IFS0<31> | IEC0<31>   | IPC6<20:18> | IPC6<17:16>  | No        |  |  |

| CMP1 – Comparator Interrupt         | 32  | 27     | IFS1<0>  | IEC1<0>    | IPC6<28:26> | IPC6<25:24>  | No        |  |  |

| CMP2 – Comparator Interrupt         | 33  | 28     | IFS1<1>  | IEC1<1>    | IPC7<4:2>   | IPC7<1:0>    | No        |  |  |

| CMP3 – Comparator Interrupt         | 34  | 29     | IFS1<2>  | IEC1<2>    | IPC7<12:10> | IPC7<9:8>    | No        |  |  |

| USB – USB Interrupts                | 35  | 30     | IFS1<3>  | IEC1<3>    | IPC7<20:18> | IPC7<17:16>  | Yes       |  |  |

| SPI1E – SPI1 Fault                  | 36  | 31     | IFS1<4>  | IEC1<4>    | IPC7<28:26> | IPC7<25:24>  | Yes       |  |  |

| SPI1RX – SPI1 Receive Done          | 37  | 31     | IFS1<5>  | IEC1<5>    | IPC7<28:26> | IPC7<25:24>  | Yes       |  |  |

| SPI1TX – SPI1 Transfer Done         | 38  | 31     | IFS1<6>  | IEC1<6>    | IPC7<28:26> | IPC7<25:24>  | Yes       |  |  |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX 28/36/44-Pin General Purpose Family Features" and TABLE 2: "PIC32MX2XX 28/36/44-pin USB Family Features" for the lists of available peripherals.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | _                 | —                 | _                 | -                 | _                 | _                 | _                | —                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        | —                 | —                 | _                 | -                 | _                 | _                 | -                | —                |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15:8         |                   | —                 |                   | _                 | _                 |                   | _                | —                |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   | CHPDAT<7:0>       |                   |                   |                   |                   |                  |                  |  |  |  |  |

## REGISTER 9-18: DCHxDAT: DMA CHANNEL 'x' PATTERN DATA REGISTER

## Legend:

| ========          |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-0 CHPDAT<7:0>: Channel Data Register bits

Pattern Terminate mode: Data to be matched must be stored in this register to allow a "terminate on match".

All other modes: Unused.

## TABLE 11-2: OUTPUT PIN SELECTION

| RPn Port Pin | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection       |  |  |  |  |

|--------------|----------|-------------|---------------------------------------------|--|--|--|--|

| RPA0         | RPA0R    | RPA0R<3:0>  | 0000 = No Connect                           |  |  |  |  |

| RPB3         | RPB3R    | RPB3R<3:0>  | 0001 = <u>U1TX</u><br>0010 = <u>U2RTS</u>   |  |  |  |  |

| RPB4         | RPB4R    | RPB4R<3:0>  | 0011 = SS1                                  |  |  |  |  |

| RPB15        | RPB15R   | RPB15R<3:0> |                                             |  |  |  |  |

| RPB7         | RPB7R    | RPB7R<3:0>  | 0110 = Reserved<br>0111 = C2OUT             |  |  |  |  |

| RPC7         | RPC7R    | RPC7R<3:0>  | 1000 = Reserved                             |  |  |  |  |

| RPC0         | RPC0R    | RPC0R<3:0>  | •                                           |  |  |  |  |

| RPC5         | RPC5R    | RPC5R<3:0>  | •<br>1111 = Reserved                        |  |  |  |  |

| RPA1         | RPA1R    | RPA1R<3:0>  | 0000 = No Connect                           |  |  |  |  |

| RPB5         | RPB5R    | RPB5R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |  |  |  |  |

| RPB1         | RPB1R    | RPB1R<3:0>  | 0011 = SDO1                                 |  |  |  |  |

| RPB11        | RPB11R   | RPB11R<3:0> | 0100 = SDO2<br>0101 = OC2                   |  |  |  |  |

| RPB8         | RPB8R    | RPB8R<3:0>  | 0110 = Reserved                             |  |  |  |  |

| RPA8         | RPA8R    | RPA8R<3:0>  |                                             |  |  |  |  |

| RPC8         | RPC8R    | RPC8R<3:0>  | •                                           |  |  |  |  |

| RPA9         | RPA9R    | RPA9R<3:0>  | 1111 = Reserved                             |  |  |  |  |

| RPA2         | RPA2R    | RPA2R<3:0>  | 0000 = No Connect                           |  |  |  |  |

| RPB6         | RPB6R    | RPB6R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |  |  |  |  |

| RPA4         | RPA4R    | RPA4R<3:0>  | 0011 = SDO1<br>0100 = SDO2                  |  |  |  |  |

| RPB13        | RPB13R   | RPB13R<3:0> | 0101 <b>= OC4</b>                           |  |  |  |  |

| RPB2         | RPB2R    | RPB2R<3:0>  |                                             |  |  |  |  |

| RPC6         | RPC6R    | RPC6R<3:0>  | 1000 = Reserved                             |  |  |  |  |

| RPC1         | RPC1R    | RPC1R<3:0>  |                                             |  |  |  |  |

| RPC3         | RPC3R    | RPC3R<3:0>  | 1111 = Reserved                             |  |  |  |  |

| RPA3         | RPA3R    | RPA3R<3:0>  | 0000 = No Connect                           |  |  |  |  |

| RPB14        | RPB14R   | RPB14R<3:0> |                                             |  |  |  |  |

| RPB0         | RPB0R    | RPB0R<3:0>  | 0011 = <u>Reserved</u><br>0100 = <u>SS2</u> |  |  |  |  |

| RPB10        | RPB10R   | RPB10R<3:0> | 0101 <b>= OC3</b>                           |  |  |  |  |

| RPB9         | RPB9R    | RPB9R<3:0>  |                                             |  |  |  |  |

| RPC9         | RPC9R    | RPC9R<3:0>  | 1000 = Reserved                             |  |  |  |  |

| RPC2         | RPC2R    | RPC2R<3:0>  |                                             |  |  |  |  |

| RPC4         | RPC4R    | RPC4R<3:0>  | 1111 = Reserved                             |  |  |  |  |

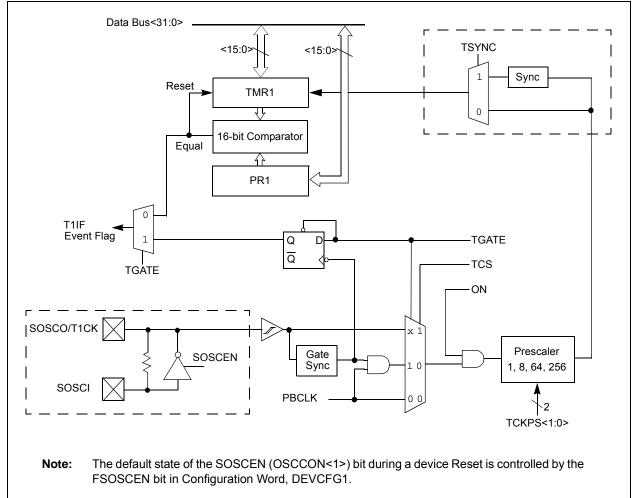

## 12.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features one synchronous/asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can also be used with the Low-Power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications.

FIGURE 12-1: TIMER1 BLOCK DIAGRAM

The following modes are supported:

- · Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

## 12.1 Additional Supported Features

- · Selectable clock prescaler

- Timer operation during CPU Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

Figure 12-1 illustrates a general block diagram of Timer1.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

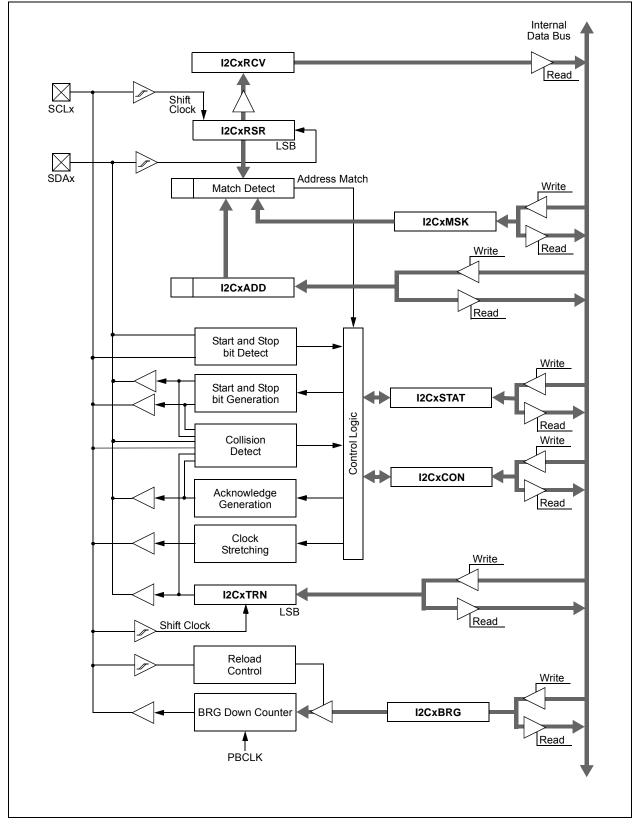

## FIGURE 18-1: I<sup>2</sup>C BLOCK DIAGRAM

## **REGISTER 18-2:** I2CxSTAT: I<sup>2</sup>C STATUS REGISTER (CONTINUED)

| bit 4 | <b>P:</b> Stop bit<br>1 = Indicates that a Stop bit has been detected last                                                                                                                                                       |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>0 = Stop bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul>                                                                                               |

| bit 3 | S: Start bit                                                                                                                                                                                                                     |

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul>                                                                                       |

|       | Hardware set or clear when Start, Repeated Start or Stop detected.                                                                                                                                                               |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                |

|       | <ul> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave</li> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> </ul> |

| bit 1 | <b>RBF:</b> Receive Buffer Full Status bit                                                                                                                                                                                       |

|       | <ul> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> </ul>      |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                             |

|       | 1 = Transmit in progress, I2CxTRN is full                                                                                                                                                                                        |

0 = Transmit complete, I2CxTRN is empty

Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.

## 19.1 UART Control Registers

## TABLE 19-1: UART1 AND UART2 REGISTER MAP

| np for point | ess                         |                  | 6         |        |        |        |       |        |       |       | Bi          | ts                |         |       |             |        |       |        |       | 6          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------|-----------|--------|--------|--------|-------|--------|-------|-------|-------------|-------------------|---------|-------|-------------|--------|-------|--------|-------|------------|

| 6000         01MODe <sup>1</sup> 15.0         ON         -         SIDL         IREN         RTSMD         -         UEN<1.0>         WAKE         LPBACK         ABAUD         RXINV         BRGH         PDEL<1.0>         STSL         0.00           610         U1STA(1)         31.16         -         -         -         -         ADM_EN         VERSE         ADM         ADM_EN         RIDE         PERR         PERR         OERR         VERSO         0000           0107         116         -         -         -         -         -         -         -         -         0000         0000           01080         116         -         -         -         -         -         -         -         -         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15  | 30/14  | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8        | 23/7              | 22/6    | 21/5  | 20/4        | 19/3   | 18/2  | 17/1   | 16/0  | All Resets |

| 610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610 <td>6000</td> <td></td> <td>31:16</td> <td></td> <td></td> <td>_</td> <td>_</td> <td>—</td> <td></td> <td></td> <td>_</td> <td></td> <td>—</td> <td></td> <td></td> <td>—</td> <td>_</td> <td>_</td> <td>_</td> <td>0000</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6000                        |                  | 31:16     |        |        | _      | _     | —      |       |       | _           |                   | —       |       |             | —      | _     | _      | _     | 0000       |

| 600         UTXINT         UTXINV         UTXINV         UTXEN         UTXEN <t< td=""><td>0000</td><td>COOL O INICEE</td><td>15:0</td><td>ON</td><td></td><td>SIDL</td><td>IREN</td><td>RTSMD</td><td>—</td><td>UEN</td><td>-</td><td>WAKE</td><td>LPBACK</td><td>ABAUD</td><td>RXINV</td><td>BRGH</td><td>PDSEI</td><td>L&lt;1:0&gt;</td><td>STSEL</td><td>0000</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0000                        | COOL O INICEE    | 15:0      | ON     |        | SIDL   | IREN  | RTSMD  | —     | UEN   | -           | WAKE              | LPBACK  | ABAUD | RXINV       | BRGH   | PDSEI | L<1:0> | STSEL | 0000       |

| 15:0         15:0         01XSE<10.5         01XBR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6010                        | 111STA(1)        | 31:16     | _      | _      | _      | —     | —      | _     | _     | ADM_EN      |                   |         |       | ADDR        | 2<7:0> |       |        |       | 0000       |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0010                        | 0010 01017.      | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE            | EL<1:0> | ADDEN | RIDLE       | PERR   | FERR  | OERR   | URXDA | 0110       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6020                        |                  | 31:16     | —      | -      | —      | _     | —      | —     | -     | —           | _                 | —       | —     | _           | _      | _     | —      | _     | 0000       |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0020                        | UTTAKLG          | 15:0      | _      |        | _      |       | _      | _     |       |             | Transmit Register |         |       |             | 0000   |       |        |       |            |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6030                        |                  | 31:16     | _      |        | _      |       | _      | _     |       | _           | _                 | _       | _     |             | -      |       | _      |       | 0000       |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0030                        | UINAREG          | 15:0      | _      |        | _      |       | _      | _     |       |             |                   |         | Re    | ceive Regis | ster   |       |        |       | 0000       |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6040                        |                  | 31:16     | -      |        | -      |       | _      | -     |       | —           | —                 | _       | -     |             | -      |       | -      |       | 0000       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00+0                        | 0 IDIXO          | 15:0      |        |        |        |       |        |       | Bau   | d Rate Gene | erator Pres       | caler   |       |             |        |       |        |       | 0000       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6200                        | 112MODE(1)       | 31:16     | _      | _      | _      | —     | —      | _     | _     | —           | —                 | —       | _     | -           | —      | _     | —      | _     | 0000       |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0200                        | OZINODL          | 15:0      | ON     |        | SIDL   | IREN  | RTSMD  | —     | UEN   | <1:0>       | WAKE              | LPBACK  | ABAUD | RXINV       | BRGH   | PDSE  | L<1:0> | STSEL | 0000       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6210                        | 112974(1)        | 31:16     | _      |        | _      |       | _      | _     |       | ADM_EN      |                   |         |       | ADDR        | <7:0>  |       |        |       | 0000       |

| 620     U2TXREG     15:0     -     -     -     -     -     -     -     -     000       6230     U2RXREG     31:16     -     -     -     -     -     -     -     -     000       6230     U2RXREG     31:16     -     -     -     -     -     -     -     -     000       6240     U2BRG(1)     31:16     -     -     -     -     -     -     -     000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0210                        | 0231A. /         | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE            | EL<1:0> | ADDEN | RIDLE       | PERR   | FERR  | OERR   | URXDA | 0110       |

| 150     -     -     -     -     -     -     -     -     -     000       623     U2RXEG     31:6     -     -     -     -     -     -     -     -     -     000       623     U2RXEG     31:16     -     -     -     -     -     -     -     -     -     -     000       6240     U2BRG(1)     31:16     -     -     -     -     -     -     -     -     000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6220                        |                  | 31:16     | _      |        | _      |       | _      | _     |       | _           | _                 | _       | _     |             | -      |       | _      |       | 0000       |

| 6230     U2RXREG     -     -     -     -     -     -     -     0000       6240     U2BRG <sup>(1)</sup> 31:16     -     -     -     -     -     -     -     -     0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0220                        | UZTARLO          | 15:0      | _      |        | _      |       | _      | _     |       |             |                   |         | Tra   | nsmit Regis | ster   |       |        |       | 0000       |