Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f256dt-i-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

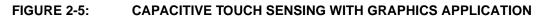

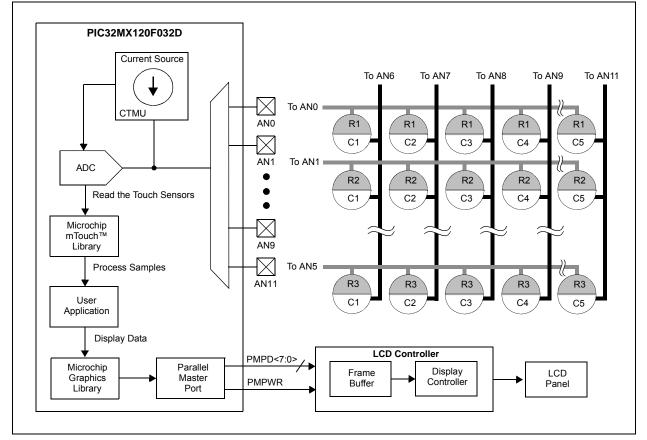

# 2.9 Typical Application Connection Examples

Examples of typical application connections are shown in Figure 2-5 and Figure 2-6.

FIGURE 2-6: AUDIO PLAYBACK APPLICATION

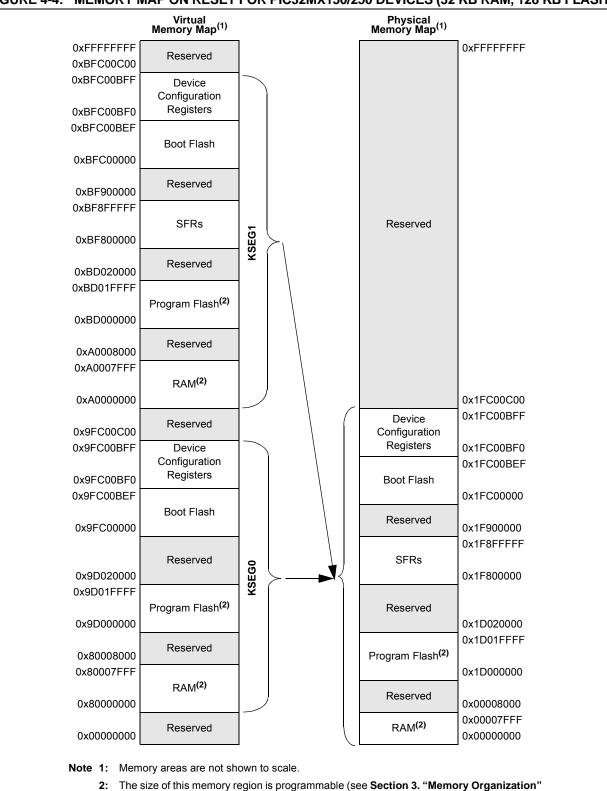

# FIGURE 4-4: MEMORY MAP ON RESET FOR PIC32MX150/250 DEVICES (32 KB RAM, 128 KB FLASH)

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS60001115) in the "*PIC32 Family Reference Manual*") and can be changed by initialization code provided by end-user development tools (refer to the specific development tool documentation for information).

# 8.0 OSCILLATOR CONFIGURATION

| Note: | This data sheet summarizes the features<br>of the PIC32MX1XX/2XX 28/36/44-pin<br>Family of devices. It is not intended to be<br>a comprehensive reference source. To<br>complement the information in this data |  |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|       | sheet, refer to Section 6. "Oscillator                                                                                                                                                                          |  |  |  |  |  |  |

|       | Configuration" (DS60001112), which is                                                                                                                                                                           |  |  |  |  |  |  |

|       | available from the Documentation >                                                                                                                                                                              |  |  |  |  |  |  |

|       | Reference Manual section of the                                                                                                                                                                                 |  |  |  |  |  |  |

|       | Microchip PIC32 web site                                                                                                                                                                                        |  |  |  |  |  |  |

|       | (www.microchip.com/pic32).                                                                                                                                                                                      |  |  |  |  |  |  |

The PIC32MX1XX/2XX 28/36/44-pin Family oscillator system has the following modules and features:

- Four external and internal oscillator options as clock sources

- On-Chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-Chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Dedicated On-Chip PLL for USB peripheral

A block diagram of the oscillator system is provided in Figure 8-1.

# REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| bit 3   | CF: Clock Fail Detect bit                                                                                                                                      |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = FSCM has detected a clock failure                                                                                                                          |

|         | 0 = No clock failure has been detected                                                                                                                         |

| bit 2   | UFRCEN: USB FRC Clock Enable bit <sup>(1)</sup>                                                                                                                |

|         | <ul> <li>1 = Enable the FRC as the clock source for the USB clock source</li> <li>0 = Use the Primary Oscillator or USB PLL as the USB clock source</li> </ul> |

| bit 1   | SOSCEN: Secondary Oscillator (Sosc) Enable bit                                                                                                                 |

|         | 1 = Enable the Secondary Oscillator                                                                                                                            |

|         | 0 = Disable the Secondary Oscillator                                                                                                                           |

| bit 0   | OSWEN: Oscillator Switch Enable bit                                                                                                                            |

|         | <ul> <li>1 = Initiate an oscillator switch to selection specified by NOSC&lt;2:0&gt; bits</li> <li>0 = Oscillator switch is complete</li> </ul>                |

| Note 1: | This bit is only available on PIC32MX2XX devices.                                                                                                              |

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        |                   |                   |                   | ROTRI             | //<8:1>           |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | ROTRIM<0>         | _                 | _                 | _                 | —                 | _                 | —                | —                |  |  |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         | —                 | _                 | _                 | _                 | —                 | _                 | —                | —                |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7:0          | _                 | _                 | _                 | _                 | —                 | _                 | _                | —                |  |  |

# REGISTER 8-4: REFOTRIM: REFERENCE OSCILLATOR TRIM REGISTER

# Legend:

| Logona.           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

Note: While the ON (REFOCON<15>) bit is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

### REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-----------------------|-------------------|-------------------|--------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0              | U-0               | U-0              | R/W-0            |  |  |

| 31:24        | —                 | _                     | BYTC              | <1:0>             | WBO <sup>(1)</sup> | —                 | _                | BITO             |  |  |

| 22:16        | U-0               | U-0                   | U-0               | U-0               | U-0                | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | _                     | —                 | _                 | —                  | —                 | _                | _                |  |  |

| 45.0         | U-0               | U-0                   | U-0               | R/W-0             | R/W-0              | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         |                   | _                     | _                 |                   |                    | PLEN<4:0>         |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0                | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> | CRCTYP            | _                 | _                  | (                 | CRCCH<2:0>       |                  |  |  |

# Legend:

| Logona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-30 Unimplemented: Read as '0'

- bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (i.e., source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (i.e., reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (i.e., reverse source byte order)

- 00 = No swapping (i.e., source byte order)

- bit 27 **WBO:** CRC Write Byte Order Selection bit<sup>(1)</sup>

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (i.e., reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (i.e., not reflected)

#### <u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (i.e., reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (i.e., not reflected)

#### bit 23-13 Unimplemented: Read as '0'

bit 12-8 **PLEN<4:0>:** Polynomial Length bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): These bits are unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Denotes the length of the polynomial -1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- Note 1: When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

# TABLE 11-6: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| ssa                         |                  |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |       |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| FA04                        | INT1R            | 31:16     |       |       |       |       | _     | _     |      |      |      |      |      |      |      | _     |        |      | 0000       |

| FA04                        |                  | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | INT1F | R<3:0> |      | 0000       |

| FA08                        | INT2R            | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | _     | —      | —    | 0000       |

| FAUO                        | INTZR            | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | INT2F | R<3:0> |      | 0000       |

| FA0C                        | INT3R            | 31:16     | _     | _     | _     | _     | —     | —     | _    | _    | —    | _    |      | —    | _    |       | —      | —    | 0000       |

| FAUC                        | IN I 3R          | 15:0      |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | INT3F | R<3:0> |      | 0000       |

| 5440                        |                  | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | -    | 0000       |

| FA10                        | INT4R            | 15:0      | -     | _     | _     | _     | -     | -     | _    | _    | _    | _    | _    | _    |      | INT4F | R<3:0> |      | 0000       |

| 5440                        | TAOKA            | 31:16     | _     | _     | _     | _     | —     | —     | _    | _    | _    | _    | _    | _    | _    | _     | _      | —    | 0000       |

| FA18                        | T2CKR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T2CK  | R<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    |      | _    | _    |       | _      | _    | 0000       |

| FA1C                        | T3CKR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    |      | _    |      | T3CK  | R<3:0> | •    | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    |      | _    | _    |       | _      | _    | 0000       |

| FA20                        | T4CKR            | 15:0      | _     |       | _     |       | _     | _     | _    | _    | _    |      |      | _    |      | T4CK  | R<3:0> | •    | 0000       |

|                             |                  | 31:16     | _     |       | _     |       | _     | _     | _    | _    | _    |      |      | _    | _    |       | _      | _    | 0000       |

| FA24                        | T5CKR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T5CK  | R<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |       | —      | _    | 0000       |

| FA28                        | IC1R             | 15:0      | _     | _     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    |      | IC1R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      | _    | _     | _      | _    | 0000       |

| FA2C                        | IC2R             | 15:0      | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      |      | IC2R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FA30                        | IC3R             | 15:0      | _     | _     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    |      | IC3R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      | _    | _     | _      | _    | 0000       |

| FA34                        | IC4R             | 15:0      | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      |      | IC4R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      | _    | _     | _      | _    | 0000       |

| FA38                        | IC5R             | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | IC5R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     | _     |       |       | _     | _     |      | _    | _    | _    | _    | _    |      | _     |        | _    | 0000       |

| FA48                        | OCFAR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | OCFA  | R<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FA4C                        | OCFBR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | OCFB  | R<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FA50                        | U1RXR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U1RX  | R<3:0> |      | 0000       |

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

NOTES:

# REGISTER 17-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)

- bit 5 **MSTEN:** Master Mode Enable bit

- 1 = Master mode

- 0 = Slave mode

- bit 4 DISSDI: Disable SDI bit

- 1 = SDI pin is not used by the SPI module (pin is controlled by PORT function)

- 0 = SDI pin is controlled by the SPI module

- bit 3-2 STXISEL<1:0>: SPI Transmit Buffer Empty Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)

- 10 = Interrupt is generated when the buffer is empty by one-half or more

- 01 = Interrupt is generated when the buffer is completely empty

- 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are complete

- bit 1-0 SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is full

- 10 = Interrupt is generated when the buffer is full by one-half or more

- 01 = Interrupt is generated when the buffer is not empty

- 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit can only be written when the ON bit = 0.

- 3: This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- 4: When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                     | -                 | _                 | -                 | -                 | _                | _                |

| 23:16        | U-0               | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:10        | —                 | —                     |                   | _                 |                   | _                 | _                | _                |

|              | U-0               | R/W-0                 | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | CS1 <sup>(1)</sup>    |                   |                   | -                 |                   |                  |                  |

|              |                   | ADDR14 <sup>(2)</sup> | _                 |                   |                   | ADDR<10:8>        |                  |                  |

| 7:0          | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | ADDR<7:0>         |                       |                   |                   |                   |                   |                  |                  |

# REGISTER 20-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31-15 **Unimplemented:** Read as '0'

- bit 14 **CS1:** Chip Select 1 bit<sup>(1)</sup>

- 1 = Chip Select 1 is active

- 0 = Chip Select 1 is inactive

- bit 14 ADDR<14>: Destination Address bit 14<sup>(2)</sup>

- bit 13-11 Unimplemented: Read as '0'

- bit 10-0 ADDR<10:0>: Destination Address bits

- Note 1: When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4   | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|------------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 31.24        | EDG1MOD           | EDG1POL           |                   | EDG1S               | EL<3:0>           |                   | EDG2STAT               | EDG1STAT         |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | U-0                    | U-0              |

| 23.10        | EDG2MOD           | EDG2POL           |                   | EDG2S               | EL<3:0>           | —                 | —                      |                  |

| 15:8         | R/W-0             | U-0               | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 15.0         | ON                | —                 | CTMUSIDL          | TGEN <sup>(1)</sup> | EDGEN             | EDGSEQEN          | IDISSEN <sup>(2)</sup> | CTTRIG           |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 7.0          | ITRIM<5:0>        |                   |                   |                     |                   |                   |                        | <1:0>            |

# REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER

# Legend:

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

- bit 31 EDG1MOD: Edge1 Edge Sampling Select bit

- 1 = Input is edge-sensitive

- 0 = Input is level-sensitive

- bit 30 EDG1POL: Edge 1 Polarity Select bit

- 1 = Edge1 programmed for a positive edge response

- 0 = Edge1 programmed for a negative edge response

- bit 29-26 EDG1SEL<3:0>: Edge 1 Source Select bits

- 1111 = C3OUT pin is selected

- 1110 = C2OUT pin is selected

- 1101 = C1OUT pin is selected

- 1100 = IC3 Capture Event is selected

- 1011 = IC2 Capture Event is selected

- 1010 = IC1 Capture Event is selected

- 1001 = CTED8 pin is selected

- 1000 = CTED7 pin is selected

- 0111 = CTED6 pin is selected

- 0110 = CTED5 pin is selected

- 0101 = CTED4 pin is selected

- 0100 = CTED3 pin is selected

- 0011 = CTED1 pin is selected

- 0010 = CTED2 pin is selected

- 0001 = OC1 Compare Event is selected 0000 = Timer1 Event is selected

# bit 25 EDG2STAT: Edge2 Status bit

Indicates the status of Edge2 and can be written to control edge source

- 1 = Edge2 has occurred

- 0 = Edge2 has not occurred

- Note 1: When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 30-41) in Section 30.0 "Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

# TABLE 26-2: PERIPHERAL MODULE DISABLE REGISTER MAP

| ess                         |                                 |           |       |       |       |       |       |       |        |        | Bits |      |      |       |       |        |        |        | 6          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|--------|--------|------|------|------|-------|-------|--------|--------|--------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8   | 23/7 | 22/6 | 21/5 | 20/4  | 19/3  | 18/2   | 17/1   | 16/0   | All Resets |

| 5040                        | PMD1                            | 31:16     | —     | —     | _     | —     | _     |       | —      | —      | —    | —    | —    | —     |       | —      | —      | —      | 0000       |

| F240                        | FIVIDI                          | 15:0      | -     |       |       | CVRMD | Ι     |       | —      | CTMUMD | —    | -    |      | -     |       |        | —      | AD1MD  | 0000       |

| 5250                        | PMD2                            | 31:16     | —     | —     |       | —     | _     | _     |        | —      | —    | —    | —    | —     | -     | —      | —      | —      | 0000       |

| F250                        | FIVIDZ                          | 15:0      | —     | _     | _     | —     | _     | _     | —      | —      | _    | _    | _    | _     | _     | CMP3MD | CMP2MD | CMP1MD | 0000       |

| F260                        | PMD3                            | 31:16     | _     |       |       | _     | -     |       | _      | _      | _    |      | _    | OC5MD | OC4MD | OC3MD  | OC2MD  | OC1MD  | 0000       |

| F200                        | FIVIDS                          | 15:0      | _     |       |       | _     | -     |       | _      | _      | _    |      | _    | IC5MD | IC4MD | IC3MD  | IC2MD  | IC1MD  | 0000       |

| F270                        | PMD4                            | 31:16     | _     |       |       | _     | -     |       | _      | _      | _    |      | _    | -     |       | _      | —      | _      | 0000       |

| F270                        | F IVID4                         | 15:0      | _     |       |       | _     | -     |       | _      | _      | _    |      | _    | T5MD  | T4MD  | T3MD   | T2MD   | T1MD   | 0000       |

| F280                        | PMD5                            | 31:16     | _     |       |       | _     | -     |       | _      | USB1MD | _    |      | _    | -     |       | _      | I2C1MD | I2C1MD | 0000       |

| F200                        | FIVIDS                          | 15:0      | _     |       |       | _     | -     |       | SPI2MD | SPI1MD | _    |      | _    | -     |       | _      | U2MD   | U1MD   | 0000       |

| F200                        | PMD6                            | 31:16     | _     | —     |       | —     | _     | _     | _      | —      | —    | _    | —    | _     | _     | —      | —      | PMPMD  | 0000       |

| F290                        |                                 | 15:0      | —     | —     |       |       | _     |       | —      | _      | —    |      | —    | -     |       | —      | REFOMD | RTCCMD | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2       | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|----------------------|-------------------------|------------------|------------------|

| 24.04        | r-0               | r-1               | r-1               | R/P               | r-1                  | r-1                     | r-1              | R/P              |

| 31:24        |                   | _                 |                   | CP                | —                    | _                       | _                | BWP              |

| 00.40        | r-1               | r-1               | r-1               | r-1               | r-1                  | R/P                     | R/P              | R/P              |

| 23:16        |                   |                   |                   | _                 | —                    | PWP<8:6> <sup>(3)</sup> |                  |                  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | R/P                  | R/P                     | r-1              | r-1              |

| 15:8         | PWP<5:0>          |                   |                   |                   |                      |                         | —                | —                |

| 7.0          | r-1               | r-1               | r-1               | R/P               | R/P                  | R/P                     | R/P              | R/P              |

| 7:0          |                   |                   |                   | ICESEL            | <1:0> <sup>(2)</sup> | JTAGEN <sup>(1)</sup>   | DEBU             | G<1:0>           |

# REGISTER 27-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

| Legend:           | r = Reserved bit | P = Programmable bit |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31 Reserved: Write '0'

bit 30-29 Reserved: Write '1'

- bit 28 **CP:** Code-Protect bit

- Prevents boot and program Flash memory from being read or modified by an external programming device. 1 = Protection is disabled

0 = Protection is enabled

bit 27-25 Reserved: Write '1'

bit 24 **BWP:** Boot Flash Write-Protect bit

Prevents boot Flash memory from being modified during code execution.

1 = Boot Flash is writable

0 = Boot Flash is not writable

- bit 23-19 Reserved: Write '1'

- **Note 1:** This bit sets the value for the JTAGEN bit in the CFGCON register.

- 2: The PGEC4/PGED4 pin pair is not available on all devices. Refer to the "**Pin Diagrams**" section for availability.

- 3: The PWP<8:7> bits are only available on devices with 256 KB Flash.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.04        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | R/P              | R/P              |  |

| 31:24        | _                 | _                 | _                 | _                 |                   |                   | — FWDTWINSZ<1:   |                  |  |

| 00.40        | R/P               | R/P               | r-1               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 23:16        | FWDTEN WINDIS     |                   | _                 |                   |                   | WDTPS<4:0>        |                  |                  |  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | r-1               | R/P               | R/P              | R/P              |  |

| 15:8         | FCKSM             | 1<1:0>            | FPBDI             | V<1:0>            | —                 | OSCIOFNC          | POSCM            | OD<1:0>          |  |

| 7.0          | R/P r-1           |                   | R/P               | r-1               | r-1               | R/P               | R/P              | R/P              |  |

| 7:0          | IESO —            |                   | FSOSCEN —         |                   | —                 | FNOSC<2:0>        |                  |                  |  |

# REGISTER 27-2: DEVCFG1: DEVICE CONFIGURATION WORD 1

| Legend:           | r = Reserved bit | P = Programmable bit     |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-26 Reserved: Write '1'

bit 25-24 FWDTWINSZ<1:0>: Watchdog Timer Window Size bits

- 11 = Window size is 25%

- 10 = Window size is 37.5%

- 01 = Window size is 50%

- 00 = Window size is 75%

#### bit 23 FWDTEN: Watchdog Timer Enable bit

- 1 = Watchdog Timer is enabled and cannot be disabled by software

- 0 = Watchdog Timer is not enabled; it can be enabled in software

# bit 22 WINDIS: Watchdog Timer Window Enable bit

- 1 = Watchdog Timer is in non-Window mode

- 0 = Watchdog Timer is in Window mode

#### bit 21 Reserved: Write '1'

#### bit 20-16 WDTPS<4:0>: Watchdog Timer Postscale Select bits

| 10100 <b>= 1:1048576</b>                                     |

|--------------------------------------------------------------|

| 10011 <b>= 1:524288</b>                                      |

| 10010 <b>= 1:262144</b>                                      |

| 10001 <b>= 1:131072</b>                                      |

| 10000 <b>= 1:65536</b>                                       |

| 01111 <b>= 1:32768</b>                                       |

| 01110 <b>= 1:16384</b>                                       |

| 01101 = 1:8192                                               |

| 01100 = 1:4096                                               |

| 01011 = <b>1:2048</b>                                        |

| 01010 = 1:1024                                               |

| 01001 = 1:512                                                |

| 01000 <b>= 1:256</b>                                         |

| 00111 <b>= 1:128</b>                                         |

| 00110 <b>= 1:64</b>                                          |

| 00101 <b>= 1:32</b>                                          |

| 00100 <b>= 1:16</b>                                          |

| 00011 <b>= 1:8</b>                                           |

| 00010 = 1:4                                                  |

| 00001 = 1:2                                                  |

| 00000 = 1:1                                                  |

| All other combinations not shown result in operation = 10100 |

| ······································                       |

**Note 1:** Do not disable the Posc (POSCMOD = 11) when using this oscillator source.

# 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

# 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- · Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

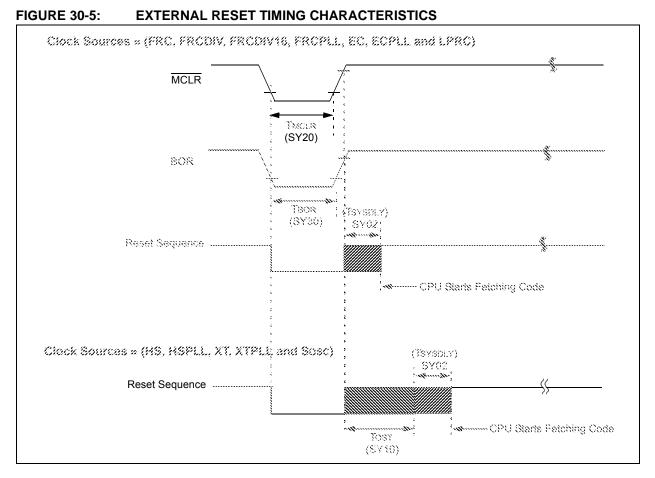

| TABLE         | 30-22: F | RESETS TIMING                                                                                                                              |        |                                                 |                           |            |                                                    |

|---------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------|---------------------------|------------|----------------------------------------------------|

| АС СНА        | RACTER   | ISTICS                                                                                                                                     | (unles | ard Operating<br>s otherwise s<br>ing temperatu | <b>tated)</b><br>re -40°C | C ≤ TA ≤ + | to 3.6V<br>85°C for Industrial<br>105°C for V-temp |

| Param.<br>No. | Symbol   | Characteristics <sup>(1)</sup>                                                                                                             | Min.   | Typical <sup>(2)</sup>                          | Max.                      | Units      | Conditions                                         |

| SY00          | Τρυ      | Power-up Period<br>Internal Voltage Regulator Enabled                                                                                      | —      | 400                                             | 600                       | μS         | _                                                  |

| SY02          | TSYSDLY  | System Delay Period:<br>Time Required to Reload Device<br>Configuration Fuses plus SYSCLK<br>Delay before First instruction is<br>Fetched. | _      | 1 μs +<br>8 SYSCLK<br>cycles                    | _                         | _          | _                                                  |

| SY20          | TMCLR    | MCLR Pulse Width (low)                                                                                                                     | 2      | _                                               | _                         | μS         | —                                                  |

| SY30          | TBOR     | BOR Pulse Width (low)                                                                                                                      |        | 1                                               | _                         | μS         | —                                                  |

These parameters are characterized, but not tested in manufacturing. Note 1:

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Characterized by design but not tested.

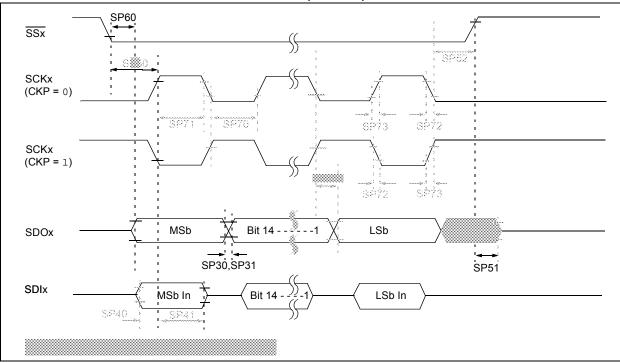

# FIGURE 30-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

# TABLE 30-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        | AC CHARACTERISTICS    |                                                                           |        | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |      |       |                    |  |  |

|---------------|-----------------------|---------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------|--|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                                            | Min.   | Typical <sup>(2)</sup>                                                                                                                                                                                    | Max. | Units | Conditions         |  |  |

| SP70          | TscL                  | SCKx Input Low Time (Note 3)                                              | Tsck/2 | _                                                                                                                                                                                                         | _    | ns    | —                  |  |  |

| SP71          | TscH                  | SCKx Input High Time (Note 3)                                             | Tsck/2 | —                                                                                                                                                                                                         | _    | ns    | —                  |  |  |

| SP72          | TscF                  | SCKx Input Fall Time                                                      | _      | 5                                                                                                                                                                                                         | 10   | ns    | —                  |  |  |

| SP73          | TscR                  | SCKx Input Rise Time                                                      | —      | 5                                                                                                                                                                                                         | 10   | ns    | —                  |  |  |

| SP30          | TDOF                  | SDOx Data Output Fall Time (Note 4)                                       | —      | —                                                                                                                                                                                                         | _    | ns    | See parameter DO32 |  |  |

| SP31          | TDOR                  | SDOx Data Output Rise Time (Note 4)                                       | —      | —                                                                                                                                                                                                         | _    | ns    | See parameter DO31 |  |  |

| SP35          | TscH2doV,             | SDOx Data Output Valid after                                              | _      | —                                                                                                                                                                                                         | 20   | ns    | VDD > 2.7V         |  |  |

|               | TscL2DoV              | SCKx Edge                                                                 | _      | —                                                                                                                                                                                                         | 30   | ns    | VDD < 2.7V         |  |  |

| SP40          | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge                                | 10     | —                                                                                                                                                                                                         | _    | ns    | —                  |  |  |

| SP41          | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                 | 10     | —                                                                                                                                                                                                         |      | ns    | —                  |  |  |

| SP50          | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ Input | 175    | —                                                                                                                                                                                                         |      | ns    | _                  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 50 ns.

- **4:** Assumes 50 pF load on all SPIx pins.

# TABLE 30-34: ADC MODULE SPECIFICATIONS

|               | AC CHAR    | ACTERISTICS                       | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 5): 2.5V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |              |      |       |                                                         |  |  |

|---------------|------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|-------|---------------------------------------------------------|--|--|

| Param.<br>No. | Symbol     | Characteristics                   | Min.                                                                                                                                                                                                                                                                                               | Typical      | Max. | Units | Conditions                                              |  |  |

| ADC Ac        | curacy – N | leasurements with Inter           | nal VREF+/V                                                                                                                                                                                                                                                                                        | REF-         |      | •     | •                                                       |  |  |

| AD20d         | Nr         | Resolution                        |                                                                                                                                                                                                                                                                                                    | 10 data bits | 3    | bits  | (Note 3)                                                |  |  |

| AD21d         | INL        | Integral Non-linearity            | > -1                                                                                                                                                                                                                                                                                               | _            | < 1  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |  |

| AD22d         | DNL        | Differential Non-linearity        | > -1                                                                                                                                                                                                                                                                                               | —            | < 1  | LSb   | VINL = AVss = 0V,<br>AVDD = 2.5V to 3.6V<br>(Notes 2,3) |  |  |

| AD23d         | Gerr       | Gain Error                        | > -4                                                                                                                                                                                                                                                                                               | _            | < 4  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |  |

| AD24d         | EOFF       | Offset Error                      | > -2                                                                                                                                                                                                                                                                                               | _            | < 2  | Lsb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |  |

| AD25d         |            | Monotonicity                      |                                                                                                                                                                                                                                                                                                    |              | _    | _     | Guaranteed                                              |  |  |

| Dynami        | c Performa | ance                              | ·                                                                                                                                                                                                                                                                                                  |              |      | ·     |                                                         |  |  |

| AD32b         | SINAD      | Signal to Noise and<br>Distortion | 55                                                                                                                                                                                                                                                                                                 | 58.5         | _    | dB    | (Notes 3,4)                                             |  |  |

| AD34b         | ENOB       | Effective Number of bits          | 9.0                                                                                                                                                                                                                                                                                                | 9.5          |      | bits  | (Notes 3,4)                                             |  |  |

**Note 1:** These parameters are not characterized or tested in manufacturing.

2: With no missing codes.

3: These parameters are characterized, but not tested in manufacturing.

4: Characterized with a 1 kHz sine wave.

**5:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

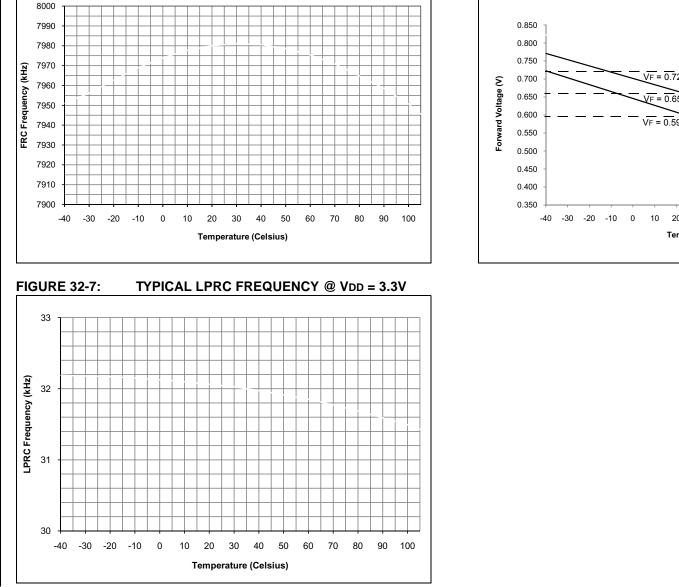

TYPICAL FRC FREQUENCY @ VDD = 3.3V

**FIGURE 32-6:**