Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f256dt-v-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 9: PIN NAMES FOR 44-PIN GENERAL PURPOSE DEVICES

#### 44-PIN QFN (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX110F016D PIC32MX120F032D PIC32MX130F064D PIC32MX130F256D PIC32MX150F128D PIC32MX170F256D

| Pin # | Full Pin Name                                  | Pin # | Full Pin Name                        |

|-------|------------------------------------------------|-------|--------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                       | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 |

| 2     | RPC6/PMA1/RC6                                  | 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3   |

| 3     | RPC7/PMA0/RC7                                  | 25    | AN6/RPC0/RC0                         |

| 4     | RPC8/PMA5/RC8                                  | 26    | AN7/RPC1/RC1                         |

| 5     | RPC9/CTED7/PMA6/RC9                            | 27    | AN8/RPC2/PMA2/RC2                    |

| 6     | Vss                                            | 28    | VDD                                  |

| 7     | VCAP                                           | 29    | Vss                                  |

| 8     | PGED2/RPB10/CTED11/PMD2/RB10                   | 30    | OSC1/CLKI/RPA2/RA2                   |

| 9     | PGEC2/RPB11/PMD1/RB11                          | 31    | OSC2/CLKO/RPA3/RA3                   |

| 10    | AN12/PMD0/RB12                                 | 32    | TDO/RPA8/PMA8/RA8                    |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                     | 33    | SOSCI/RPB4/RB4                       |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10           | 34    | SOSCO/RPA4/T1CK/CTED9/RA4            |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7       | 35    | TDI/RPA9/PMA9/RA9                    |

| 14    | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 | 36    | RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          | 37    | RPC4/PMA4/RC4                        |

| 16    | AVss                                           | 38    | RPC5/PMA3/RC5                        |

| 17    | AVDD                                           | 39    | Vss                                  |

| 18    | MCLR                                           | 40    | VDD                                  |

| 19    | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          | 41    | PGED3/RPB5/PMD7/RB5                  |

| 20    | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                | 42    | PGEC3/RPB6/PMD6/RB6                  |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0           | 43    | RPB7/CTED3/PMD5/INT0/RB7             |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1          | 44    | RPB8/SCL1/CTED10/PMD4/RB8            |

44

1

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

5: Shaded pins are 5V tolerant.

|          |                                        | Pin Nu                                | mber <sup>(1)</sup>                    |                                        |             |                |                                                                         |

|----------|----------------------------------------|---------------------------------------|----------------------------------------|----------------------------------------|-------------|----------------|-------------------------------------------------------------------------|

| Pin Name | 28-pin<br>QFN                          | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC     | 36-pin<br>VTLA                         | 44-pin<br>QFN/<br>TQFP/<br>VTLA        | Pin<br>Type | Buffer<br>Type | Description                                                             |

| USBID    | <sub>11</sub> (3)                      | 14 <sup>(3)</sup>                     | 15 <b>(3)</b>                          | 41 <sup>(3)</sup>                      | I           | ST             | USB OTG ID detect                                                       |

| CTED1    | 27                                     | 2                                     | 33                                     | 19                                     | I           | ST             | CTMU External Edge Input                                                |

| CTED2    | 28                                     | 3                                     | 34                                     | 20                                     | Ι           | ST             | 7                                                                       |

| CTED3    | 13                                     | 16                                    | 17                                     | 43                                     | I           | ST             | 7                                                                       |

| CTED4    | 15                                     | 18                                    | 19                                     | 1                                      | I           | ST             | 7                                                                       |

| CTED5    | 22                                     | 25                                    | 28                                     | 14                                     | I           | ST             | 7                                                                       |

| CTED6    | 23                                     | 26                                    | 29                                     | 15                                     | I           | ST             | 7                                                                       |

| CTED7    | _                                      | _                                     | 20                                     | 5                                      | I           | ST             | 7                                                                       |

| CTED8    | _                                      |                                       | _                                      | 13                                     | I           | ST             | 7                                                                       |

| CTED9    | 9                                      | 12                                    | 10                                     | 34                                     | I           | ST             | 7                                                                       |

| CTED10   | 14                                     | 17                                    | 18                                     | 44                                     | I           | ST             | 7                                                                       |

| CTED11   | 18                                     | 21                                    | 24                                     | 8                                      | I           | ST             | 7                                                                       |

| CTED12   | 2                                      | 5                                     | 36                                     | 22                                     | I           | ST             | 7                                                                       |

| CTED13   | 3                                      | 6                                     | 1                                      | 23                                     | I           | ST             | 7                                                                       |

| CTPLS    | 21                                     | 24                                    | 27                                     | 11                                     | 0           | _              | CTMU Pulse Output                                                       |

| PGED1    | 1                                      | 4                                     | 35                                     | 21                                     | I/O         | ST             | Data I/O pin for Programming/Debuggin<br>Communication Channel 1        |

| PGEC1    | 2                                      | 5                                     | 36                                     | 22                                     | Ι           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 1 |

| PGED2    | 18                                     | 21                                    | 24                                     | 8                                      | I/O         | ST             | Data I/O pin for Programming/Debuggin<br>Communication Channel 2        |

| PGEC2    | 19                                     | 22                                    | 25                                     | 9                                      | I           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 2 |

| PGED3    | 11 <sup>(2)</sup><br>27 <sup>(3)</sup> | 14 <sup>(2)</sup><br>2 <sup>(3)</sup> | 15 <sup>(2)</sup><br>33 <sup>(3)</sup> | 41 <sup>(2)</sup><br>19 <sup>(3)</sup> | I/O         | ST             | Data I/O pin for Programming/Debuggin<br>Communication Channel 3        |

|          | 12 <b>(2)</b>                          | 15 <b>(2)</b>                         | 16 <b>(2)</b>                          | 42 <sup>(2)</sup>                      |             | OT             | Clock input pin for Programming/                                        |

| PGEC3    | 28 <sup>(3)</sup>                      | 3 <b>(3)</b>                          | 34 <sup>(3)</sup>                      | 20 <sup>(3)</sup>                      |             | ST             | Debugging Communication Channel 3                                       |

| PGED4    | —                                      | —                                     | 3                                      | 12                                     | I/O         | ST             | Data I/O pin for Programming/Debuggir<br>Communication Channel 4        |

| PGEC4    | —                                      | —                                     | 4                                      | 13                                     | I           | ST             | Clock input pin for Programming/<br>Debugging Communication Channel 4   |

# TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

TTL = TTL input buffer PPS = Peripheral Pin Select

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

**2:** Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

— = N/A

|          |                         | Pin Nu                            | mber <sup>(1)</sup> |                                 |             |                      |                                                                                      |

|----------|-------------------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------------|--------------------------------------------------------------------------------------|

| Pin Name | 28-pin<br>QFN           | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type       | Description                                                                          |

| MCLR     | 26                      | 1                                 | 32                  | 18                              | I/P         | ST                   | Master Clear (Reset) input. This pin is an active-low Reset to the device.           |

| AVDD     | 25                      | 28                                | 31                  | 17                              | Р           | _                    | Positive supply for analog modules. This pin must be connected at all times.         |

| AVss     | 24                      | 27                                | 30                  | 16                              | Р           | —                    | Ground reference for analog modules                                                  |

| Vdd      | 10                      | 13                                | 5, 13, 14,<br>23    | 28, 40                          | Р           | _                    | Positive supply for peripheral logic and<br>I/O pins                                 |

| VCAP     | 17                      | 20                                | 22                  | 7                               | Р           | —                    | CPU logic filter capacitor connection                                                |

| Vss      | 5, 16                   | 8, 19                             | 6, 12, 21           | 6, 29, 39                       | Р           | _                    | Ground reference for logic and I/O pins.<br>This pin must be connected at all times. |

| VREF+    | 27                      | 2                                 | 33                  | 19                              | I           | Analog               | Analog voltage reference (high) input                                                |

| VREF-    | 28                      | 3                                 | 34                  | 20                              | I           | Analog               | Analog voltage reference (low) input                                                 |

| Legend:  | CMOS = CM<br>ST = Schmi |                                   | •                   |                                 |             | Analog =<br>O = Outp | Analog input P = Power<br>ut I = Input                                               |

#### TADI E 4 4. DINOUT I/O DESCRIPTIONS (CONTINUED)

ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer

| . , .     |

|-----------|

| P = Powe  |

| l = Input |

| — = N/A   |

|           |

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

#### 5.1 Flash Controller Control Registers

### TABLE 5-1: FLASH CONTROLLER REGISTER MAP

| ess                         |                        | 0         |              |       |       |        |         |       |      | Bit       | s         |      |      |      |      |      |        |      | 6          |

|-----------------------------|------------------------|-----------|--------------|-------|-------|--------|---------|-------|------|-----------|-----------|------|------|------|------|------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range | 31/15        | 30/14 | 29/13 | 28/12  | 27/11   | 26/10 | 25/9 | 24/8      | 23/7      | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| F400                        | NVMCON <sup>(1)</sup>  | 31:16     | —            | —     | -     | —      | —       | —     | _    | -         | —         | _    | —    | _    | —    | —    | -      | -    | 0000       |

| F400                        | 1400 NVMCON(*)         | 15:0      | WR           | WREN  | WRERR | LVDERR | LVDSTAT | _     |      | —         |           | _    | —    | _    |      | NVMO | P<3:0> |      | 0000       |

| F410                        | NVMKEY                 | 31:16     | NVMKEY<31:0> |       |       |        |         |       |      |           | 0000      |      |      |      |      |      |        |      |            |

| 1410                        |                        | 15:0      |              |       |       |        |         |       |      |           |           |      |      |      |      | 0000 |        |      |            |

| F420                        | NVMADDR <sup>(1)</sup> | 31:16     |              |       |       |        |         |       |      | NVMADD    | ₽<31·0>   |      |      |      |      |      |        |      | 0000       |

| 1 420                       | NVINADDR               | 15:0      |              |       |       |        |         |       |      | NVINADD   | N~51.02   |      |      |      |      |      |        |      | 0000       |

| F430                        | NVMDATA                | 31:16     |              |       |       |        |         |       |      | NVMDAT    | N~31·0>   |      |      |      |      |      |        |      | 0000       |

| 1 430                       |                        | 15:0      |              |       |       |        |         |       |      |           |           |      |      |      |      |      |        |      | 0000       |

| E440                        | NVMSRCADDR             | 31:16     |              |       |       |        |         |       | N    | VMSRCAD   |           |      |      |      |      |      |        |      | 0000       |

| 1 440                       | NVINGRCADDR            | 15:0      |              |       |       |        |         |       | IN   | VIVIGRUAL | 011-01.02 |      |      |      |      |      |        |      | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |

| 31:24        | NVMKEY<31:24>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |

| 23:16        | NVMKEY<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |

| 15:8         |                   |                   |                   | NVMK              | EY<15:8>          |                   |                  |                  |  |  |  |  |

| 7.0          | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |

| 7:0          | NVMKEY<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

#### REGISTER 5-2: NVMKEY: PROGRAMMING UNLOCK REGISTER

# Legend:

| Legena.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-0 NVMKEY<31:0>: Unlock Register bits

These bits are write-only, and read as '0' on any read

Note: This register is used as part of the unlock sequence to prevent inadvertent writes to the PFM.

#### REGISTER 5-3: NVMADDR: FLASH ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | NVMADDR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 22:40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | NVMADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         |                   |                   |                   | NVMAD             | DR<15:8>          |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | NVMAE             | )DR<7:0>          |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-0 NVMADDR<31:0>: Flash Address bits

Bulk/Chip/PFM Erase: Address is ignored. Page Erase: Address identifies the page to erase. Row Program: Address identifies the row to program. Word Program: Address identifies the word to program.

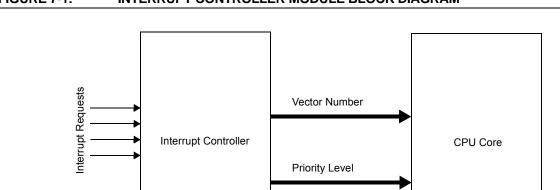

# 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Interrupt Controller" (DS60001108), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The PIC32MX1XX/2XX 28/36/44-pin Family interrupt module includes the following features:

- Up to 64 interrupt sources

- · Up to 44 interrupt vectors

- · Single and multi-vector mode operations

- Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable subpriority levels within each priority

- · Software can generate any interrupt

- User-configurable Interrupt Vector Table (IVT) location

- User-configurable interrupt vector spacing

A simplified block diagram of the Interrupt Controller module is illustrated in Figure 7-1.

#### FIGURE 7-1: INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

Note: The dedicated shadow register set is not present on PIC32MX1XX/2XX 28/36/44-pin Family devices.

| Interrupt Source <sup>(1)</sup>       | IRQ | Vector |          | Interru       | pt Bit Location |              | Persistent |

|---------------------------------------|-----|--------|----------|---------------|-----------------|--------------|------------|

| Interrupt Source.                     | #   | #      | Flag     | Enable        | Priority        | Sub-priority | Interrupt  |

| U1E – UART1 Fault                     | 39  | 32     | IFS1<7>  | IEC1<7>       | IPC8<4:2>       | IPC8<1:0>    | Yes        |

| U1RX – UART1 Receive Done             | 40  | 32     | IFS1<8>  | IEC1<8>       | IPC8<4:2>       | IPC8<1:0>    | Yes        |

| U1TX – UART1 Transfer Done            | 41  | 32     | IFS1<9>  | IEC1<9>       | IPC8<4:2>       | IPC8<1:0>    | Yes        |

| I2C1B – I2C1 Bus Collision Event      | 42  | 33     | IFS1<10> | IEC1<10>      | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| I2C1S – I2C1 Slave Event              | 43  | 33     | IFS1<11> | IEC1<11>      | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| I2C1M – I2C1 Master Event             | 44  | 33     | IFS1<12> | IEC1<12>      | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CNA – PORTA Input Change<br>Interrupt | 45  | 34     | IFS1<13> | IEC1<13>      | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| CNB – PORTB Input Change<br>Interrupt | 46  | 34     | IFS1<14> | IEC1<14>      | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| CNC – PORTC Input Change<br>Interrupt | 47  | 34     | IFS1<15> | IEC1<15>      | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| PMP – Parallel Master Port            | 48  | 35     | IFS1<16> | IEC1<16>      | IPC8<28:26>     | IPC8<25:24>  | Yes        |

| PMPE – Parallel Master Port Error     | 49  | 35     | IFS1<17> | IEC1<17>      | IPC8<28:26>     | IPC8<25:24>  | Yes        |

| SPI2E – SPI2 Fault                    | 50  | 36     | IFS1<18> | IEC1<18>      | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| SPI2RX – SPI2 Receive Done            | 51  | 36     | IFS1<19> | IEC1<19>      | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| SPI2TX – SPI2 Transfer Done           | 52  | 36     | IFS1<20> | IEC1<20>      | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| U2E – UART2 Error                     | 53  | 37     | IFS1<21> | IEC1<21>      | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| U2RX – UART2 Receiver                 | 54  | 37     | IFS1<22> | IEC1<22>      | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| U2TX – UART2 Transmitter              | 55  | 37     | IFS1<23> | IEC1<23>      | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| I2C2B – I2C2 Bus Collision Event      | 56  | 38     | IFS1<24> | IEC1<24>      | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| I2C2S – I2C2 Slave Event              | 57  | 38     | IFS1<25> | IEC1<25>      | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| I2C2M – I2C2 Master Event             | 58  | 38     | IFS1<26> | IEC1<26>      | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| CTMU – CTMU Event                     | 59  | 39     | IFS1<27> | IEC1<27>      | IPC9<28:26>     | IPC9<25:24>  | Yes        |

| DMA0 – DMA Channel 0                  | 60  | 40     | IFS1<28> | IEC1<28>      | IPC10<4:2>      | IPC10<1:0>   | No         |

| DMA1 – DMA Channel 1                  | 61  | 41     | IFS1<29> | IEC1<29>      | IPC10<12:10>    | IPC10<9:8>   | No         |

| DMA2 – DMA Channel 2                  | 62  | 42     | IFS1<30> | IEC1<30>      | IPC10<20:18>    | IPC10<17:16> | No         |

| DMA3 – DMA Channel 3                  | 63  | 43     | IFS1<31> | IEC1<31>      | IPC10<28:26>    | IPC10<25:24> | No         |

|                                       |     | Lowes  |          | rder Priority | E 4. ((DIOOON)) |              |            |

#### TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX 28/36/44-Pin General Purpose Family Features" and TABLE 2: "PIC32MX2XX 28/36/44-pin USB Family Features" for the lists of available peripherals.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | —                 | —                 | —                 |                   | IP03<2:0>         | IS03<1:0>         |                  |                  |

| 23:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | _                 | —                 |                   |                   | IP02<2:0>         | IS02<1:0>         |                  |                  |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         | _                 | —                 |                   |                   | IP01<2:0>         |                   |                  | <1:0>            |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | _                 | _                 | _                 |                   | IP00<2:0>         | IS00<1:0>         |                  |                  |

#### REGISTER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

#### Legend:

| Logonal           |                               |                      |                    |

|-------------------|-------------------------------|----------------------|--------------------|

| R = Readable bit  | Readable bit W = Writable bit |                      | ead as '0'         |

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-26 IP03<2:0>: Interrupt Priority bits

- 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1 000 = Interrupt is disabled bit 25-24 IS03<1:0>: Interrupt Subpriority bits 11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1 00 = Interrupt subpriority is 0 bit 23-21 Unimplemented: Read as '0' bit 20-18 IP02<2:0>: Interrupt Priority bits 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1 000 = Interrupt is disabled bit 17-16 IS02<1:0>: Interrupt Subpriority bits 11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1 00 = Interrupt subpriority is 0 bit 15-13 Unimplemented: Read as '0' bit 12-10 IP01<2:0>: Interrupt Priority bits 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1

- 000 = Interrupt is disabled

- **Note:** This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions.

#### REGISTER 10-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 **PPBRST:** Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the EVEN Buffer Descriptor banks

- 0 = Even/Odd buffer pointers are not Reset

- bit 0 USBEN: USB Module Enable bit<sup>(4)</sup>

- 1 = USB module and supporting circuitry is enabled

- 0 = USB module and supporting circuitry is disabled

SOFEN: SOF Enable bit<sup>(5)</sup>

- 1 = SOF token is sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

#### TABLE 11-2: OUTPUT PIN SELECTION

| RPn Port Pin | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection       |

|--------------|----------|-------------|---------------------------------------------|

| RPA0         | RPA0R    | RPA0R<3:0>  | 0000 = No Connect                           |

| RPB3         | RPB3R    | RPB3R<3:0>  | 0001 = <u>U1TX</u><br>0010 = <u>U2RTS</u>   |

| RPB4         | RPB4R    | RPB4R<3:0>  | 0011 = SS1                                  |

| RPB15        | RPB15R   | RPB15R<3:0> |                                             |

| RPB7         | RPB7R    | RPB7R<3:0>  | 0110 = Reserved<br>0111 = C2OUT             |

| RPC7         | RPC7R    | RPC7R<3:0>  | 1000 = Reserved                             |

| RPC0         | RPC0R    | RPC0R<3:0>  | •                                           |

| RPC5         | RPC5R    | RPC5R<3:0>  | •<br>1111 = Reserved                        |

| RPA1         | RPA1R    | RPA1R<3:0>  | 0000 = No Connect                           |

| RPB5         | RPB5R    | RPB5R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPB1         | RPB1R    | RPB1R<3:0>  | 0011 = SDO1                                 |

| RPB11        | RPB11R   | RPB11R<3:0> | 0100 = SDO2<br>0101 = OC2                   |

| RPB8         | RPB8R    | RPB8R<3:0>  | 0110 = Reserved                             |

| RPA8         | RPA8R    | RPA8R<3:0>  |                                             |

| RPC8         | RPC8R    | RPC8R<3:0>  | •                                           |

| RPA9         | RPA9R    | RPA9R<3:0>  | 1111 = Reserved                             |

| RPA2         | RPA2R    | RPA2R<3:0>  | 0000 = No Connect                           |

| RPB6         | RPB6R    | RPB6R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPA4         | RPA4R    | RPA4R<3:0>  | 0011 = SDO1<br>0100 = SDO2                  |

| RPB13        | RPB13R   | RPB13R<3:0> | 0101 <b>= OC4</b>                           |

| RPB2         | RPB2R    | RPB2R<3:0>  |                                             |

| RPC6         | RPC6R    | RPC6R<3:0>  | 1000 = Reserved                             |

| RPC1         | RPC1R    | RPC1R<3:0>  |                                             |

| RPC3         | RPC3R    | RPC3R<3:0>  | 1111 = Reserved                             |

| RPA3         | RPA3R    | RPA3R<3:0>  | 0000 = No Connect                           |

| RPB14        | RPB14R   | RPB14R<3:0> |                                             |

| RPB0         | RPB0R    | RPB0R<3:0>  | 0011 = <u>Reserved</u><br>0100 = <u>SS2</u> |

| RPB10        | RPB10R   | RPB10R<3:0> | 0101 <b>= OC3</b>                           |

| RPB9         | RPB9R    | RPB9R<3:0>  |                                             |

| RPC9         | RPC9R    | RPC9R<3:0>  | 1000 = Reserved                             |

| RPC2         | RPC2R    | RPC2R<3:0>  |                                             |

| RPC4         | RPC4R    | RPC4R<3:0>  | 1111 = Reserved                             |

#### TABLE 11-7: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| ss                          |                      |           |       |       | Bits  |       |       |       |      |      |      |      |      |      |      |      |       |      |            |

|-----------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|-------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0 | All Resets |

| 5000                        | RPC8R <sup>(1)</sup> | 31:16     | _     | —     | —     | —     | —     | _     | —    | —    | _    | —    | —    | —    | _    | —    | —     | —    | 0000       |

| FB8C                        | RPCoR                | 15:0      | —     | —     | —     | —     | —     | _     | —    | —    | _    | —    | —    | —    |      | RPC8 | <3:0> |      | 0000       |

| 5000                        | RPC9R <sup>(3)</sup> | 31:16     | —     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | _    | _    | —    | —     |      | 0000       |

| FB90                        | RPC9R                | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    |      | RPC  | <3:0> |      | 0000       |

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1:

2:

This register is only available on 44-pin devices. This register is only available on PIC32MX1XX devices. This register is only available on 36-pin and 44-pin devices. 3:

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 02:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | —                 | -                 | -                 | _                 | _                 | -                | —                |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8      | 0N <sup>(1)</sup> | —                 | SIDL              | _                 | _                 | _                 | FEDGE            | C32              |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | ICTMR             | ICI<              | 1:0>              | ICOV              | ICBNE             |                   | ICM<2:0>         |                  |

#### REGISTER 15-1: ICxCON: INPUT CAPTURE 'x' CONTROL REGISTER

# Legend:

| R = Readable bit                        | W = Writable bit | U = Unimplemented bit |                  |

|-----------------------------------------|------------------|-----------------------|------------------|

| -n = Bit Value at POR: ('0', '1', x = u | nknown)          | P = Programmable bit  | r = Reserved bit |

| bit 31-16 | Unimplemented: Read as '0'                                                                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | <b>ON:</b> Input Capture Module Enable bit <sup>(1)</sup>                                                                                                                                |

|           | 1 = Module is enabled                                                                                                                                                                    |

|           | 0 = Disable and reset module, disable clocks, disable interrupt generation and allow SFR modifications                                                                                   |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 13    | SIDL: Stop in Idle Control bit                                                                                                                                                           |

|           | <ul> <li>1 = Halt in Idle mode</li> <li>0 = Continue to operate in Idle mode</li> </ul>                                                                                                  |

| bit 12-10 | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 9     | FEDGE: First Capture Edge Select bit (only used in mode 6, ICM<2:0> = 110)                                                                                                               |

|           | 1 = Capture rising edge first                                                                                                                                                            |

|           | 0 = Capture falling edge first                                                                                                                                                           |

| bit 8     | C32: 32-bit Capture Select bit                                                                                                                                                           |

|           | 1 = 32-bit timer resource capture                                                                                                                                                        |

|           | 0 = 16-bit timer resource capture                                                                                                                                                        |

| bit 7     | ICTMR: Timer Select bit (Does not affect timer selection when C32 (ICxCON<8>) is '1')                                                                                                    |

|           | 0 = Timer3 is the counter source for capture                                                                                                                                             |

|           | 1 = Timer2 is the counter source for capture                                                                                                                                             |

| bit 6-5   | ICI<1:0>: Interrupt Control bits                                                                                                                                                         |

|           | <ul> <li>11 = Interrupt on every fourth capture event</li> <li>10 = Interrupt on every third capture event</li> </ul>                                                                    |

|           | 01 = Interrupt on every second capture event                                                                                                                                             |

|           | 00 = Interrupt on every capture event                                                                                                                                                    |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                                                 |

|           | 1 = Input capture overflow has occurred                                                                                                                                                  |

|           | 0 = No input capture overflow has occurred                                                                                                                                               |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                                                             |

|           | <ul> <li>1 = Input capture buffer is not empty; at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>                                        |

| Note 1:   | When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. |

|           | STOCEN Gyole infinediately following the instruction that deals the module's ON bit.                                                                                                     |

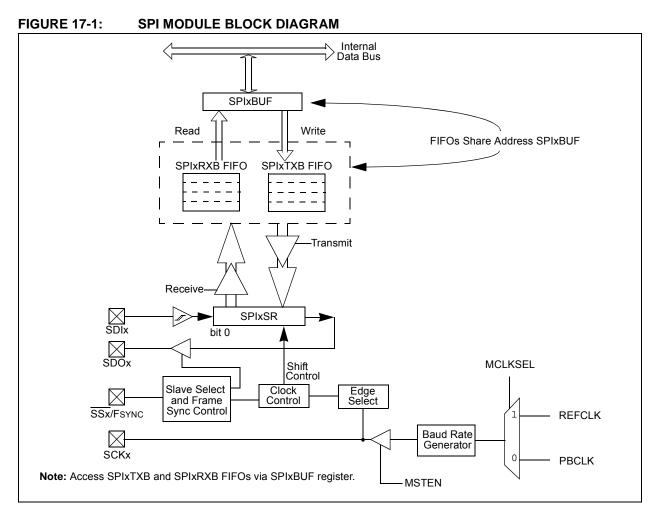

# 17.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS60001106), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontrollers. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters (ADC), etc. The PIC32 SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces. Some of the key features of the SPI module are:

- Master mode and Slave mode support

- Four clock formats

- Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

FIFO buffers act as 4/8/16-level deep FIFOs based on 32/16/8-bit data width

- Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- · Operation during Sleep and Idle modes

- Audio Codec Support:

- I<sup>2</sup>S protocol

- Left-justified

- Right-justified

- PCM

## 28.0 INSTRUCTION SET

The PIC32MX1XX/2XX family instruction set complies with the MIPS32<sup>®</sup> Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- · Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

**Note:** Refer to *"MIPS32<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set"* at www.imgtec.com for more information.

#### TABLE 30-18: PLL CLOCK TIMING SPECIFICATIONS

| AC CHARACTERISTICS |        |                                                                     | (unless ot        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |         |      |                                |                                      |  |  |

|--------------------|--------|---------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|--------------------------------|--------------------------------------|--|--|

| Param.<br>No.      | Symbol | Characteristi                                                       | cs <sup>(1)</sup> | Min.                                                                                                                                                                                                                                                                                | Typical | Max. | Units                          | Conditions                           |  |  |

| OS50               | Fplli  | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range |                   | 3.92                                                                                                                                                                                                                                                                                | _       | 5    | MHz                            | ECPLL, HSPLL, XTPLL,<br>FRCPLL modes |  |  |

| OS51               | Fsys   | On-Chip VCO Syste<br>Frequency                                      | m                 | 60                                                                                                                                                                                                                                                                                  | —       | 120  | MHz                            | _                                    |  |  |

| OS52               | TLOCK  | PLL Start-up Time (L                                                | ock Time)         | _                                                                                                                                                                                                                                                                                   | _       | 2    | ms                             | —                                    |  |  |

| OS53               | DCLK   | CLKO Stability <sup>(2)</sup><br>(Period Jitter or Cum              | -0.25             | —                                                                                                                                                                                                                                                                                   | +0.25   | %    | Measured over 100 ms<br>period |                                      |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{SYSCLK}{CommunicationClock}}}$$

For example, if SYSCLK = 40 MHz and SPI bit rate = 20 MHz, the effective jitter is as follows:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{40}{20}}} = \frac{D_{CLK}}{1.41}$$

#### TABLE 30-19: INTERNAL FRC ACCURACY

| АС СНА                                          | RACTERISTICS    | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |         |      |       |            |  |  |  |

|-------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|--|--|

| Param.<br>No.                                   | Characteristics | Min.                                                                                                                                                                                               | Typical | Max. | Units | Conditions |  |  |  |

| Internal FRC Accuracy @ 8.00 MHz <sup>(1)</sup> |                 |                                                                                                                                                                                                    |         |      |       |            |  |  |  |

| F20b                                            | FRC             | -0.9                                                                                                                                                                                               |         | +0.9 | %     | _          |  |  |  |

Note 1: Frequency calibrated at 25°C and 3.3V. The TUN bits can be used to compensate for temperature drift.

#### TABLE 30-20: INTERNAL LPRC ACCURACY

| АС СНА                          | RACTERISTICS    | $\label{eq:standard operating Conditions: 2.3V to 3.6V} \end{tabular} \begin{tabular}{lllllllllllllllllllllllllllllllllll$ |         |      |       |            |  |  |  |  |

|---------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|--|--|--|

| Param.<br>No.                   | Characteristics |                                                                                                                            | Typical | Max. | Units | Conditions |  |  |  |  |

| LPRC @ 31.25 kHz <sup>(1)</sup> |                 |                                                                                                                            |         |      |       |            |  |  |  |  |

| F21                             | LPRC            | -15 — +15 % —                                                                                                              |         |      |       |            |  |  |  |  |

**Note 1:** Change of LPRC frequency as VDD changes.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

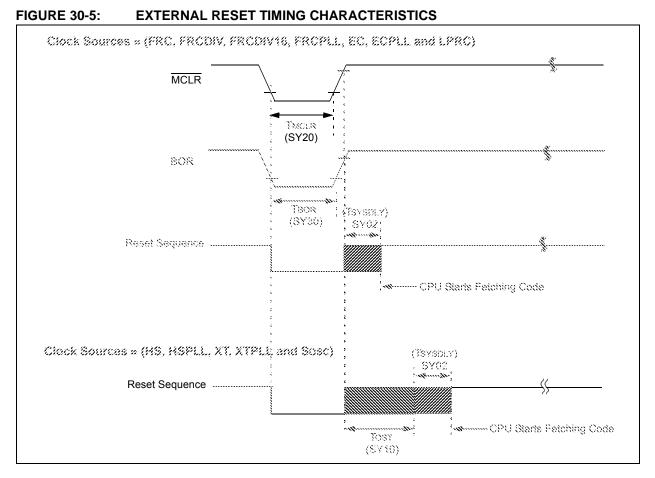

| TABLE              | 30-22: F | RESETS TIMING                                                                                                                              |                                                       |                              |      |       |            |  |  |  |

|--------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------|------|-------|------------|--|--|--|

| AC CHARACTERISTICS |          |                                                                                                                                            | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                              |      |       |            |  |  |  |

| Param.<br>No.      | Symbol   | Characteristics <sup>(1)</sup>                                                                                                             | Min.                                                  | Typical <sup>(2)</sup>       | Max. | Units | Conditions |  |  |  |

| SY00               | Τρυ      | Power-up Period<br>Internal Voltage Regulator Enabled                                                                                      | —                                                     | 400                          | 600  | μS    | _          |  |  |  |

| SY02               | TSYSDLY  | System Delay Period:<br>Time Required to Reload Device<br>Configuration Fuses plus SYSCLK<br>Delay before First instruction is<br>Fetched. | _                                                     | 1 μs +<br>8 SYSCLK<br>cycles | _    | _     | _          |  |  |  |

| SY20               | TMCLR    | MCLR Pulse Width (low)                                                                                                                     | 2                                                     | _                            | _    | μS    | —          |  |  |  |

| SY30               | TBOR     | BOR Pulse Width (low)                                                                                                                      |                                                       | 1                            | _    | μS    | —          |  |  |  |

These parameters are characterized, but not tested in manufacturing. Note 1:

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Characterized by design but not tested.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### FIGURE 30-10: SPIx MODULE MASTER MODE (CKE = 0) TIMING CHARACTERISTICS SCKx (CKP = 0) SP11 SP10 SP21 SP20 SCKx (CKP = 1) SP35 SP20 SP21 SDOx MSb Bit 14 -1 LSb **SP31** SP30 SDIx LSb In MSb In Bit 14 SP40 'SP41' Note: Refer to Figure 30-1 for load conditions.

#### TABLE 30-28: SPIx MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHA        | AC CHARACTERISTICS    |                                            |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |                    |  |  |  |

|---------------|-----------------------|--------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------|--|--|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>             | Min.   | Typical <sup>(2)</sup>                                                                                                                                                                                                                                                                | Max. | Units | Conditions         |  |  |  |

| SP10          | TscL                  | SCKx Output Low Time<br>(Note 3)           | Тѕск/2 | _                                                                                                                                                                                                                                                                                     |      | ns    | _                  |  |  |  |

| SP11          | TscH                  | SCKx Output High Time<br>(Note 3)          | Тѕск/2 | —                                                                                                                                                                                                                                                                                     | _    | ns    | _                  |  |  |  |

| SP20          | TscF                  | SCKx Output Fall Time (Note 4)             | —      | —                                                                                                                                                                                                                                                                                     |      | ns    | See parameter DO32 |  |  |  |

| SP21          | TscR                  | SCKx Output Rise Time<br>(Note 4)          | —      | —                                                                                                                                                                                                                                                                                     | _    | ns    | See parameter DO31 |  |  |  |

| SP30          | TDOF                  | SDOx Data Output Fall Time (Note 4)        | —      | —                                                                                                                                                                                                                                                                                     | _    | ns    | See parameter DO32 |  |  |  |

| SP31          | TDOR                  | SDOx Data Output Rise Time (Note 4)        | —      | _                                                                                                                                                                                                                                                                                     | _    | ns    | See parameter DO31 |  |  |  |

| SP35          | TscH2doV,             | SDOx Data Output Valid after               | —      | —                                                                                                                                                                                                                                                                                     | 15   | ns    | VDD > 2.7V         |  |  |  |

|               | TscL2doV              | SCKx Edge                                  |        | _                                                                                                                                                                                                                                                                                     | 20   | ns    | VDD < 2.7V         |  |  |  |

| SP40          | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge | 10     | —                                                                                                                                                                                                                                                                                     | —    | ns    | —                  |  |  |  |

| SP41          | TSCH2DIL,<br>TSCL2DIL | Hold Time of SDIx Data Input to SCKx Edge  | 10     | —                                                                                                                                                                                                                                                                                     |      | ns    |                    |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 50 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

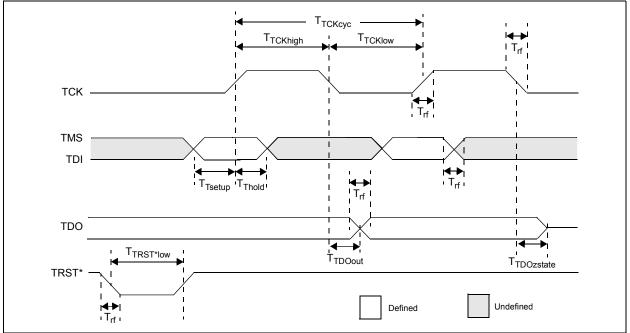

#### FIGURE 30-23: EJTAG TIMING CHARACTERISTICS

#### TABLE 30-42: EJTAG TIMING REQUIREMENTS

| AC CHA        | AC CHARACTERISTICS |                                                  |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industria} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |       |            |  |  |  |

|---------------|--------------------|--------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|--|--|--|

| Param.<br>No. | Symbol             | Description <sup>(1)</sup>                       | Min. | Max.                                                                                                                                                                                                                                                                                 | Units | Conditions |  |  |  |

| EJ1           | Ттсксус            | TCK Cycle Time                                   | 25   |                                                                                                                                                                                                                                                                                      | ns    | _          |  |  |  |

| EJ2           | Ттскнідн           | TCK High Time                                    | 10   | _                                                                                                                                                                                                                                                                                    | ns    | —          |  |  |  |

| EJ3           | TTCKLOW            | TCK Low Time                                     | 10   | _                                                                                                                                                                                                                                                                                    | ns    | _          |  |  |  |

| EJ4           | TTSETUP            | TAP Signals Setup Time Before<br>Rising TCK      | 5    | _                                                                                                                                                                                                                                                                                    | ns    | _          |  |  |  |

| EJ5           | TTHOLD             | TAP Signals Hold Time After<br>Rising TCK        | 3    | -                                                                                                                                                                                                                                                                                    | ns    | —          |  |  |  |

| EJ6           | Ττροουτ            | TDO Output Delay Time from<br>Falling TCK        | -    | 5                                                                                                                                                                                                                                                                                    | ns    | —          |  |  |  |

| EJ7           | TTDOZSTATE         | TDO 3-State Delay Time from<br>Falling TCK       | _    | 5                                                                                                                                                                                                                                                                                    | ns    | _          |  |  |  |

| EJ8           | TTRSTLOW           | TRST Low Time                                    | 25   |                                                                                                                                                                                                                                                                                      | ns    |            |  |  |  |

| EJ9           | Trf                | TAP Signals Rise/Fall Time, All Input and Output | —    | _                                                                                                                                                                                                                                                                                    | ns    | _          |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

#### 31.1 DC Characteristics

#### TABLE 31-1: OPERATING MIPS VS. VOLTAGE

| Characteristic | VDD Range                 | Temp. Range    | Max. Frequency                     |

|----------------|---------------------------|----------------|------------------------------------|

| Characteristic | (in Volts) <sup>(1)</sup> | (in °C)        | PIC32MX1XX/2XX 28/36/44-pin Family |

| MDC5           | 2.3-3.6V                  | -40°C to +85°C | 50 MHz                             |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 30-11 for BOR values.

#### TABLE 31-2: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACTERISTICS                  |                        |      | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |            |  |

|-------------------------------------|------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|

| Parameter<br>No.                    | Typical <sup>(3)</sup> | Max. | Units                                                                                                                                               | Conditions |  |

| Operating Current (IDD) (Note 1, 2) |                        |      |                                                                                                                                                     |            |  |

| MDC24                               | 25                     | 37   | mA                                                                                                                                                  | 50 MHz     |  |

**Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

- 2: The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, Program Flash, and SRAM data memory are operational, SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- CPU executing while(1) statement from Flash

- 3: RTCC and JTAG are disabled

- **4:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

#### TABLE 31-3: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARACTERISTICS                                             |                        |      | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |            |  |

|----------------------------------------------------------------|------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|

| Parameter<br>No.                                               | Typical <sup>(2)</sup> | Max. | Units                                                                                                                                           | Conditions |  |

| Idle Current (IIDLE): Core Off, Clock on Base Current (Note 1) |                        |      |                                                                                                                                                 |            |  |

| MDC34a                                                         | 8                      | 13   | mA                                                                                                                                              | 50 MHz     |  |

Note 1: The test conditions for IIDLE current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- + CPU is in Idle mode (CPU core Halted), and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.