Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                  |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Through Hole                                                                     |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                          |

| Supplier Device Package    | 28-SPDIP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx150f128b-50i-sp |

### **Table of Contents**

| 1.0   | Device Overview                                    | 19  |

|-------|----------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 32-bit MCUs.   |     |

| 3.0   | CPU.                                               |     |

| 4.0   | Memory Organization                                |     |

| 5.0   | Flash Program Memory                               |     |

| 6.0   | Resets                                             |     |

| 7.0   | Interrupt Controller                               |     |

| 8.0   | Oscillator Configuration                           | 73  |

| 9.0   | Direct Memory Access (DMA) Controller              | 83  |

| 10.0  | USB On-The-Go (OTG)                                | 103 |

| 11.0  | I/O Ports                                          | 127 |

| 12.0  | Timer1                                             | 143 |

| 13.0  | Timer2/3, Timer4/5                                 | 147 |

| 14.0  | Watchdog Timer (WDT)                               | 153 |

| 15.0  | Input Capture                                      | 157 |

|       | Output Compare                                     |     |

| 17.0  | Serial Peripheral Interface (SPI)                  | 165 |

| 18.0  | Inter-Integrated Circuit (I <sup>2</sup> C)        |     |

| 19.0  | Universal Asynchronous Receiver Transmitter (UART) | 181 |

|       | Parallel Master Port (PMP)                         |     |

|       | Real-Time Clock and Calendar (RTCC)                |     |

| 22.0  | 10-bit Analog-to-Digital Converter (ADC)           | 209 |

| 23.0  | Comparator                                         |     |

| 24.0  | Comparator Voltage Reference (CVREF)               | 223 |

| 25.0  | Charge Time Measurement Unit (CTMU)                | 227 |

| 26.0  | Power-Saving Features                              | 233 |

| 27.0  | Special Features                                   | 239 |

| 28.0  | Instruction Set                                    |     |

| 29.0  | Development Support                                | 253 |

|       | Electrical Characteristics                         |     |

|       | 50 MHz Electrical Characteristics                  |     |

|       | DC and AC Device Characteristics Graphs            |     |

|       | Packaging Information                              |     |

|       | Aicrochip Web Site                                 |     |

|       | omer Change Notification Service                   |     |

|       | omer Support                                       |     |

| Produ | uct Identification System                          | 342 |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |               | Pin Nu                            | mber <sup>(1)</sup> |                                 |             |                |                                                |

|----------|---------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------|------------------------------------------------|

| Pin Name | 28-pin<br>QFN | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                    |

| RC0      | _             | _                                 | 3                   | 25                              | I/O         | ST             | PORTC is a bidirectional I/O port              |

| RC1      | _             | _                                 | 4                   | 26                              | I/O         | ST             |                                                |

| RC2      |               | _                                 |                     | 27                              | I/O         | ST             |                                                |

| RC3      | _             | _                                 | 11                  | 36                              | I/O         | ST             |                                                |

| RC4      | _             | _                                 | _                   | 37                              | I/O         | ST             |                                                |

| RC5      | _             | _                                 | _                   | 38                              | I/O         | ST             |                                                |

| RC6      | _             | _                                 | _                   | 2                               | I/O         | ST             |                                                |

| RC7      | _             | _                                 | _                   | 3                               | I/O         | ST             |                                                |

| RC8      | _             | _                                 | _                   | 4                               | I/O         | ST             |                                                |

| RC9      | _             | _                                 | 20                  | 5                               | I/O         | ST             |                                                |

| T1CK     | 9             | 12                                | 10                  | 34                              | I           | ST             | Timer1 external clock input                    |

| T2CK     | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | Timer2 external clock input                    |

| T3CK     | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | Timer3 external clock input                    |

| T4CK     | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | Timer4 external clock input                    |

| T5CK     | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | Timer5 external clock input                    |

| U1CTS    | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | UART1 clear to send                            |

| U1RTS    | PPS           | PPS                               | PPS                 | PPS                             | 0           | _              | UART1 ready to send                            |

| U1RX     | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | UART1 receive                                  |

| U1TX     | PPS           | PPS                               | PPS                 | PPS                             | 0           | _              | UART1 transmit                                 |

| U2CTS    | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | UART2 clear to send                            |

| U2RTS    | PPS           | PPS                               | PPS                 | PPS                             | 0           | _              | UART2 ready to send                            |

| U2RX     | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | UART2 receive                                  |

| U2TX     | PPS           | PPS                               | PPS                 | PPS                             | 0           | _              | UART2 transmit                                 |

| SCK1     | 22            | 25                                | 28                  | 14                              | I/O         | ST             | Synchronous serial clock input/output for SPI1 |

| SDI1     | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | SPI1 data in                                   |

| SDO1     | PPS           | PPS                               | PPS                 | PPS                             | 0           | _              | SPI1 data out                                  |

| SS1      | PPS           | PPS                               | PPS                 | PPS                             | I/O         | ST             | SPI1 slave synchronization or frame pulse I/O  |

| SCK2     | 23            | 26                                | 29                  | 15                              | I/O         | ST             | Synchronous serial clock input/output for SPI2 |

| SDI2     | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | SPI2 data in                                   |

| SDO2     | PPS           | PPS                               | PPS                 | PPS                             | 0           | _              | SPI2 data out                                  |

| SS2      | PPS           | PPS                               | PPS                 | PPS                             | I/O         | ST             | SPI2 slave synchronization or frame pulse I/O  |

| SCL1     | 14            | 17                                | 18                  | 44                              | I/O         | ST             | Synchronous serial clock input/output for I2C1 |

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer Analog = Analog input

O = Output

PPS = Peripheral Pin Select

P = Power I = Input — = N/A

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

- 2: Pin number for PIC32MX1XX devices only.

- 3: Pin number for PIC32MX2XX devices only.

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

TABLE 3-3: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE EXCEPTION TYPES

| F         | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Exception | Description                                                                                                                             |

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                               |

| DSS       | EJTAG debug single step.                                                                                                                |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                                |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                            |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                         |

| AdEL      | Fetch address alignment error. Fetch reference to protected address.                                                                    |

| IBE       | Instruction fetch bus error.                                                                                                            |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                                      |

| Sys       | Execution of SYSCALL instruction.                                                                                                       |

| Вр        | Execution of BREAK instruction.                                                                                                         |

| RI        | Execution of a reserved instruction.                                                                                                    |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                           |

| CEU       | Execution of a Corextend instruction when Corextend is not enabled.                                                                     |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                                 |

| Tr        | Execution of a trap (when trap condition is true).                                                                                      |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                           |

| AdEL      | Load address alignment error. Load reference to protected address.                                                                      |

| AdES      | Store address alignment error. Store to protected address.                                                                              |

| DBE       | Load or store bus error.                                                                                                                |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                            |

### 3.3 Power Management

The MIPS M4K processor core offers many power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or Halting the clocks, which reduces system power consumption during Idle periods.

## 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see **Section 26.0** "Power-Saving Features".

### 3.4 EJTAG Debug Support

The MIPS M4K processor core provides an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the M4K core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used.

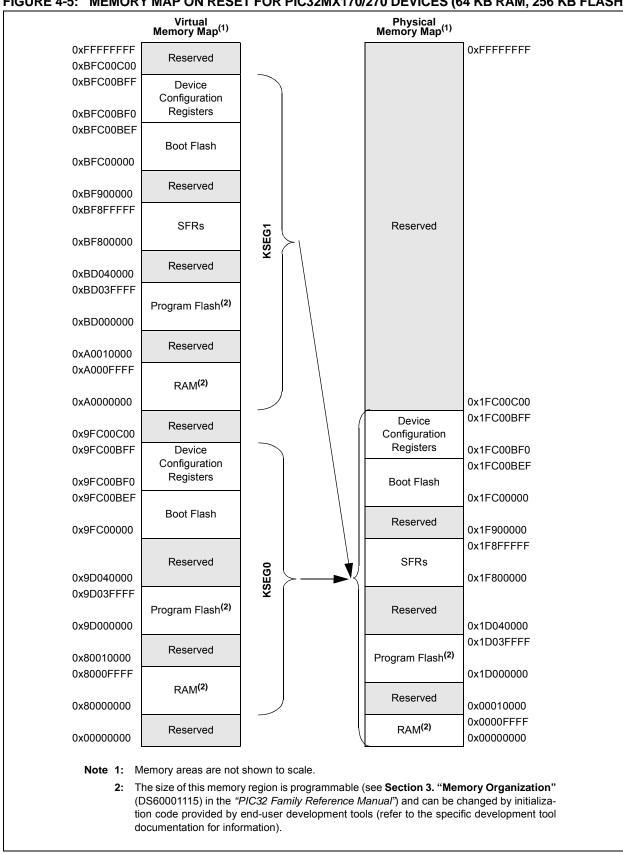

FIGURE 4-5: MEMORY MAP ON RESET FOR PIC32MX170/270 DEVICES (64 KB RAM, 256 KB FLASH)

| PIC32MX1XX | /2XX 28/3 | 86/44-PIN | FAMILY |  |

|------------|-----------|-----------|--------|--|

| NOTES:     |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

### REGISTER 6-1: RCON: RESET CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| 24.24        | U-0                | U-0                |

| 31:24        | _                 | _                 | -                 | _                 | _                 |                   | _                  | _                  |

| 22.46        | U-0                | U-0                |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                  | _                  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS          | R/W-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | CMR                | VREGS              |

| 7.0          | R/W-0, HS         | R/W-0, HS         | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-1, HS          | R/W-1, HS          |

| 7:0          | EXTR              | SWR               | _                 | WDTO              | SLEEP             | IDLE              | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |

**Legend:** HS = Set by hardware

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-10 Unimplemented: Read as '0'

bit 9 **CMR:** Configuration Mismatch Reset Flag bit

1 = Configuration mismatch Reset has occurred

0 = Configuration mismatch Reset has not occurred

bit 8 VREGS: Voltage Regulator Standby Enable bit

1 = Regulator is enabled and is on during Sleep mode

0 = Regulator is disabled and is off during Sleep mode

bit 7 **EXTR:** External Reset (MCLR) Pin Flag bit

1 = Master Clear (pin) Reset has occurred

0 = Master Clear (pin) Reset has not occurred

bit 6 SWR: Software Reset Flag bit

1 = Software Reset was executed

0 = Software Reset as not executed

bit 5 Unimplemented: Read as '0'

bit 4 WDTO: Watchdog Timer Time-out Flag bit

1 = WDT Time-out has occurred

0 = WDT Time-out has not occurred

bit 3 SLEEP: Wake From Sleep Flag bit

1 = Device was in Sleep mode

0 = Device was not in Sleep mode

bit 2 IDLE: Wake From Idle Flag bit

1 = Device was in Idle mode

0 = Device was not in Idle mode

bit 1 **BOR:** Brown-out Reset Flag bit<sup>(1)</sup>

1 = Brown-out Reset has occurred

0 = Brown-out Reset has not occurred

bit 0 **POR:** Power-on Reset Flag bit<sup>(1)</sup>

1 = Power-on Reset has occurred

0 = Power-on Reset has not occurred

**Note 1:** User software must clear this bit to view next detection.

TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

| Intermed Course(1)                 | IRQ | Vector |              | Interru       | pt Bit Location |              | Persistent |

|------------------------------------|-----|--------|--------------|---------------|-----------------|--------------|------------|

| Interrupt Source <sup>(1)</sup>    | #   | #      | Flag         | Enable        | Priority        | Sub-priority | Interrupt  |

| U1E – UART1 Fault                  | 39  | 32     | IFS1<7>      | IEC1<7>       | IPC8<4:2>       | IPC8<1:0>    | Yes        |

| U1RX – UART1 Receive Done          | 40  | 32     | IFS1<8>      | IEC1<8>       | IPC8<4:2>       | IPC8<1:0>    | Yes        |

| U1TX – UART1 Transfer Done         | 41  | 32     | IFS1<9>      | IEC1<9>       | IPC8<4:2>       | IPC8<1:0>    | Yes        |

| I2C1B – I2C1 Bus Collision Event   | 42  | 33     | IFS1<10>     | IEC1<10>      | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| I2C1S - I2C1 Slave Event           | 43  | 33     | IFS1<11>     | IEC1<11>      | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| I2C1M – I2C1 Master Event          | 44  | 33     | IFS1<12>     | IEC1<12>      | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CNA – PORTA Input Change Interrupt | 45  | 34     | IFS1<13>     | IEC1<13>      | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| CNB – PORTB Input Change Interrupt | 46  | 34     | IFS1<14>     | IEC1<14>      | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| CNC – PORTC Input Change Interrupt | 47  | 34     | IFS1<15>     | IEC1<15>      | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| PMP – Parallel Master Port         | 48  | 35     | IFS1<16>     | IEC1<16>      | IPC8<28:26>     | IPC8<25:24>  | Yes        |

| PMPE – Parallel Master Port Error  | 49  | 35     | IFS1<17>     | IEC1<17>      | IPC8<28:26>     | IPC8<25:24>  | Yes        |

| SPI2E – SPI2 Fault                 | 50  | 36     | IFS1<18>     | IEC1<18>      | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| SPI2RX – SPI2 Receive Done         | 51  | 36     | IFS1<19>     | IEC1<19>      | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| SPI2TX – SPI2 Transfer Done        | 52  | 36     | IFS1<20>     | IEC1<20>      | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| U2E – UART2 Error                  | 53  | 37     | IFS1<21>     | IEC1<21>      | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| U2RX – UART2 Receiver              | 54  | 37     | IFS1<22>     | IEC1<22>      | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| U2TX – UART2 Transmitter           | 55  | 37     | IFS1<23>     | IEC1<23>      | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| I2C2B – I2C2 Bus Collision Event   | 56  | 38     | IFS1<24>     | IEC1<24>      | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| I2C2S - I2C2 Slave Event           | 57  | 38     | IFS1<25>     | IEC1<25>      | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| I2C2M – I2C2 Master Event          | 58  | 38     | IFS1<26>     | IEC1<26>      | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| CTMU – CTMU Event                  | 59  | 39     | IFS1<27>     | IEC1<27>      | IPC9<28:26>     | IPC9<25:24>  | Yes        |

| DMA0 – DMA Channel 0               | 60  | 40     | IFS1<28>     | IEC1<28>      | IPC10<4:2>      | IPC10<1:0>   | No         |

| DMA1 – DMA Channel 1               | 61  | 41     | IFS1<29>     | IEC1<29>      | IPC10<12:10>    | IPC10<9:8>   | No         |

| DMA2 – DMA Channel 2               | 62  | 42     | IFS1<30>     | IEC1<30>      | IPC10<20:18>    | IPC10<17:16> | No         |

| DMA3 – DMA Channel 3               | 63  | 43     | IFS1<31>     | IEC1<31>      | IPC10<28:26>    | IPC10<25:24> | No         |

|                                    |     | Lowes  | st Natural O | rder Priority |                 |              |            |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX 28/36/44-Pin General Purpose Family Features" and TABLE 2: "PIC32MX2XX 28/36/44-pin USB Family Features" for the lists of available peripherals.

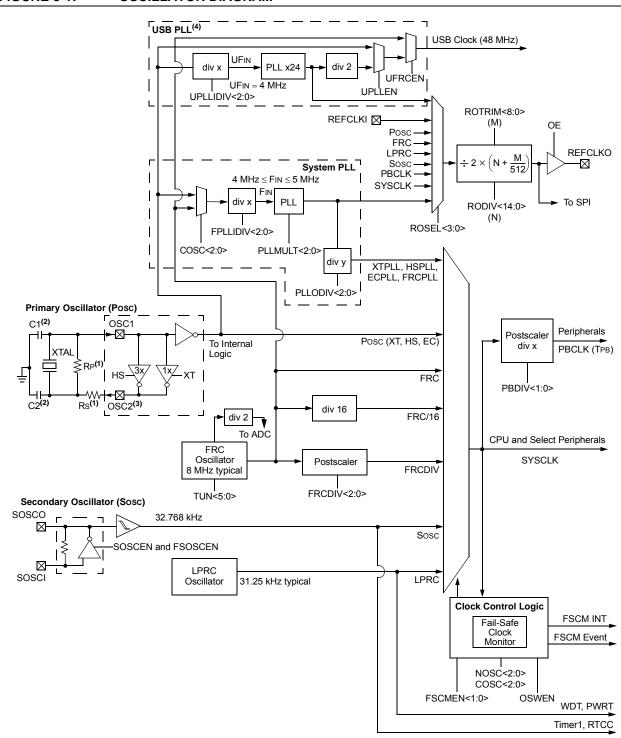

FIGURE 8-1: OSCILLATOR DIAGRAM

- Notes: 1. A series resistor, Rs, may be required for AT strip cut crystals or eliminate clipping. Alternately, to increase oscillator circuit gain, add a parallel resistor, RP, with a value of 1 MΩ.

- Refer to Section 6. "Oscillator Configuration" (DS60001112) in the "PIC32 Family Reference Manual" for help in determining the best oscillator components.

- 3. The PBCLK out is only available on the OSC2 pin in certain clock modes.

- 4. The USB PLL is only available on PIC32MX2XX devices.

#### REGISTER 10-21: U1EP0-U1EP15: USB ENDPOINT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -                 | -                 | 1                 | -                 | -                | -                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | _                 | -                 |                   | -                 | -                 | -                | -                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | LSPD              | RETRYDIS          | _                 | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 LSPD: Low-Speed Direct Connection Enable bit (Host mode and U1EP0 only)

1 = Direct connection to a Low-Speed device enabled

0 = Direct connection to a Low-Speed device disabled; hub required with PRE\_PID

bit 6 RETRYDIS: Retry Disable bit (Host mode and U1EP0 only)

1 = Retry NAKed transactions disabled

0 = Retry NAKed transactions enabled; retry done in hardware

bit 5 **Unimplemented:** Read as '0'

bit 4 **EPCONDIS:** Bidirectional Endpoint Control bit

If EPTXEN = 1 and EPRXEN = 1:

1 = Disable Endpoint n from Control transfers; only TX and RX transfers allowed

0 = Enable Endpoint n for Control (SETUP) transfers; TX and RX transfers also allowed

Otherwise, this bit is ignored.

bit 3 **EPRXEN:** Endpoint Receive Enable bit

1 = Endpoint n receive is enabled

0 = Endpoint n receive is disabled

bit 2 **EPTXEN:** Endpoint Transmit Enable bit

1 = Endpoint n transmit is enabled

0 = Endpoint n transmit is disabled

bit 1 **EPSTALL:** Endpoint Stall Status bit

1 = Endpoint n was stalled

0 = Endpoint n was not stalled

bit 0 **EPHSHK:** Endpoint Handshake Enable bit

1 = Endpoint Handshake is enabled

0 = Endpoint Handshake is disabled (typically used for isochronous endpoints)

### TABLE 11-7: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| ss                          |                      |           |       | Bits  |       |       |       |       |      |      |      |      |      |      |      |      |       |      |            |

|-----------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|-------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0 | All Resets |

| ED00                        | RPC8R <sup>(1)</sup> | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _     | _    | 0000       |

| FB8C                        | RPC8R**              | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPC8 | <3:0> |      | 0000       |

| ED00                        | RPC9R <sup>(3)</sup> | 31:16     | _     | _     | _     | -     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _     | _    | 0000       |

| FB90                        | RPC9R <sup>(*)</sup> | 15:0      | _     | _     | _     |       | 1     | 1     | _    | _    | _    | _    | _    | _    |      | RPC9 | <3:0> |      | 0000       |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1:

This register is only available on 44-pin devices. This register is only available on PIC32MX1XX devices. 2:

This register is only available on 36-pin and 44-pin devices.

### 14.1 Watchdog Timer Control Registers

### TABLE 14-1: WATCHDOG TIMER CONTROL REGISTER MAP

| ess                         |                                 |           |       | Bits  |       |       |       |       |      |      |      |      |      |           |      |      |          | s      |           |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|-----------|------|------|----------|--------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4      | 19/3 | 18/2 | 17/1     | 16/0   | All Reset |

| 0000                        | WDTCON                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _         | _    | _    | _        | _      | 0000      |

| 0000                        | WDTCON                          | 15:0      | ON    | _     | _     | l     | _     | _     | ı    | _    |      |      | SV   | VDTPS<4:0 | )>   |      | WDTWINEN | WDTCLR | 0000      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

### REGISTER 21-1: RTCCON: RTC CONTROL REGISTER (CONTINUED)

- bit 5-4 **Unimplemented:** Read as '0'

- bit 3 RTCWREN: RTC Value Registers Write Enable bit (4)

- 1 = RTC Value registers can be written to by the user

- 0 = RTC Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: RTCC Value Registers Read Synchronization bit

- 1 = RTC Value registers can change while reading, due to a rollover ripple that results in an invalid data read If the register is read twice and results in the same data, the data can be assumed to be valid

- 0 = RTC Value registers can be read without concern about a rollover ripple

- bit 1 HALFSEC: Half-Second Status bit<sup>(5)</sup>

- 1 = Second half period of a second

- 0 = First half period of a second

- bit 0 RTCOE: RTCC Output Enable bit

- 1 = RTCC clock output enabled clock presented onto an I/O

- 0 = RTCC clock output disabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 3: Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- **4:** The RTCWREN bit can be set only when the write sequence is enabled.

- 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

**Note:** This register is reset only on a Power-on Reset (POR).

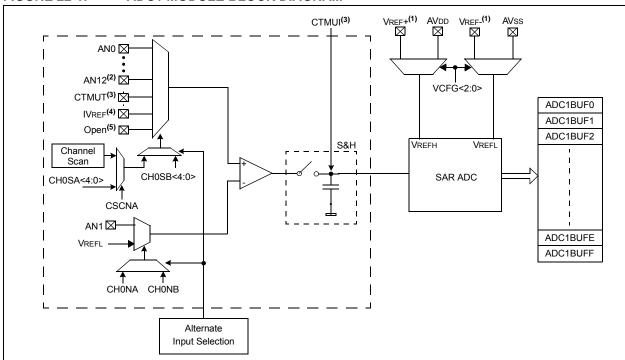

# 22.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- · Up to 1 Msps conversion speed

- · Up to 13 analog input pins

- · External voltage reference input pins

- One unipolar, differential Sample and Hold Amplifier (SHA)

- · Automatic Channel Scan mode

- Selectable conversion trigger source

- · 16-word conversion result buffer

- · Selectable buffer fill modes

- Eight conversion result format options

- · Operation during Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 22-1. Figure 22-2 illustrates a block diagram of the ADC conversion clock period. The 10-bit ADC has up to 13 analog input pins, designated AN0-AN12. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

#### FIGURE 22-1: ADC1 MODULE BLOCK DIAGRAM

- Note 1: VREF+ and VREF- inputs can be multiplexed with other analog inputs.

- 2: AN8 is only available on 44-pin devices. AN6, AN7, and AN12 are not available on 28-pin devices.

- 3: Connected to the CTMU module. See Section 25.0 "Charge Time Measurement Unit (CTMU)" for more information.

- 4: Internal precision voltage reference (1.2V).

- 5: This selection is only used with CTMU capacitive and time measurement.

### 25.1 CTMU Control Registers

### TABLE 25-1: CTMU REGISTER MAP

| ess                      |                                                                                    |           |         | Bits    |       |       |         |       |          |          |         |         |      |       |          |      |      |      |            |

|--------------------------|------------------------------------------------------------------------------------|-----------|---------|---------|-------|-------|---------|-------|----------|----------|---------|---------|------|-------|----------|------|------|------|------------|

| Virtual Addr<br>(BF80_#) | Regist<br>Name<br>Name                                                             | Bit Range | 31/15   | 30/14   | 29/13 | 28/12 | 27/11   | 26/10 | 25/9     | 24/8     | 23/7    | 22/6    | 21/5 | 20/4  | 19/3     | 18/2 | 17/1 | 16/0 | All Resets |

| 4000                     | CTMUCON                                                                            | 31:16     | EDG1MOD | EDG1POL |       | EDG1S | EL<3:0> |       | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL |      | EDG2S | SEL<3:0> |      | _    | _    | 0000       |

| A200                     | CTMUCON 15:0 ON — CTMUSIDL TGEN EDGEN EDGSEQEN IDISSEN CTTRIG ITRIM<5:0> IRNG<1:0> |           |         |         |       |       |         |       |          | 0000     |         |         |      |       |          |      |      |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

### REGISTER 27-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

| Bit<br>Range | Bit<br>31/23/15/7                                    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|------------------------------------------------------|-------------------|-------------------|-------------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | r-0                                                  | r-1               | r-1               | R/P                     | r-1               | r-1               | r-1              | R/P              |

| 31:24        |                                                      | _                 | _                 | CP                      | _                 | _                 |                  | BWP              |

| 22.46        | r-1                                                  | r-1               | r-1               | r-1                     | r-1               | R/P               | R/P              | R/P              |

| 23:16        |                                                      | _                 | I                 | PWP<8:6> <sup>(3)</sup> |                   |                   |                  |                  |

| 45.0         | R/P                                                  | R/P               | R/P               | R/P                     | R/P               | R/P               | r-1              | r-1              |

| 15:8         |                                                      |                   |                   | _                       |                   |                   |                  |                  |

| 7.0          | r-1                                                  | r-1               | r-1               | R/P                     | R/P               | R/P               | R/P              | R/P              |

| 7:0          | — — ICESEL<1:0> <sup>(2)</sup> JTAGEN <sup>(1)</sup> |                   |                   |                         |                   |                   | DEBU             | G<1:0>           |

Legend:r = Reserved bitP = Programmable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31 Reserved: Write '0' bit 30-29 Reserved: Write '1' bit 28 CP: Code-Protect bit

Prevents boot and program Flash memory from being read or modified by an external programming device.

1 = Protection is disabled0 = Protection is enabled

bit 27-25 Reserved: Write '1'

bit 24 **BWP:** Boot Flash Write-Protect bit

Prevents boot Flash memory from being modified during code execution.

1 = Boot Flash is writable0 = Boot Flash is not writable

bit 23-19 Reserved: Write '1'

Note 1: This bit sets the value for the JTAGEN bit in the CFGCON register.

- 2: The PGEC4/PGED4 pin pair is not available on all devices. Refer to the "Pin Diagrams" section for availability.

- 3: The PWP<8:7> bits are only available on devices with 256 KB Flash.

### 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB® X IDE Software

- · Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>TM</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- · In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- · Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- · Third-party development tools

## 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users

#### Feature-Rich Editor:

- · Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

Project-Based Workspaces:

- · Multiple projects

- · Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- · Built-in support for Bugzilla issue tracker

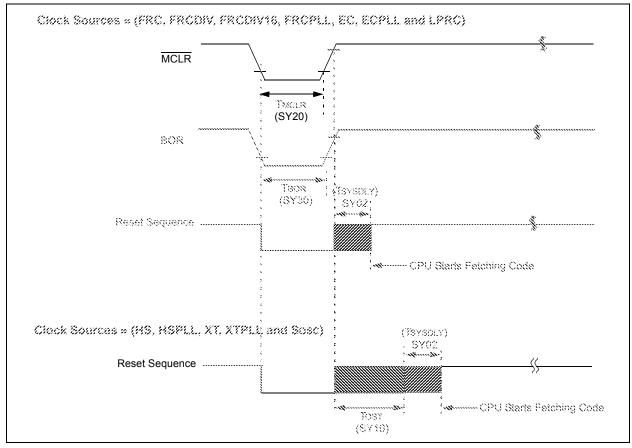

FIGURE 30-5: EXTERNAL RESET TIMING CHARACTERISTICS

**TABLE 30-22: RESETS TIMING**

| AC CHARACTERISTICS |         |                                                                                                                                | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                              |      |       |            |

|--------------------|---------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|-------|------------|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                                                                                 | Min.                                                                                                                                                                                                                                           | Typical <sup>(2)</sup>       | Max. | Units | Conditions |

| SY00               | TPU     | Power-up Period<br>Internal Voltage Regulator Enabled                                                                          | _                                                                                                                                                                                                                                              | 400                          | 600  | μS    | _          |

| SY02               | TSYSDLY | System Delay Period: Time Required to Reload Device Configuration Fuses plus SYSCLK Delay before First instruction is Fetched. | _                                                                                                                                                                                                                                              | 1 μs +<br>8 SYSCLK<br>cycles | l    | _     |            |

| SY20               | TMCLR   | MCLR Pulse Width (low)                                                                                                         | 2                                                                                                                                                                                                                                              | _                            | _    | μS    | _          |

| SY30               | TBOR    | BOR Pulse Width (low)                                                                                                          | _                                                                                                                                                                                                                                              | 1                            | _    | μS    |            |

Note 1: These parameters are characterized, but not tested in manufacturing.

<sup>2:</sup> Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Characterized by design but not tested.

**TABLE 30-37: PARALLEL SLAVE PORT REQUIREMENTS**

| AC CHARACTERISTICS |              |                                                     | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +105^{\circ}\text{C}$ for V-temp |      |      |       |            |  |

|--------------------|--------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|--|

| Para<br>m.No.      | Symbol       | Characteristics <sup>(1)</sup>                      | Min.                                                                                                                                                                                                                                           | Тур. | Max. | Units | Conditions |  |

| PS1                | TdtV2wr<br>H | Data In Valid before WR or CS Inactive (setup time) | 20                                                                                                                                                                                                                                             |      | _    | ns    | _          |  |

| PS2                | TwrH2dt<br>I | WR or CS Inactive to Data-In Invalid (hold time)    | 40                                                                                                                                                                                                                                             | _    | _    | ns    | _          |  |

| PS3                | TrdL2dt<br>V | RD and CS Active to Data-Out Valid                  | _                                                                                                                                                                                                                                              |      | 60   | ns    | _          |  |

| PS4                | TrdH2dtl     | RD Active or CS Inactive to Data-Out Invalid        | 0                                                                                                                                                                                                                                              |      | 10   | ns    | _          |  |

| PS5                | Tcs          | CS Active Time                                      | TpB + 40                                                                                                                                                                                                                                       | _    | _    | ns    | _          |  |

| PS6                | Twr          | WR Active Time                                      | TPB + 25                                                                                                                                                                                                                                       |      | _    | ns    | _          |  |

| PS7                | TRD          | RD Active Time                                      | TpB + 25                                                                                                                                                                                                                                       | _    | _    | ns    | _          |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

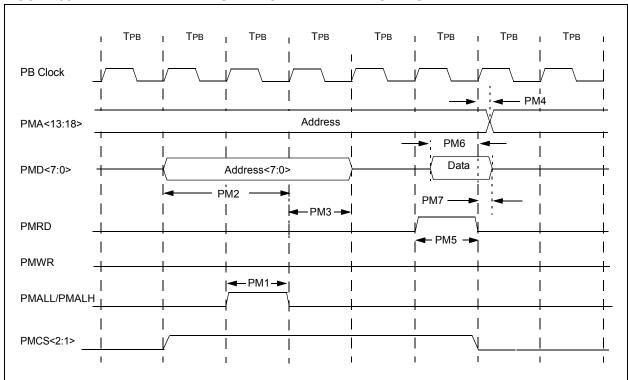

### FIGURE 30-21: PARALLEL MASTER PORT READ TIMING DIAGRAM

TABLE 30-38: PARALLEL MASTER PORT READ TIMING REQUIREMENTS

| AC CHARACTERISTICS |         |                                                                      | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |       |      |       |            |

|--------------------|---------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                       | Min.                                                                                                                                                                                                                                           | Тур.  | Max. | Units | Conditions |

| PM1                | TLAT    | PMALL/PMALH Pulse Width                                              | _                                                                                                                                                                                                                                              | 1 Трв |      | _     | _          |

| PM2                | TADSU   | Address Out Valid to<br>PMALL/PMALH Invalid (address<br>setup time)  | _                                                                                                                                                                                                                                              | 2 Трв |      | _     | _          |

| РМ3                | TADHOLD | PMALL/PMALH Invalid to<br>Address Out Invalid (address<br>hold time) | _                                                                                                                                                                                                                                              | 1 Трв | _    | _     | _          |

| PM4                | TAHOLD  | PMRD Inactive to Address Out<br>Invalid<br>(address hold time)       | 5                                                                                                                                                                                                                                              | _     | _    | ns    | _          |

| PM5                | TRD     | PMRD Pulse Width                                                     | _                                                                                                                                                                                                                                              | 1 Трв |      | _     | _          |

| PM6                | TDSU    | PMRD or PMENB Active to Data In Valid (data setup time)              | 15                                                                                                                                                                                                                                             | _     | _    | ns    | _          |

| PM7                | TDHOLD  | PMRD or PMENB Inactive to Data In Invalid (data hold time)           | _                                                                                                                                                                                                                                              | 80    | _    | ns    | _          |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

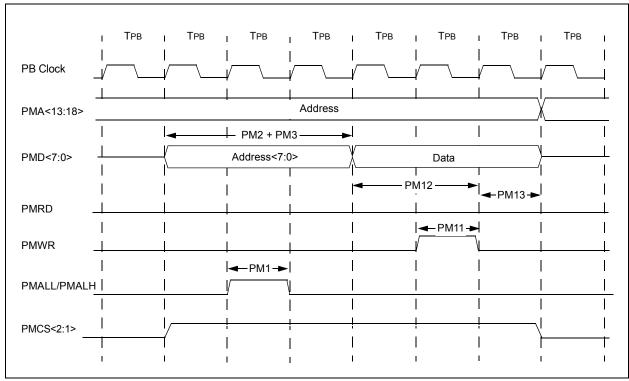

FIGURE 30-22: PARALLEL MASTER PORT WRITE TIMING DIAGRAM

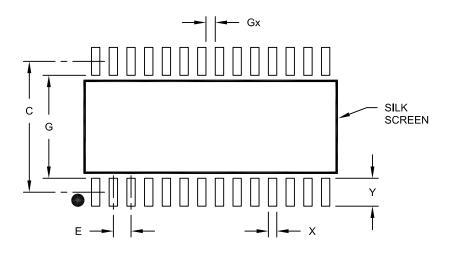

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**lote:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |          |      |      |  |

|--------------------------|-------------|----------|------|------|--|

| Dimension Limits         |             | MIN      | NOM  | MAX  |  |

| Contact Pitch            | E           | 1.27 BSC |      |      |  |

| Contact Pad Spacing      | C           |          | 9.40 |      |  |

| Contact Pad Width (X28)  | Х           |          |      | 0.60 |  |

| Contact Pad Length (X28) | Υ           |          |      | 2.00 |  |

| Distance Between Pads    | Gx          | 0.67     |      |      |  |

| Distance Between Pads    | G           | 7.40     |      | ·    |  |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A