#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betano                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 10x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

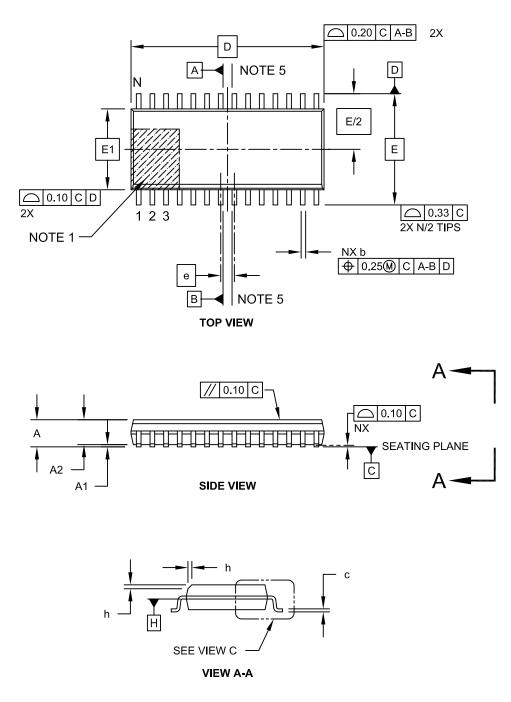

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx150f128b-i-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to documents listed in the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

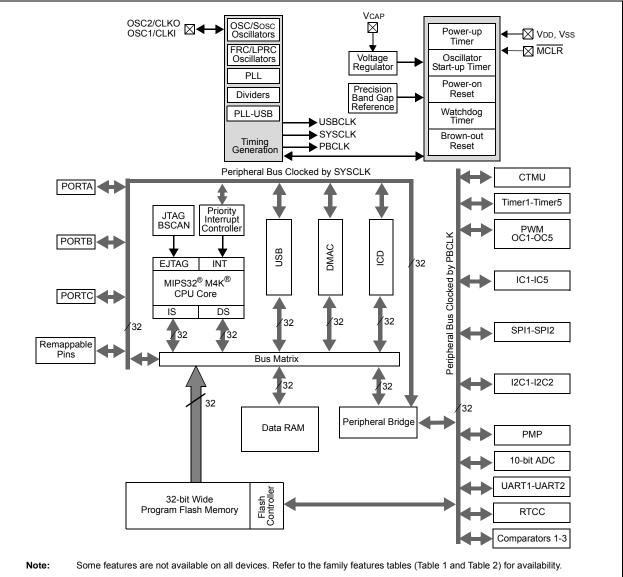

**BLOCK DIAGRAM**

This document contains device-specific information for PIC32MX1XX/2XX 28/36/44-pin Family devices.

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX1XX/2XX 28/36/44-pin Family of devices.

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

FIGURE 1-1:

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

NOTES:

#### TABLE 4-1: SFR MEMORY MAP

|                           | Virtual A | ddress          |

|---------------------------|-----------|-----------------|

| Peripheral                | Base      | Offset<br>Start |

| Watchdog Timer            |           | 0x0000          |

| RTCC                      |           | 0x0200          |

| Timer1-5                  |           | 0x0600          |

| Input Capture 1-5         |           | 0x2000          |

| Output Compare 1-5        |           | 0x3000          |

| IC1 and IC2               |           | 0x5000          |

| SPI1 and SPI2             |           | 0x5800          |

| UART1 and UART2           |           | 0x6000          |

| PMP                       |           | 0x7000          |

| ADC                       | 0xBF80    | 0x9000          |

| CVREF                     |           | 0x9800          |

| Comparator                |           | 0xA000          |

| CTMU                      |           | 0xA200          |

| Oscillator                |           | 0xF000          |

| Device and Revision ID    |           | 0xF220          |

| Peripheral Module Disable |           | 0xF240          |

| Flash Controller          |           | 0xF400          |

| Reset                     |           | 0xF600          |

| PPS                       |           | 0xFA04          |

| Interrupts                |           | 0x1000          |

| Bus Matrix                |           | 0x2000          |

| DMA                       | 0xBF88    | 0x3000          |

| USB                       |           | 0x5050          |

| PORTA-PORTC               |           | 0x6000          |

| Configuration             | 0xBFC0    | 0x0BF0          |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2    | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | _                 |                      | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                    | —                | -                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                | R/W-0            | R/W-0            |

| 15:8         | —                 | _                 |                   | _                 | _                 | S                    | RIPL<2:0>(1)     |                  |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 |                   |                   | VEC               | <5:0> <sup>(1)</sup> |                  |                  |

#### REGISTER 7-2: INTSTAT: INTERRUPT STATUS REGISTER

### Legend:

| Legena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-11 Unimplemented: Read as '0'

- bit 10-8 SRIPL<2:0>: Requested Priority Level bits<sup>(1)</sup>

- 111-000 = The priority level of the latest interrupt presented to the CPU

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 VEC<5:0>: Interrupt Vector bits<sup>(1)</sup> 11111-00000 = The interrupt vector that is presented to the CPU

- Note 1: This value should only be used when the interrupt controller is configured for Single Vector mode.

| D:/          | Dit               | Dit               | D:                | Dit               | D'i               | D''               | Dir              | Dit              |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | IPTMF             | <31:24>           |                   |                  |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        |                   |                   |                   | IPTMF             | <23:16>           |                   |                  |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         |                   |                   |                   | IPTM              | R<15:8>           |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   |                   |                   | IPTM              | R<7:0>            |                   |                  |                  |

#### REGISTER 7-3: IPTMR: INTERRUPT PROXIMITY TIMER REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 31-0 **IPTMR<31:0>:** Interrupt Proximity Timer Reload bits Used by the Interrupt Proximity Timer as a reload value when the Interrupt Proximity timer is triggered by an interrupt event.

#### TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 | 0         |       |       |       |       |       |       |      |      | Bi    | ts       |       |          |        |        |           |          | (0         |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|-------|----------|-------|----------|--------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6     | 21/5  | 20/4     | 19/3   | 18/2   | 17/1      | 16/0     | All Resets |

| 5280                        | U1FRML <sup>(3)</sup>           | 31:16     | _     | —     | —     | —     | _     | _     | _    | _    | _     | —        | _     | —        | _      | _      | —         | —        | 0000       |

| 5200                        |                                 | 15:0      | _     | _     | _     | _     | —     | _     | —    | _    |       |          |       | FRML<    | 7:0>   |        |           |          | 0000       |

| 5290                        | U1FRMH <sup>(3)</sup>           | 31:16     | _     | —     | —     | —     |       | —     | —    | _    |       | —        |       | —        | —      | —      | _         | —        | 0000       |

| 52.50                       | OTTRAIT                         | 15:0      | _     | —     | —     | —     | —     | —     | —    |      |       | —        |       | _        | —      |        | FRMH<2:0> | >        | 0000       |

| 52A0                        | U1TOK                           | 31:16     | _     | —     | —     | —     |       | —     | —    | _    |       | —        | _     | _        | —      | —      | _         | —        | 0000       |

| 5270                        | UTTOR                           | 15:0      | _     | —     | —     | —     | —     | —     | —    |      |       | PID      | <3:0> |          |        | EP     | <3:0>     | -        | 0000       |

| 52B0                        | U1SOF                           | 31:16     | —     | —     |       |       | —     |       |      | _    | _     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 5260                        | 0130F                           | 15:0      | —     |       |       | _     | _     |       | _    |      |       |          |       | CNT<7    | /:0>   |        | -         |          | 0000       |

| 52C0                        | U1BDTP2                         | 31:16     | _     | —     |       | _     |       |       | _    | _    | _     | —        | _     | —        | —      | _      | _         | —        | 0000       |

| 5200                        | OIBDIF2                         | 15:0      | _     | —     |       | _     |       |       | _    | _    |       |          |       | BDTPTR   | H<7:0> |        |           |          | 0000       |

| 52D0                        | U1BDTP3                         | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    | _     | —        | _     | _        | —      | —      | —         | —        | 0000       |

| 5200                        | OIBDIF3                         | 15:0      | _     | —     |       | _     |       |       | _    | _    |       |          |       | BDTPTRI  | J<7:0> |        |           |          | 0000       |

| 52E0                        | U1CNFG1                         | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    | _     | —        | _     | _        | —      | —      | —         | —        | 0000       |

| 5210                        | UTCNI UT                        | 15:0      | _     | _     | —     | —     | —     | —     | —    | _    | UTEYE | UOEMON   |       | USBSIDL  | —      | —      | _         | UASUSPND | 0001       |

| 5300                        | U1EP0                           | 31:16     | _     | _     | —     | —     | —     | —     | —    | _    |       | —        |       | _        | —      | —      | _         | —        | 0000       |

| 5500                        | UIEI U                          | 15:0      | _     | _     | —     | —     | —     | —     | —    | _    | LSPD  | RETRYDIS |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5310                        | U1EP1                           | 31:16     | _     | _     | —     | —     | —     | —     | —    | _    |       | —        |       | _        | —      | —      | _         | —        | 0000       |

| 5510                        | UIEI I                          | 15:0      | _     | _     | —     | —     | —     | —     | —    | _    |       | —        |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5320                        | U1EP2                           | 31:16     | —     | —     | _     | _     | _     | _     | —    | _    | —     | —        | —     | _        | —      | _      | —         | —        | 0000       |

| 0020                        | OTET 2                          | 15:0      | _     | —     |       | —     | —     |       | —    | —    |       | —        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5330                        | U1EP3                           | 31:16     | _     | —     |       | —     | —     | —     | —    |      |       | —        | _     | _        | —      | —      |           | —        | 0000       |

| 0000                        | UTER 0                          | 15:0      | _     | —     |       | —     | —     |       | —    | —    |       | —        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5340                        | U1EP4                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      |           | —        | 0000       |

| 0010                        | 01EFT                           | 15:0      | —     | —     | —     | —     | —     |       | —    | _    | —     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5350                        | U1EP5                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 0000                        | 01EI 0                          | 15:0      | —     | —     | —     | —     | —     |       | —    | _    | —     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5360                        | U1EP6                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 0000                        | 0.2.0                           | 15:0      | _     | —     | _     | _     |       |       |      |      | _     | —        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5370                        | U1EP7                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      |           | —        | 0000       |

| 3070                        | 01217                           | 15:0      | —     | —     | —     | —     | —     | —     | —    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5380                        | U1EP8                           | 31:16     | _     | —     | —     | —     |       |       | —    | _    | _     | —        | _     | _        | —      | —      | —         | —        | 0000       |

| 5500                        | UILI U                          | 15:0      | —     | -     | _     | _     | —     | _     | _    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

### TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       | - /   |       |      |      | Bit  | s    |      |          |        |        |         |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 5390                        | U1EP9                           | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |      | _    | —    | —        | —      | _      | —       | —      | 0000       |

| 5590                        | UIEF9                           | 15:0      |       |       | —     | —     | _     | —     | _    | —    |      |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5240                        | U1EP10                          | 31:16     | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | —        | _      | _      | —       | _      | 0000       |

| 53A0                        | UIEPIU                          | 15:0      |       | _     | _     | -     | _     | _     | _    | -    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                        | U1EP11                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 53BU                        | UIEPII                          | 15:0      | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                        | U1EP12                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEFIZ                          | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53D0                        | U1EP13                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEF 13                         | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     |       | _     | _     |       | -     | _     | _    | _    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 53E0                        | U1EP14                          | 15:0      | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | —        | _      | _      | _       | _      | 0000       |

| 53F0                        | U1EP15                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | —    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

## 11.1 Parallel I/O (PIO) Ports

All port pins have 10 registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

### 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx, and TRISx registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V-tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the **"Pin Diagrams"** section for the available pins and their functionality.

## 11.1.2 CONFIGURING ANALOG AND DIGITAL PORT PINS

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs must have their corresponding ANSEL and TRIS bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

If the TRIS bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or Comparator module.

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

### 11.1.3 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP.

## 11.1.4 INPUT CHANGE NOTIFICATION

The input change notification function of the I/O ports allows the PIC32MX1XX/2XX 28/36/44-pin Family devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a change-of-state.

Five control registers are associated with the CN functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups act as a current source or sink source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

**Note:** Pull-ups and pull-downs on change notification pins should always be disabled when the port pin is configured as a digital output.

An additional control register (CNCONx) is shown in Register 11-3.

## 11.2 CLR, SET and INV Registers

Every I/O module register has a corresponding CLR (clear), SET (set) and INV (invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR, or INV register, the base register must be read.

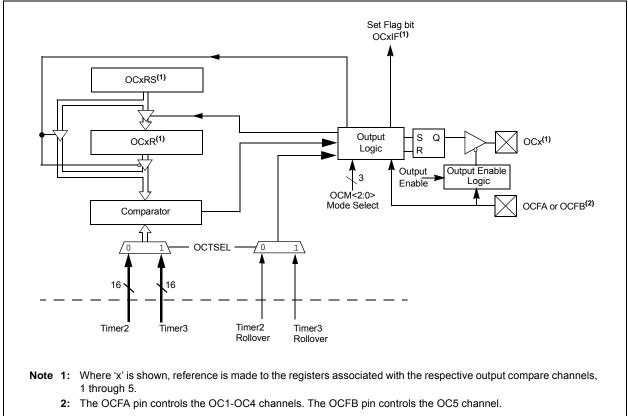

## 16.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 16. "Output Compare" (DS60001111), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Output Compare module is used to generate a single pulse or a train of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation. The following are some of the key features:

- · Multiple Output Compare Modules in a device

- Programmable interrupt generation on compare event

- Single and Dual Compare modes

- Single and continuous output pulse generation

- Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

## REGISTER 18-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | -                 | _                 | -                 | —                 |                   | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | _                 | —                 | _                | -                |

| 15.0         | R-0, HSC          | R-0, HSC          | U-0               | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |

| 15:8         | ACKSTAT           | TRSTAT            | -                 | -                 | _                 | BCL               | GCSTAT           | ADD10            |

| 7:0          | R/C-0, HS         | R/C-0, HS         | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |

| Legend:           | HS = Set in hardware | HSC = Hardware set/clea  | red               |

|-------------------|----------------------|--------------------------|-------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, r | ead as '0'        |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared     | C = Clearable bit |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 ACKSTAT: Acknowledge Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) 1 = Acknowledge was not received from slave 0 = Acknowledge was received from slave Hardware set or clear at end of slave Acknowledge. bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) 1 = Master transmit is in progress (8 bits + ACK) 0 = Master transmit is not in progress Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge. bit 13-11 Unimplemented: Read as '0' bit 10 BCL: Master Bus Collision Detect bit 1 = A bus collision has been detected during a master operation 0 = No collisionHardware set at detection of bus collision. This condition can only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module. bit 9 GCSTAT: General Call Status bit 1 = General call address was received 0 = General call address was not received Hardware set when address matches general call address. Hardware clear at Stop detection. bit 8 ADD10: 10-bit Address Status bit 1 = 10-bit address was matched 0 = 10-bit address was not matched Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.

#### bit 7 IWCOL: Write Collision Detect bit

| 1 = An attempt to write the I2CxTRN register failed because the I <sup>2</sup> C module is busy |  |

|-------------------------------------------------------------------------------------------------|--|

| 0 = No collision                                                                                |  |

Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).

#### bit 6 I2COV: Receive Overflow Flag bit

1 = A byte was received while the I2CxRCV register is still holding the previous byte 0 = No overflow

Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

#### bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was device address

Hardware clear at device address match. Hardware set by reception of slave byte.

NOTES:

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Bit<br>24/16/8/0 | Bit<br>25/17/9/1 | Bit<br>26/18/10/2 | Bit<br>27/19/11/3 | Bit<br>28/20/12/4 | Bit<br>29/21/13/5 | Bit<br>30/22/14/6 | Bit<br>31/23/15/7 | Bit<br>Range |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------|

| Image: How provided with the system         HR10<1:0>         HR01<3:0>           23:16         U-0         R/W-x         R/W-x         R/W-x         R/W-x         R/W-x           23:16         —         MIN10<2:0>         MIN01<3:0>         MIN01<3:0>           15:8         U-0         R/W-x         R/W-x         R/W-x         R/W-x         R/W-x           15:8         —         SEC10<2:0>         SEC01<3:0>         SEC01<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-x            | R/W-x            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | U-0               | U-0               | 04.04        |

| 23:16         —         MIN10<2:0>         MIN01<3:0>           15:8         U-0         R/W-x         R/W-x         R/W-x         R/W-x         R/W-x           15:8         —         SEC10<2:0>         SEC01<3:0>         SEC01<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  | <3:0>            | HR01              |                   | <1:0>             | HR10              | —                 | _                 | 31:24        |

| U-0         R/W-x         R | R/W-x            | R/W-x            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | U-0               | 00.40        |

| 15:8 — SEC10<2:0> SEC01<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  | <3:0>            | MIN01             |                   |                   | MIN10<2:0>        |                   | _                 | 23:16        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-x            | R/W-x            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | U-0               | 45.0         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  | <3:0>            | SEC01             |                   |                   | SEC10<2:0>        |                   | _                 | 15:8         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | U-0              | U-0              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | 7.0          |

| 7:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                |                  | _                 | _                 | _                 | _                 | _                 | _                 | 7:0          |

#### REGISTER 21-5: ALRMTIME: ALARM TIME VALUE REGISTER

# R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary Coded Decimal value of hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 **HR01<3:0>:** Binary Coded Decimal value of hours bits, 1s place digit; contains a value from 0 to 9 bit 23 **Unimplemented:** Read as '0'

bit 22-20 MIN10<2:0>: Binary Coded Decimal value of minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 **MIN01<3:0>:** Binary Coded Decimal value of minutes bits, 1s place digit; contains a value from 0 to 9 bit 15 **Unimplemented:** Read as '0'

bit 14-12 SEC10<2:0>: Binary Coded Decimal value of seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 **SEC01<3:0>:** Binary Coded Decimal value of seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### TABLE 26-2: PERIPHERAL MODULE DISABLE REGISTER MAP

| ess                         |                                 |           | Bits  |       |       |       |       |       |        |        |      |      |      |       | 6     |        |        |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|--------|--------|------|------|------|-------|-------|--------|--------|--------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8   | 23/7 | 22/6 | 21/5 | 20/4  | 19/3  | 18/2   | 17/1   | 16/0   | All Resets |

| F0.40                       | PMD1                            | 31:16     | —     | —     | _     | —     | _     | _     | _      | —      | —    | —    | —    | —     | _     | —      | —      | —      | 0000       |

| F240                        | FIVIDI                          | 15:0      | -     |       |       | CVRMD | Ι     |       |        | CTMUMD | —    | -    |      | -     |       |        | —      | AD1MD  | 0000       |

| 5250                        | PMD2                            | 31:16     | —     | —     |       | —     | _     | _     |        | —      | —    | —    | —    | —     | _     | —      | —      | —      | 0000       |

| F250                        | FIVIDZ                          | 15:0      | -     |       |       | —     | Ι     |       |        | —      | —    | -    |      | -     |       | CMP3MD | CMP2MD | CMP1MD | 0000       |

| F260                        | PMD3                            | 31:16     | _     | -     |       | _     | -     |       |        | _      | _    |      | _    | OC5MD | OC4MD | OC3MD  | OC2MD  | OC1MD  | 0000       |

| F200                        | FIVIDS                          | 15:0      | _     | -     |       | _     | -     |       |        | _      | _    |      | _    | IC5MD | IC4MD | IC3MD  | IC2MD  | IC1MD  | 0000       |

| F270                        | PMD4                            | 31:16     | _     | -     |       | _     | -     |       |        | _      | _    |      | _    | -     | _     | _      | —      | _      | 0000       |

| F270                        | F IVID4                         | 15:0      | _     | -     |       | _     | -     |       |        | _      | _    |      | _    | T5MD  | T4MD  | T3MD   | T2MD   | T1MD   | 0000       |

| F280                        | PMD5                            | 31:16     | _     | -     |       | _     | -     |       |        | USB1MD | _    |      | _    | -     | _     | _      | I2C1MD | I2C1MD | 0000       |

| F200                        | FIVIDS                          | 15:0      | _     | -     |       | _     | -     |       | SPI2MD | SPI1MD | _    |      | _    | -     | _     | _      | U2MD   | U1MD   | 0000       |

| F200                        | PMD6                            | 31:16     | _     | —     |       | —     | _     | _     |        | _      | —    | _    | —    | —     | _     | —      | —      | PMPMD  | 0000       |

| F290                        | I WD0                           | 15:0      | —     | _     | _     | —     | _     | _     | -      | —      | —    | _    | _    | _     | _     | _      | REFOMD | RTCCMD | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| DC CHA                                | RACTERIS               | TICS | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |            |                                                 |  |  |  |  |  |  |

|---------------------------------------|------------------------|------|------------------------------------------------------|------------|-------------------------------------------------|--|--|--|--|--|--|

| Param.<br>No.                         | Typical <sup>(2)</sup> | Max. | Units                                                | Conditions |                                                 |  |  |  |  |  |  |

| Power-Down Current (IPD) (Notes 1, 5) |                        |      |                                                      |            |                                                 |  |  |  |  |  |  |

| DC40k                                 | 44                     | 70   | μA                                                   | -40°C      |                                                 |  |  |  |  |  |  |

| DC40I                                 | 44                     | 70   | μA                                                   | +25°C      | Base Power-Down Current                         |  |  |  |  |  |  |

| DC40n                                 | 168                    | 259  | μA                                                   | +85°C      |                                                 |  |  |  |  |  |  |

| DC40m                                 | 335                    | 536  | μA                                                   | +105°C     |                                                 |  |  |  |  |  |  |

| Module Differential Current           |                        |      |                                                      |            |                                                 |  |  |  |  |  |  |

| DC41e                                 | 5                      | 20   | μA                                                   | 3.6V       | Watchdog Timer Current: AIWDT (Note 3)          |  |  |  |  |  |  |

| DC42e                                 | 23                     | 50   | μA                                                   | 3.6V       | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3) |  |  |  |  |  |  |

| DC43d                                 | 1000                   | 1100 | μA                                                   | 3.6V       | ADC: Aladc (Notes 3,4)                          |  |  |  |  |  |  |

## TABLE 30-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** The test conditions for IPD current measurements are as follows:

Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

OSC2/CLKO is configured as an I/O input pin

• USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

• CPU is in Sleep mode, and SRAM data memory Wait states = 1

• No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set

• WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

• All I/O pins are configured as inputs and pulled to Vss

• MCLR = VDD

• RTCC and JTAG are disabled

2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

- 5: IPD electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

| DC CHARACTERISTICS |                              |                     |                    | otherwi | se state | nditions: 2.3V to 3.6V<br>d)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                                                     |  |

|--------------------|------------------------------|---------------------|--------------------|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|

| Param.             | . Symbol Characteristic Min. |                     |                    |         | Max.     | Units                                                                                                                                       | Conditions                                          |  |

| DO10               | Vol                          | Output Low Voltage  | _                  | _       | 0.4      | V                                                                                                                                           | $\text{IOL} \leq 10 \text{ mA, VDD} = 3.3 \text{V}$ |  |

|                    |                              | Output High Voltage | 1.5(1)             | _       | _        | V                                                                                                                                           | IOH $\geq$ -14 mA, VDD = 3.3V                       |  |

| DO20               | Vон                          | I/O Pins            | 2.0 <sup>(1)</sup> | _       | _        |                                                                                                                                             | IOH $\geq$ -12 mA, VDD = 3.3V                       |  |

| D020               | VOH                          |                     | 2.4                | _       | _        | v                                                                                                                                           | IOH $\geq$ -10 mA, VDD = 3.3V                       |  |

|                    |                              |                     | 3.0(1)             | —       | —        |                                                                                                                                             | $IOH \ge -7 \text{ mA}, \text{ VDD} = 3.3 \text{V}$ |  |

### TABLE 30-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

Note 1: Parameters are characterized, but not tested.

#### TABLE 30-11: ELECTRICAL CHARACTERISTICS: BOR

|               |        |                                                           |                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |            |  |  |  |

|---------------|--------|-----------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|--|

| Param.<br>No. | Symbol | Characteristics                                           | Min. <sup>(1)</sup> | Typical                                                                                                                                                                                                                                                                             | Max. | Units | Conditions |  |  |  |

| BO10          | VBOR   | BOR Event on VDD transition<br>high-to-low <sup>(2)</sup> | 2.0                 | —                                                                                                                                                                                                                                                                                   | 2.3  | V     | _          |  |  |  |

**Note 1:** Parameters are for design guidance only and are not tested in manufacturing.

2: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN.

| DC CHA        |        | STICS                                                     | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 4): 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |         |      |       |                                                                                         |  |  |

|---------------|--------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|-----------------------------------------------------------------------------------------|--|--|

| Param.<br>No. | Symbol | Characteristics                                           | Min.                                                                                                                                                                                                                                                                                               | Typical | Max. | Units | Comments                                                                                |  |  |

| D300          | VIOFF  | Input Offset Voltage                                      | -                                                                                                                                                                                                                                                                                                  | ±7.5    | ±25  | mV    | AVDD = VDD,<br>AVSS = VSS                                                               |  |  |

| D301          | VICM   | Input Common Mode Voltage                                 | 0                                                                                                                                                                                                                                                                                                  | -       | Vdd  | V     | AVDD = VDD,<br>AVss = Vss<br>(Note 2)                                                   |  |  |

| D302          | CMRR   | Common Mode Rejection Ratio                               | 55                                                                                                                                                                                                                                                                                                 | —       | _    | dB    | Max VICM = (VDD - 1)V<br>(Note 2)                                                       |  |  |

| D303A         | TRESP  | Large Signal Response Time                                | _                                                                                                                                                                                                                                                                                                  | 150     | 400  | ns    | AVDD = VDD, AVSS = VSS<br>(Note 1,2)                                                    |  |  |

| D303B         | TSRESP | Small Signal Response Time                                | -                                                                                                                                                                                                                                                                                                  | 1       | _    | μS    | This is defined as an input<br>step of 50 mV with 15 mV<br>of overdrive <b>(Note 2)</b> |  |  |

| D304          | ON2ov  | Comparator Enabled to Output<br>Valid                     | _                                                                                                                                                                                                                                                                                                  | _       | 10   | μs    | Comparator module is<br>configured before setting<br>the comparator ON bit<br>(Note 2)  |  |  |

| D305          | IVREF  | Internal Voltage Reference                                | 1.14                                                                                                                                                                                                                                                                                               | 1.2     | 1.26 | V     | —                                                                                       |  |  |

| D312          | TSET   | Internal Comparator Voltage<br>DRC Reference Setting time | —                                                                                                                                                                                                                                                                                                  | —       | 10   | μs    | (Note 3)                                                                                |  |  |

#### TABLE 30-13: COMPARATOR SPECIFICATIONS

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

**2:** These parameters are characterized but not tested.

**3:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

**4:** The Comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

| АС СНА        | RACTERI       | ISTICS                                                                                                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |                        |             |            |                                              |  |  |

|---------------|---------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------|------------|----------------------------------------------|--|--|

| Param.<br>No. | Symbol        | Characteristics                                                                                                  | Min.                                                                                                                                                                                                                                                                              | Typical <sup>(1)</sup> | Max.        | Units      | Conditions                                   |  |  |

| OS10          | Fosc          | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes)                               | DC<br>4                                                                                                                                                                                                                                                                           |                        | 40<br>40    | MHz<br>MHz | EC (Note 4)<br>ECPLL (Note 3)                |  |  |

| OS11          |               | Oscillator Crystal Frequency                                                                                     | 3                                                                                                                                                                                                                                                                                 | —                      | 10          | MHz        | XT (Note 4)                                  |  |  |

| OS12          |               |                                                                                                                  | 4                                                                                                                                                                                                                                                                                 | —                      | 10          | MHz        | XTPLL<br>(Notes 3,4)                         |  |  |

| OS13          |               |                                                                                                                  | 10                                                                                                                                                                                                                                                                                | —                      | 25          | MHz        | HS (Note 5)                                  |  |  |

| OS14          |               |                                                                                                                  | 10                                                                                                                                                                                                                                                                                | -                      | 25          | MHz        | HSPLL<br>(Notes 3,4)                         |  |  |

| OS15          |               |                                                                                                                  | 32                                                                                                                                                                                                                                                                                | 32.768                 | 100         | kHz        | Sosc (Note 4)                                |  |  |

| OS20          | Tosc          | Tosc = 1/Fosc = Tcy (Note 2)                                                                                     | —                                                                                                                                                                                                                                                                                 | —                      | _           | —          | See parameter<br>OS10 for Fosc<br>value      |  |  |

| OS30          | TosL,<br>TosH | External Clock In (OSC1)<br>High or Low Time                                                                     | 0.45 x Tosc                                                                                                                                                                                                                                                                       | -                      | —           | ns         | EC (Note 4)                                  |  |  |

| OS31          | TosR,<br>TosF | External Clock In (OSC1)<br>Rise or Fall Time                                                                    | —                                                                                                                                                                                                                                                                                 | —                      | 0.05 x Tosc | ns         | EC (Note 4)                                  |  |  |

| OS40          | Тоѕт          | Oscillator Start-up Timer Period<br>(Only applies to HS, HSPLL,<br>XT, XTPLL and Sosc Clock<br>Oscillator modes) | _                                                                                                                                                                                                                                                                                 | 1024                   | _           | Tosc       | (Note 4)                                     |  |  |

| OS41          | TFSCM         | Primary Clock Fail Safe<br>Time-out Period                                                                       | —                                                                                                                                                                                                                                                                                 | 2                      | _           | ms         | (Note 4)                                     |  |  |

| OS42          | Gм            | External Oscillator<br>Transconductance (Primary<br>Oscillator only)                                             | —                                                                                                                                                                                                                                                                                 | 12                     | —           | mA/V       | VDD = 3.3V,<br>TA = +25°C<br><b>(Note 4)</b> |  |  |

### TABLE 30-17: EXTERNAL CLOCK TIMING REQUIREMENTS

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are characterized but are not tested.

2: Instruction cycle period (Tcr) equals the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin.

3: PLL input requirements: 4 MHz  $\leq$  FPLLIN  $\leq$  5 MHz (use PLL prescaler to reduce FOSC). This parameter is characterized, but tested at 10 MHz only at manufacturing.

4: This parameter is characterized, but not tested in manufacturing.

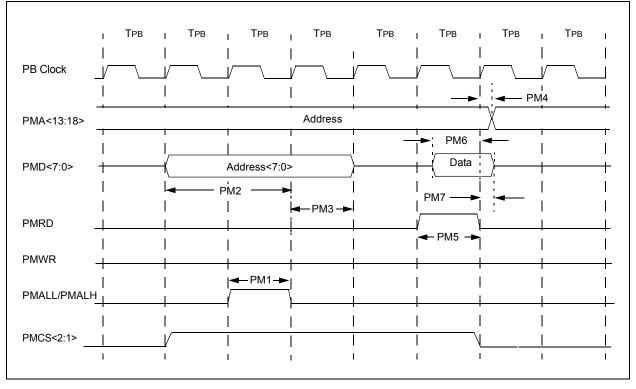

#### TABLE 30-37: PARALLEL SLAVE PORT REQUIREMENTS

| AC CH         | ARACTE       | RISTICS                                                                          | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |      |      |       |            |  |  |

|---------------|--------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|--|--|

| Para<br>m.No. | Symbol       | Characteristics <sup>(1)</sup>                                                   | Min.                                                                                                                                                                                                                                                                            | Тур. | Max. | Units | Conditions |  |  |

| PS1           | TdtV2wr<br>H | Data In Valid before $\overline{WR}$ or $\overline{CS}$<br>Inactive (setup time) | 20                                                                                                                                                                                                                                                                              |      |      | ns    | _          |  |  |

| PS2           | TwrH2dt<br>I | WR or CS Inactive to Data-In Invalid (hold time)                                 | 40                                                                                                                                                                                                                                                                              | —    | _    | ns    | _          |  |  |