Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 10x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 28-SPDIP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx150f128b-i-sp |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-1: **PINOUT I/O DESCRIPTIONS**

|          | Pin Number <sup>(1)</sup> |                                             |                                        |                                        |                         |             |                                                                                                                                                                                                |

|----------|---------------------------|---------------------------------------------|----------------------------------------|----------------------------------------|-------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | 28-pin<br>QFN             | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC           | 36-pin<br>VTLA                         | 44-pin<br>QFN/<br>TQFP/<br>VTLA        | Pin Buffer<br>Type Type | Description |                                                                                                                                                                                                |

| AN0      | 27                        | 2                                           | 33                                     | 19                                     |                         | Analog      | Analog input channels.                                                                                                                                                                         |

| AN1      | 28                        | 3                                           | 34                                     | 20                                     | I                       | Analog      |                                                                                                                                                                                                |

| AN2      | 1                         | 4                                           | 35                                     | 21                                     |                         | Analog      |                                                                                                                                                                                                |

| AN3      | 2                         | 5                                           | 36                                     | 22                                     |                         | Analog      |                                                                                                                                                                                                |

| AN4      | 3                         | 6                                           | 1                                      | 23                                     | I                       | Analog      |                                                                                                                                                                                                |

| AN5      | 4                         | 7                                           | 2                                      | 24                                     | I                       | Analog      |                                                                                                                                                                                                |

| AN6      | _                         | _                                           | 3                                      | 25                                     | I                       | Analog      |                                                                                                                                                                                                |

| AN7      | _                         | _                                           | 4                                      | 26                                     | I                       | Analog      |                                                                                                                                                                                                |

| AN8      | _                         | _                                           | _                                      | 27                                     | I                       | Analog      |                                                                                                                                                                                                |

| AN9      | 23                        | 26                                          | 29                                     | 15                                     | I                       | Analog      |                                                                                                                                                                                                |

| AN10     | 22                        | 25                                          | 28                                     | 14                                     | I                       | Analog      |                                                                                                                                                                                                |

| AN11     | 21                        | 24                                          | 27                                     | 11                                     | I                       | Analog      |                                                                                                                                                                                                |

| AN12     | 20 <sup>(2)</sup>         | 23 <sup>(2)</sup>                           | 26 <sup>(2)</sup><br>11 <sup>(3)</sup> | 10 <sup>(2)</sup><br>36 <sup>(3)</sup> | 1                       | Analog      | *                                                                                                                                                                                              |

| CLKI     | 6                         | 9                                           | 7                                      | 30                                     | I                       | ST/CMOS     | External clock source input. Always associated with OSC1 pin function.                                                                                                                         |

| CLKO     | 7                         | 10                                          | 8                                      | 31                                     | 0                       | _           | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes. Always associated<br>with OSC2 pin function. |

| OSC1     | 6                         | 9                                           | 7                                      | 30                                     | I                       | ST/CMOS     | -                                                                                                                                                                                              |

| OSC2     | 7                         | 10                                          | 8                                      | 31                                     | 0                       | -           | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes.                                              |

| SOSCI    | 8                         | 11                                          | 9                                      | 33                                     | I                       | ST/CMOS     | 32.768 kHz low-power oscillator crystal<br>input; CMOS otherwise.                                                                                                                              |

| SOSCO    | 9                         | 12                                          | 10                                     | 34                                     | 0                       | —           | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                |

| REFCLKI  | PPS                       | PPS                                         | PPS                                    | PPS                                    |                         | ST          | Reference Input Clock                                                                                                                                                                          |

| REFCLKO  | PPS                       | PPS                                         | PPS                                    | PPS                                    | 0                       | —           | Reference Output Clock                                                                                                                                                                         |

| IC1      | PPS                       | PPS                                         | PPS                                    | PPS                                    |                         | ST          | Capture Inputs 1-5                                                                                                                                                                             |

| IC2      | PPS                       | PPS                                         | PPS                                    | PPS                                    | 1                       | ST          | 1                                                                                                                                                                                              |

| IC3      | PPS                       | PPS                                         | PPS                                    | PPS                                    | 1                       | ST          | 1                                                                                                                                                                                              |

| IC4      | PPS                       | PPS                                         | PPS                                    | PPS                                    |                         | ST          | 1                                                                                                                                                                                              |

| IC5      | PPS                       | PPS                                         | PPS                                    | PPS                                    |                         | ST          | 1                                                                                                                                                                                              |

|          | ST = Schm                 | MOS compa<br>itt Trigger in<br>input buffer |                                        |                                        | •                       | O = Outp    | Analog inputP = PowerutI = Inputeripheral Pin Select— = N/A                                                                                                                                    |

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability. 2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

|          |                        | Pin Number <sup>(1)</sup>         |                   |                                 |             |                |                                           |

|----------|------------------------|-----------------------------------|-------------------|---------------------------------|-------------|----------------|-------------------------------------------|

| Pin Name | 28-pin<br>QFN          | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA    | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                               |

| OC1      | PPS                    | PPS                               | PPS               | PPS                             | 0           |                | Output Compare Output 1                   |

| OC2      | PPS                    | PPS                               | PPS               | PPS                             | 0           | _              | Output Compare Output 2                   |

| OC3      | PPS                    | PPS                               | PPS               | PPS                             | 0           | —              | Output Compare Output 3                   |

| OC4      | PPS                    | PPS                               | PPS               | PPS                             | 0           | _              | Output Compare Output 4                   |

| OC5      | PPS                    | PPS                               | PPS               | PPS                             | 0           | _              | Output Compare Output 5                   |

| OCFA     | PPS                    | PPS                               | PPS               | PPS                             | I           | ST             | Output Compare Fault A Input              |

| OCFB     | PPS                    | PPS                               | PPS               | PPS                             | I           | ST             | Output Compare Fault B Input              |

| INT0     | 13                     | 16                                | 17                | 43                              | I           | ST             | External Interrupt 0                      |

| INT1     | PPS                    | PPS                               | PPS               | PPS                             | 1           | ST             | External Interrupt 1                      |

| INT2     | PPS                    | PPS                               | PPS               | PPS                             | 1           | ST             | External Interrupt 2                      |

| INT3     | PPS                    | PPS                               | PPS               | PPS                             | I           | ST             | External Interrupt 3                      |

| INT4     | PPS                    | PPS                               | PPS               | PPS                             | I           | ST             | External Interrupt 4                      |

| RA0      | 27                     | 2                                 | 33                | 19                              | I/O         | ST             | PORTA is a bidirectional I/O port         |

| RA1      | 28                     | 3                                 | 34                | 20                              | I/O         | ST             | -                                         |

| RA2      | 6                      | 9                                 | 7                 | 30                              | I/O         | ST             | -                                         |

| RA3      | 7                      | 10                                | 8                 | 31                              | I/O         | ST             | -                                         |

| RA4      | 9                      | 12                                | 10                | 34                              | I/O         | ST             | -                                         |

| RA7      | _                      |                                   |                   | 13                              | I/O         | ST             | -                                         |

| RA8      |                        |                                   |                   | 32                              | I/O         | ST             | -                                         |

| RA9      | <u> </u>               |                                   | _                 | 35                              | I/O         | ST             | -                                         |

| RA10     |                        |                                   |                   | 12                              | I/O         | ST             | -                                         |

| RB0      | 1                      | 4                                 | 35                | 21                              | I/O         | ST             | PORTB is a bidirectional I/O port         |

| RB1      | 2                      | 5                                 | 36                | 22                              | I/O         | ST             |                                           |

| RB2      | 3                      | 6                                 | 1                 | 23                              | I/O         | ST             | -                                         |

| RB3      | 4                      | 7                                 | 2                 | 24                              | I/O         | ST             | -                                         |

| RB4      | 8                      | 11                                | 9                 | 33                              | I/O         | ST             | -                                         |

| RB5      | 11                     | 14                                | 15                | 41                              | I/O         | ST             | -                                         |

| RB6      | 12 <sup>(2)</sup>      | 15 <sup>(2)</sup>                 | 16 <sup>(2)</sup> | 42(2)                           | I/O         | ST             | 1                                         |

| RB7      | 13                     | 16                                | 17                | 43                              | I/O         | ST             | 4                                         |

| RB8      | 18                     | 10                                | 18                | 44                              | I/O         | ST             | 4                                         |

| RB9      | 15                     | 18                                | 19                | 1                               | I/O         | ST             | 4                                         |

| RB10     | 18                     | 21                                | 24                | 8                               | I/O         | ST             | 4                                         |

| RB11     | 10                     | 22                                | 25                | 9                               | I/O         | ST             | 4                                         |

| RB12     | 20(2)                  | 23(2)                             | 26 <sup>(2)</sup> | 10 <sup>(2)</sup>               | I/O         | ST             | 4                                         |

| RB13     | 21                     | 24                                | 27                | 11                              | I/O         | ST             | 4                                         |

| RB14     | 21                     | 25                                | 28                | 14                              | I/O         | ST             | 4                                         |

| RB15     | 23                     | 26                                | 29                | 15                              | 1/O         | ST             | 4                                         |

|          | CMOS = C               | -                                 |                   |                                 |             |                | Analog input P = Power                    |

| Leyena.  | ST = Schm<br>TTL = TTL | itt Trigger in                    |                   |                                 |             | O = Outp       |                                           |

| Note 1:  |                        | -                                 | led for refe      | rence onlv.                     | See the     |                | grams" section for device pin availabilit |

####

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

|              |                        | Pin Number <sup>(1)</sup>                   |                |                                 |             |                     |                                                            |

|--------------|------------------------|---------------------------------------------|----------------|---------------------------------|-------------|---------------------|------------------------------------------------------------|

| Pin Name     | 28-pin<br>QFN          | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC           | 36-pin<br>VTLA | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type      | Description                                                |

| RC0          | —                      | —                                           | 3              | 25                              | I/O         | ST                  | PORTC is a bidirectional I/O port                          |

| RC1          | —                      | —                                           | 4              | 26                              | I/O         | ST                  |                                                            |

| RC2          | —                      | —                                           | _              | 27                              | I/O         | ST                  |                                                            |

| RC3          | —                      | —                                           | 11             | 36                              | I/O         | ST                  | _                                                          |

| RC4          | —                      | —                                           | _              | 37                              | I/O         | ST                  | _                                                          |

| RC5          | —                      |                                             |                | 38                              | I/O         | ST                  | _                                                          |

| RC6          |                        | —                                           | _              | 2                               | I/O         | ST                  | _                                                          |

| RC7          | —                      |                                             | —              | 3                               | I/O         | ST                  | _                                                          |

| RC8          | —                      | —                                           | —              | 4                               | I/O         | ST                  | _                                                          |

| RC9          |                        | - 40                                        | 20             | 5                               | I/O         | ST                  | Time and an element all all in must                        |

| T1CK<br>T2CK | 9<br>PPS               | 12                                          | 10             | 34                              |             | ST                  | Timer1 external clock input                                |

| T3CK         | PPS<br>PPS             | PPS<br>PPS                                  | PPS<br>PPS     | PPS<br>PPS                      |             | ST<br>ST            | Timer2 external clock input<br>Timer3 external clock input |

| T4CK         | PPS                    | PPS                                         | PPS            | PPS                             | 1           | ST                  | Timer4 external clock input                                |

| T5CK         | PPS                    | PPS                                         | PPS            | PPS                             |             | ST                  | Timer5 external clock input                                |

|              | PPS                    | PPS                                         | PPS            | PPS                             |             | ST                  | UART1 clear to send                                        |

| U1RTS        | PPS                    | PPS                                         | PPS            | PPS                             |             | 51                  |                                                            |

| U1RX         | PPS<br>PPS             | PPS<br>PPS                                  | PPS<br>PPS     | PPS<br>PPS                      | 0           | ST                  | UART1 ready to send<br>UART1 receive                       |

| U1TX         | PPS                    | PPS                                         | PPS            | PPS                             | -           |                     |                                                            |

|              |                        |                                             |                |                                 | 0           |                     | UART1 transmit                                             |

| U2CTS        | PPS                    | PPS                                         | PPS            | PPS                             | I           | ST                  | UART2 clear to send                                        |

| U2RTS        | PPS                    | PPS                                         | PPS            | PPS                             | 0           |                     | UART2 ready to send                                        |

| U2RX         | PPS                    | PPS                                         | PPS            | PPS                             | I           | ST                  | UART2 receive                                              |

| U2TX         | PPS                    | PPS                                         | PPS            | PPS                             | 0           |                     | UART2 transmit                                             |

| SCK1         | 22                     | 25                                          | 28             | 14                              | I/O         | ST                  | Synchronous serial clock input/output for SPI1             |

| SDI1         | PPS                    | PPS                                         | PPS            | PPS                             | I           | ST                  | SPI1 data in                                               |

| SDO1         | PPS                    | PPS                                         | PPS            | PPS                             | 0           | _                   | SPI1 data out                                              |

| SS1          | PPS                    | PPS                                         | PPS            | PPS                             | I/O         | ST                  | SPI1 slave synchronization or frame pulse I/O              |

| SCK2         | 23                     | 26                                          | 29             | 15                              | I/O         | ST                  | Synchronous serial clock input/output for SPI2             |

| SDI2         | PPS                    | PPS                                         | PPS            | PPS                             |             | ST                  | SPI2 data in                                               |

| SDO2         | PPS                    | PPS                                         | PPS            | PPS                             | 0           | _                   | SPI2 data out                                              |

| SS2          | PPS                    | PPS                                         | PPS            | PPS                             | I/O         | ST                  | SPI2 slave synchronization or frame pulse I/O              |

| SCL1         | 14                     | 17                                          | 18             | 44                              | I/O         | ST                  | Synchronous serial clock input/output for<br>I2C1          |

|              | ST = Schm<br>TTL = TTL | MOS compa<br>itt Trigger in<br>input buffer | put with CN    | MOS levels                      |             | O = Outp<br>PPS = P | Analog input P = Power                                     |

####

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

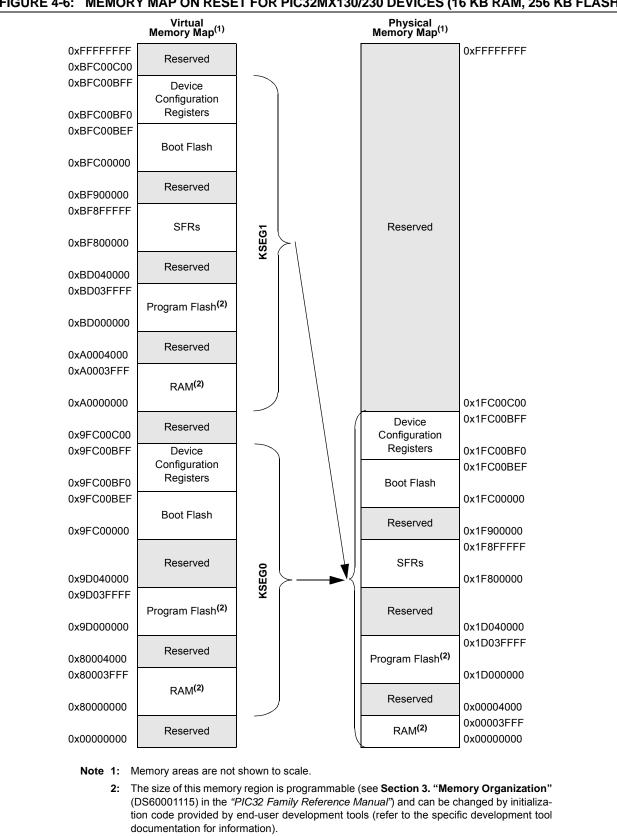

#### FIGURE 4-6: MEMORY MAP ON RESET FOR PIC32MX130/230 DEVICES (16 KB RAM, 256 KB FLASH)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

|              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | _                 | _                 | —                 | _                 | —                 | _                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | _                 | —                 | _                 | —                 | —                | —                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |

| 15:8         | BMXDUDBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   | BMXDUDBA<7:0>     |                   |                   |                   |                   |                  |                  |  |  |

#### REGISTER 4-3: BMXDUDBA: DATA RAM USER DATA BASE ADDRESS REGISTER

### Legend:

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-10 BMXDUDBA<15:10>: DRM User Data Base Address bits

When non-zero, the value selects the relative base address for User mode data space in RAM, the value must be greater than BMXDKPBA.

#### bit 9-0 BMXDUDBA<9:0>: Read-Only bits This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

|              | _                 | _                 |                   | _                 | _                 | —                 | —                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                 | _                 |                   | _                 | _                 | _                 | —                | —                |  |  |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | —                 | _                 | —                 | MVEC              | _                 |                   | TPC<2:0>         |                  |  |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | _                 | _                 | _                 | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |  |  |

#### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

#### Legend:

| Logona.           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-13 Unimplemented: Read as '0'

- bit 12 MVEC: Multi Vector Configuration bit

- 1 = Interrupt controller configured for Multi-vectored mode

- 0 = Interrupt controller configured for Single-vectored mode

- bit 11 Unimplemented: Read as '0'

- bit 10-8 **TPC<2:0>:** Interrupt Proximity Timer Control bits

- 111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer

- 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer

- 101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer

- 100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer

- 011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer

- 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

- 001 = Interrupts of group priority 1 start the Interrupt Proximity timer

- 000 = Disables Interrupt Proximity timer

#### bit 7-5 Unimplemented: Read as '0'

- bit 4 INT4EP: External Interrupt 4 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

- 1 =Rising edge

- 0 = Falling edge

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

#### REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- bit 3-0 ROSEL<3:0>: Reference Clock Source Select bits<sup>(1)</sup>

- 1111 = Reserved; do not use

- 1001 = Reserved; do not use 1000 = REFCLKI 0111 = System PLL output 0110 = USB PLL output 0101 = Sosc 0100 = LPRC 0011 = FRC 0010 = POSC 0001 = PBCLK 0000 = SYSCLK

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- 2: This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

#### REGISTER 10-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER (CONTINUED)

- bit 1 CRC5EF: CRC5 Host Error Flag bit<sup>(4)</sup>

- 1 = Token packet rejected due to CRC5 error

- 0 = Token packet accepted

- EOFEF: EOF Error Flag bit<sup>(3,5)</sup>

- 1 = An EOF error condition was detected

- 0 = No EOF error condition was detected

- bit 0 PIDEF: PID Check Failure Flag bit

- 1 = PID check failed

- 0 = PID check passed

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- **2:** This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

#### REGISTER 10-10: U1STAT: USB STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        |                   | —                 |                   |                   |                   | _                 | _                | —                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | _                 | —                 |                   |                   |                   | _                 | _                | —                |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.0         | _                 | —                 |                   |                   |                   | _                 | _                | —                |  |

| 7.0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | U-0              | U-0              |  |

| 7:0          |                   | ENDP              | T<3:0>            |                   | DIR               | PPBI              |                  |                  |  |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7-4 **ENDPT<3:0>:** Encoded Number of Last Endpoint Activity bits (Represents the number of the Buffer Descriptor Table, updated by the last USB transfer.)

- 1111 = Endpoint 15 1110 = Endpoint 14 . . 0001 = Endpoint 1 0000 = Endpoint 0

- bit 3 **DIR:** Last Buffer Descriptor Direction Indicator bit

- 1 = Last transaction was a transmit (TX) transfer

- 0 = Last transaction was a receive (RX) transfer

- bit 2 **PPBI:** Ping-Pong Buffer Descriptor Pointer Indicator bit

- 1 = The last transaction was to the ODD Buffer Descriptor bank

- 0 = The last transaction was to the EVEN Buffer Descriptor bank

- bit 1-0 Unimplemented: Read as '0'

**Note:** The U1STAT register is a window into a 4-byte FIFO maintained by the USB module. U1STAT value is only valid when the TRNIF (U1IR<3>) bit is active. Clearing the TRNIF bit advances the FIFO. Data in register is invalid when the TRNIF bit = 0.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |  |  |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|--|--|

| 31:24        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |  |  |

| 31.24        | —                 | —                 | —                        | _                 | —                     | —                     |                  | _                    |  |  |

| 22:16        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |  |  |

| 23:16        | —                 | —                 | —                        | -                 | —                     | _                     | _                | _                    |  |  |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |  |  |

| 15.0         | —                 | —                 | —                        | -                 | —                     | _                     | _                | _                    |  |  |

|              | R-x               | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |  |  |

| 7:0          | JSTATE            | JSTATE SE0 -      | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST           | USBEN <sup>(4)</sup> |  |  |

|              |                   |                   | TOKBUSY <sup>(1,5)</sup> | USDROI            |                       |                       |                  | SOFEN <sup>(5)</sup> |  |  |

#### REGISTER 10-11: U1CON: USB CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **JSTATE:** Live Differential Receiver JSTATE flag bit 1 = JSTATE was detected on the USB

- 0 = No JSTATE was detected on the

- bit 6 **SE0:** Live Single-Ended Zero flag bit 1 = Single-Ended Zero was detected on the USB

- 0 = No Single-Ended Zero was detected

- bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

- 1 = Token and packet processing is disabled (set upon SETUP token received)

- 0 = Token and packet processing is enabled

- TOKBUSY: Token Busy Indicator bit<sup>(1,5)</sup>

- 1 = Token is being executed by the USB module

- 0 = No token is being executed

#### bit 4 USBRST: Module Reset bit<sup>(5)</sup>

- 1 = USB reset generated

- 0 = USB reset terminated

- bit 3 HOSTEN: Host Mode Enable bit<sup>(2)</sup>

- 1 = USB host capability is enabled

- 0 = USB host capability is disabled

- bit 2 RESUME: RESUME Signaling Enable bit<sup>(3)</sup>

- 1 = RESUME signaling is activated

- 0 = RESUME signaling is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

| TABL                        | E 11-7:              | PE        | RIPHER | RAL PIN | SELEC |       | PUT RE | GISTER | MAP ( | CONTIN | IUED) |                  |      |      |      |      |        |      |            |

|-----------------------------|----------------------|-----------|--------|---------|-------|-------|--------|--------|-------|--------|-------|------------------|------|------|------|------|--------|------|------------|

| SS                          |                      |           |        |         |       |       |        |        |       | В      | its   |                  |      |      |      |      |        |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15  | 30/14   | 29/13 | 28/12 | 27/11  | 26/10  | 25/9  | 24/8   | 23/7  | 22/6             | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| FB4C                        | RPB8R                | 31:16     | _      | —       | -     | _     | —      | -      | _     | _      | -     | —                | _    | —    | _    | _    | _      | —    | 0000       |

| 1040                        | IN DOIX              | 15:0      | _      | —       | —     | _     | —      |        | _     | —      |       |                  | —    | —    |      | RPB8 | <3:0>  |      | 0000       |

| FB50                        | RPB9R                | 31:16     | —      | —       | —     |       | —      | —      | _     | —      | —     | —                | —    | —    | _    | —    | —      | —    | 0000       |

| 1 830                       | KF D9K               | 15:0      | —      | —       | —     | -     | —      | —      | -     |        | _     | —                | _    | —    |      | RPB9 | <3:0>  |      | 0000       |

| FB54                        | RPB10R               | 31:16     | —      | —       | —     | -     | —      | —      | -     |        | _     | —                | —    | —    | -    | _    | —      | —    | 0000       |

| FB34                        | REDIUR               | 15:0      | —      | —       | —     |       | —      | _      |       |        | —     | —                | —    | —    |      | RPB1 | 0<3:0> |      | 0000       |

| FB58                        | RPB11R               | 31:16     | —      | —       | —     |       | —      | _      |       |        | —     | —                | —    | —    |      |      | _      | —    | 0000       |

| FB30                        | RPBIIR               | 15:0      | _      | _       | —     | _     | —      | —      | _     | _      | _     | _                | _    | —    |      | RPB1 | 1<3:0> |      | 0000       |

| FB60                        | RPB13R               | 31:16     | _      | _       | —     | _     | —      | —      | _     | _      | _     | _                | _    | —    | _    | _    | _      | _    | 0000       |

| FB00                        | RPBISR               | 15:0      | _      | _       | —     | _     | —      | —      | _     | _      | _     | _                | _    | —    |      | RPB1 | 3<3:0> |      | 0000       |

| FB64                        | RPB14R               | 31:16     | _      | _       | —     | _     | —      | —      | _     | _      | _     | _                | _    | —    | _    | _    | _      | _    | 0000       |

| FB04                        | RPD14R               | 15:0      | _      | _       | —     | _     | —      | —      | _     | _      | _     | - — — RPB14<3:0> |      |      |      |      | 0000   |      |            |

| FB68                        | RPB15R               | 31:16     | —      | _       | —     | —     | —      | —      | —     | —      | —     | _                | _    | —    | —    | —    | —      | _    | 0000       |

| FB00                        | RPBIOR               | 15:0      | _      | _       | —     | _     | —      | —      | _     | _      | _     | _                | _    | —    |      | RPB1 | 5<3:0> |      | 0000       |

| FB6C                        | RPC0R <sup>(3)</sup> | 31:16     | _      | _       | —     | _     | —      | —      | _     | _      | _     | _                | _    | —    | _    | _    | _      | _    | 0000       |

| FBOC                        | RECOR                | 15:0      | —      | —       | -     |       | —      | —      | -     |        | —     | —                | -    | —    |      | RPCC | <3:0>  |      | 0000       |

| FB70                        | RPC1R <sup>(3)</sup> | 31:16     | _      | _       | —     | _     | —      | —      | _     | _      | _     | _                | _    | —    | _    | _    | _      | _    | 0000       |

| FB/U                        | RPUIK                | 15:0      | _      | _       | —     | _     | —      | —      | _     | _      | _     | _                | _    | —    |      | RPC1 | <3:0>  |      | 0000       |

| FB74                        | RPC2R <sup>(1)</sup> | 31:16     | _      | _       | —     | _     | —      | —      | _     | _      | _     | _                | _    | —    | _    | _    | _      | _    | 0000       |

| FB/4                        | RPG2R <sup>V</sup>   | 15:0      | _      | _       | —     | _     | —      | —      | _     | _      | _     | _                | _    | —    |      | RPC2 | <3:0>  |      | 0000       |

| FB78                        | RPC3R <sup>(3)</sup> | 31:16     | _      | _       | —     | _     | —      | —      | _     | _      | _     | _                | _    | —    | _    | _    | _      | _    | 0000       |

| FB/0                        | RPCSR                | 15:0      | _      | _       | —     | _     | —      | —      | _     | _      | _     | _                | _    | —    |      | RPC3 | <3:0>  |      | 0000       |

| FB7C                        | RPC4R <sup>(1)</sup> | 31:16     | _      | _       | —     | _     | —      | —      | _     | _      | _     | _                | _    | —    | _    | _    | _      | _    | 0000       |

| FB/C                        | RPC4R <sup>1</sup>   | 15:0      | _      | _       | —     | _     | —      | —      | _     | _      | _     | _                | _    | —    |      | RPC4 | <3:0>  |      | 0000       |

|                             | RPC5R <sup>(1)</sup> | 31:16     | _      | _       | —     | _     | —      | —      | _     | _      | _     | _                | _    | —    | _    | _    | _      | _    | 0000       |

| FB80                        | KPU5K <sup>(1)</sup> | 15:0      | —      | —       | —     | _     | —      | _      | _     | _      | —     |                  | —    | —    |      | RPC5 | i<3:0> |      | 0000       |

|                             | RPC6R <sup>(1)</sup> | 31:16     | —      | —       | —     | _     | —      | _      | _     | _      | _     |                  | —    | —    | _    | —    |        | —    | 0000       |

| FB84                        | RPUBRIT              | 15:0      | —      | —       | —     | _     | —      | _      | —     | _      | —     |                  | —    | —    |      | RPC  | i<3:0> |      | 0000       |

| FB88                        | RPC7R <sup>(1)</sup> | 31:16     | —      | —       | —     | _     | —      | _      | _     | _      | _     |                  | —    | —    | _    | —    |        | —    | 0000       |

| FB98                        | KPU/K"               | 15:0      | _      | _       | —     |       | _      | _      |       | _      |       |                  |      | _    |      | RPC7 | <3:0>  |      | 0000       |

#### OT AUTOUT DEALATED MAD

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register is only available on 44-pin devices. Note 1:

2: 3:

This register is only available on PIC32MX1XX devices. This register is only available on 36-pin and 44-pin devices.

#### REGISTER 21-2: RTCALRM: RTC ALARM CONTROL REGISTER (CONTINUED)

bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits<sup>(2)</sup> 11111111 = Alarm will trigger 256 times

> 00000000 = Alarm will trigger one time The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1.

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

Note: This register is reset only on a Power-on Reset (POR).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        | —                 | —                 | HR10              | <1:0>             | HR01<3:0>         |                   |                  |                  |  |  |  |

| 00.40        | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        |                   |                   | MIN10<2:0>        |                   |                   | MIN01             | <3:0>            |                  |  |  |  |

| 45.0         | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         |                   |                   | SEC10<2:0>        |                   | SEC01<3:0>        |                   |                  |                  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 7:0          |                   | —                 | —                 |                   | _                 | -                 | —                | —                |  |  |  |

|              |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:      |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 21-5: ALRMTIME: ALARM TIME VALUE REGISTER

# R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary Coded Decimal value of hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 **HR01<3:0>:** Binary Coded Decimal value of hours bits, 1s place digit; contains a value from 0 to 9 bit 23 **Unimplemented:** Read as '0'

bit 22-20 MIN10<2:0>: Binary Coded Decimal value of minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 **MIN01<3:0>:** Binary Coded Decimal value of minutes bits, 1s place digit; contains a value from 0 to 9 bit 15 **Unimplemented:** Read as '0'

bit 14-12 SEC10<2:0>: Binary Coded Decimal value of seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 **SEC01<3:0>:** Binary Coded Decimal value of seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        |                   | —                 | —                 | —                 | _                 |                   | —                | _                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | _                 | —                 | —                 | _                 | _                 | —                 | —                | _                |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | CSSL15            | CSSL14            | CSSL13            | CSSL12            | CSSL11            | CSSL10            | CSSL9            | CSSL8            |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | CSSL7             | CSSL6             | CSSL5             | CSSL4             | CSSL3             | CSSL2             | CSSL1            | CSSL0            |  |  |  |  |

#### REGISTER 22-5: AD1CSSL: ADC INPUT SCAN SELECT REGISTER

#### Legend:

| Logena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CSSL<15:0>: ADC Input Pin Scan Selection bits<sup>(1,2)</sup>

1 = Select ANx for input scan

0 = Skip ANx for input scan

- **Note 1:** CSSL = ANx, where 'x' = 0-12; CSSL13 selects CTMU input for scan; CSSL14 selects IVREF for scan; CSSL15 selects Vss for scan.

- 2: On devices with less than 13 analog inputs, all CSSLx bits can be selected; however, inputs selected for scan without a corresponding input on the device will convert to VREFL.

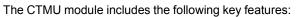

### 25.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Charge Time Measurement Unit (CTMU) is a flexible analog module that has a configurable current source with a digital configuration circuit built around it. The CTMU can be used for differential time measurement between pulse sources and can be used for generating an asynchronous pulse. By working with other on-chip analog modules, the CTMU can be used for high resolution time measurement, measure capacitance, measure relative changes in capacitance or generate output pulses with a specific time delay. The CTMU is ideal for interfacing with capacitive-based sensors.

- Up to 13 channels available for capacitive or time measurement input

- · On-chip precision current source

- 16-edge input trigger sources

- · Selection of edge or level-sensitive inputs

- · Polarity control for each edge source

- Control of edge sequence

- Control of response to edges

- · High precision time measurement

- Time delay of external or internal signal asynchronous to system clock

- · Integrated temperature sensing diode

- · Control of current source during auto-sampling

- · Four current source ranges

- · Time measurement resolution of one nanosecond

A block diagram of the CTMU is shown in Figure 25-1.

© 2011-2016 Microchip Technology Inc.

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3           | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-----------------------------|-------------------|---------------------|-------------------|-----------------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R                           | R                 | R                   | R                 | R                           | R                 | R                | R                |  |  |  |

| 31:24        |                             | VER<              | 3:0> <sup>(1)</sup> |                   | DEVID<27:24> <sup>(1)</sup> |                   |                  |                  |  |  |  |

| 00.40        | R                           | R                 | R                   | R                 | R                           | R                 | R                | R                |  |  |  |

| 23:16        | DEVID<23:16> <sup>(1)</sup> |                   |                     |                   |                             |                   |                  |                  |  |  |  |

| 45.0         | R                           | R                 | R                   | R                 | R                           | R                 | R                | R                |  |  |  |

| 15:8         | DEVID<15:8> <sup>(1)</sup>  |                   |                     |                   |                             |                   |                  |                  |  |  |  |

| 7.0          | R                           | R                 | R                   | R                 | R                           | R                 | R                | R                |  |  |  |

| 7:0          |                             |                   |                     | DEVID             | <7:0>(1)                    |                   |                  |                  |  |  |  |

#### REGISTER 27-6: DEVID: DEVICE AND REVISION ID REGISTER

#### Legend:

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 DEVID<27:0>: Device ID bits<sup>(1)</sup>

**Note 1:** See the "*PIC32 Flash Programming Specification*" (DS60001145) for a list of Revision and Device ID values.

#### 29.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 29.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 29.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 29.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

#### 29.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

#### TABLE 30-18: PLL CLOCK TIMING SPECIFICATIONS

| AC CHA        | RACTERI | STICS                                                               | (unless ot        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |         |      |                                |                                      |  |  |

|---------------|---------|---------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|--------------------------------|--------------------------------------|--|--|

| Param.<br>No. | Symbol  | Characteristi                                                       | cs <sup>(1)</sup> | Min.                                                                                                                                                                                                                                                                                  | Typical | Max. | Units                          | Conditions                           |  |  |

| OS50          | Fplli   | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range |                   | 3.92                                                                                                                                                                                                                                                                                  | _       | 5    | MHz                            | ECPLL, HSPLL, XTPLL,<br>FRCPLL modes |  |  |

| OS51          | Fsys    | On-Chip VCO Syste<br>Frequency                                      | m                 | 60                                                                                                                                                                                                                                                                                    | —       | 120  | MHz                            | _                                    |  |  |

| OS52          | TLOCK   | PLL Start-up Time (Lock Time)                                       |                   | _                                                                                                                                                                                                                                                                                     | _       | 2    | ms                             | —                                    |  |  |

| OS53          | DCLK    | CLKO Stability <sup>(2)</sup><br>(Period Jitter or Curr             | -0.25             | —                                                                                                                                                                                                                                                                                     | +0.25   | %    | Measured over 100 ms<br>period |                                      |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{SYSCLK}{CommunicationClock}}}$$

For example, if SYSCLK = 40 MHz and SPI bit rate = 20 MHz, the effective jitter is as follows:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{40}{20}}} = \frac{D_{CLK}}{1.41}$$

#### TABLE 30-19: INTERNAL FRC ACCURACY

| AC CHARACTERISTICS |                                                 | (unless | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |       |            |  |  |  |  |

|--------------------|-------------------------------------------------|---------|------------------------------------------------------|------|-------|------------|--|--|--|--|

| Param.<br>No.      | Characteristics                                 | Min.    | Typical                                              | Max. | Units | Conditions |  |  |  |  |

| Internal           | Internal FRC Accuracy @ 8.00 MHz <sup>(1)</sup> |         |                                                      |      |       |            |  |  |  |  |

| F20b               | FRC                                             | -0.9    |                                                      | +0.9 | %     | _          |  |  |  |  |

Note 1: Frequency calibrated at 25°C and 3.3V. The TUN bits can be used to compensate for temperature drift.

#### TABLE 30-20: INTERNAL LPRC ACCURACY

| АС СНА                        | RACTERISTICS                    | (unless | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |            |  |  |  |  |

|-------------------------------|---------------------------------|---------|-------------------------------------------------------|------|-------|------------|--|--|--|--|

| Param.<br>No. Characteristics |                                 | Min.    | Typical                                               | Max. | Units | Conditions |  |  |  |  |