#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Dectano                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 50MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 32K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

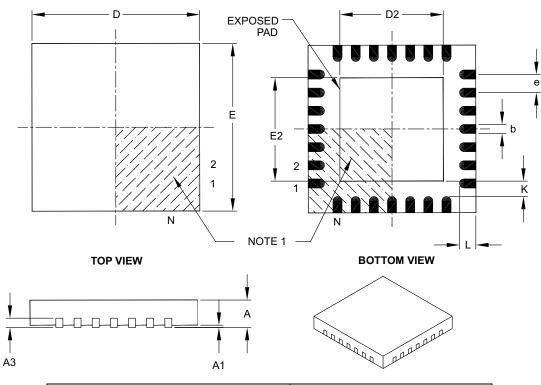

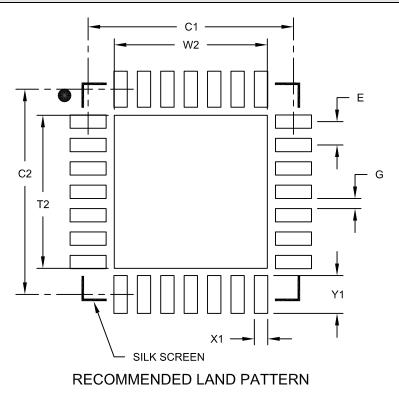

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                    |

| Supplier Device Package    | 28-SSOP                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx150f128bt-50i-ss |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 10: PIN NAMES FOR 44-PIN USB DEVICES

#### 44-PIN QFN (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX210F016D PIC32MX220F032D PIC32MX230F064D PIC32MX230F256D PIC32MX250F128D PIC32MX270F256D

|       |                                                  |       | 44 1                                      |

|-------|--------------------------------------------------|-------|-------------------------------------------|

| Pin # | Full Pin Name                                    | Pin # | Full Pin Name                             |

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                         | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 2     | RPC6/PMA1/RC6                                    | 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 3     | RPC7/PMA0/RC7                                    | 25    | AN6/RPC0/RC0                              |

| 4     | RPC8/PMA5/RC8                                    | 26    | AN7/RPC1/RC1                              |

| 5     | RPC9/CTED7/PMA6/RC9                              | 27    | AN8/RPC2/PMA2/RC2                         |

| 6     | Vss                                              | 28    | Vdd                                       |

| 7     | VCAP                                             | 29    | Vss                                       |

| 8     | PGED2/RPB10/D+/CTED11/RB10                       | 30    | OSC1/CLKI/RPA2/RA2                        |

| 9     | PGEC2/RPB11/D-/RB11                              | 31    | OSC2/CLKO/RPA3/RA3                        |

| 10    | VUSB3V3                                          | 32    | TDO/RPA8/PMA8/RA8                         |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                       | 33    | SOSCI/RPB4/RB4                            |

| 12    | PGED4/TMS/PMA10/RA10                             | 34    | SOSCO/RPA4/T1CK/CTED9/RA4                 |

| 13    | PGEC4/TCK/CTED8/PMA7/RA7                         | 35    | TDI/RPA9/PMA9/RA9                         |

| 14    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 | 36    | AN12/RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            | 37    | RPC4/PMA4/RC4                             |

| 16    | AVss                                             | 38    | RPC5/PMA3/RC5                             |

| 17    | AVDD                                             | 39    | Vss                                       |

| 18    | MCLR                                             | 40    | Vdd                                       |

| 19    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 | 41    | RPB5/USBID/RB5                            |

| 20    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       | 42    | VBUS                                      |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        | 43    | RPB7/CTED3/PMD5/INT0/RB7                  |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       | 44    | RPB8/SCL1/CTED10/PMD4/RB8                 |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

5: Shaded pins are 5V tolerant.

#### TABLE 1-1: **PINOUT I/O DESCRIPTIONS**

|          |                   | Pin Nu                                      | nber <sup>(1)</sup>                    |                                        |             |                |                                                                                                                                                                                                |  |  |  |

|----------|-------------------|---------------------------------------------|----------------------------------------|----------------------------------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name | 28-pin<br>QFN     | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC           | 36-pin<br>VTLA                         | 44-pin<br>QFN/<br>TQFP/<br>VTLA        | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                    |  |  |  |

| AN0      | 27                | 2                                           | 33                                     | 19                                     |             | Analog         | Analog input channels.                                                                                                                                                                         |  |  |  |

| AN1      | 28                | 3                                           | 34                                     | 20                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |

| AN2      | 1                 | 4                                           | 35                                     | 21                                     |             | Analog         |                                                                                                                                                                                                |  |  |  |

| AN3      | 2                 | 5                                           | 36                                     | 22                                     |             | Analog         |                                                                                                                                                                                                |  |  |  |

| AN4      | 3                 | 6                                           | 1                                      | 23                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |

| AN5      | 4                 | 7                                           | 2                                      | 24                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |

| AN6      | _                 | _                                           | 3                                      | 25                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |

| AN7      | _                 | _                                           | 4                                      | 26                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |

| AN8      | _                 | _                                           | _                                      | 27                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |

| AN9      | 23                | 26                                          | 29                                     | 15                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |

| AN10     | 22                | 25                                          | 28                                     | 14                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |

| AN11     | 21                | 24                                          | 27                                     | 11                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |

| AN12     | 20 <sup>(2)</sup> | 23 <sup>(2)</sup>                           | 26 <sup>(2)</sup><br>11 <sup>(3)</sup> | 10 <sup>(2)</sup><br>36 <sup>(3)</sup> | 1           | Analog         | *                                                                                                                                                                                              |  |  |  |

| CLKI     | 6                 | 9                                           | 7                                      | 30                                     | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                         |  |  |  |

| CLKO     | 7                 | 10                                          | 8                                      | 31                                     | 0           | _              | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes. Always associated<br>with OSC2 pin function. |  |  |  |

| OSC1     | 6                 | 9                                           | 7                                      | 30                                     | I           | ST/CMOS        | -                                                                                                                                                                                              |  |  |  |

| OSC2     | 7                 | 10                                          | 8                                      | 31                                     | 0           | -              | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes.                                              |  |  |  |

| SOSCI    | 8                 | 11                                          | 9                                      | 33                                     | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal<br>input; CMOS otherwise.                                                                                                                              |  |  |  |

| SOSCO    | 9                 | 12                                          | 10                                     | 34                                     | 0           | —              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                |  |  |  |

| REFCLKI  | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | Reference Input Clock                                                                                                                                                                          |  |  |  |

| REFCLKO  | PPS               | PPS                                         | PPS                                    | PPS                                    | 0           | —              | Reference Output Clock                                                                                                                                                                         |  |  |  |

| IC1      | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | Capture Inputs 1-5                                                                                                                                                                             |  |  |  |

| IC2      | PPS               | PPS                                         | PPS                                    | PPS                                    | 1           | ST             | 1                                                                                                                                                                                              |  |  |  |

| IC3      | PPS               | PPS                                         | PPS                                    | PPS                                    | 1           | ST             | 1                                                                                                                                                                                              |  |  |  |

| IC4      | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | 1                                                                                                                                                                                              |  |  |  |

| IC5      | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | 1                                                                                                                                                                                              |  |  |  |

|          | ST = Schm         | MOS compa<br>itt Trigger in<br>input buffer |                                        |                                        | •           | O = Outp       | Analog inputP = PowerutI = Inputeripheral Pin Select— = N/A                                                                                                                                    |  |  |  |

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability. 2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

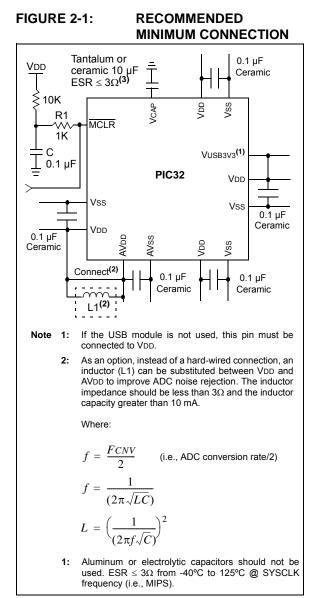

### 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ . This capacitor should be located as close to the device as possible.

## 2.3 Capacitor on Internal Voltage Regulator (VCAP)

#### 2.3.1 INTERNAL REGULATOR MODE

A low-ESR (3 ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD, and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. Refer to **30.0 "Electrical Characteristics"** for additional information on CEFC specifications.

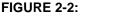

# 2.4 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides two specific device functions:

- Device Reset

- · Device programming and debugging

Pulling The  $\overline{\text{MCLR}}$  pin low generates a device Reset. Figure 2-2 illustrates a typical  $\overline{\text{MCLR}}$  circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

# EXAMPLE OF MCLR PIN CONNECTIONS

**3:** No pull-ups or bypass capacitors are allowed on active debug/program PGECx/PGEDx pins.

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

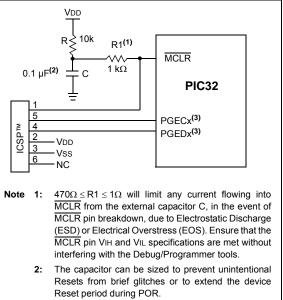

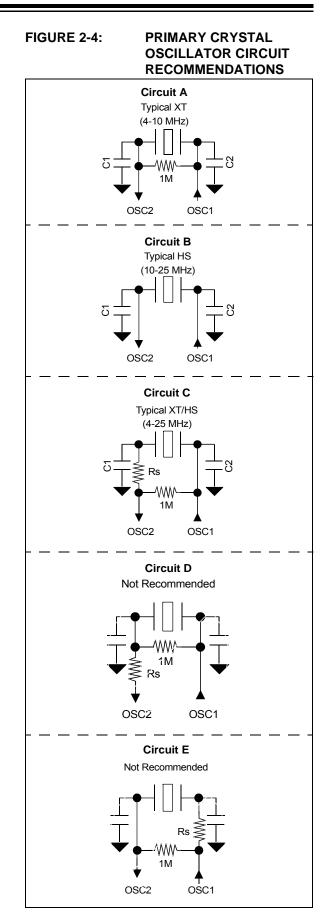

#### 2.8.1 CRYSTAL OSCILLATOR DESIGN CONSIDERATION

The following example assumptions are used to calculate the Primary Oscillator loading capacitor values:

- CIN = PIC32\_OSC2\_Pin Capacitance = ~4-5 pF

- COUT = PIC32\_OSC1\_Pin Capacitance = ~4-5 pF

- C1 and C2 = XTAL manufacturing recommended loading capacitance

- Estimated PCB stray capacitance, (i.e.,12 mm length) = 2.5 pF

#### EXAMPLE 2-1: CRYSTAL LOAD CAPACITOR CALCULATION

The following tips are used to increase oscillator gain, (i.e., to increase peak-to-peak oscillator signal):

- Select a crystal with a lower "minimum" power drive rating

- Select an crystal oscillator with a lower XTAL manufacturing "ESR" rating.

- Add a parallel resistor across the crystal. The smaller the resistor value the greater the gain. It is recommended to stay in the range of 600k to 1M

- C1 and C2 values also affect the gain of the oscillator. The lower the values, the higher the gain.

- C2/C1 ratio also affects gain. To increase the gain, make C1 slightly smaller than C2, which will also help start-up performance.

- Note: Do not add excessive gain such that the oscillator signal is clipped, flat on top of the sine wave. If so, you need to reduce the gain or add a series resistor, RS, as shown in circuit "C" in Figure 2-4. Failure to do so will stress and age the crystal, which can result in an early failure. Adjust the gain to trim the max peak-to-peak to ~VDD-0.6V. When measuring the oscillator signal you must use a FET scope probe or a probe with ≤ 1.5 pF or the scope probe itself will unduly change the gain and peak-to-peak levels.

#### 2.8.1.1 Additional Microchip References

- AN588 "PICmicro<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826 "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849 "Basic PICmicro<sup>®</sup> Oscillator Design"

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 31:24        | BMXPFMSZ<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 23:16        | BMXPFMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 15:8         | BMXPFMSZ<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 7:0          |                   |                   |                   | BMXPF             | MSZ<7:0>          |                   |                  |                  |  |  |  |

#### REGISTER 4-7: BMXPFMSZ: PROGRAM FLASH (PFM) SIZE REGISTER

# Legend:

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 BMXPFMSZ<31:0>: Program Flash Memory (PFM) Size bits

Static value that indicates the size of the PFM in bytes: 0x00004000 = Device has 16 KB Flash 0x00008000 = Device has 32 KB Flash 0x00010000 = Device has 64 KB Flash 0x00020000 = Device has 128 KB Flash 0x00040000 = Device has 256 KB Flash

### REGISTER 4-8: BMXBOOTSZ: BOOT FLASH (IFM) SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 |   |   | Bit Bit<br>28/20/12/4 27/19/11/3 |           | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|---|---|----------------------------------|-----------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R                 | R | R | R                                | R         | R                 | R                | R                |  |  |  |

| 31:24        | BMXBOOTSZ<31:24>  |   |   |                                  |           |                   |                  |                  |  |  |  |

| 00.40        | R                 | R | R | R                                | R         | R                 | R                | R                |  |  |  |

| 23:16        | BMXBOOTSZ<23:16>  |   |   |                                  |           |                   |                  |                  |  |  |  |

| 45.0         | R                 | R | R | R                                | R         | R                 | R                | R                |  |  |  |

| 15:8         | BMXBOOTSZ<15:8>   |   |   |                                  |           |                   |                  |                  |  |  |  |

| 7.0          | R                 | R | R | R                                | R         | R                 | R                | R                |  |  |  |

| 7:0          |                   |   |   | BMXBO                            | OTSZ<7:0> |                   |                  |                  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 **BMXBOOTSZ<31:0>:** Boot Flash Memory (BFM) Size bits Static value that indicates the size of the Boot PFM in bytes: 0x00000C00 = Device has 3 KB boot Flash

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4     | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|----------------------|-----------------------|------------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | —                 | —                 | _                    | —                     | —                      |                   | _                |                  |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | —                 | —                 | —                    | —                     | —                      | —                 | —                | —                |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R-0                  | R-0                   | R-0                    | U-0               | U-0              | U-0              |  |  |  |  |  |

| 15:8         | WR                | WREN              | WRERR <sup>(1)</sup> | LVDERR <sup>(1)</sup> | LVDSTAT <sup>(1)</sup> |                   | _                |                  |  |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0                  | U-0                   | R/W-0                  | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          | _                 | —                 |                      | —                     |                        | NVMOF             | P<3:0>           |                  |  |  |  |  |  |

|              |                   |                   |                      |                       |                        |                   |                  |                  |  |  |  |  |  |

#### REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re- | ad as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

| 011 31-10           | Unimplemented. Read as 0                                                                                              |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|

| bit 15              | WR: Write Control bit                                                                                                 |

|                     | This bit is writable when WREN = 1 and the unlock sequence is followed.                                               |

|                     | 1 = Initiate a Flash operation. Hardware clears this bit when the operation completes                                 |

|                     | 0 = Flash operation is complete or inactive                                                                           |

| bit 14              | WREN: Write Enable bit                                                                                                |

|                     | This is the only bit in this register reset by a device Reset.                                                        |

|                     | 1 = Enable writes to WR bit and enables LVD circuit                                                                   |

|                     | 0 = Disable writes to WR bit and disables LVD circuit                                                                 |

| bit 13              | WRERR: Write Error bit <sup>(1)</sup>                                                                                 |

|                     | This bit is read-only and is automatically set by hardware.                                                           |

|                     | 1 = Program or erase sequence did not complete successfully                                                           |

|                     | 0 = Program or erase sequence completed normally                                                                      |

| bit 12              | LVDERR: Low-Voltage Detect Error bit (LVD circuit must be enabled) <sup>(1)</sup>                                     |

|                     | This bit is read-only and is automatically set by hardware.                                                           |

|                     | 1 = Low-voltage detected (possible data corruption, if WRERR is set)                                                  |

|                     | 0 = Voltage level is acceptable for programming                                                                       |

| bit 11              | LVDSTAT: Low-Voltage Detect Status bit (LVD circuit must be enabled) <sup>(1)</sup>                                   |

|                     | This bit is read-only and is automatically set and cleared by the hardware.                                           |

|                     | 1 = Low-voltage event is active                                                                                       |

| hit 10 1            | 0 = Low-voltage event is not active                                                                                   |

| bit 10-4<br>bit 3-0 | Unimplemented: Read as '0'                                                                                            |

| 0-6 110             | <b>NVMOP&lt;3:0&gt;:</b> NVM Operation bits<br>These bits are writable when WREN = 0.                                 |

|                     |                                                                                                                       |

|                     | 1111 = Reserved                                                                                                       |

|                     | •                                                                                                                     |

|                     | •                                                                                                                     |

|                     | 0111 = Reserved<br>0110 = No operation                                                                                |

|                     | 0101 = Program Flash Memory (PFM) erase operation: erases PFM, if all pages are not write-protected                   |

|                     | 0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected                            |

|                     | 0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected                          |

|                     | 0010 = No operation                                                                                                   |

|                     | 0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected<br>0000 = No operation |

|                     |                                                                                                                       |

**Note 1:** This bit is cleared by setting NVMOP == `b0000, and initiating a Flash operation (i.e., WR).

# 6.1 Reset Control Registers

# TABLE 6-1: RESET CONTROL REGISTER MAP

| ess                         | Register<br>Name <sup>(1)</sup> | Bits      |       |       |       |       |       |       |      |       |      |      |      | s    |       |      |      |       |           |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|-------|------|------|------|------|-------|------|------|-------|-----------|

| Virtual Address<br>(BF80_#) |                                 | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7 | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1 | 16/0  | All Reset |

| F600                        | RCON                            | 31:16     | _     | _     | _     |       | —     | _     |      | —     | _    | _    |      | _    |       | -    | -    | _     | 0000      |

| 1 000                       | ROOM                            | 15:0      | _     |       | -     |       | _     | -     | CMR  | VREGS | EXTR | SWR  |      | WDTO | SLEEP | IDLE | BOR  | POR   | xxxx(2)   |

| E610                        | RSWRST                          | 31:16     |       | —     | -     | —     | —     | —     | —    | —     |      | —    | —    | _    | —     | _    | —    | —     | 0000      |

| 1010                        | N31/K31                         | 15:0      | _     | _     | _     | -     | _     | —     |      | —     | _    | _    | -    | _    | _     | _    | -    | SWRST | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

| Bit<br>Range | Bit<br>31/23/15/7              | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|--------------------------------|-------------------|-------------------|-------------------|---------------------|-------------------|------------------|------------------|--|--|--|--|--|

|              | U-0                            | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        | — RODIV<14:8> <sup>(1,3)</sup> |                   |                   |                   |                     |                   |                  |                  |  |  |  |  |  |

|              | R/W-0                          | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | RODIV<7:0> <sup>(1,3)</sup>    |                   |                   |                   |                     |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0                          | U-0               | R/W-0             | R/W-0             | R/W-0               | U-0               | R/W-0, HC        | R-0, HS, HC      |  |  |  |  |  |

| 15:8         | ON                             | _                 | SIDL              | OE                | RSLP <sup>(2)</sup> | _                 | DIVSWEN          | ACTIVE           |  |  |  |  |  |

|              | U-0                            | U-0               | U-0               | U-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                                |                   |                   |                   |                     | ROSEL             | .<3:0>(1)        |                  |  |  |  |  |  |

#### REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| Legend:           | HC = Hardware Clearable | HS = Hardware Settable   |                    |

|-------------------|-------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |

bit 31 Unimplemented: Read as '0'

| bit 30-16 | RODIV<14:0> Reference Clock Divider bits <sup>(1,3)</sup>                           |

|-----------|-------------------------------------------------------------------------------------|

|           | The value selects the reference clock divider bits. See Figure 8-1 for information. |

| bit 15    | ON: Output Enable bit                                                               |

|           | 1 = Reference Oscillator module is enabled                                          |

|           | 0 = Reference Oscillator module is disabled                                         |

| bit 14    | Unimplemented: Read as '0'                                                          |

| bit 13    | SIDL: Peripheral Stop in Idle Mode bit                                              |

- 1 = Discontinue module operation when the device enters Idle mode

- 0 =Continue module operation when the device enters lide mode

- bit 12 **OE:** Reference Clock Output Enable bit

- 1 = Reference clock is driven out on REFCLKO pin

- 0 = Reference clock is not driven out on REFCLKO pin

- bit 11 RSLP: Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference Oscillator module output continues to run in Sleep

- 0 = Reference Oscillator module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 DIVSWEN: Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- bit 8 ACTIVE: Reference Clock Request Status bit

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- **2:** This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

## REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER (CONTINUED)

bit 6 **CRCAPP:** CRC Append Mode bit<sup>(1)</sup>

- 1 = The DMA transfers data from the source into the CRC but NOT to the destination. When a block transfer completes the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC obeying WBO as it writes the data to the destination

- bit 5 **CRCTYP:** CRC Type Selection bit

- 1 = The CRC module will calculate an IP header checksum

- 0 = The CRC module will calculate a LFSR CRC

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 CRCCH<2:0>: CRC Channel Select bits

- 111 = CRC is assigned to Channel 7

- 110 = CRC is assigned to Channel 6

- 101 = CRC is assigned to Channel 5

- 100 = CRC is assigned to Channel 4

- 011 = CRC is assigned to Channel 3

- 010 = CRC is assigned to Channel 2

- 001 = CRC is assigned to Channel 1

- 000 = CRC is assigned to Channel 0

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

#### **USB Control Registers** 10.1

# TABLE 10-1: USB REGISTER MAP

| ess                         |                                 |           |       |       |       |       |       |       |      |      | Bit                    | s        |          |                  |          |          |                 |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------------------------|----------|----------|------------------|----------|----------|-----------------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7                   | 22/6     | 21/5     | 20/4             | 19/3     | 18/2     | 17/1            | 16/0     | All Resets |

| 5040                        | (4)                             | 31:16     | _     | —     | —     | —     | —     | —     |      | _    | —                      | —        | —        | —                | —        | —        | _               | —        | 000        |

| 5040                        | UTUTUIK()                       | 15:0      |       | _     | _     | —     | _     | _     |      | _    | IDIF                   | T1MSECIF | LSTATEIF | ACTVIF           | SESVDIF  | SESENDIF | 1               | VBUSVDIF | 000        |

| 5050                        | <b>U10TGIE</b>                  | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —                      |          | —        | —                | —        | —        | _               | —        | 000        |

| 0000                        | OTOTOLE                         | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | IDIE                   | T1MSECIE | LSTATEIE | ACTVIE           | SESVDIE  | SESENDIE | _               | VBUSVDIE | 000        |

| 5060                        | U10TGSTAT <sup>(3)</sup>        | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |                        |          | —        | —                |          | —        | _               |          | 000        |

| 0000                        | 0101001/11                      | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | ID                     |          | LSTATE   | —                | SESVD    | SESEND   | _               | VBUSVD   | 000        |

| 5070                        | U10TGCON                        | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |                        |          | —        | —                |          | —        | _               |          | 000        |

| 0070                        | UTOTOOON                        | 15:0      | _     | —     | —     | —     | —     | —     | _    | —    | DPPULUP                | DMPULUP  | DPPULDWN | DMPULDWN         | VBUSON   | OTGEN    | VBUSCHG         | VBUSDIS  | 000        |

| 5080                        | U1PWRC                          | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |                        |          | —        | —                |          | —        | _               |          | 000        |

| 0000                        | on wite                         | 15:0      | _     | —     | —     | —     | —     | —     | _    | —    | UACTPND <sup>(4)</sup> |          | —        | USLPGRD          | USBBUSY  | —        | USUSPEND        | USBPWR   | 000        |

|                             |                                 | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |                        |          | —        | —                |          | —        | _               |          | 000        |

| 5200                        | U1IR <sup>(2)</sup>             | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | STALLIF                | ATTACHIF | RESUMEIF | IDLEIF           | TRNIF    | SOFIF    | UERRIF          | URSTIF   | 000        |

|                             |                                 | 04.40     |       |       |       |       |       |       |      |      |                        |          |          |                  |          |          |                 | DETACHIF | 000        |

| 5210                        | U1IE                            | 31:16     | _     | _     |       |       |       |       |      | _    | —                      | —        |          | —                | —        | —        | —               |          | 000        |

| 5210                        | OTIE                            | 15:0      | —     | —     |       | —     | —     | —     | —    | —    | STALLIE                | ATTACHIE | RESUMEIE | IDLEIE           | TRNIE    | SOFIE    | UERRIE          | DETACHIE | 000        |

|                             |                                 | 31:16     | _     | _     | _     | _     |       | _     |      |      | _                      | _        | _        | _                | _        | _        | _               |          | 000        |

| 5220                        | U1EIR <sup>(2)</sup>            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | BTSEF                  | BMXEF    | DMAEF    | BTOEF            | DFN8EF   | CRC16EF  | CRC5EF<br>EOFEF | PIDEF    | 000        |

|                             |                                 | 31:16     | _     | _     |       | _     | _     | _     | _    | _    | _                      |          | _        | _                | _        | _        | _               |          | 000        |

| 5230                        | U1EIE                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | BTSEE                  | BMXEE    | DMAEE    | BTOEE            | DFN8EE   | CRC16EE  | CRC5EE<br>EOFEE | PIDEE    | 000        |

|                             | (2)                             | 31:16     | _     | _     |       | _     | _     |       |      | _    |                        | _        |          | _                | _        |          | _               | _        | 000        |

| 5240                        | U1STAT <sup>(3)</sup>           | 15:0      | _     | _     | _     | _     | _     | _     |      | _    |                        |          | PT<3:0>  |                  | DIR      | PPBI     | _               | _        | 000        |

|                             |                                 | 31:16     | _     |       | _     | _     | _     | _     |      | _    | _                      | _        |          |                  | _        | _        | _               | _        | 000        |

| 5250                        | U1CON                           |           |       |       |       |       |       |       |      |      |                        |          | PKTDIS   |                  |          |          |                 | USBEN    | 000        |

|                             |                                 | 15:0      |       | —     | —     | —     | —     | —     |      | —    | JSTATE                 | SE0      | TOKBUSY  | USBRST           | HOSTEN   | RESUME   | PPBRST          | SOFEN    | 000        |

| 5260                        | U1ADDR                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _                      | _        | _        | _                | _        | _        | _               | —        | 000        |

| 5260                        | UTADDR                          | 15:0      | _     | _     | _     | _     | _     | —     | _    | _    | LSPDEN                 |          |          | DE               | VADDR<6: | 0>       |                 |          | 000        |

| 5070                        |                                 | 31:16     | -     | _     | _     | _     | _     | _     | _    | _    | _                      | _        | _        | _                | _        | _        | _               | _        | 000        |

| 5270                        | U1BDTP1                         | 15:0      | —     |       |       | —     |       |       |      | _    |                        |          | BC       | )<br>TPTRL<15:9> | >        |          |                 |          | 0000       |

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information. Note 1:

2: This register does not have associated SET and INV registers.

This register does not have associated CLR, SET and INV registers. 3:

4: Reset value for this bit is undefined.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### REGISTER 10-3: U1OTGSTAT: USB OTG STATUS REGISTER

|              |                   |                   |                   | • • • • • • •     |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 51.24        | -                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   | —                 | —                 | —                 | _                 | —                 |                  | —                |

| 7:0          | R-0               | U-0               | R-0               | U-0               | R-0               | R-0               | U-0              | R-0              |

| 7.0          | ID                |                   | LSTATE            | _                 | SESVD             | SESEND            | _                | VBUSVD           |

#### Legend:

| Logona.           |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 ID: ID Pin State Indicator bit

- 1 = No cable is attached or a "type B" cable has been inserted into the USB receptacle

- 0 = A "type A" OTG cable has been inserted into the USB receptacle

- bit 6 Unimplemented: Read as '0'

- bit 5 LSTATE: Line State Stable Indicator bit

- 1 = USB line state (SE0 (U1CON<6>) bit and JSTATE (U1CON<7>)) bit has been stable for previous 1 ms 0 = USB line state (SE0 and JSTATE) has not been stable for previous 1 ms

#### bit 4 Unimplemented: Read as '0'

- bit 3 SESVD: Session Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A or B device

- 0 = VBUS voltage is below Session Valid on the A or B device

- bit 2 SESEND: B-Device Session End Indicator bit

- 1 = VBUS voltage is below Session Valid on the B device

- 0 = VBUS voltage is above Session Valid on the B device

#### bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVD: A-Device VBUS Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A device

- 0 = VBUS voltage is below Session Valid on the A device

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

### TABLE 11-1: INPUT PIN SELECTION

| Peripheral Pin | [pin name]R SFR | [pin name]R bits | [ <i>pin name</i> ]R Value to<br>RPn Pin Selection                                     |

|----------------|-----------------|------------------|----------------------------------------------------------------------------------------|

| INT4           | INT4R           | INT4R<3:0>       | 0000 = RPA0<br>0001 = RPB3                                                             |

| T2CK           | T2CKR           | T2CKR<3:0>       | 0010 = RPB4<br>0011 = RPB15<br>0100 = RPB7                                             |

| IC4            | IC4R            | IC4R<3:0>        | 0101 = RPC7 <sup>(2)</sup><br>0110 = RPC0 <sup>(1)</sup><br>0111 = RPC5 <sup>(2)</sup> |

| SS1            | SS1R            | SS1R<3:0>        | 1000 = Reserved                                                                        |

| REFCLKI        | REFCLKIR        | REFCLKIR<3:0>    | :<br>1111 = Reserved                                                                   |

| INT3           | INT3R           | INT3R<3:0>       | 0000 = RPA1<br>0001 = RPB5                                                             |

| ТЗСК           | T3CKR           | T3CKR<3:0>       | 0010 = RPB1<br>0011 = RPB11                                                            |

| IC3            | IC3R            | IC3R<3:0>        | 0100 = RPB8<br>0101 = RPA8 <sup>(2)</sup>                                              |

| U1CTS          | U1CTSR          | U1CTSR<3:0>      | 0110 = RPC8 <sup>(2)</sup><br>0111 = RPA9 <sup>(2)</sup>                               |

| U2RX           | U2RXR           | U2RXR<3:0>       | 1000 = Reserved                                                                        |

| SDI1           | SDI1R           | SDI1R<3:0>       | •<br>1111 = Reserved                                                                   |

| INT2           | INT2R           | INT2R<3:0>       | 0000 = RPA2                                                                            |

| T4CK           | T4CKR           | T4CKR<3:0>       |                                                                                        |

| IC1            | IC1R            | IC1R<3:0>        | 0011 = RPB13<br>0100 = RPB2                                                            |

| IC5            | IC5R            | IC5R<3:0>        | 0101 = RPC6 <sup>(2)</sup>                                                             |

| U1RX           | U1RXR           | U1RXR<3:0>       | 0110 = RPC1 <sup>(1)</sup><br>0111 = RPC3 <sup>(1)</sup>                               |

| U2CTS          | U2CTSR          | U2CTSR<3:0>      | 1000 = Reserved                                                                        |

| SDI2           | SDI2R           | SDI2R<3:0>       | •                                                                                      |

| OCFB           | OCFBR           | OCFBR<3:0>       | •<br>1111 = Reserved                                                                   |

| INT1           | INT1R           | INT1R<3:0>       | 0000 = RPA3<br>0001 = RPB14                                                            |

| T5CK           | T5CKR           | T5CKR<3:0>       | 0010 = RPB0<br>0011 = RPB10<br>0100 = RPB9                                             |

| IC2            | IC2R            | IC2R<3:0>        | 0101 = RPC9 <sup>(1)</sup><br>0110 = RPC2 <sup>(2)</sup><br>0111 = RPC4 <sup>(2)</sup> |

| SS2            | SS2R            | SS2R<3:0>        | 1000 = Reserved                                                                        |

| OCFA           | OCFAR           | OCFAR<3:0>       | •<br>•<br>1111 = Reserved                                                              |

Note 1: This pin is not available on 28-pin devices.

2: This pin is only available on 44-pin devices.

#### **Input Capture Control Registers** 15.1

|                             | LE 15-1:              | IN            | PUT C | APTURE | E 1-INPU | JT CAP | <b>FURE 5</b> | REGIST | ER MAI | 2      |        |      |      |      |       |      |          |

|-----------------------------|-----------------------|---------------|-------|--------|----------|--------|---------------|--------|--------|--------|--------|------|------|------|-------|------|----------|

| ess                         |                       |               |       |        |          |        |               |        |        | Bi     | ts     |      |      |      |       |      |          |

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range     | 31/15 | 30/14  | 29/13    | 28/12  | 27/11         | 26/10  | 25/9   | 24/8   | 23/7   | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1     |

| 2000                        | IC1CON <sup>(1)</sup> | 31:16         |       | —      | —        | —      | _             | —      | —      | —      | —      | —    | _    | —    | —     | _    | —        |

| 2000                        | 101001                | 15:0          | ON    | —      | SIDL     | —      | —             |        | FEDGE  | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |

| 2010                        | IC1BUF                | 31:16<br>15:0 |       |        |          |        |               |        |        | IC1BUF | <31:0> |      |      |      |       |      |          |

| 2200                        | IC2CON <sup>(1)</sup> | 31:16         |       | —      | —        | —      | —             | —      | —      | _      | —      | —    | —    | —    | _     |      | -        |

| 2200                        | 102001                | 15:0          | ON    | —      | SIDL     | —      | —             | —      | FEDGE  | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |

| 2210                        | IC2BUF                | 31:16<br>15:0 |       |        |          |        |               |        |        | IC2BUF | <31:0> |      |      |      |       |      |          |

| 2400                        | IC3CON <sup>(1)</sup> | 31:16         | -     | —      | _        | _      | _             | -      | —      | _      | —      | -    | _    | —    | —     |      | —        |

| 2400                        | 103001                | 15.0          | ON    | —      | SIDL     | —      | —             | —      | FEDGE  | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |

| 2410                        | IC3BUF                | 31:16<br>15:0 |       |        |          |        |               |        |        | IC3BUF | <31:0> |      |      |      |       |      |          |

| 2600                        | IC4CON <sup>(1)</sup> | 31:16         |       | _      | _        | —      | _             | _      | _      |        | _      | —    | —    | —    | _     |      | —        |

| 2000                        | 104001                | 15:0          | ON    | —      | SIDL     | —      | —             | —      | FEDGE  | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |

| 2610                        | IC4BUF                | 31:16<br>15:0 |       |        |          |        |               |        |        | IC4BUF | <31:0> |      |      |      |       |      |          |

| 2800                        | IC5CON <sup>(1)</sup> | 31:16         | -     | —      | —        | _      | _             | _      | —      | —      | —      | _    |      | —    | —     |      | —        |

| 2000                        | 1000014               | 15:0          | ON    | —      | SIDL     | _      | _             | _      | FEDGE  | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |

| 2810                        | IC5BUF                | 31:16<br>15:0 |       |        |          |        |               |        |        | IC5BUF | <31:0> |      |      |      |       |      |          |

#

Legend:

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information. Note 1:

All Resets

0000

0000 xxxx xxxx 0000 0000 xxxx xxxx 0000 0000 xxxx xxxx 0000 0000 xxxx xxxx 0000 0000 xxxx xxxx

16/0

—

#### TABLE 26-2: PERIPHERAL MODULE DISABLE REGISTER MAP

| ess                         |                                 |           |       |       |       |       |       |       |        |        | Bits |      |      |       |       |        |        |        | 6          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|--------|--------|------|------|------|-------|-------|--------|--------|--------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8   | 23/7 | 22/6 | 21/5 | 20/4  | 19/3  | 18/2   | 17/1   | 16/0   | All Resets |

| 5040                        | PMD1                            | 31:16     | —     | —     | _     | —     | _     | _     | _      | —      | —    | —    | —    | —     | —     | —      | —      | —      | 0000       |

| F240                        | FIVIDI                          | 15:0      | -     |       |       | CVRMD | Ι     |       |        | CTMUMD | —    | -    |      | -     | —     |        | —      | AD1MD  | 0000       |

| 5250                        | PMD2                            | 31:16     | —     | —     |       | —     | _     | _     |        | —      | —    | —    | —    | —     | —     | —      | —      | —      | 0000       |

| F250                        | FIVIDZ                          | 15:0      | -     |       |       | —     | Ι     |       |        | —      | —    | -    |      | -     | —     | CMP3MD | CMP2MD | CMP1MD | 0000       |

| F260                        | PMD3                            | 31:16     | _     | -     |       | _     | -     |       |        | _      | _    |      | _    | OC5MD | OC4MD | OC3MD  | OC2MD  | OC1MD  | 0000       |

| F200                        | FIVIDS                          | 15:0      | _     | -     |       | _     | -     |       |        | _      | _    |      | _    | IC5MD | IC4MD | IC3MD  | IC2MD  | IC1MD  | 0000       |

| F270                        | PMD4                            | 31:16     | _     | -     |       | _     | -     |       |        | _      | _    |      | _    | -     | _     | _      | —      | _      | 0000       |

| F270                        | F IVID4                         | 15:0      | _     | -     |       | _     | -     |       |        | _      | _    |      | _    | T5MD  | T4MD  | T3MD   | T2MD   | T1MD   | 0000       |

| F280                        | PMD5                            | 31:16     | _     | -     |       | _     | -     |       |        | USB1MD | _    |      | _    | -     | _     | _      | I2C1MD | I2C1MD | 0000       |

| F200                        | FIVIDS                          | 15:0      | _     | -     |       | _     | -     |       | SPI2MD | SPI1MD | _    |      | _    | -     | _     | _      | U2MD   | U1MD   | 0000       |

| F200                        | PMD6                            | 31:16     | _     | —     |       | —     | _     | _     |        | _      | —    | _    | —    | _     | —     | —      | —      | PMPMD  | 0000       |

| F290                        | I WD0                           | 15:0      | —     | _     | _     | —     | _     | _     | -      | —      | —    | _    | _    | _     | —     | _      | REFOMD | RTCCMD | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

# 27.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Configuration" Section 32. Section (DS60001124) and 33. "Programming and **Diagnostics**" (DS60001129), which are available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family devices include the following features intended to maximize application flexibility, reliability and minimize cost through elimination of external components.

- Flexible device configuration

- Joint Test Action Group (JTAG) interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

# 27.1 Configuration Bits

The Configuration bits can be programmed using the following registers to select various device configurations.

- DEVCFG0: Device Configuration Word 0

- DEVCFG1: Device Configuration Word 1

- DEVCFG2: Device Configuration Word 2

- DEVCFG3: Device Configuration Word 3

- · CFGCON: Configuration Control Register

In addition, the DEVID register (Register 27-6) provides device and revision information.

# 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

## 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- · Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

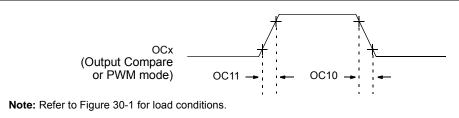

### FIGURE 30-8: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

### TABLE 30-26: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| AC CHA        | RACTER | ISTICS                         | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                        |      |       |                    |  |  |  |

|---------------|--------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|--|--|--|

| Param.<br>No. | Symbol | Characteristics <sup>(1)</sup> | Min.                                                                                                                                                                                               | Typical <sup>(2)</sup> | Max. | Units | Conditions         |  |  |  |

| OC10          | TccF   | OCx Output Fall Time           | —                                                                                                                                                                                                  | —                      | _    | ns    | See parameter DO32 |  |  |  |

| OC11          | TccR   | OCx Output Rise Time           | —                                                                                                                                                                                                  | —                      |      | ns    | See parameter DO31 |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

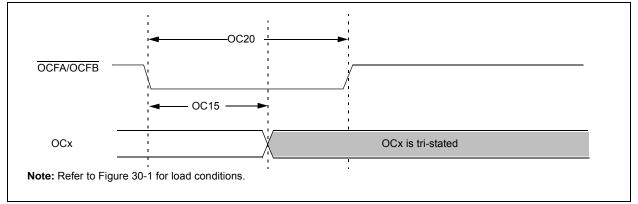

#### FIGURE 30-9: OCx/PWM MODULE TIMING CHARACTERISTICS

### TABLE 30-27: SIMPLE OCx/PWM MODE TIMING REQUIREMENTS

| AC CHAF      | AC CHARACTERISTICS |                                |                            | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |       |            |  |  |  |  |

|--------------|--------------------|--------------------------------|----------------------------|-------------------------------------------------------|-----|-------|------------|--|--|--|--|

| Param<br>No. | Symbol             | Characteristics <sup>(1)</sup> | Min Typical <sup>(2)</sup> |                                                       | Max | Units | Conditions |  |  |  |  |

| OC15         | TFD                | Fault Input to PWM I/O Change  | —                          | —                                                     | 50  | ns    | _          |  |  |  |  |

| OC20         | TFLT               | Fault Input Pulse Width        | 50                         | —                                                     |     | ns    | —          |  |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

### TABLE 31-8:SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| АС СНА        | ARACTERIS | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature } -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |        |      |      |       |            |  |

|---------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|-------|------------|--|

| Param.<br>No. | Symbol    | Characteristics                                                                                                                                                                                                                                                                | Min.   | Тур. | Max. | Units | Conditions |  |

| MSP70         | TscL      | SCKx Input Low Time (Note 1,2)                                                                                                                                                                                                                                                 | Tsck/2 |      | _    | ns    | _          |  |

| MSP71         | TscH      | SCKx Input High Time (Note 1,2)                                                                                                                                                                                                                                                | Tsck/2 | —    |      | ns    | —          |  |

| MSP51         | TssH2doZ  | SSx ↑ to SDOx Output<br>High-Impedance <b>(Note 2)</b>                                                                                                                                                                                                                         | 5      |      | 25   | ns    | —          |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns.

## TABLE 31-9: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS