Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                 |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx150f128bt-v-so |

#### TABLE 14: PIN NAMES FOR 44-PIN USB DEVICES

44-PIN VTLA (TOP VIEW)(1,2,3,5)

PIC32MX210F016D PIC32MX220F032D PIC32MX230F064D PIC32MX230F256D PIC32MX250F128D PIC32MX270F256D

44

| Pin # | Full Pin Name                                    |

|-------|--------------------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                         |

| 2     | RPC6/PMA1/RC6                                    |

| 3     | RPC7/PMA0/RC7                                    |

| 4     | RPC8/PMA5/RC8                                    |

| 5     | RPC9/CTED7/PMA6/RC9                              |

| 6     | Vss                                              |

| 7     | VCAP                                             |

| 8     | PGED2/RPB10/D+/CTED11/RB10                       |

| 9     | PGEC2/RPB11/D-/RB11                              |

| 10    | Vusb3v3                                          |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10             |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7         |

| 14    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 16    | AVss                                             |

| 17    | AVDD                                             |

| 18    | MCLR                                             |

| 19    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 20    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       |

| Pin# | Full Pin Name                             |

|------|-------------------------------------------|

| 23   | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 24   | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 25   | AN6/RPC0/RC0                              |

| 26   | AN7/RPC1/RC1                              |

| 27   | AN8/RPC2/PMA2/RC2                         |

| 28   | VDD                                       |

| 29   | Vss                                       |

| 30   | OSC1/CLKI/RPA2/RA2                        |

| 31   | OSC2/CLKO/RPA3/RA3                        |

| 32   | TDO/RPA8/PMA8/RA8                         |

| 33   | SOSCI/RPB4/RB4                            |

| 34   | SOSCO/RPA4/T1CK/CTED9/RA4                 |

| 35   | TDI/RPA9/PMA9/RA9                         |

| 36   | AN12/RPC3/RC3                             |

| 37   | RPC4/PMA4/RC4                             |

| 38   | RPC5/PMA3/RC5                             |

| 39   | Vss                                       |

| 40   | VDD                                       |

| 41   | RPB5/USBID/RB5                            |

| 42   | VBUS                                      |

| 43   | RPB7/CTED3/PMD5/INT0/RB7                  |

| 44   | RPB8/SCL1/CTED10/PMD4/RB8                 |

#### Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3 "Peripheral Pin Select"** for restrictions.

- 2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: This pin function is not available on PIC32MX210F016D and PIC32MX220F032D devices.

- 5: Shaded pins are 5V tolerant.

#### REGISTER 4-4: BMXDUPBA: DATA RAM USER PROGRAM BASE ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | _                 | _                 | -                 | _                 |                   |                   | _                | _                |  |  |  |  |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | _                 | _                 | _                 | _                 | -                 | _                 | _                | _                |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |  |

| 15:8         |                   |                   |                   | BMXDU             | PBA<15:8>         |                   |                  |                  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          |                   | BMXDUPBA<7:0>     |                   |                   |                   |                   |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUPBA<15:10>: DRM User Program Base Address bits

When non-zero, the value selects the relative base address for User mode program space in RAM, BMXDUPBA must be greater than BMXDUDBA.

bit 9-0 **BMXDUPBA<9:0>:** Read-Only bits

This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

### 7.1 Interrupt Control Registers

### TABLE 7-2: INTERRUPT REGISTER MAP

| ess                         |                                 |               |        |        |        |            |                     |           |          | Bits    |        |          |          |                     |                      |        |        |        |               |

|-----------------------------|---------------------------------|---------------|--------|--------|--------|------------|---------------------|-----------|----------|---------|--------|----------|----------|---------------------|----------------------|--------|--------|--------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14  | 29/13  | 28/12      | 27/11               | 26/10     | 25/9     | 24/8    | 23/7   | 22/6     | 21/5     | 20/4                | 19/3                 | 18/2   | 17/1   | 16/0   | All<br>Resets |

| 1000                        | INTCON                          | 31:16         | _      | _      | _      | -          | _                   | _         | _        | _       | _      | _        | _        | _                   | _                    | _      | _      | _      | 0000          |

| 1000                        | IIIIOOII                        | 15:0          | _      | _      | _      | MVEC       | _                   |           | TPC<2:0> |         |        | _        | _        | INT4EP              | INT3EP               | INT2EP | INT1EP | INT0EP | 0000          |

| 1010                        | INTSTAT <sup>(3)</sup>          | 31:16         | _      | _      | _      | _          |                     |           |          | _       |        | _        | _        | _                   | _                    | _      | _      | _      | 0000          |

| 1010                        | INTOTAL                         | 15:0          | _      | _      | _      | _          | SRIPL<2:0> VEC<5:0> |           |          |         |        |          |          |                     | 0000                 |        |        |        |               |

| 1020                        | IPTMR                           | 31:16<br>15:0 |        |        |        |            |                     |           |          | IPTMR<3 | 1:0>   |          |          |                     |                      |        |        |        | 0000          |

|                             |                                 | 31:16         | FCEIF  | RTCCIF | FSCMIF | AD1IF      | OC5IF               | IC5IF     | IC5EIF   | T5IF    | INT4IF | OC4IF    | IC4IF    | IC4EIF              | T4IF                 | INT3IF | OC3IF  | IC3IF  | 0000          |

| 1030                        | IFS0                            | 15:0          | IC3EIF | T3IF   | INT2IF | OC2IF      | IC2IF               | IC2EIF    | T2IF     | INT1IF  | OC1IF  | IC1IF    | IC1EIF   | T1IF                | INTOIF               | CS1IF  | CS0IF  | CTIF   | 0000          |

|                             |                                 | 31:16         | DMA3IF | DMA2IF | DMA1IF | DMA0IF     | CTMUIF              | I2C2MIF   | I2C2SIF  | I2C2BIF | U2TXIF | U2RXIF   | U2EIF    | SPI2TXIF            | SPI2RXIF             |        | PMPEIF | PMPIF  | 0000          |

| 1040                        | IFS1                            | 15:0          | CNCIF  | CNBIF  | CNAIF  | I2C1MIF    | I2C1SIF             | I2C2IVIIF | U1TXIF   | U1RXIF  | U1EIF  | SPI1TXIF | SPI1RXIF | SPI2TXIF<br>SPI1EIF | USBIF <sup>(2)</sup> | CMP3IF | CMP2IF | CMP1IF | 0000          |

|                             |                                 | 31:16         | FCEIE  | RTCCIE | FSCMIE | AD1IE      | OC5IE               | IC5IE     | IC5EIE   | T5IE    | INT4IE | OC4IE    | IC4IE    | IC4EIE              | T4IE                 | INT3IE | OC3IE  | IC3IE  | 0000          |

| 1060                        | IEC0                            | 15:0          | IC3EIE | T3IE   | INT2IE | OC2IE      | IC2IE               | IC2EIE    | T2IE     | INT1IE  | OC1IE  | IC1IE    | IC1EIE   | T1IE                | INTOIE               | CS1IE  | CS0IE  | CTIE   | 0000          |

|                             |                                 | 31:16         | DMA3IE | DMA2IE | DMA1IE | DMA0IE     | CTMUIE              | I2C2MIE   | I2C2SIE  | I2C2BIE | U2TXIE | U2RXIE   | U2EIE    | SPI2TXIE            | SPI2RXIE             |        | PMPEIE | PMPIE  | 0000          |

| 1070                        | IEC1                            | 15:0          | CNCIE  | CNBIE  | CNAIE  | I2C1MIE    | I2C1SIE             | I2C1BIE   | U1TXIE   | U1RXIE  | U1EIE  | SPI1TXIE | SPI1RXIE | SPI1EIE             | USBIE <sup>(2)</sup> | CMP3IE |        |        |               |

|                             |                                 | 31:16         | _      | _      | _      |            | INT0IP<2:0>         |           | INTOIS   |         | _      | _        | _        |                     | S1IP<2:0>            | 1      | CS1IS  | l      | 0000          |

| 1090                        | IPC0                            | 15:0          | _      | _      | _      |            | CS0IP<2:0>          |           | CS0IS    |         | _      | _        | _        |                     | CTIP<2:0>            |        |        | <1:0>  | 0000          |

|                             |                                 | 31:16         | _      | _      | _      |            | INT1IP<2:0>         |           | INT1IS   | <1:0>   |        | _        | _        | С                   | C1IP<2:0>            |        | OC1IS  | S<1:0> | 0000          |

| 10A0                        | IPC1                            | 15:0          | _      | _      | _      |            | IC1IP<2:0>          |           | IC1IS•   | <1:0>   | _      | _        | _        |                     | T1IP<2:0>            |        | T1IS-  | <1:0>  | 0000          |

|                             |                                 | 31:16         | -      | _      | _      |            | INT2IP<2:0>         |           | INT2IS   | <1:0>   | -      | _        | -        | С                   | C2IP<2:0>            |        | OC2IS  | S<1:0> | 0000          |

| 10B0                        | IPC2                            | 15:0          | _      | _      | _      |            | IC2IP<2:0>          |           | IC2IS•   | <1:0>   | _      | _        | _        |                     | T2IP<2:0>            |        | T2IS-  | <1:0>  | 0000          |

| 1000                        | IDOS                            | 31:16         | _      | _      | _      |            | INT3IP<2:0>         |           | INT3IS   | <1:0>   | _      | _        | _        | C                   | C3IP<2:0>            |        | OC3IS  | S<1:0> | 0000          |

| 10C0                        | IPC3                            | 15:0          | _      | _      | _      |            | IC3IP<2:0>          |           | IC3IS    | <1:0>   |        | _        | _        |                     | T3IP<2:0>            |        | T3IS-  | <1:0>  | 0000          |

| 4000                        | IPC4                            | 31:16         | _      | _      | _      |            | INT4IP<2:0>         |           | INT4IS   | <1:0>   |        | _        | _        | С                   | C4IP<2:0>            |        | OC4IS  | S<1:0> | 0000          |

| 10D0                        | IPC4                            | 15:0          | _      | _      | _      |            | IC4IP<2:0>          |           | IC4IS•   | <1:0>   |        | _        | _        | T4IP<2:0>           |                      | T4IS   | <1:0>  | 0000   |               |

| 10E0                        | IPC5                            | 31:16         | _      | _      | _      | AD1IP<2:0> |                     |           | AD1IS    | <1:0>   | _      | _        | _        | C                   | C5IP<2:0>            |        | OC5IS  | S<1:0> | 0000          |

| 10E0                        | IPC5                            | 15:0          | -      |        | _      | IC5IP<2:0> |                     |           | IC5IS•   | <1:0>   | 1      | _        | 1        | -                   | T5IP<2:0>            |        | T5IS-  | <1:0>  | 0000          |

| 10F0                        | IPC6                            | 31:16         | _      | _      | _      | (          | CMP1IP<2:0>         |           |          | S<1:0>  | _      | _        | _        | F                   | CEIP<2:0>            |        | FCEIS  | S<1:0> | 0000          |

| 1050                        | IFCO                            | 15:0          | _      |        | _      | F          | RTCCIP<2:0>         | •         | RTCCIS   | S<1:0>  | -      | _        | _        | FS                  | SCMIP<2:0            | >      | FSCMI  | S<1:0> | 0000          |

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

<sup>2:</sup> These bits are not available on PIC32MX1XX devices.

<sup>3:</sup> This register does not have associated CLR, SET, INV registers.

### REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

bit 3-0 ROSEL<3:0>: Reference Clock Source Select bits<sup>(1)</sup>

```

1111 = Reserved; do not use

```

•

•

1001 = Reserved; do not use

1000 = REFCLKI

0111 = System PLL output

0110 = USB PLL output

0101 = Sosc

0100 = LPRC

0011 **= FRC**

0010 = Posc

0001 = PBCLK

0000 = SYSCLK

- Note 1: The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- 2: This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

| <b>TABLE 9-3:</b> | DMA CHANNE | -I S 0-3 | REGISTER | MAP |

|-------------------|------------|----------|----------|-----|

|                   |            |          |          |     |

| ess                         |                                 | 0             |                                                                                       |             |       |       |             |       |      | Ві     | its     |         |        |                 |                  |          |        |        | "            |

|-----------------------------|---------------------------------|---------------|---------------------------------------------------------------------------------------|-------------|-------|-------|-------------|-------|------|--------|---------|---------|--------|-----------------|------------------|----------|--------|--------|--------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15                                                                                 | 30/14       | 29/13 | 28/12 | 27/11       | 26/10 | 25/9 | 24/8   | 23/7    | 22/6    | 21/5   | 20/4            | 19/3             | 18/2     | 17/1   | 16/0   | All Resets   |

| 3060                        | DCH0CON                         | 31:16         | _                                                                                     | _           | _     | 1     | ı           | ı     | _    | _      | _       | _       | _      | 1               | _                | _        | _      | _      | 0000         |

| 3060                        | DCHUCON                         | 15:0          | CHBUSY                                                                                | _           | _     | _     | _           | _     | _    | CHCHNS | CHEN    | CHAED   | CHCHN  | CHAEN           | _                | CHEDET   | CHPR   | l<1:0> | 0000         |

| 3070                        | DCH0ECON                        | 31:16         | _                                                                                     | _           | _     | _     | _           | _     | _    | _      |         |         |        | CHAIR           |                  |          |        |        | 00FF         |

|                             |                                 | 15:0          |                                                                                       |             |       | CHSIR | Q<7:0>      |       | 1    |        | CFORCE  | CABORT  | PATEN  | SIRQEN          | AIRQEN           | _        | _      | _      | FF00         |

| 3080                        | DCH0INT                         | 31:16         | _                                                                                     |             | _     | _     | _           | _     | _    | _      | CHSDIE  | CHSHIE  | CHDDIE | CHDHIE          | CHBCIE           | CHCCIE   | CHTAIE | CHERIE | 0000         |

|                             |                                 | 15:0          | _                                                                                     |             |       |       |             |       |      |        |         |         |        |                 | 0000             |          |        |        |              |

| 3090                        | DCH0SSA                         | 31:16<br>15:0 |                                                                                       |             |       |       |             |       |      | CHSSA  | <31:0>  |         |        |                 |                  |          |        |        | 0000         |

|                             |                                 | 31:16         |                                                                                       | 0000        |       |       |             |       |      |        |         |         |        |                 |                  |          |        |        |              |

| 30A0                        | DCH0DSA                         | 15:0          |                                                                                       | CHDSA<31:0> |       |       |             |       |      |        |         |         |        |                 |                  |          |        |        |              |

|                             |                                 | 31:16         | _                                                                                     | _           | _     | _     | _           | _     | _    | _      | _       | _       | _      | _               | _                | _        | _      | _      | 0000         |

| 30B0                        | DCH0SSIZ                        | 15:0          |                                                                                       |             |       |       |             |       |      | CHSSIZ | Z<15:0> |         |        |                 |                  |          |        |        | 0000         |

|                             |                                 | 31:16         | _                                                                                     | _           | _     | _     | _           | _     | _    | _      | _       | _       | _      | _               | _                | _        | _      | _      | 0000         |

| 30C0                        | DCH0DSIZ                        | 15:0          |                                                                                       |             |       |       |             |       |      | CHDSIZ | Z<15:0> |         |        |                 |                  |          |        |        | 0000         |

| 0000                        | DOLLOODED                       | 31:16         | _                                                                                     | _           | _     | _     | _           | _     | _    | _      | _       | _       | _      | _               | _                | _        | _      | _      | 0000         |

| 3000                        | DCH0SPTR                        | 15:0          | •                                                                                     |             |       |       |             |       | •    | CHSPTI | R<15:0> | •       | •      |                 | •                |          | •      | •      | 0000         |

| 30E0                        | DCH0DPTR                        | 31:16         | _                                                                                     | _           | _     | _     | _           | _     | _    | _      | _       | _       | _      | _               | _                | _        | _      | _      | 0000         |

| 30E0                        | DCHUDFIK                        | 15:0          |                                                                                       |             |       |       |             |       |      | CHDPT  | R<15:0> |         |        |                 |                  |          |        |        | 0000         |

| 30F0                        | DCH0CSIZ                        | 31:16         | _                                                                                     |             | _     | _     | _           | _     | _    | _      | _       | _       | _      | _               | _                | _        | _      | _      | 0000         |

| 001 0                       | DOI 100012                      | 15:0          |                                                                                       |             |       |       |             |       |      | CHCSIZ | Z<15:0> |         |        |                 |                  |          |        |        | 0000         |

| 3100                        | DCH0CPTR                        | 31:16         | _                                                                                     | _           | _     | _     | _           | _     | _    | _      | _       | _       | _      | _               | _                | _        | _      | _      | 0000         |

|                             |                                 | 15:0          |                                                                                       |             |       |       |             |       |      | CHCPT  | R<15:0> |         |        |                 |                  |          |        |        | 0000         |

| 3110                        | DCH0DAT                         | 31:16         | _                                                                                     |             | _     | _     | _           | _     | _    | _      | _       | _       | _      |                 |                  | _        | _      | _      | 0000         |

|                             |                                 | 15:0          | _                                                                                     |             | _     |       |             |       | _    | _      |         |         |        | CHPDA           |                  |          |        |        | 0000         |

| 3120                        | DCH1CON                         | 31:16         | —<br>—                                                                                |             | _     | _     | _           |       | _    | -      | - CLIEN | - CHAFD | -      | - CLIATNI       | _                | - CHEDET |        | -      | 0000         |

|                             |                                 | 15:0          | CHBUSY                                                                                |             | _     | _     | _           | _     | _    | CHCHNS | CHEN    | CHAED   | CHCHN  | CHAEN           | —<br>O 47:05     | CHEDET   | CHPR   | 1<1:0> | 0000         |

| 3130                        | DCH1ECON                        | 31:16<br>15:0 | _                                                                                     |             | _     | CHSIR | —<br>O<7:0> | _     | _    | _      | CFORCE  | CABORT  | PATEN  | CHAIR<br>SIRQEN | Q<7:0><br>AIRQEN | _        |        |        | 00FF<br>FF00 |

|                             |                                 | 31:16         | _                                                                                     |             | _     | CHOIR | Q~1.U~      |       |      | _      | CHSDIE  | CHSHIE  | CHDDIE | CHDHIE          | CHBCIE           | CHCCIE   | CHTAIE | CHERIE | 0000         |

| 3140                        | DCH1INT                         | 15:0          | _                                                                                     |             |       |       |             |       |      |        | CHSDIF  | CHSHIF  | CHDDIF | CHDHIF          | CHBCIE           | CHCCIE   | CHTAIL | CHERIF | 0000         |

|                             |                                 | 31:16         | 000                                                                                   |             |       |       |             |       |      |        |         |         |        |                 | 0000             |          |        |        |              |

| 3150                        | DCH1SSA                         | 15:0          | CHSSA<31:0>                                                                           |             |       |       |             |       |      |        |         |         |        | 0000            |                  |          |        |        |              |

| <u> </u>                    |                                 | 31:16         |                                                                                       |             |       |       |             |       |      |        |         |         |        |                 |                  |          |        |        | 0000         |

| 3160                        | DCH1DSA                         | 15:0          |                                                                                       |             |       |       |             |       |      | CHDSA  | \<31:0> |         |        |                 |                  |          |        |        | 0000         |

| Legen                       |                                 |               | value on Reset: — = unimplemented, read as '0'. Reset values are shown in heyadecimal |             |       |       |             |       |      |        |         |         |        |                 |                  |          |        |        |              |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### REGISTER 9-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | -                 | _                 | _                 | _                | _                |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | CHSDIE            | CHSHIE            | CHDDIE            | CHDHIE            | CHBCIE            | CHCCIE            | CHTAIE           | CHERIE           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CHSDIF            | CHSHIF            | CHDDIF            | CHDHIF            | CHBCIF            | CHCCIF            | CHTAIF           | CHERIF           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-24 Unimplemented: Read as '0'

bit 23 CHSDIE: Channel Source Done Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 22 CHSHIE: Channel Source Half Empty Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 21 CHDDIE: Channel Destination Done Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 20 **CHDHIE:** Channel Destination Half Full Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 19 CHBCIE: Channel Block Transfer Complete Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 18 CHCCIE: Channel Cell Transfer Complete Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 17 CHTAIE: Channel Transfer Abort Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 16 CHERIE: Channel Address Error Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 15-8 Unimplemented: Read as '0'

bit 7 CHSDIF: Channel Source Done Interrupt Flag bit

1 = Channel Source Pointer has reached end of source (CHSPTR = CHSSIZ)

0 = No interrupt is pending

bit 6 CHSHIF: Channel Source Half Empty Interrupt Flag bit

1 = Channel Source Pointer has reached midpoint of source (CHSPTR = CHSSIZ/2)

0 = No interrupt is pending

bit 5 CHDDIF: Channel Destination Done Interrupt Flag bit

1 = Channel Destination Pointer has reached end of destination (CHDPTR = CHDSIZ)

0 = No interrupt is pending

#### REGISTER 10-4: U10TGCON: USB OTG CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | -                 | _                 | -                 | _                 | _                 | -                | _                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | DPPULUP           | DMPULUP           | DPPULDWN          | DMPULDWN          | VBUSON            | OTGEN             | VBUSCHG          | VBUSDIS          |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 **DPPULUP:** D+ Pull-Up Enable bit

1 = D+ data line pull-up resistor is enabled

0 = D+ data line pull-up resistor is disabled

bit 6 DMPULUP: D- Pull-Up Enable bit

1 = D- data line pull-up resistor is enabled

0 = D- data line pull-up resistor is disabled

bit 5 **DPPULDWN:** D+ Pull-Down Enable bit

1 = D+ data line pull-down resistor is enabled

0 = D+ data line pull-down resistor is disabled

bit 4 DMPULDWN: D- Pull-Down Enable bit

1 = D- data line pull-down resistor is enabled

0 = D- data line pull-down resistor is disabled

bit 3 VBUSON: VBUS Power-on bit

1 = VBUS line is powered

0 = VBUS line is not powered

bit 2 OTGEN: OTG Functionality Enable bit

1 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under software control

0 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under USB hardware control

bit 1 VBUSCHG: VBUS Charge Enable bit

1 = VBUS line is charged through a pull-up resistor

0 = VBUS line is not charged through a resistor

bit 0 VBUSDIS: VBUS Discharge Enable bit

1 = VBUS line is discharged through a pull-down resistor

0 = VBUS line is not discharged through a resistor

#### REGISTER 10-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|

| 24.24        | U-0                   | U-0              |

| 31:24        |                   | _                 | _                 | _                 | _                 | _                 | _                     | _                |

| 23:16        | U-0                   | U-0              |

| 23.10        |                   | _                 | _                 | _                 | _                 | -                 | _                     | _                |

| 15:8         | U-0                   | U-0              |

| 15.6         |                   | _                 | _                 | _                 | _                 | _                 | _                     | _                |

|              | R/W-0                 | R/W-0            |

| 7:0          | BTSEE             | BTSEE BMXEE       |                   | BTOEE             | DFN8EE            | CRC16EE           | CRC5EE <sup>(1)</sup> | PIDEE            |

|              | DISEL             | DIVINEE           | DMAEE             | DIOEE             | DINOEE            | ONO IDEE          | EOFEE <sup>(2)</sup>  | IIDEE            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 BTSEE: Bit Stuff Error Interrupt Enable bit

1 = BTSEF interrupt is enabled0 = BTSEF interrupt is disabled

bit 6 BMXEE: Bus Matrix Error Interrupt Enable bit

1 = BMXEF interrupt is enabled0 = BMXEF interrupt is disabled

bit 5 DMAEE: DMA Error Interrupt Enable bit

1 = DMAEF interrupt is enabled0 = DMAEF interrupt is disabled

bit 4 BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit

1 = BTOEF interrupt is enabled0 = BTOEF interrupt is disabled

bit 3 DFN8EE: Data Field Size Error Interrupt Enable bit

1 = DFN8EF interrupt is enabled0 = DFN8EF interrupt is disabled

bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

1 = CRC16EF interrupt is enabled0 = CRC16EF interrupt is disabled

bit 1 CRC5EE: CRC5 Host Error Interrupt Enable bit(1)

1 = CRC5EF interrupt is enabled 0 = CRC5EF interrupt is disabled

**EOFEE:** EOF Error Interrupt Enable bit<sup>(2)</sup>

1 = EOF interrupt is enabled0 = EOF interrupt is disabled

bit 0 PIDEE: PID Check Failure Interrupt Enable bit

1 = PIDEF interrupt is enabled0 = PIDEF interrupt is disabled

Note 1: Device mode.

2: Host mode.

Note: For an interrupt to propagate the USBIF register, the UERRIE (U1IE<1>) bit must be set.

### TABLE 11-7: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| ss                          |                                                 |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |      |       |      |            |

|-----------------------------|-------------------------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|-------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name                                | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0 | All Resets |

| ED00                        | RPC8R <sup>(1)</sup>                            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _     | _    | 0000       |

| FB8C                        | RPC8R**                                         | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPC8 | <3:0> |      | 0000       |

| ED00                        | RPC9R <sup>(3)</sup>                            | 31:16     | _     | _     | _     | -     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _     | _    | 0000       |

| FB90                        | 90 RPC9R*7 15:0 — — — — — — — — — — — RPC9<3:0> |           |       |       |       |       |       | 0000  |      |      |      |      |      |      |      |      |       |      |            |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1:

This register is only available on 44-pin devices. This register is only available on PIC32MX1XX devices. 2:

This register is only available on 36-pin and 44-pin devices.

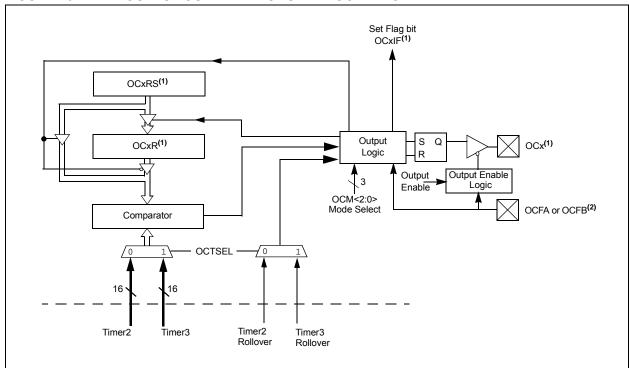

#### 16.0 OUTPUT COMPARE

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 16. "Output Compare"** (DS60001111), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Output Compare module is used to generate a single pulse or a train of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation.

The following are some of the key features:

- · Multiple Output Compare Modules in a device

- Programmable interrupt generation on compare event

- · Single and Dual Compare modes

- · Single and continuous output pulse generation

- · Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

#### FIGURE 16-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

- **Note 1:** Where 'x' is shown, reference is made to the registers associated with the respective output compare channels, 1 through 5.

- 2: The OCFA pin controls the OC1-OC4 channels. The OCFB pin controls the OC5 channel.

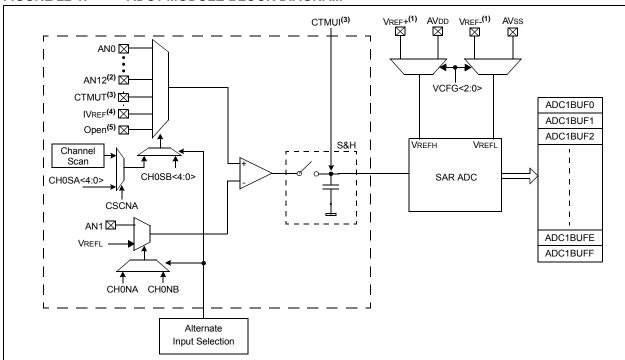

# 22.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- · Up to 1 Msps conversion speed

- · Up to 13 analog input pins

- · External voltage reference input pins

- One unipolar, differential Sample and Hold Amplifier (SHA)

- · Automatic Channel Scan mode

- Selectable conversion trigger source

- · 16-word conversion result buffer

- · Selectable buffer fill modes

- Eight conversion result format options

- · Operation during Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 22-1. Figure 22-2 illustrates a block diagram of the ADC conversion clock period. The 10-bit ADC has up to 13 analog input pins, designated AN0-AN12. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

#### FIGURE 22-1: ADC1 MODULE BLOCK DIAGRAM

- Note 1: VREF+ and VREF- inputs can be multiplexed with other analog inputs.

- 2: AN8 is only available on 44-pin devices. AN6, AN7, and AN12 are not available on 28-pin devices.

- 3: Connected to the CTMU module. See Section 25.0 "Charge Time Measurement Unit (CTMU)" for more information.

- 4: Internal precision voltage reference (1.2V).

- 5: This selection is only used with CTMU capacitive and time measurement.

#### REGISTER 22-5: AD1CSSL: ADC INPUT SCAN SELECT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 |                   |                   | _                | _                |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | _                 | _                 | -                 | _                 | -                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | CSSL15            | CSSL14            | CSSL13            | CSSL12            | CSSL11            | CSSL10            | CSSL9            | CSSL8            |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CSSL7             | CSSL6             | CSSL5             | CSSL4             | CSSL3             | CSSL2             | CSSL1            | CSSL0            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CSSL<15:0>: ADC Input Pin Scan Selection bits<sup>(1,2)</sup>

1 = Select ANx for input scan0 = Skip ANx for input scan

**Note 1:** CSSL = ANx, where 'x' = 0-12; CSSL13 selects CTMU input for scan; CSSL14 selects IVREF for scan; CSSL15 selects VSS for scan.

2: On devices with less than 13 analog inputs, all CSSLx bits can be selected; however, inputs selected for scan without a corresponding input on the device will convert to VREFL.

#### 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB® X IDE Software

- · Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>TM</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- · In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- · Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- · Third-party development tools

# 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users

#### Feature-Rich Editor:

- · Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

Project-Based Workspaces:

- · Multiple projects

- · Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- · Built-in support for Bugzilla issue tracker

#### 30.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MX1XX/2XX 28/36/44-pin Family electrical characteristics for devices that operate at 40 MHz. Refer to **Section 31.0** "50 **MHz Electrical Characteristics**" for additional specifications for operations at higher frequency. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC32MX1XX/2XX 28/36/44-pin Family devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

### **Absolute Maximum Ratings**

#### (See Note 1)

| Ambient temperature under bias                                                  | 40°C to +105°C           |

|---------------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                             | 65°C to +150°C           |

| Voltage on VDD with respect to Vss                                              | 0.3V to +4.0V            |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)        | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 2.3V$ (Note 3) | 0.3V to +5.5V            |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3)     | 0.3V to +3.6V            |

| Voltage on D+ or D- pin with respect to Vusb3v3                                 | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                             | 0.3V to +5.5V            |

| Maximum current out of Vss pin(s)                                               | 300 mA                   |

| Maximum current into VDD pin(s) (Note 2)                                        | 300 mA                   |

| Maximum output current sunk by any I/O pin                                      | 15 mA                    |

| Maximum output current sourced by any I/O pin                                   | 15 mA                    |

| Maximum current sunk by all ports                                               | 200 mA                   |

| Maximum current sourced by all ports (Note 2)                                   | 200 mA                   |

- Note 1: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

**TABLE 30-17: EXTERNAL CLOCK TIMING REQUIREMENTS**

| AC CHARACTERISTICS |               |                                                                                                                  | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                        |             |            |                                         |  |  |  |

|--------------------|---------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------|------------|-----------------------------------------|--|--|--|

| Param.<br>No.      | Symbol        | Characteristics                                                                                                  | Min.                                                                                                                                                                                                                                           | Typical <sup>(1)</sup> | Max.        | Units      | Conditions                              |  |  |  |

| OS10               | Fosc          | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes)                               | DC<br>4                                                                                                                                                                                                                                        | _                      | 40<br>40    | MHz<br>MHz | EC (Note 4)<br>ECPLL (Note 3)           |  |  |  |

| OS11               |               | Oscillator Crystal Frequency                                                                                     | 3                                                                                                                                                                                                                                              | _                      | 10          | MHz        | XT (Note 4)                             |  |  |  |

| OS12               |               |                                                                                                                  | 4                                                                                                                                                                                                                                              | _                      | 10          | MHz        | XTPLL<br>(Notes 3,4)                    |  |  |  |

| OS13               | 1             |                                                                                                                  | 10                                                                                                                                                                                                                                             | _                      | 25          | MHz        | HS (Note 5)                             |  |  |  |

| OS14               |               |                                                                                                                  | 10                                                                                                                                                                                                                                             | _                      | 25          | MHz        | HSPLL<br>(Notes 3,4)                    |  |  |  |

| OS15               |               |                                                                                                                  | 32                                                                                                                                                                                                                                             | 32.768                 | 100         | kHz        | Sosc (Note 4)                           |  |  |  |

| OS20               | Tosc          | Tosc = 1/Fosc = Tcy (Note 2)                                                                                     | _                                                                                                                                                                                                                                              | _                      | _           | _          | See parameter<br>OS10 for Fosc<br>value |  |  |  |

| OS30               | TosL,<br>TosH | External Clock In (OSC1)<br>High or Low Time                                                                     | 0.45 x Tosc                                                                                                                                                                                                                                    | _                      | _           | ns         | EC (Note 4)                             |  |  |  |

| OS31               | TosR,<br>TosF | External Clock In (OSC1) Rise or Fall Time                                                                       | _                                                                                                                                                                                                                                              | _                      | 0.05 x Tosc | ns         | EC (Note 4)                             |  |  |  |

| OS40               | Tost          | Oscillator Start-up Timer Period<br>(Only applies to HS, HSPLL,<br>XT, XTPLL and Sosc Clock<br>Oscillator modes) | _                                                                                                                                                                                                                                              | 1024                   | _           | Tosc       | (Note 4)                                |  |  |  |

| OS41               | TFSCM         | Primary Clock Fail Safe<br>Time-out Period                                                                       | _                                                                                                                                                                                                                                              | 2                      | _           | ms         | (Note 4)                                |  |  |  |

| OS42               | Gм            | External Oscillator<br>Transconductance (Primary<br>Oscillator only)                                             | _                                                                                                                                                                                                                                              | 12                     | _           | mA/V       | VDD = 3.3V,<br>TA = +25°C<br>(Note 4)   |  |  |  |

- Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are characterized but are not tested.

- 2: Instruction cycle period (TCY) equals the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin.

- 3: PLL input requirements:  $4 \text{ MHz} \le \text{FPLLIN} \le 5 \text{ MHz}$  (use PLL prescaler to reduce Fosc). This parameter is characterized, but tested at 10 MHz only at manufacturing.

- 4: This parameter is characterized, but not tested in manufacturing.

#### **TABLE 30-18: PLL CLOCK TIMING SPECIFICATIONS**

AC CHARACTERISTICS Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature  $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$  for Industrial  $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$  for V-temp

| Param.<br>No. | Symbol | Characteristics <sup>(1)</sup>                                      | Min.  | Typical | Max.  | Units | Conditions                        |

|---------------|--------|---------------------------------------------------------------------|-------|---------|-------|-------|-----------------------------------|

| OS50          | FPLLI  | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range | 3.92  | _       | 5     | MHz   | ECPLL, HSPLL, XTPLL, FRCPLL modes |

| OS51          | Fsys   | On-Chip VCO System Frequency                                        | 60    | _       | 120   | MHz   | _                                 |

| OS52          | TLOCK  | PLL Start-up Time (Lock Time)                                       | _     | _       | 2     | ms    | _                                 |

| OS53          | DCLK   | CLKO Stability <sup>(2)</sup><br>(Period Jitter or Cumulative)      | -0.25 | _       | +0.25 | %     | Measured over 100 ms period       |

- Note 1: These parameters are characterized, but not tested in manufacturing.

- **2:** This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

$$Effective Jitter = \frac{D_{CLK}}{\sqrt{\frac{SYSCLK}{CommunicationClock}}}$$

For example, if SYSCLK = 40 MHz and SPI bit rate = 20 MHz, the effective jitter is as follows:

$$Effective Jitter = \frac{D_{CLK}}{\sqrt{\frac{40}{20}}} = \frac{D_{CLK}}{1.41}$$

#### **TABLE 30-19: INTERNAL FRC ACCURACY**

|                                                 |                 | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C \text{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \text{ for V-temp}$ |         |      |       |            |  |  |  |

|-------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|--|--|

| Param.<br>No.                                   | Characteristics | Min.                                                                                                                                                                                                                      | Typical | Max. | Units | Conditions |  |  |  |

| Internal FRC Accuracy @ 8.00 MHz <sup>(1)</sup> |                 |                                                                                                                                                                                                                           |         |      |       |            |  |  |  |

| F20b                                            | FRC             | -0.9                                                                                                                                                                                                                      | _       | +0.9 | %     | _          |  |  |  |

**Note 1:** Frequency calibrated at 25°C and 3.3V. The TUN bits can be used to compensate for temperature drift.

#### **TABLE 30-20: INTERNAL LPRC ACCURACY**

| AC CHA                          | RACTERISTICS | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |         |      |       |            |  |  |  |

|---------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|--|--|

| Param. No. Characteristics      |              | Min.                                                                                                                                                                                                 | Typical | Max. | Units | Conditions |  |  |  |

| LPRC @ 31.25 kHz <sup>(1)</sup> |              |                                                                                                                                                                                                      |         |      |       |            |  |  |  |

| F21                             | LPRC         | -15                                                                                                                                                                                                  | _       | +15  | %     | _          |  |  |  |

Note 1: Change of LPRC frequency as VDD changes.

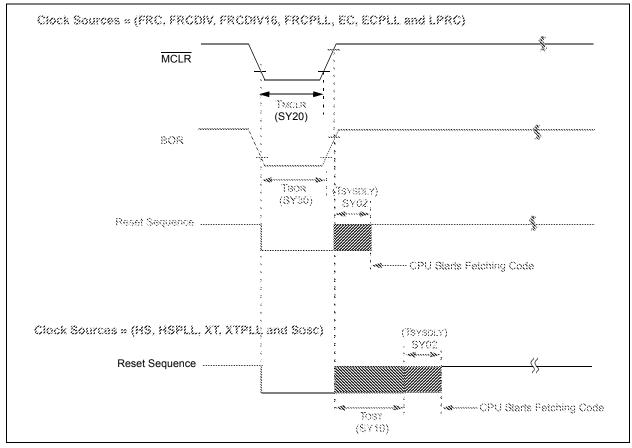

FIGURE 30-5: EXTERNAL RESET TIMING CHARACTERISTICS

**TABLE 30-22: RESETS TIMING**

| AC CHA        | RACTERI | STICS                                                                                                                          | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                              |     |    |   |  |

|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----|----|---|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>                                                                                                 | Min. Typical <sup>(2)</sup> Max. Units Conditions                                                                                                                                                                                              |                              |     |    |   |  |

| SY00          | TPU     | Power-up Period<br>Internal Voltage Regulator Enabled                                                                          | _                                                                                                                                                                                                                                              | 400                          | 600 | μS | _ |  |

| SY02          | TSYSDLY | System Delay Period: Time Required to Reload Device Configuration Fuses plus SYSCLK Delay before First instruction is Fetched. | _                                                                                                                                                                                                                                              | 1 μs +<br>8 SYSCLK<br>cycles | l   | _  |   |  |

| SY20          | TMCLR   | MCLR Pulse Width (low)                                                                                                         | 2                                                                                                                                                                                                                                              | _                            | _   | μS | _ |  |

| SY30          | TBOR    | BOR Pulse Width (low)                                                                                                          | _                                                                                                                                                                                                                                              | 1                            | _   | μS |   |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

<sup>2:</sup> Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Characterized by design but not tested.

NOTES:

#### 33.0 PACKAGING INFORMATION

### 33.1 Package Marking Information

28-Lead SOIC

### Example

28-Lead SPDIP

#### Example

28-Lead SSOP

#### Example

28-Lead QFN

#### Example

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

B Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (B)

can be found on the outer packaging for this package.

**Note:** If the full Microchip part number cannot be marked on one line, it is carried over to the next line, thus limiting the number of available characters for customer-specific information.

#### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- · Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support