#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuns                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 28-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx150f128bt-v-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

#### 6.1 Reset Control Registers

### TABLE 6-1: RESET CONTROL REGISTER MAP

| ess                         |                                 | 0         |       | Bits  |       |       |       |       |      |       |      |      |      |      |       |      |      |       | s         |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|-------|------|------|------|------|-------|------|------|-------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7 | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1 | 16/0  | All Reset |

| F600                        | RCON                            | 31:16     | _     | _     | _     |       | —     | _     |      | —     | _    | _    |      | _    |       | -    | -    | _     | 0000      |

| 1 000                       | ROOM                            | 15:0      | _     |       | -     |       | _     | -     | CMR  | VREGS | EXTR | SWR  |      | WDTO | SLEEP | IDLE | BOR  | POR   | xxxx(2)   |

| E610                        | RSWRST                          | 31:16     |       | —     | -     | —     | —     | —     | —    | —     |      | —    | —    | _    | —     | _    | —    | —     | 0000      |

| 1010                        | N31/K31                         | 15:0      | _     | _     | _     | -     | _     | —     |      | —     | _    | _    | -    | _    | _     | _    | -    | SWRST | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| 24.04        | U-0                | U-0                |

| 31:24        | _                 | _                 | _                 | _                 | _                 |                   | -                  | —                  |

| 22:16        | U-0                | U-0                |

| 23:16        | _                 | _                 | _                 | _                 | _                 |                   | -                  | —                  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS          | R/W-0              |

| 15:8         |                   | _                 | _                 | -                 | _                 | _                 | CMR                | VREGS              |

| 7.0          | R/W-0, HS         | R/W-0, HS         | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-1, HS          | R/W-1, HS          |

| 7:0          | EXTR              | SWR               | _                 | WDTO              | SLEEP             | IDLE              | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |

#### REGISTER 6-1: RCON: RESET CONTROL REGISTER

| Legend:           | HS = Set by hardware |                           |                    |

|-------------------|----------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-10 Unimplemented: Read as '0'

| bit 9 | CMR: Configuration Mismatch Reset Flag bit             |

|-------|--------------------------------------------------------|

|       | 1 = Configuration mismatch Reset has occurred          |

|       | 0 = Configuration mismatch Reset has not occurred      |

| bit 8 | VREGS: Voltage Regulator Standby Enable bit            |

|       | 1 = Regulator is enabled and is on during Sleep mode   |

|       | 0 = Regulator is disabled and is off during Sleep mode |

| bit 7 | EXTR: External Reset (MCLR) Pin Flag bit               |

|       | 1 = Master Clear (pin) Reset has occurred              |

|       | 0 = Master Clear (pin) Reset has not occurred          |

| bit 6 | SWR: Software Reset Flag bit                           |

|       | 1 = Software Reset was executed                        |

|       | 0 = Software Reset as not executed                     |

| bit 5 | Unimplemented: Read as '0'                             |

| bit 4 | WDTO: Watchdog Timer Time-out Flag bit                 |

|       | 1 = WDT Time-out has occurred                          |

|       | 0 = WDT Time-out has not occurred                      |

| bit 3 | SLEEP: Wake From Sleep Flag bit                        |

|       | 1 = Device was in Sleep mode                           |

|       | 0 = Device was not in Sleep mode                       |

| bit 2 | IDLE: Wake From Idle Flag bit                          |

|       | 1 = Device was in Idle mode                            |

|       | 0 = Device was not in Idle mode                        |

| bit 1 | BOR: Brown-out Reset Flag bit <sup>(1)</sup>           |

|       | 1 = Brown-out Reset has occurred                       |

|       | 0 = Brown-out Reset has not occurred                   |

| bit 0 | POR: Power-on Reset Flag bit <sup>(1)</sup>            |

|       | 1 = Power-on Reset has occurred                        |

|       | 0 = Power-on Reset has not occurred                    |

|       |                                                        |

**Note 1:** User software must clear this bit to view next detection.

#### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| bit 3   | CF: Clock Fail Detect bit                                                                                                                                      |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = FSCM has detected a clock failure                                                                                                                          |

|         | 0 = No clock failure has been detected                                                                                                                         |

| bit 2   | UFRCEN: USB FRC Clock Enable bit <sup>(1)</sup>                                                                                                                |

|         | <ul> <li>1 = Enable the FRC as the clock source for the USB clock source</li> <li>0 = Use the Primary Oscillator or USB PLL as the USB clock source</li> </ul> |

| bit 1   | SOSCEN: Secondary Oscillator (Sosc) Enable bit                                                                                                                 |

|         | 1 = Enable the Secondary Oscillator                                                                                                                            |

|         | 0 = Disable the Secondary Oscillator                                                                                                                           |

| bit 0   | OSWEN: Oscillator Switch Enable bit                                                                                                                            |

|         | <ul> <li>1 = Initiate an oscillator switch to selection specified by NOSC&lt;2:0&gt; bits</li> <li>0 = Oscillator switch is complete</li> </ul>                |

| Note 1: | This bit is only available on PIC32MX2XX devices.                                                                                                              |

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

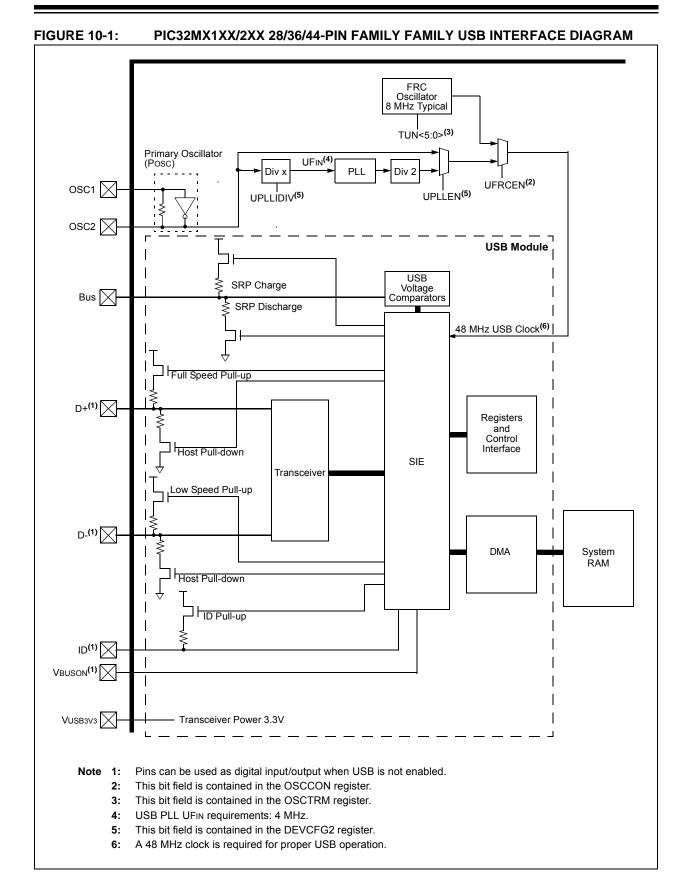

### 10.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 Full-Speed and Low-Speed embedded host, Full-Speed device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 10-1.

The clock generator provides the 48 MHz clock required for USB Full-Speed and Low-Speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module. The PIC32 USB module includes the following features:

- · USB Full-Speed support for Host and Device

- Low-Speed Host support

- USB OTG support

- · Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- · Transaction handshaking performed by hardware

- · Endpoint buffering anywhere in system RAM

- · Integrated DMA to access system RAM and Flash

- Note: The implementation and use of the USB specifications, as well as other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc., also referred to as USB-IF (www.usb.org). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                              | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------------------|------------------|

| 21.24        | U-0                                           | U-0              |

| 31:24        |                   | _                 | —                 | —                 | _                 | —                 | _                                             | _                |

| 22:16        | U-0                                           | U-0              |

| 23:16        |                   | _                 | _                 | _                 |                   |                   | _                                             |                  |

| 15:0         | U-0                                           | U-0              |

| 15:8         |                   | —                 | —                 | —                 | —                 | -                 | —                                             | —                |

|              | R/W-0                                         | R/W-0            |

| 7:0          | BTSEE             | BMXEE             | DMAEE             | BTOEE             | DFN8EE            | CRC16EE           | CRC5EE <sup>(1)</sup><br>EOFEE <sup>(2)</sup> | PIDEE            |

#### REGISTER 10-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

#### Legend:

| 0                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

|       | •                                                         |

|-------|-----------------------------------------------------------|

| bit 7 | BTSEE: Bit Stuff Error Interrupt Enable bit               |

|       | 1 = BTSEF interrupt is enabled                            |

|       | 0 = BTSEF interrupt is disabled                           |

| bit 6 | BMXEE: Bus Matrix Error Interrupt Enable bit              |

|       | 1 = BMXEF interrupt is enabled                            |

|       | 0 = BMXEF interrupt is disabled                           |

| bit 5 | DMAEE: DMA Error Interrupt Enable bit                     |

|       | 1 = DMAEF interrupt is enabled                            |

|       | 0 = DMAEF interrupt is disabled                           |

| bit 4 | BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit |

|       | 1 = BTOEF interrupt is enabled                            |

|       | 0 = BTOEF interrupt is disabled                           |

| bit 3 | DFN8EE: Data Field Size Error Interrupt Enable bit        |

|       | 1 = DFN8EF interrupt is enabled                           |

|       | 0 = DFN8EF interrupt is disabled                          |

- bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

- 1 = CRC16EF interrupt is enabled

- 0 = CRC16EF interrupt is disabled

- bit 1 CRC5EE: CRC5 Host Error Interrupt Enable bit<sup>(1)</sup>

- 1 = CRC5EF interrupt is enabled

- 0 = CRC5EF interrupt is disabled

- EOFEE: EOF Error Interrupt Enable bit<sup>(2)</sup>

- 1 = EOF interrupt is enabled

- 0 = EOF interrupt is disabled

- bit 0 PIDEE: PID Check Failure Interrupt Enable bit

- 1 = PIDEF interrupt is enabled

- 0 = PIDEF interrupt is disabled

- Note 1: Device mode.

- 2: Host mode.

Note: For an interrupt to propagate the USBIF register, the UERRIE (U1IE<1>) bit must be set.

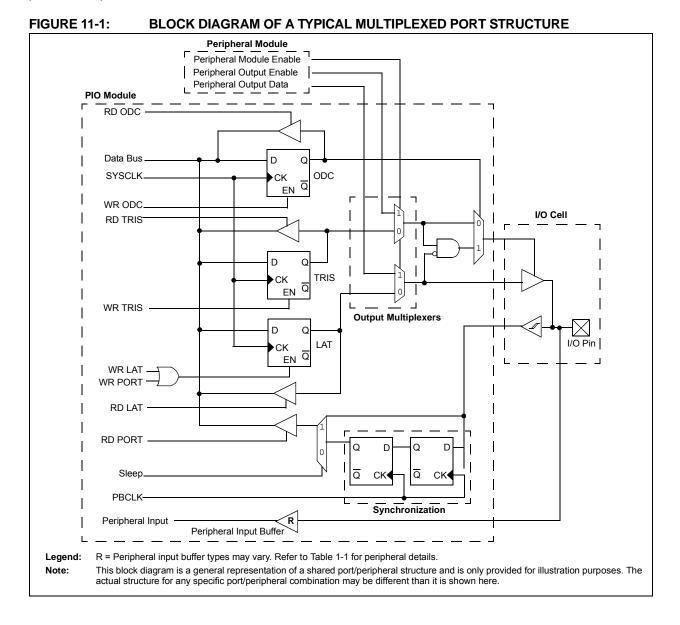

#### 11.0 I/O PORTS

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS60001120), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

General purpose I/O pins are the simplest of peripherals. They allow the PIC<sup>®</sup> MCU to monitor and control other devices. To add flexibility and functionality, some pins are multiplexed with alternate functions. These functions depend on which peripheral features are on the device. In general, when a peripheral is functioning, that pin may not be used as a general purpose I/O pin.

Key features of this module include:

- · Individual output pin open-drain enable/disable

- · Individual input pin weak pull-up and pull-down

- Monitor selective inputs and generate interrupt when change in pin state is detected

- · Operation during Sleep and Idle modes

- Fast bit manipulation using CLR, SET, and INV registers

Figure 11-1 illustrates a block diagram of a typical multiplexed I/O port.

#### 13.2 Timer Control Registers

### TABLE 13-1: TIMER2-TIMER5 REGISTER MAP

|                             | - 15                            |           |              |       |       |       |             |       |      |      |        |      |            |      |      |      |          |      |            |

|-----------------------------|---------------------------------|-----------|--------------|-------|-------|-------|-------------|-------|------|------|--------|------|------------|------|------|------|----------|------|------------|

| ess                         |                                 |           |              |       |       |       |             |       |      | Bi   | its    |      |            |      |      |      |          |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15        | 30/14 | 29/13 | 28/12 | 27/11       | 26/10 | 25/9 | 24/8 | 23/7   | 22/6 | 21/5       | 20/4 | 19/3 | 18/2 | 17/1     | 16/0 | All Resets |

| 0800                        | T2CON                           | 31:16     | _            | _     | —     | _     | —           | —     | —    | _    | —      | -    | —          | _    | —    | _    | _        | -    | 0000       |

| 0000                        | 12001                           | 15:0      | ON           |       | SIDL  | —     | —           | —     | _    | _    | TGATE  | -    | TCKPS<2:0> | >    | T32  | —    | TCS      | —    | 0000       |

| 0810                        | TMR2                            | 31:16     | —            | —     | —     | —     | —           | —     | _    | —    | —      | —    | —          | —    |      | —    | —        | _    | 0000       |

| 0010                        |                                 | 15:0      | TMR2<15:0> 0 |       |       |       |             |       |      |      |        |      |            | 0000 |      |      |          |      |            |

| 0820                        | PR2                             | 31:16     | —            | —     | —     | —     | —           | —     | —    | —    | —      | _    | —          | —    | —    | —    | —        | _    | 0000       |

| 0020                        |                                 | 15:0      |              |       |       |       |             |       |      | PR2< | 15:0>  |      |            |      |      |      |          |      | FFFF       |

| 0040                        | T3CON                           | 31:16     | —            | —     | —     | _     | —           | —     | —    | —    | —      | -    | —          | —    | —    | _    | —        | —    | 0000       |

| 0/100                       | 10001                           | 15:0      | ON           | —     | SIDL  | _     | —           | —     | —    | —    | TGATE  |      | TCKPS<2:0> | >    | —    | _    | TCS      | —    | 0000       |

| 0A10                        | TMR3                            | 31:16     |              | _     | _     | —     | _           | —     |      | —    |        | —    | —          | _    | —    | _    | _        |      | 0000       |

| 0,110                       | -                               | 15:0      |              |       |       |       |             |       |      | TMR3 | <15:0> |      |            |      |      |      |          |      | 0000       |

| 0A20                        | PR3                             | 31:16     | —            | —     | —     | —     | —           | —     | _    | —    | —      |      | —          | _    |      | —    | —        |      | 0000       |

|                             | _                               | 15:0      |              |       |       |       |             |       |      | PR3< | :15:0> |      |            |      |      |      |          |      | FFFF       |

| 0C00                        | T4CON                           | 31:16     | _            | _     | —     | —     | —           | —     | —    | _    | —      | —    | —          | —    | —    | —    | _        | —    | 0000       |

|                             |                                 | 15:0      | ON           | —     | SIDL  | —     | —           |       | _    | —    | TGATE  | -    | TCKPS<2:0  | >    | T32  | —    | TCS      |      | 0000       |

| 0C10                        | TMR4                            | 31:16     | _            | —     | —     | —     | —           | —     | _    | —    | —      | —    | —          | —    | —    | —    | —        | —    | 0000       |

|                             |                                 | 15:0      |              |       |       |       |             |       |      | TMR4 |        |      |            |      |      |      |          |      | 0000       |

| 0C20                        | PR4                             | 31:16     | _            | —     | —     | —     | —           | —     | _    | -    | —      | _    | —          | _    | —    | _    | —        |      | 0000       |

|                             |                                 | 15:0      |              |       |       |       |             |       |      |      | :15:0> |      |            |      |      |      |          |      | FFFF       |

| 0E00                        | T5CON                           | 31:16     | -            | _     | -     | _     |             | —     |      | _    |        |      |            |      |      |      | —<br>T00 |      | 0000       |

|                             |                                 | 15:0      | ON           |       | SIDL  | _     |             |       | _    | _    | TGATE  |      | TCKPS<2:0> |      | _    | _    | TCS      | _    | 0000       |

| 0E10                        | TMR5                            |           |              |       |       |       |             |       |      | _    | 0000   |      |            |      |      |      |          |      |            |

| <u> </u>                    |                                 | 15:0      |              |       |       |       |             |       |      |      | <15:0> |      |            |      |      |      |          |      | 0000       |

| 0E20                        | PR5                             | 31:16     |              | —     | —     | —     | —           | —     | _    |      |        | _    | —          | _    | —    | —    | —        |      | 0000       |

|                             |                                 | 15:0      |              |       |       |       | d a stal Da |       |      |      | :15:0> |      |            |      |      |      |          |      | FFFF       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### REGISTER 15-1: ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER (CONTINUED)

ICM<2:0>: Input Capture Mode Select bits

bit 2-0

- 111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

- 110 = Simple Capture Event mode every edge, specified edge first and every edge thereafter

- 101 = Prescaled Capture Event mode every sixteenth rising edge

- 100 = Prescaled Capture Event mode every fourth rising edge

- 011 = Simple Capture Event mode every rising edge

- 010 = Simple Capture Event mode every falling edge

- 001 = Edge Detect mode every edge (rising and falling)

- 000 = Input Capture module is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 17-3: SPIxSTAT: SPI STATUS REGISTER

bit 3 SPITBE: SPI Transmit Buffer Empty Status bit 1 = Transmit buffer, SPIxTXB is empty 0 = Transmit buffer, SPIxTXB is not empty Automatically set in hardware when SPI transfers data from SPIxTXB to SPIxSR. Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB. bit 2 Unimplemented: Read as '0' bit 1 SPITBF: SPI Transmit Buffer Full Status bit 1 = Transmit not yet started, SPITXB is full 0 = Transmit buffer is not full Standard Buffer Mode: Automatically set in hardware when the core writes to the SPIBUF location, loading SPITXB. Automatically cleared in hardware when the SPI module transfers data from SPITXB to SPISR. Enhanced Buffer Mode: Set when CWPTR + 1 = SRPTR; cleared otherwise bit 0 SPIRBF: SPI Receive Buffer Full Status bit 1 = Receive buffer, SPIxRXB is full

0 = Receive buffer, SPIxRXB is not full

#### Standard Buffer Mode:

Automatically set in hardware when the SPI module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

#### Enhanced Buffer Mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24        |                   |                   | HR10              | <1:0>             | HR01<3:0>         |                   |                  |                  |  |  |

| 00.40        | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        |                   |                   | MIN10<2:0>        |                   |                   | MIN01             | <3:0>            |                  |  |  |

| 45.0         | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         |                   |                   | SEC10<2:0>        |                   | SEC01<3:0>        |                   |                  |                  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7:0          | _                 | _                 | —                 | —                 | —                 | _                 | —                | —                |  |  |

|              |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

| Leaend:      |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

#### REGISTER 21-5: ALRMTIME: ALARM TIME VALUE REGISTER

# R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary Coded Decimal value of hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 **HR01<3:0>:** Binary Coded Decimal value of hours bits, 1s place digit; contains a value from 0 to 9 bit 23 **Unimplemented:** Read as '0'

bit 22-20 MIN10<2:0>: Binary Coded Decimal value of minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 **MIN01<3:0>:** Binary Coded Decimal value of minutes bits, 1s place digit; contains a value from 0 to 9 bit 15 **Unimplemented:** Read as '0'

bit 14-12 SEC10<2:0>: Binary Coded Decimal value of seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 **SEC01<3:0>:** Binary Coded Decimal value of seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

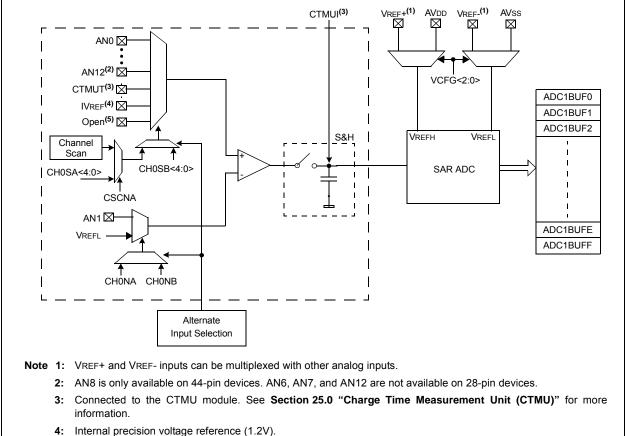

#### 22.0 **10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)**

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- · Up to 1 Msps conversion speed

**FIGURE 22-1:**

- Up to 13 analog input pins

- External voltage reference input pins

- · One unipolar, differential Sample and Hold Amplifier (SHA)

- Automatic Channel Scan mode

- Selectable conversion trigger source

- · 16-word conversion result buffer

- Selectable buffer fill modes

- Eight conversion result format options

- · Operation during Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 22-1. Figure 22-2 illustrates a block diagram of the ADC conversion clock period. The 10-bit ADC has up to 13 analog input pins, designated AN0-AN12. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

#### 5: This selection is only used with CTMU capacitive and time measurement.

ADC1 MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 51.24        | _                 | —                 |                   | —                 | _                 |                   | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | —                 |                   | —                 | _                 | _                 | _                | —                |

| 15:8         | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | -                 | —                 | SIDL              | —                 | _                 | _                 |                  | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |

| 7.0          |                   |                   |                   |                   |                   | C3OUT             | C2OUT            | C10UT            |

#### REGISTER 23-2: CMSTAT: COMPARATOR STATUS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-14 Unimplemented: Read as '0'

#### bit 13 SIDL: Stop in Idle Control bit

1 = All Comparator modules are disabled when the device enters Idle mode

0 = All Comparator modules continue to operate when the device enters Idle mode

#### bit 12-3 Unimplemented: Read as '0'

#### bit 2 C3OUT: Comparator Output bit

- 1 = Output of Comparator 3 is a '1'

- 0 = Output of Comparator 3 is a '0'

#### bit 1 C2OUT: Comparator Output bit

- 1 = Output of Comparator 2 is a '1'

- 0 = Output of Comparator 2 is a '0'

#### bit 0 **C1OUT:** Comparator Output bit

- 1 = Output of Comparator 1 is a '1'

- 0 = Output of Comparator 1 is a '0'

#### REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED) bit 24 EDG1STAT: Edge1 Status bit Indicates the status of Edge1 and can be written to control edge source 1 = Edge1 has occurred 0 = Edge1 has not occurred EDG2MOD: Edge2 Edge Sampling Select bit bit 23 1 = Input is edge-sensitive 0 = Input is level-sensitive bit 22 EDG2POL: Edge 2 Polarity Select bit 1 = Edge2 programmed for a positive edge response 0 = Edge2 programmed for a negative edge response bit 21-18 EDG2SEL<3:0>: Edge 2 Source Select bits 1111 = C3OUT pin is selected 1110 = C2OUT pin is selected 1101 = C1OUT pin is selected 1100 = PBCLK clock is selected 1011 = IC3 Capture Event is selected 1010 = IC2 Capture Event is selected 1001 = IC1 Capture Event is selected 1000 = CTED13 pin is selected 0111 = CTED12 pin is selected 0110 = CTED11 pin is selected 0101 = CTED10 pin is selected 0100 = CTED9 pin is selected 0011 = CTED1 pin is selected 0010 = CTED2 pin is selected 0001 = OC1 Compare Event is selected 0000 = Timer1 Event is selected bit 17-16 Unimplemented: Read as '0' bit 15 **ON:** ON Enable bit 1 = Module is enabled 0 = Module is disabled bit 14 Unimplemented: Read as '0' bit 13 CTMUSIDL: Stop in Idle Mode bit 1 = Discontinue module operation when the device enters Idle mode 0 = Continue module operation when the device enters Idle mode TGEN: Time Generation Enable bit<sup>(1)</sup> bit 12 1 = Enables edge delay generation 0 = Disables edge delay generation bit 11 EDGEN: Edge Enable bit 1 = Edges are not blocked 0 = Edges are blocked

- **Note 1:** When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 30-41) in Section 30.0 "Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

#### 26.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid. To disable a peripheral, the associated PMDx bit must be set to '1'. To enable a peripheral, the associated PMDx bit must be cleared (default). See Table 26-1 for more information.

Note: Disabling a peripheral module while it's ON bit is set, may result in undefined behavior. The ON bit for the associated peripheral module must be cleared prior to disable a module via the PMDx bits.

| TABLE 26-1: | PERIPHERAL MODULE DISABLE BITS AND LOCATIONS |  |

|-------------|----------------------------------------------|--|

|             |                                              |  |

| Peripheral <sup>(1)</sup>    | PMDx bit Name <sup>(1)</sup> | Register Name and Bit Location |  |  |

|------------------------------|------------------------------|--------------------------------|--|--|

| ADC1                         | AD1MD                        | PMD1<0>                        |  |  |

| СТМU                         | CTMUMD                       | PMD1<8>                        |  |  |

| Comparator Voltage Reference | CVRMD                        | PMD1<12>                       |  |  |

| Comparator 1                 | CMP1MD                       | PMD2<0>                        |  |  |

| Comparator 2                 | CMP2MD                       | PMD2<1>                        |  |  |

| Comparator 3                 | CMP3MD                       | PMD2<2>                        |  |  |

| Input Capture 1              | IC1MD                        | PMD3<0>                        |  |  |

| Input Capture 2              | IC2MD                        | PMD3<1>                        |  |  |

| Input Capture 3              | IC3MD                        | PMD3<2>                        |  |  |

| Input Capture 4              | IC4MD                        | PMD3<3>                        |  |  |

| Input Capture 5              | IC5MD                        | PMD3<4>                        |  |  |

| Output Compare 1             | OC1MD                        | PMD3<16>                       |  |  |

| Output Compare 2             | OC2MD                        | PMD3<17>                       |  |  |

| Output Compare 3             | OC3MD                        | PMD3<18>                       |  |  |

| Output Compare 4             | OC4MD                        | PMD3<19>                       |  |  |

| Output Compare 5             | OC5MD                        | PMD3<20>                       |  |  |

| Timer1                       | T1MD                         | PMD4<0>                        |  |  |

| Timer2                       | T2MD                         | PMD4<1>                        |  |  |

| Timer3                       | T3MD                         | PMD4<2>                        |  |  |

| Timer4                       | T4MD                         | PMD4<3>                        |  |  |

| Timer5                       | T5MD                         | PMD4<4>                        |  |  |

| UART1                        | U1MD                         | PMD5<0>                        |  |  |

| UART2                        | U2MD                         | PMD5<1>                        |  |  |

| SPI1                         | SPI1MD                       | PMD5<8>                        |  |  |

| SPI2                         | SPI2MD                       | PMD5<9>                        |  |  |

| I2C1                         | I2C1MD                       | PMD5<16>                       |  |  |

| I2C2                         | I2C2MD                       | PMD5<17>                       |  |  |

| USB <sup>(2)</sup>           | USBMD                        | PMD5<24>                       |  |  |

| RTCC                         | RTCCMD                       | PMD6<0>                        |  |  |

| Reference Clock Output       | REFOMD                       | PMD6<1>                        |  |  |

| PMP                          | PMPMD                        | PMD6<16>                       |  |  |

Note 1: Not all modules and associated PMDx bits are available on all devices. See TABLE 1: "PIC32MX1XX 28/36/44-Pin General Purpose Family Features" and TABLE 2: "PIC32MX2XX 28/36/44-pin USB Family Features" for the lists of available peripherals.

2: The module must not be busy after clearing the associated ON bit and prior to setting the USBMD bit.

### 27.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Configuration" Section 32. Section (DS60001124) and 33. "Programming and **Diagnostics**" (DS60001129), which are available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family devices include the following features intended to maximize application flexibility, reliability and minimize cost through elimination of external components.

- Flexible device configuration

- Joint Test Action Group (JTAG) interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

#### 27.1 Configuration Bits

The Configuration bits can be programmed using the following registers to select various device configurations.

- DEVCFG0: Device Configuration Word 0

- DEVCFG1: Device Configuration Word 1

- DEVCFG2: Device Configuration Word 2

- DEVCFG3: Device Configuration Word 3

- · CFGCON: Configuration Control Register

In addition, the DEVID register (Register 27-6) provides device and revision information.

|                                      |       | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) |                                                                                                                                                                                            |      |            |            |                                                   |  |

|--------------------------------------|-------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|------------|---------------------------------------------------|--|

| DC CHARACTERISTICS                   |       |                                                                       | $\begin{array}{ll} \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |            |            |                                                   |  |

| Param.<br>No. Symbol Characteristics |       | Min.                                                                  | Typical <sup>(1)</sup>                                                                                                                                                                     | Max. | Units      | Conditions |                                                   |  |

|                                      | VIL   | Input Low Voltage                                                     |                                                                                                                                                                                            |      |            |            |                                                   |  |

| DI10                                 |       | I/O Pins with PMP                                                     | Vss                                                                                                                                                                                        | —    | 0.15 Vdd   | V          |                                                   |  |

|                                      |       | I/O Pins                                                              | Vss                                                                                                                                                                                        | —    | 0.2 Vdd    | V          |                                                   |  |

| DI18                                 |       | SDAx, SCLx                                                            | Vss                                                                                                                                                                                        | —    | 0.3 VDD    | V          | SMBus disabled<br>(Note 4)                        |  |

| DI19                                 |       | SDAx, SCLx                                                            | Vss                                                                                                                                                                                        | —    | 0.8        | V          | SMBus enabled<br>(Note 4)                         |  |

|                                      | VIH   | Input High Voltage                                                    |                                                                                                                                                                                            |      |            |            |                                                   |  |

| DI20                                 |       | I/O Pins not 5V-tolerant <sup>(5)</sup>                               | 0.65 VDD                                                                                                                                                                                   | _    | Vdd        | V          | (Note 4,6)                                        |  |

|                                      |       | I/O Pins 5V-tolerant with<br>PMP <sup>(5)</sup>                       | 0.25 VDD + 0.8V                                                                                                                                                                            | —    | 5.5        | V          | (Note 4,6)                                        |  |

|                                      |       | I/O Pins 5V-tolerant <sup>(5)</sup>                                   | 0.65 VDD                                                                                                                                                                                   | —    | 5.5        | V          |                                                   |  |

| DI28                                 |       | SDAx, SCLx                                                            | 0.65 VDD                                                                                                                                                                                   | _    | 5.5        | V          | SMBus disabled<br>(Note 4,6)                      |  |

| DI29                                 |       | SDAx, SCLx                                                            | 2.1                                                                                                                                                                                        | _    | 5.5        | V          | SMBus enabled,<br>2.3V ≤ VPIN ≤ 5.5<br>(Note 4,6) |  |

| DI30                                 | ICNPU | Change Notification<br>Pull-up Current                                | _                                                                                                                                                                                          | —    | -50        | μA         | VDD = 3.3V, VPIN = VSS<br>(Note 3,6)              |  |

| DI31                                 | ICNPD | Change Notification<br>Pull-down Current <sup>(4)</sup>               | _                                                                                                                                                                                          | —    | -50        | μA         | VDD = 3.3V, VPIN = VDD                            |  |

|                                      | lı∟   | Input Leakage Current<br>(Note 3)                                     |                                                                                                                                                                                            |      |            |            |                                                   |  |

| DI50                                 |       | I/O Ports                                                             | _                                                                                                                                                                                          | _    | <u>+</u> 1 | μA         | $Vss \le VPIN \le VDD$ ,<br>Pin at high-impedance |  |

| DI51                                 |       | Analog Input Pins                                                     | _                                                                                                                                                                                          | _    | <u>+</u> 1 | μA         | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance  |  |

| DI55                                 |       | MCLR <sup>(2)</sup>                                                   | —                                                                                                                                                                                          | _    | <u>+</u> 1 | μA         | $Vss \leq V PIN \leq V DD$                        |  |

| DI56                                 |       | OSC1                                                                  | _                                                                                                                                                                                          | _    | <u>+</u> 1 | μA         | $Vss \le VPIN \le VDD,$<br>XT and HS modes        |  |

#### TABLE 30-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Pin Diagrams" section for the 5V-tolerant pins.

- 6: The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

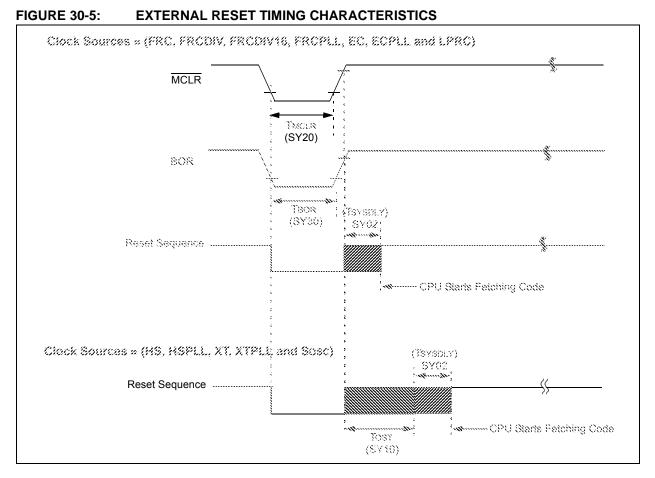

| TABLE 30-22: RESETS TIMING |         |                                                                                                                                                                                                                                                                                 |      |                              |      |       |            |  |

|----------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------|------|-------|------------|--|

| AC CHARACTERISTICS         |         | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |      |                              |      |       |            |  |

| Param.<br>No.              | Symbol  | Characteristics <sup>(1)</sup>                                                                                                                                                                                                                                                  | Min. | Typical <sup>(2)</sup>       | Max. | Units | Conditions |  |

| SY00                       | Τρυ     | Power-up Period<br>Internal Voltage Regulator Enabled                                                                                                                                                                                                                           | —    | 400                          | 600  | μS    | _          |  |

| SY02                       | TSYSDLY | System Delay Period:<br>Time Required to Reload Device<br>Configuration Fuses plus SYSCLK<br>Delay before First instruction is<br>Fetched.                                                                                                                                      | _    | 1 μs +<br>8 SYSCLK<br>cycles | _    | _     | _          |  |

| SY20                       | TMCLR   | MCLR Pulse Width (low)                                                                                                                                                                                                                                                          | 2    | _                            | _    | μS    | —          |  |

| SY30                       | TBOR    | BOR Pulse Width (low)                                                                                                                                                                                                                                                           |      | 1                            | _    | μS    | —          |  |

These parameters are characterized, but not tested in manufacturing. Note 1:

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Characterized by design but not tested.

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2011-2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN:978-1-5224-0471-2