Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 25                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 12x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 36-VFTLA Exposed Pad                                                           |

| Supplier Device Package    | 36-VTLA (5x5)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx150f128c-i-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUs

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

### 2.1 Basic Connection Requirements

Getting started with the PIC32MX1XX/2XX 28/36/44pin Family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes (see **2.5** "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.7 "External Oscillator Pins")

The following pins may be required:

• VREF+/VREF- pins – used when external voltage reference for the ADC module is implemented

Note: The AVDD and AVss pins must be connected, regardless of ADC use and the ADC voltage reference source.

### 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1  $\mu$ F (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

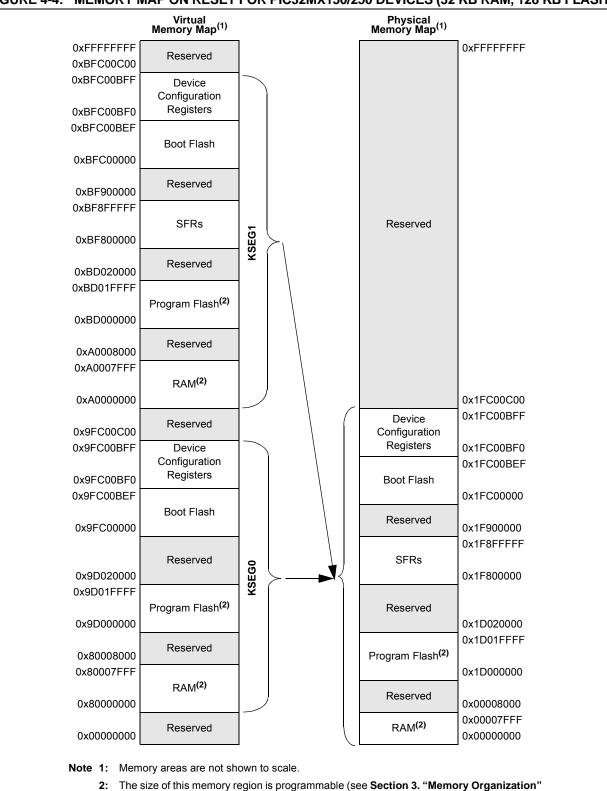

#### FIGURE 4-4: MEMORY MAP ON RESET FOR PIC32MX150/250 DEVICES (32 KB RAM, 128 KB FLASH)

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS60001115) in the "*PIC32 Family Reference Manual*") and can be changed by initialization code provided by end-user development tools (refer to the specific development tool documentation for information).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 31:24        |                   | BMXDRMSZ<31:24>   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 23:16        | BMXDRMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 15:8         |                   |                   |                   | BMXDR             | MSZ<15:8>         |                   |                  |                  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 7:0          | BMXDRMSZ<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |

#### **BMXDRMSZ: DATA RAM SIZE REGISTER REGISTER 4-5:**

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-0 BMXDRMSZ<31:0>: Data RAM Memory (DRM) Size bits

Static value that indicates the size of the Data RAM in bytes: 0x00001000 = Device has 4 KB RAM 0x00002000 = Device has 8 KB RAM 0x00004000 = Device has 16 KB RAM 0x00008000 = Device has 32 KB RAM 0x00010000 = Device has 64 KB RAM

#### **REGISTER 4-6: BMXPUPBA: PROGRAM FLASH (PFM) USER PROGRAM BASE ADDRESS** REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | —                 | —                 | _                 | _                 | —                 | —                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | _                 | _                 | _                 | _                 | BMXPUPBA<19:16>   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0              | R-0              |  |  |

| 15:8         |                   | BMXPUPBA<15:8>    |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          | BMXPUPBA<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-20 Unimplemented: Read as '0'

bit 19-11 BMXPUPBA<19:11>: Program Flash (PFM) User Program Base Address bits

#### bit 10-0 BMXPUPBA<10:0>: Read-Only bits This value is always '0', which forces 2 KB increments

Note 1: At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXPFMSZ.

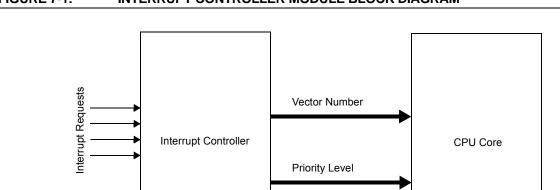

## 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Interrupt Controller" (DS60001108), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The PIC32MX1XX/2XX 28/36/44-pin Family interrupt module includes the following features:

- Up to 64 interrupt sources

- · Up to 44 interrupt vectors

- · Single and multi-vector mode operations

- Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable subpriority levels within each priority

- · Software can generate any interrupt

- User-configurable Interrupt Vector Table (IVT) location

- User-configurable interrupt vector spacing

A simplified block diagram of the Interrupt Controller module is illustrated in Figure 7-1.

#### FIGURE 7-1: INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

Note: The dedicated shadow register set is not present on PIC32MX1XX/2XX 28/36/44-pin Family devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6            | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|------------------------------|-------------------|-------------------|---------------------|-------------------|------------------|------------------|--|--|

|              | U-0               | R/W-0                        | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | _                 | RODIV<14:8> <sup>(1,3)</sup> |                   |                   |                     |                   |                  |                  |  |  |

|              | R/W-0             | R/W-0                        | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        |                   | RODIV<7:0> <sup>(1,3)</sup>  |                   |                   |                     |                   |                  |                  |  |  |

| 45.0         | R/W-0             | U-0                          | R/W-0             | R/W-0             | R/W-0               | U-0               | R/W-0, HC        | R-0, HS, HC      |  |  |

| 15:8         | ON                | _                            | SIDL              | OE                | RSLP <sup>(2)</sup> | _                 | DIVSWEN          | ACTIVE           |  |  |

|              | U-0               | U-0                          | U-0               | U-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                              |                   |                   |                     | ROSEL             | .<3:0>(1)        |                  |  |  |

#### REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| Legend:           | HC = Hardware Clearable | e HS = Hardware Settable           |                    |  |

|-------------------|-------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31 Unimplemented: Read as '0'

| bit 30-16 | RODIV<14:0> Reference Clock Divider bits <sup>(1,3)</sup>                           |

|-----------|-------------------------------------------------------------------------------------|

|           | The value selects the reference clock divider bits. See Figure 8-1 for information. |

| bit 15    | ON: Output Enable bit                                                               |

|           | 1 = Reference Oscillator module is enabled                                          |

|           | 0 = Reference Oscillator module is disabled                                         |

| bit 14    | Unimplemented: Read as '0'                                                          |

| bit 13    | SIDL: Peripheral Stop in Idle Mode bit                                              |

- 1 = Discontinue module operation when the device enters Idle mode

- 0 =Continue module operation when the device enters lide mode

- bit 12 **OE:** Reference Clock Output Enable bit

- 1 = Reference clock is driven out on REFCLKO pin

- 0 = Reference clock is not driven out on REFCLKO pin

- bit 11 RSLP: Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference Oscillator module output continues to run in Sleep

- 0 = Reference Oscillator module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 DIVSWEN: Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- bit 8 ACTIVE: Reference Clock Request Status bit

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- **2:** This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

| Bit Range      | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|----------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 21.24          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24          |                   |                   |                   | CHSSA<            | 31:24>            |                   |                  |                  |  |

| 00:40          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16          | CHSSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |

| 45.0           | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8           | CHSSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0            | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0 CHSSA<7:0> |                   |                   |                   |                   |                   |                   |                  |                  |  |

#### **REGISTER 9-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER**

| Legend:           |                                      |                      |                    |

|-------------------|--------------------------------------|----------------------|--------------------|

| R = Readable bit  | le bit W = Writable bit U = Unimplem |                      |                    |

| -n = Value at POR | '1' = Bit is set                     | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0

CHSSA<31:0> Channel Source Start Address bits

Channel source start address.

Note: This must be the physical address of the source.

#### **REGISTER 9-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        |                   |                   |                   | CHDSA<            | 31:24>            |                   |                  |                  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | CHDSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | CHDSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |

|              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   | CHDSA<7:0>        |                   |                   |                   |                   |                  |                  |  |

| Legend:           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 31-0 **CHDSA<31:0>:** Channel Destination Start Address bits Channel destination start address.

$\ensuremath{\textbf{Note:}}$  This must be the physical address of the destination.

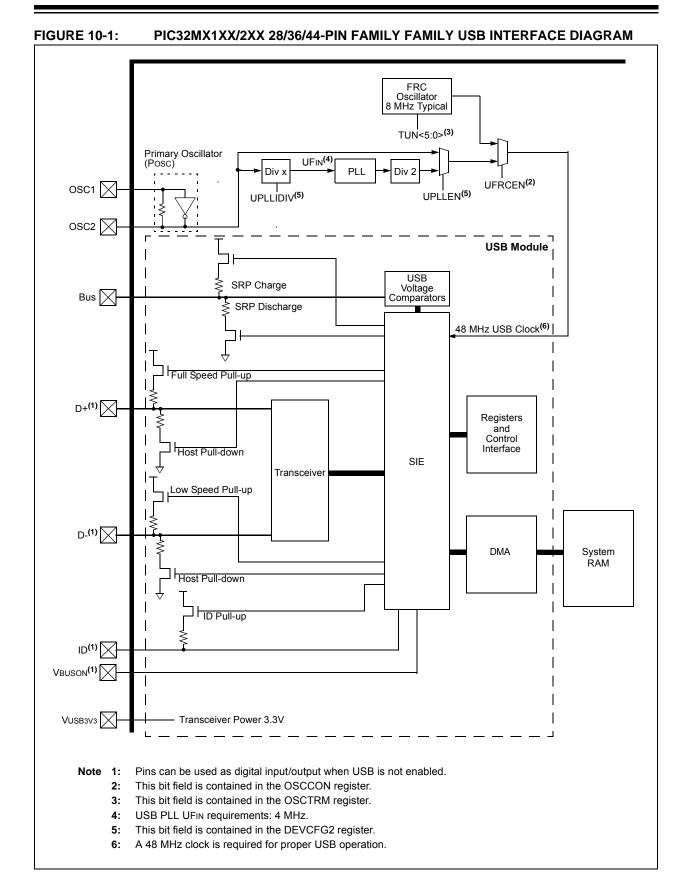

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### **USB Control Registers** 10.1

#### TABLE 10-1: USB REGISTER MAP

| ess                         |                                 |           |       |       |       |       |       |       |      |      | Bit                    | s        |          |              |          |          |                 |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------------------------|----------|----------|--------------|----------|----------|-----------------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7                   | 22/6     | 21/5     | 20/4         | 19/3     | 18/2     | 17/1            | 16/0     | All Resets |

| 5040                        | (4)                             | 31:16     |       | _     | —     | —     | —     | —     |      | _    | —                      | —        | —        | —            | —        | —        | _               | —        | 000        |

| 5040                        | 01010IR( )                      | 15:0      |       |       | _     | —     | -     | _     |      | _    | IDIF                   | T1MSECIF | LSTATEIF | ACTVIF       | SESVDIF  | SESENDIF | 1               | VBUSVDIF | 000        |

| 5050                        | <b>U10TGIE</b>                  | 31:16     | —     | _     | —     | —     | —     | —     | —    | —    | —                      |          | —        | —            | —        | —        | _               | —        | 000        |

| 0000                        | OTOTOLE                         | 15:0      | —     | _     | —     | —     | —     | —     | —    | —    | IDIE                   | T1MSECIE | LSTATEIE | ACTVIE       | SESVDIE  | SESENDIE | _               | VBUSVDIE | 000        |

| 5060                        | U10TGSTAT <sup>(3)</sup>        | 31:16     |       |       | —     | —     | —     | —     | _    | —    |                        |          | —        | —            |          | —        | _               |          | 000        |

| 0000                        | 0101001/11                      | 15:0      | —     | _     | —     | —     | —     | —     | —    | —    | ID                     |          | LSTATE   | —            | SESVD    | SESEND   | _               | VBUSVD   | 000        |

| 5070                        | U10TGCON                        | 31:16     |       |       | —     | —     | —     | —     | _    | —    |                        |          | —        | —            |          | —        | _               |          | 000        |

| 0070                        | 01010001                        | 15:0      |       |       | —     | —     | —     | —     | _    | —    | DPPULUP                | DMPULUP  | DPPULDWN | DMPULDWN     | VBUSON   | OTGEN    | VBUSCHG         | VBUSDIS  | 000        |

| 5080                        | U1PWRC                          | 31:16     |       |       | —     | —     | —     | —     | _    | —    |                        |          | —        | —            |          | —        | _               |          | 000        |

| 0000                        | on mile                         | 15:0      |       |       | —     | —     | —     | —     | _    | —    | UACTPND <sup>(4)</sup> |          | —        | USLPGRD      | USBBUSY  | —        | USUSPEND        | USBPWR   | 000        |

|                             |                                 | 31:16     |       |       | —     | —     | —     | —     | _    | —    |                        |          | —        | —            |          | —        | _               |          | 000        |

| 5200                        | U1IR <sup>(2)</sup>             | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | STALLIF                | ATTACHIF | RESUMEIF | IDLEIF       | TRNIF    | SOFIF    | UERRIF          | URSTIF   | 000        |

|                             |                                 | 04.40     |       |       |       |       |       |       |      |      |                        |          |          |              |          |          |                 | DETACHIF | 000        |

| 5210                        | U1IE                            | 31:16     |       | _     |       |       |       |       |      | _    | —                      | —        |          | —            | —        | —        | —               |          | 000        |

| 5210                        | OTIE                            | 15:0      | —     | —     |       | —     | —     | —     | —    | —    | STALLIE                | ATTACHIE | RESUMEIE | IDLEIE       | TRNIE    | SOFIE    | UERRIE          | DETACHIE | 000        |

|                             |                                 | 31:16     |       | _     | _     | _     |       | _     |      |      | _                      | _        | _        | _            | _        | _        | _               |          | 000        |

| 5220                        | U1EIR <sup>(2)</sup>            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | BTSEF                  | BMXEF    | DMAEF    | BTOEF        | DFN8EF   | CRC16EF  | CRC5EF<br>EOFEF | PIDEF    | 000        |

|                             |                                 | 31:16     | _     | _     |       | _     | _     | _     | _    | _    | _                      |          | _        | _            | _        | _        | _               |          | 000        |

| 5230                        | U1EIE                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | BTSEE                  | BMXEE    | DMAEE    | BTOEE        | DFN8EE   | CRC16EE  | CRC5EE<br>EOFEE | PIDEE    | 000        |

|                             | (2)                             | 31:16     | _     | _     |       | _     | _     |       |      | _    |                        | _        |          | _            | _        |          | _               | _        | 000        |

| 5240                        | U1STAT <sup>(3)</sup>           | 15:0      | _     | _     | _     | _     | _     | _     |      | _    |                        |          | PT<3:0>  |              | DIR      | PPBI     | _               | _        | 000        |

|                             |                                 | 31:16     | _     | _     | _     | _     |       | _     | _    | _    |                        | _        | _        |              | _        | _        | _               |          | 000        |

| 5250                        | U1CON                           | -         |       |       |       |       |       |       |      |      | IOTATE                 | 050      | PKTDIS   |              | LIGOTELL | DEOLINE  |                 | USBEN    | 000        |

|                             |                                 | 15:0      | _     | _     | _     | —     | _     | —     | _    | -    | JSTATE                 | SE0      | TOKBUSY  | USBRST       | HOSTEN   | RESUME   | PPBRST          | SOFEN    | 000        |

| 5260                        | U1ADDR                          | 31:16     | _     | _     |       | —     |       | —     | _    | —    | _                      | _        | _        | —            | —        | —        | _               | —        | 000        |

| 5200                        | UIADDR                          | 15:0      |       | _     | —     | —     | —     | —     | -    | —    | – LSPDEN DEVADDR<6:0>  |          |          |              |          |          |                 | 000      |            |

| 5270                        | U1BDTP1                         | 31:16     | _     | _     | —     | —     | —     | —     | _    | _    | —                      | —        | _        | —            | —        | _        | _               | —        | 000        |

| 5210                        |                                 | 15:0      | —     | _     | _     | _     | _     | _     | _    | -    |                        |          | BC       | )TPTRL<15:9> | >        |          |                 | _        | 0000       |

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information. Note 1:

2: This register does not have associated SET and INV registers.

This register does not have associated CLR, SET and INV registers. 3:

4: Reset value for this bit is undefined.

#### REGISTER 13-1: TXCON: TYPE B TIMER CONTROL REGISTER (CONTINUED)

- bit 3 T32: 32-Bit Timer Mode Select bit<sup>(2)</sup>

- 1 = Odd numbered and even numbered timers form a 32-bit timer

- 0 = Odd numbered and even numbered timers form a separate 16-bit timer

- bit 2 Unimplemented: Read as '0'

- bit 1 **TCS:** Timer Clock Source Select bit<sup>(3)</sup>

- 1 = External clock from TxCK pin

- 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3, and Timer5). All timer functions are set through the even numbered timers.

- 4: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                   | _                 | _                 | _                 | _                 | _                 | —                | _                |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                   | —                 | _                 | _                 | _                 | _                 | —                | _                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> | _                 | _                 | _                 | —                 | _                 | —                | _                |

| 7.0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          | _                   |                   | S                 | WDTWINEN          | WDTCLR            |                   |                  |                  |

#### REGISTER 14-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend: y = Values set from Configuration bits on POR |                                                     |                      |                    |  |  |  |  |

|-------------------------------------------------------|-----------------------------------------------------|----------------------|--------------------|--|--|--|--|

| R = Readable bit                                      | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |  |  |

| -n = Value at POR                                     | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

- 1 = Enables the WDT if it is not enabled by the device configuration

- 0 = Disable the WDT if it was enabled in software

- bit 14-7 Unimplemented: Read as '0'

- bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> of Configuration bits.

- bit 1 WDTWINEN: Watchdog Timer Window Enable bit

- 1 = Enable windowed Watchdog Timer

- 0 = Disable windowed Watchdog Timer

- bit 0 **WDTCLR:** Watchdog Timer Reset bit

- 1 = Writing a '1' will clear the WDT

- 0 = Software cannot force this bit to a '0'

- **Note 1:** A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 19-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | <ul> <li>ABAUD: Auto-Baud Enable bit</li> <li>1 = Enable baud rate measurement on the next character – requires reception of Sync character (0x55); cleared by hardware upon completion</li> <li>0 = Baud rate measurement disabled or completed</li> </ul> |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | RXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                           |

| bit 3   | BRGH: High Baud Rate Enable bit<br>1 = High-Speed mode – 4x baud clock enabled<br>0 = Standard Speed mode – 16x baud clock enabled                                                                                                                          |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits<br>11 = 9-bit data, no parity<br>10 = 8-bit data, odd parity<br>01 = 8-bit data, even parity<br>00 = 8-bit data, no parity                                                                                       |

| bit 0   | <b>STSEL:</b> Stop Selection bit<br>1 = 2 Stop bits<br>0 = 1 Stop bit                                                                                                                                                                                       |

**Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 19-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED) bit 7-6 URXISEL<1:0>: Receive Interrupt Mode Selection bit 11 = Reserved; do not use 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (i.e., has 6 or more data characters) 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (i.e., has 4 or more data characters) 00 = Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character) bit 5 ADDEN: Address Character Detect bit (bit 8 of received data = 1) 1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect. 0 = Address Detect mode is disabled bit 4 **RIDLE:** Receiver Idle bit (read-only) 1 =Receiver is Idle 0 = Data is being received PERR: Parity Error Status bit (read-only) bit 3 1 = Parity error has been detected for the current character 0 = Parity error has not been detected bit 2 FERR: Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character 0 = Framing error has not been detected **OERR:** Receive Buffer Overrun Error Status bit. bit 1 This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and the RSR to an empty state. 1 = Receive buffer has overflowed 0 = Receive buffer has not overflowed bit 0 **URXDA:** Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

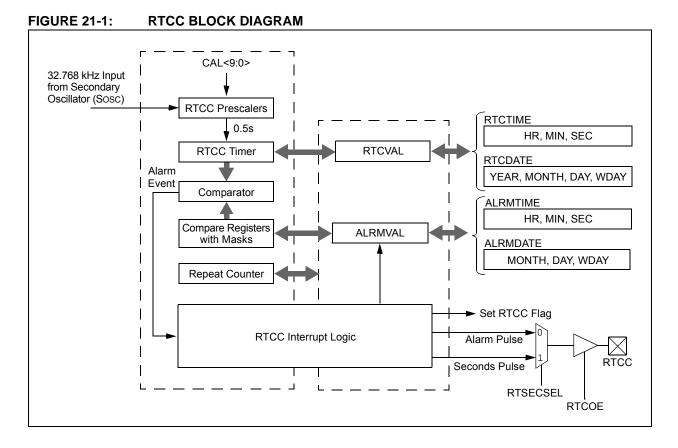

## 21.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32 RTCC module is intended for applications in which accurate time must be maintained for extended periods of time with minimal or no CPU intervention. Low-power optimization provides extended battery lifetime while keeping track of time. Following are some of the key features of this module:

- · Time: hours, minutes and seconds

- 24-hour format (military time)

- · Visibility of one-half second period

- · Provides calendar: day, date, month and year

- Alarm intervals are configurable for half of a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month and one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat: Chime

- Year range: 2000 to 2099

- Leap vear correction

- · BCD format for smaller firmware overhead

- Optimized for long-term battery operation

- Fractional second synchronization

- User calibration of the clock crystal frequency with auto-adjust

- Calibration range: ±0.66 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- Requirements: External 32.768 kHz clock crystal

- Alarm pulse or seconds clock output on RTCC pin

#### REGISTER 22-1: AD1CON1: ADC CONTROL REGISTER 1 (CONTINUED)

bit 4 CLRASAM: Stop Conversion Sequence bit (when the first ADC interrupt is generated)

- 1 = Stop conversions when the first ADC interrupt is generated. Hardware clears the ASAM bit when the ADC interrupt is generated.

- 0 = Normal operation, buffer contents will be overwritten by the next conversion sequence

- bit 3 Unimplemented: Read as '0'

- bit 2 **ASAM:** ADC Sample Auto-Start bit

1 = Sampling begins immediately after last conversion completes; SAMP bit is automatically set.

- 0 = Sampling begins when SAMP bit is set

- bit 1 SAMP: ADC Sample Enable bit<sup>(2)</sup>

1 = The ADC sample and hold amplifier is sampling

0 = The ADC sample/hold amplifier is holding

When ASAM = 0, writing '1' to this bit starts sampling.

- When SSRC = 000, writing '0' to this bit will end sampling and start conversion.

- bit 0 DONE: Analog-to-Digital Conversion Status bit<sup>(3)</sup>

1 = Analog-to-digital conversion is done

0 = Analog-to-digital conversion is not done or has not started Clearing this bit will not affect any operation in progress.

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC = 0, software can write a '0' to end sampling and start conversion. If SSRC ≠ '0', this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

#### 24.1 Comparator Voltage Reference Control Register

| <b>TABLE 24-1</b> : | COMPARATOR VOLTAGE REFERENCE REGISTER MAP |

|---------------------|-------------------------------------------|

|---------------------|-------------------------------------------|

| ress<br>t)               |                                 | Ð         |       |       |       |       |       |       |      | Bits | i    |       |      |       |      |      |      |      | ŝ          |

|--------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|-------|------|-------|------|------|------|------|------------|

| Virtual Addr<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6  | 21/5 | 20/4  | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 0000                     |                                 | 31:16     | _     | _     | —     | —     | —     | —     | _    | _    | —    | —     | —    | _     | —    | _    | _    | —    | 0000       |

| 9800                     | CVRCON                          | 15:0      | ON    | _     | _     | _     | _     | _     | _    | _    | _    | CVROE | CVRR | CVRSS |      | CVR< | 3:0> |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| АС СНА        | RACTERI       | ISTICS                                                                                                           | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                        |             |            |                                              |  |  |  |  |

|---------------|---------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------|-------------|------------|----------------------------------------------|--|--|--|--|

| Param.<br>No. | Symbol        | Characteristics                                                                                                  | Min.                                                  | Typical <sup>(1)</sup> | Max.        | Units      | Conditions                                   |  |  |  |  |

| OS10          | Fosc          | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes)                               | DC<br>4                                               |                        | 40<br>40    | MHz<br>MHz | EC (Note 4)<br>ECPLL (Note 3)                |  |  |  |  |

| OS11          |               | Oscillator Crystal Frequency                                                                                     | 3                                                     | —                      | 10          | MHz        | XT (Note 4)                                  |  |  |  |  |

| OS12          |               |                                                                                                                  | 4                                                     | —                      | 10          | MHz        | XTPLL<br>(Notes 3,4)                         |  |  |  |  |

| OS13          |               |                                                                                                                  | 10                                                    | —                      | 25          | MHz        | HS (Note 5)                                  |  |  |  |  |

| OS14          |               |                                                                                                                  | 10                                                    | -                      | 25          | MHz        | HSPLL<br>(Notes 3,4)                         |  |  |  |  |

| OS15          |               |                                                                                                                  | 32                                                    | 32.768                 | 100         | kHz        | Sosc (Note 4)                                |  |  |  |  |

| OS20          | Tosc          | Tosc = 1/Fosc = Tcy (Note 2)                                                                                     | _                                                     | —                      | _           | —          | See parameter<br>OS10 for Fosc<br>value      |  |  |  |  |

| OS30          | TosL,<br>TosH | External Clock In (OSC1)<br>High or Low Time                                                                     | 0.45 x Tosc                                           | -                      | —           | ns         | EC (Note 4)                                  |  |  |  |  |

| OS31          | TosR,<br>TosF | External Clock In (OSC1)<br>Rise or Fall Time                                                                    | —                                                     | —                      | 0.05 x Tosc | ns         | EC (Note 4)                                  |  |  |  |  |

| OS40          | Tost          | Oscillator Start-up Timer Period<br>(Only applies to HS, HSPLL,<br>XT, XTPLL and Sosc Clock<br>Oscillator modes) | _                                                     | 1024                   | _           | Tosc       | (Note 4)                                     |  |  |  |  |

| OS41          | TFSCM         | Primary Clock Fail Safe<br>Time-out Period                                                                       | —                                                     | 2                      | —           | ms         | (Note 4)                                     |  |  |  |  |

| OS42          | Gм            | External Oscillator<br>Transconductance (Primary<br>Oscillator only)                                             | _                                                     | 12                     | —           | mA/V       | VDD = 3.3V,<br>TA = +25°C<br><b>(Note 4)</b> |  |  |  |  |

#### TABLE 30-17: EXTERNAL CLOCK TIMING REQUIREMENTS

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are characterized but are not tested.

2: Instruction cycle period (Tcr) equals the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin.

3: PLL input requirements: 4 MHz  $\leq$  FPLLIN  $\leq$  5 MHz (use PLL prescaler to reduce FOSC). This parameter is characterized, but tested at 10 MHz only at manufacturing.

4: This parameter is characterized, but not tested in manufacturing.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### FIGURE 30-10: SPIx MODULE MASTER MODE (CKE = 0) TIMING CHARACTERISTICS SCKx (CKP = 0) SP11 SP10 SP21 SP20 SCKx (CKP = 1) SP35 SP20 SP21 SDOx MSb Bit 14 -1 LSb **SP31 SP30** SDIx LSb In MSb In Bit 14 SP40 'SP41' Note: Refer to Figure 30-1 for load conditions.

#### TABLE 30-28: SPIx MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHA        | RACTERIST             | TICS                                       | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |      |       |                    |  |  |  |  |

|---------------|-----------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|--|--|--|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>             | Min.                                                                                                                                                                                                                                                                                  | Typical <sup>(2)</sup> | Max. | Units | Conditions         |  |  |  |  |

| SP10          | TscL                  | SCKx Output Low Time<br>(Note 3)           | Тѕск/2                                                                                                                                                                                                                                                                                | _                      |      | ns    | _                  |  |  |  |  |

| SP11          | TscH                  | SCKx Output High Time<br>(Note 3)          | Тѕск/2                                                                                                                                                                                                                                                                                | —                      | _    | ns    | _                  |  |  |  |  |

| SP20          | TscF                  | SCKx Output Fall Time (Note 4)             | —                                                                                                                                                                                                                                                                                     | —                      |      | ns    | See parameter DO32 |  |  |  |  |

| SP21          | TscR                  | SCKx Output Rise Time (Note 4)             | —                                                                                                                                                                                                                                                                                     | —                      | _    | ns    | See parameter DO31 |  |  |  |  |

| SP30          | TDOF                  | SDOx Data Output Fall Time (Note 4)        | —                                                                                                                                                                                                                                                                                     | —                      | _    | ns    | See parameter DO32 |  |  |  |  |

| SP31          | TDOR                  | SDOx Data Output Rise Time (Note 4)        | —                                                                                                                                                                                                                                                                                     | —                      | _    | ns    | See parameter DO31 |  |  |  |  |

| SP35          | TscH2doV,             | SDOx Data Output Valid after               | —                                                                                                                                                                                                                                                                                     | —                      | 15   | ns    | VDD > 2.7V         |  |  |  |  |

|               | TscL2doV              | SCKx Edge                                  |                                                                                                                                                                                                                                                                                       | _                      | 20   | ns    | VDD < 2.7V         |  |  |  |  |

| SP40          | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge | 10                                                                                                                                                                                                                                                                                    | —                      | —    | ns    | —                  |  |  |  |  |

| SP41          | TSCH2DIL,<br>TSCL2DIL | Hold Time of SDIx Data Input to SCKx Edge  | 10                                                                                                                                                                                                                                                                                    | —                      |      | ns    |                    |  |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 50 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

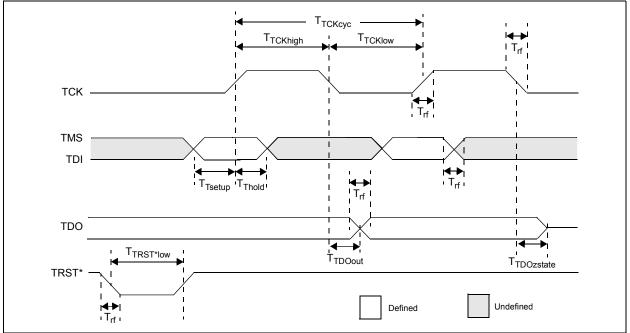

#### FIGURE 30-23: EJTAG TIMING CHARACTERISTICS

#### TABLE 30-42: EJTAG TIMING REQUIREMENTS

| AC CHA        | RACTERISTI | CS                                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industri} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-tem} \end{array}$ |      |       |            |  |  |  |  |

|---------------|------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|--|--|

| Param.<br>No. | Symbol     | Description <sup>(1)</sup>                       | Min.                                                                                                                                                                                                                                                                               | Max. | Units | Conditions |  |  |  |  |

| EJ1           | Ттсксус    | TCK Cycle Time                                   | 25                                                                                                                                                                                                                                                                                 |      | ns    | _          |  |  |  |  |

| EJ2           | Ттскнідн   | TCK High Time                                    | 10                                                                                                                                                                                                                                                                                 | _    | ns    | —          |  |  |  |  |

| EJ3           | TTCKLOW    | TCK Low Time                                     | 10                                                                                                                                                                                                                                                                                 | _    | ns    | _          |  |  |  |  |

| EJ4           | TTSETUP    | TAP Signals Setup Time Before<br>Rising TCK      | 5                                                                                                                                                                                                                                                                                  | _    | ns    | _          |  |  |  |  |

| EJ5           | TTHOLD     | TAP Signals Hold Time After<br>Rising TCK        | 3                                                                                                                                                                                                                                                                                  | -    | ns    | —          |  |  |  |  |

| EJ6           | Ττροουτ    | TDO Output Delay Time from<br>Falling TCK        | -                                                                                                                                                                                                                                                                                  | 5    | ns    | —          |  |  |  |  |

| EJ7           | TTDOZSTATE | TDO 3-State Delay Time from<br>Falling TCK       | _                                                                                                                                                                                                                                                                                  | 5    | ns    | _          |  |  |  |  |

| EJ8           | TTRSTLOW   | TRST Low Time                                    | 25                                                                                                                                                                                                                                                                                 |      | ns    |            |  |  |  |  |

| EJ9           | Trf        | TAP Signals Rise/Fall Time, All Input and Output | —                                                                                                                                                                                                                                                                                  | _    | ns    | _          |  |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

#### TABLE 31-8:SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| АС СНА        | ARACTERIS | TICS                                                   | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |      |      |       |            |  |  |  |

|---------------|-----------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|--|--|--|

| Param.<br>No. | Symbol    | Characteristics                                        | Min.                                                                                                                                                                                                          | Тур. | Max. | Units | Conditions |  |  |  |

| MSP70         | TscL      | SCKx Input Low Time (Note 1,2)                         | Tsck/2                                                                                                                                                                                                        |      | _    | ns    | _          |  |  |  |

| MSP71         | TscH      | SCKx Input High Time (Note 1,2)                        | Tsck/2                                                                                                                                                                                                        | —    |      | ns    | —          |  |  |  |

| MSP51         | TssH2doZ  | SSx ↑ to SDOx Output<br>High-Impedance <b>(Note 2)</b> | 5                                                                                                                                                                                                             |      | 25   | ns    | —          |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns.

#### TABLE 31-9: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        | RACTERIS | TICS                            | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |      |       |            |   |  |  |  |

|---------------|----------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|---|--|--|--|

| Param.<br>No. | Symbol   | Min.                            | Typical                                                                                                                                           | Max. | Units | Conditions |   |  |  |  |

| SP70          | TscL     | SCKx Input Low Time (Note 1,2)  | Tsck/2                                                                                                                                            |      |       | ns         |   |  |  |  |

| SP71          | TscH     | SCKx Input High Time (Note 1,2) | Tsck/2                                                                                                                                            | _    | _     | ns         | _ |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns.

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support