Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx150f128d-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 5: PIN NAMES FOR 28-PIN GENERAL PURPOSE DEVICES

#### 28-PIN QFN (TOP VIEW)<sup>(1,2,3.4)</sup>

PIC32MX110F016B PIC32MX120F032B PIC32MX130F064B PIC32MX130F256B PIC32MX150F128B PIC32MX170F256B

28

1

| Pin # | Full Pin Name                         | Pin # | Full Pin Name                                  |

|-------|---------------------------------------|-------|------------------------------------------------|

| 1     | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0  | 15    | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 2     | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1 | 16    | Vss                                            |

| 3     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2  | 17    | VCAP                                           |

| 4     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3    | 18    | PGED2/RPB10/CTED11/PMD2/RB10                   |

| 5     | Vss                                   | 19    | PGEC2/TMS/RPB11/PMD1/RB11                      |

| 6     | OSC1/CLKI/RPA2/RA2                    | 20    | AN12/PMD0/RB12                                 |

| 7     | OSC2/CLKO/RPA3/PMA0/RA3               | 21    | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 8     | SOSCI/RPB4/RB4                        | 22    | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 9     | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4        | 23    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 10    | Vdd                                   | 24    | AVss                                           |

| 11    | PGED3/RPB5/PMD7/RB5                   | 25    | AVDD                                           |

| 12    | PGEC3/RPB6/PMD6/RB6                   | 26    | MCLR                                           |

| 13    | TDI/RPB7/CTED3/PMD5/INT0/RB7          | 27    | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          |

| 14    | TCK/RPB8/SCL1/CTED10/PMD4/RB8         | 28    | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                |

1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: Shaded pins are 5V tolerant.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

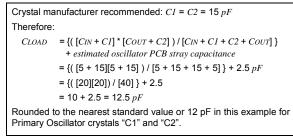

#### 2.8.1 CRYSTAL OSCILLATOR DESIGN CONSIDERATION

The following example assumptions are used to calculate the Primary Oscillator loading capacitor values:

- CIN = PIC32\_OSC2\_Pin Capacitance = ~4-5 pF

- COUT = PIC32\_OSC1\_Pin Capacitance = ~4-5 pF

- C1 and C2 = XTAL manufacturing recommended loading capacitance

- Estimated PCB stray capacitance, (i.e.,12 mm length) = 2.5 pF

#### EXAMPLE 2-1: CRYSTAL LOAD CAPACITOR CALCULATION

The following tips are used to increase oscillator gain, (i.e., to increase peak-to-peak oscillator signal):

- Select a crystal with a lower "minimum" power drive rating

- Select an crystal oscillator with a lower XTAL manufacturing "ESR" rating.

- Add a parallel resistor across the crystal. The smaller the resistor value the greater the gain. It is recommended to stay in the range of 600k to 1M

- C1 and C2 values also affect the gain of the oscillator. The lower the values, the higher the gain.

- C2/C1 ratio also affects gain. To increase the gain, make C1 slightly smaller than C2, which will also help start-up performance.

- Note: Do not add excessive gain such that the oscillator signal is clipped, flat on top of the sine wave. If so, you need to reduce the gain or add a series resistor, RS, as shown in circuit "C" in Figure 2-4. Failure to do so will stress and age the crystal, which can result in an early failure. Adjust the gain to trim the max peak-to-peak to ~VDD-0.6V. When measuring the oscillator signal you must use a FET scope probe or a probe with ≤ 1.5 pF or the scope probe itself will unduly change the gain and peak-to-peak levels.

#### 2.8.1.1 Additional Microchip References

- AN588 "PICmicro<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826 "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849 "Basic PICmicro<sup>®</sup> Oscillator Design"

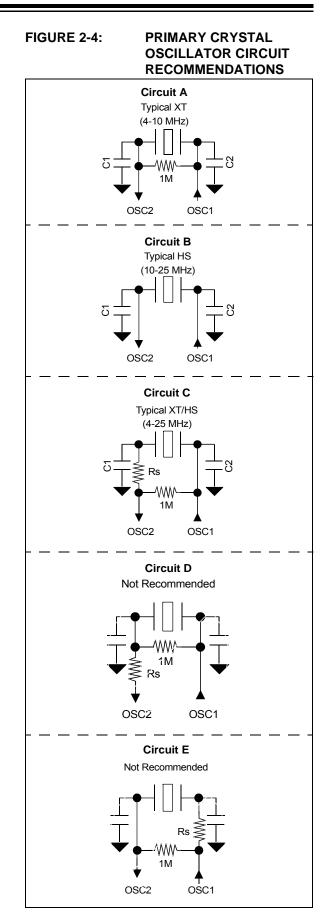

#### 3.0 CPU

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS60001113), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). Resources for the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core are available at: www.imgtec.com.

The MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core is the heart of the PIC32MX1XX/2XX family processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the destinations.

#### 3.1 Features

- 5-stage pipeline

- 32-bit address and data paths

- MIPS32 Enhanced Architecture (Release 2)

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- Bit field manipulation instructions

- MIPS16e<sup>®</sup> code compression

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE and RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8 and 16-bit data types

- Simple Fixed Mapping Translation (FMT) mechanism

- · Simple dual bus interface

- Independent 32-bit address and data buses

- Transactions can be aborted to improve interrupt latency

- · Autonomous multiply/divide unit

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (*rs*) sign extension-dependent)

- Power control

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- EJTAG debug and instruction trace

- Support for single stepping

- Virtual instruction and data address/value

- Breakpoints

#### FIGURE 3-1: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE BLOCK DIAGRAM

#### 4.2 Bus Matrix Control Registers

#### TABLE 4-2: BUS MATRIX REGISTER MAP

| ess (                       |                         | a                   |       |                |       |       |       |       |      |      |      | Bits         |      |           |           |           |            |          |               |

|-----------------------------|-------------------------|---------------------|-------|----------------|-------|-------|-------|-------|------|------|------|--------------|------|-----------|-----------|-----------|------------|----------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name        | Bit Range           | 31/15 | 30/14          | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6         | 21/5 | 20/4      | 19/3      | 18/2      | 17/1       | 16/0     | All<br>Resets |

| 2000                        | BMXCON <sup>(1)</sup>   | 31:16               | —     | _              | _     | _     | -     | _     | _    | _    |      | —            | _    | BMXERRIXI | BMXERRICD | BMXERRDMA | BMXERRDS   | BMXERRIS | 001F          |

| 2000                        |                         | 15:0                |       |                | _     | _     |       | -     |      | _    |      | BMXWSDRM     | _    | _         | -         | В         | MXARB<2:0> |          | 0041          |

| 2010                        |                         | AA(1) 31:16         |       |                |       |       |       |       |      |      | —    | 0000         |      |           |           |           |            |          |               |

| 2010                        | DIVIAUNEDA              |                     |       |                |       |       |       |       |      |      |      | 0000         |      |           |           |           |            |          |               |

| 2020                        | BMXDUDBA <sup>(1)</sup> | 31:16               |       |                |       |       |       |       |      |      | _    | 0000         |      |           |           |           |            |          |               |

|                             |                         | 15:0 BMXDUDBA<15:0> |       |                |       |       |       |       |      |      |      |              | 0000 |           |           |           |            |          |               |

| 2030                        | BMXDUPBA <sup>(1)</sup> | 31:16               | —     | —              | —     |       | —     | —     | —    | —    | —    | —            | —    | —         | —         | —         | —          | —        | 0000          |

| 2000                        |                         | 15:0                |       |                |       |       |       |       |      |      | BN   | IXDUPBA<15:0 | >    |           |           |           |            |          | 0000          |

| 2040                        | BMXDRMSZ                | 31:16               |       | BMXDRMSZ<31:0> |       |       |       |       |      |      |      |              |      |           |           |           | xxxx       |          |               |

|                             |                         | 15:0                |       |                |       | 1     |       |       |      | 1    |      |              |      | 1         |           |           |            |          | xxxx          |

| 2050                        | BMXPUPBA <sup>(1)</sup> | 31:16               | —     | —              | —     |       | —     | -     | —    | _    | _    | _            | —    | —         |           | BMXPUPBA  | <19:16>    |          | 0000          |

|                             |                         | 15:0                |       |                |       |       |       |       |      |      | BN   | IXPUPBA<15:0 | >    |           |           |           |            |          | 0000          |

| 2060                        | BMXPFMSZ                | 31:16               |       |                |       |       |       |       |      |      | BM   | IXPFMSZ<31:0 | >    |           |           |           |            |          | xxxx          |

| 2000                        | 2                       | 15:0                |       |                |       |       |       |       |      |      | 5.   |              |      |           |           |           |            |          | xxxx          |

| 2070                        | BMXBOOTSZ               | 31:16               |       |                |       |       |       |       |      |      | BM   | XBOOTSZ<31:0 | )>   |           |           |           |            |          | 0000          |

|                             | # (20010E               | 15:0                |       |                |       |       |       |       |      |      |      |              |      |           |           |           |            |          | 0C00          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| ILCIOI I     |                   |                   |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | —                 | —                 |                   | —                | —                |

|              | U-0               | U-0               | U-0               | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |

| 23:16        | _                 | —                 | _                 | BMX<br>ERRIXI     | BMX<br>ERRICD     | BMX<br>ERRDMA     | BMX<br>ERRDS     | BMX<br>ERRIS     |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | —                 | -                 | —                 | _                 |                  | —                |

|              | U-0               | R/W-1             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-1            |

| 7:0          | _                 | BMX<br>WSDRM      | _                 | _                 | _                 | E                 | 3MXARB<2:0       | >                |

#### REGISTER 4-1: BMXCON: BUS MATRIX CONFIGURATION REGISTER

#### Legend:

| 5                 |                  |                                    |

|-------------------|------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

#### bit 31-21 Unimplemented: Read as '0'

|          | Ommplemented. Read as 0                                                                                                                                                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 20   | BMXERRIXI: Enable Bus Error from IXI bit                                                                                                                                                                                              |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> </ul>                 |

| bit 19   | BMXERRICD: Enable Bus Error from ICD Debug Unit bit                                                                                                                                                                                   |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from ICD</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from ICD</li> </ul>                                       |

| bit 18   | BMXERRDMA: Bus Error from DMA bit                                                                                                                                                                                                     |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from DMA</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from DMA</li> </ul>                                       |

| bit 17   | BMXERRDS: Bus Error from CPU Data Access bit (disabled in Debug mode)                                                                                                                                                                 |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU data access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU data access</li> </ul>               |

| bit 16   | BMXERRIS: Bus Error from CPU Instruction Access bit (disabled in Debug mode)                                                                                                                                                          |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> </ul> |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 6    | BMXWSDRM: CPU Instruction or Data Access from Data RAM Wait State bit                                                                                                                                                                 |

|          | <ul> <li>1 = Data RAM accesses from CPU have one wait state for address setup</li> <li>0 = Data RAM accesses from CPU have zero wait states for address setup</li> </ul>                                                              |

| bit 5-3  | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 2-0  | BMXARB<2:0>: Bus Matrix Arbitration Mode bits                                                                                                                                                                                         |

|          | 111 = Reserved (using these Configuration modes will produce undefined behavior)                                                                                                                                                      |

|          | •                                                                                                                                                                                                                                     |

|          | •                                                                                                                                                                                                                                     |

|          | <ul><li>011 = Reserved (using these Configuration modes will produce undefined behavior)</li><li>010 = Arbitration Mode 2</li></ul>                                                                                                   |

|          | 001 = Arbitration Mode 1 (default)<br>000 = Arbitration Mode 0                                                                                                                                                                        |

|          |                                                                                                                                                                                                                                       |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | -                 | _                 | _                 | _                 | _                 |                   | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | —                 | —                 | _                 | _                 | —                 | —                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |

| 15:8         |                   |                   |                   | BMXDK             | PBA<15:8>         |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | BMXDK             | PBA<7:0>          |                   |                  |                  |

#### REGISTER 4-2: BMXDKPBA: DATA RAM KERNEL PROGRAM BASE ADDRESS REGISTER

#### Legend:

| Legenu.           |                  |                           |                    |  |  |  |  |  |  |

|-------------------|------------------|---------------------------|--------------------|--|--|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |  |  |  |  |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 **BMXDKPBA<15:10>:** DRM Kernel Program Base Address bits When non-zero, this value selects the relative base address for kernel program space in RAM

bit 9-0 BMXDKPBA<9:0>: Read-Only bits This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

#### 10.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 Full-Speed and Low-Speed embedded host, Full-Speed device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 10-1.

The clock generator provides the 48 MHz clock required for USB Full-Speed and Low-Speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module. The PIC32 USB module includes the following features:

- · USB Full-Speed support for Host and Device

- Low-Speed Host support

- USB OTG support

- · Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- · Transaction handshaking performed by hardware

- · Endpoint buffering anywhere in system RAM

- · Integrated DMA to access system RAM and Flash

- Note: The implementation and use of the USB specifications, as well as other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc., also referred to as USB-IF (www.usb.org). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

#### REGISTER 10-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 **PPBRST:** Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the EVEN Buffer Descriptor banks

- 0 = Even/Odd buffer pointers are not Reset

- bit 0 USBEN: USB Module Enable bit<sup>(4)</sup>

- 1 = USB module and supporting circuitry is enabled

- 0 = USB module and supporting circuitry is disabled

SOFEN: SOF Enable bit<sup>(5)</sup>

- 1 = SOF token is sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.0         | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |  |

| 7:0          | —                 | —                 | _                 | —                 | —                 |                   | FRMH<2:0>        |                  |  |

#### REGISTER 10-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

#### Legend:

| 0                 |                  |                                    |                    |  |  |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |  |  |

bit 31-3 Unimplemented: Read as '0'

bit 2-0 **FRMH<2:0>:** The Upper 3 bits of the Frame Numbers bits The register bits are updated with the current frame number whenever a SOF TOKEN is received.

#### Bit Bit Bit Bit Bit Bit Bit Bit Bit 30/22/14/6 27/19/11/3 26/18/10/2 25/17/9/1 24/16/8/0 Range 31/23/15/7 29/21/13/5 28/20/12/4 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 31:24 \_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 23:16 \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 15:8 \_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 7:0 PID < 3:0 > (1)EP<3:0>

#### **REGISTER 10-15: U1TOK: USB TOKEN REGISTER**

| Legend:                           |                  |                                    |                    |  |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit                  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| n = Value at POR '1' = Bit is set |                  | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-4 **PID<3:0>:** Token Type Indicator bits<sup>(1)</sup>

1101 = SETUP (TX) token type transaction

- 1001 = IN (RX) token type transaction

- 0001 = OUT (TX) token type transaction

Note: All other values are reserved and must not be used.

bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits The four bit value must specify a valid endpoint.

Note 1: All other values are reserved and must not be used.

#### 12.2 Timer1 Control Registers

#### TABLE 12-1: TIMER1 REGISTER MAP

| ess                       | Register<br>Name <sup>(1)</sup> | 0         |       |       |       |       |       |       |      | В    | its    |      |       |        |      |       |      |      | s          |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|--------|------|-------|--------|------|-------|------|------|------------|

| Virtual Addre<br>(BF80_#) |                                 | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7   | 22/6 | 21/5  | 20/4   | 19/3 | 18/2  | 17/1 | 16/0 | All Resets |

| 0600                      | T1CON                           | 31:16     | _     | _     | _     | _     | _     | —     | _    | —    | _      | —    | —     | —      | _    | —     | _    | _    | 0000       |

| 0600                      | TICON                           | 15:0      | ON    | —     | SIDL  | TWDIS | TWIP  | —     | _    | —    | TGATE  | _    | TCKPS | S<1:0> | —    | TSYNC | TCS  | _    | 0000       |

| 0610                      | TMR1                            | 31:16     | —     | -     | —     | —     | —     | —     | —    | —    | —      | —    | _     | _      | —    | —     | —    | —    | 0000       |

| 0010                      | 15:0 TMR1<15:0>                 |           |       |       |       |       |       |       |      | 0000 |        |      |       |        |      |       |      |      |            |

| 0620                      | PR1                             | 31:16     | —     | _     | _     | _     | _     | —     | -    | —    | —      | _    | —     | _      | _    | _     | _    |      | 0000       |

| 0020                      | FRI                             | 15:0      |       |       |       |       |       |       |      | PR1< | :15:0> |      |       |        |      |       |      |      | FFFF       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7        | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1    | Bit<br>24/16/8/0    |

|--------------|--------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|

| 21.24        | U-0                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0                 |

| 31:24        |                          | -                 | _                 | -                 | _                 |                   | _                   | _                   |

| 00.40        | U-0                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0                 |

| 23:16        | _                        | _                 | _                 | _                 | _                 | —                 | _                   | _                   |

| 45.0         | R/W-0                    | U-0               | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0               | R/W-0               |

| 15:8         | ON <sup>(1)</sup> — SIDL |                   | SIDL              | _                 | _                 | FORM<2:0>         |                     |                     |

| 7.0          | R/W-0                    | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0, HSC          | R/C-0, HSC          |

| 7:0          |                          | SSRC<2:0>         |                   | CLRASAM           |                   | ASAM              | SAMP <sup>(2)</sup> | DONE <sup>(3)</sup> |

#### REGISTER 22-1: AD1CON1: ADC CONTROL REGISTER 1

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** ADC Operating Mode bit<sup>(1)</sup>

- 1 = ADC module is operating

- 0 = ADC module is not operating

- bit 14 **Unimplemented:** Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

#### bit 12-11 Unimplemented: Read as '0'

- bit 10-8 **FORM<2:0>:** Data Output Format bits

- 111 = Signed Fractional 32-bit (DOUT = sddd dddd dd00 0000 0000 0000 0000)

- 110 = Fractional 32-bit (DOUT = dddd dddd dd00 0000 0000 0000 0000)

- 101 = Signed Integer 32-bit (DOUT = ssss ssss ssss ssss ssss sssd dddd dddd)

- 100 = Integer 32-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

- 011 = Signed Fractional 16-bit (DOUT = 0000 0000 0000 0000 sddd dddd dd00 0000)

- 010 = Fractional 16-bit (DOUT = 0000 0000 0000 0000 dddd dddd dd00 0000)

- 000 =Integer 16-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

#### bit 7-5 SSRC<2:0>: Conversion Trigger Source Select bits

- 111 = Internal counter ends sampling and starts conversion (auto convert)

- 110 = Reserved

- 101 = Reserved

- 100 = Reserved

- 011 = CTMU ends sampling and starts conversion

- 010 = Timer 3 period match ends sampling and starts conversion

- 001 = Active transition on INT0 pin ends sampling and starts conversion

- 000 = Clearing SAMP bit ends sampling and starts conversion

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC = 0, software can write a '0' to end sampling and start conversion. If SSRC ≠ '0', this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

NOTES:

| DC CHARACTERISTICS |        |                     |                    | $\label{eq:standard operating Conditions: 2.3V to 3.6V} \end{tabular} \begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |       |                                                     |  |

|--------------------|--------|---------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------|-----|-------|-----------------------------------------------------|--|

| Param.             | Symbol | Characteristic      | Min. Typ. Max.     |                                                                                                                            |     | Units | Conditions                                          |  |

| DO10               | Vol    | Output Low Voltage  | _                  | _                                                                                                                          | 0.4 | V     | $\text{IOL} \leq 10 \text{ mA, VDD} = 3.3 \text{V}$ |  |

|                    |        | Output High Voltage | 1.5(1)             | _                                                                                                                          | _   | V     | IOH $\geq$ -14 mA, VDD = 3.3V                       |  |

| 0000               | Vон    | I/O Pins            | 2.0 <sup>(1)</sup> | _                                                                                                                          | _   |       | IOH $\geq$ -12 mA, VDD = 3.3V                       |  |

| DO20               | VOH    |                     | 2.4                | _                                                                                                                          | _   | v     | IOH $\geq$ -10 mA, VDD = 3.3V                       |  |

|                    |        |                     | 3.0(1)             | —                                                                                                                          | —   |       | $IOH \ge -7 \text{ mA}, \text{ VDD} = 3.3 \text{V}$ |  |

#### TABLE 30-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

Note 1: Parameters are characterized, but not tested.

#### TABLE 30-11: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        |                                                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |         |      |       |            |  |

|--------------------|--------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|

| Param.<br>No.      | Symbol | Characteristics                                           | Min. <sup>(1)</sup>                                                                                                                                                                                                                                                               | Typical | Max. | Units | Conditions |  |

| BO10               | VBOR   | BOR Event on VDD transition<br>high-to-low <sup>(2)</sup> | 2.0                                                                                                                                                                                                                                                                               | —       | 2.3  | V     | _          |  |

**Note 1:** Parameters are for design guidance only and are not tested in manufacturing.

2: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN.

### PIC32MX1XX/2XX 28/36/44-PIN FAMILY

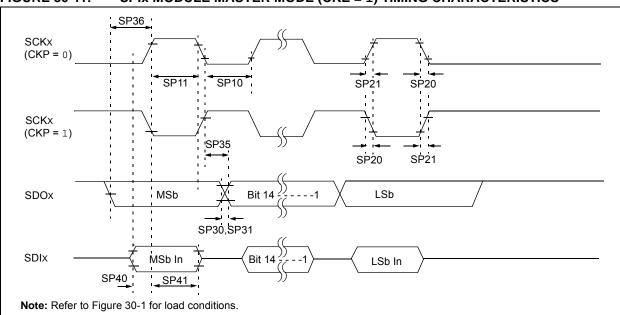

#### FIGURE 30-11: SPIX MODULE MASTER MODE (CKE = 1) TIMING CHARACTERISTICS

#### TABLE 30-29: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        |                      | rics                                         | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                     |      |       |                    |

|---------------|----------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|

| Param.<br>No. | Symbol               | Characteristics <sup>(1)</sup>               | Min.                                                                                                                                                                                                                                                                                | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |

| SP10          | TscL                 | SCKx Output Low Time (Note 3)                | Tsck/2                                                                                                                                                                                                                                                                              | —                   | _    | ns    | _                  |

| SP11          | TscH                 | SCKx Output High Time (Note 3)               | Tsck/2                                                                                                                                                                                                                                                                              | —                   | _    | ns    | —                  |

| SP20          | TscF                 | SCKx Output Fall Time (Note 4)               | —                                                                                                                                                                                                                                                                                   | —                   | —    | ns    | See parameter DO32 |

| SP21          | TscR                 | SCKx Output Rise Time (Note 4)               | _                                                                                                                                                                                                                                                                                   | _                   | _    | ns    | See parameter DO31 |

| SP30          | TDOF                 | SDOx Data Output Fall Time (Note 4)          | _                                                                                                                                                                                                                                                                                   | —                   | _    | ns    | See parameter DO32 |

| SP31          | TDOR                 | SDOx Data Output Rise Time (Note 4)          | _                                                                                                                                                                                                                                                                                   | _                   | _    | ns    | See parameter DO31 |

| SP35          | TscH2doV,            | SDOx Data Output Valid after                 |                                                                                                                                                                                                                                                                                     |                     | 15   | ns    | VDD > 2.7V         |

|               | TscL2DoV             | SCKx Edge                                    | _                                                                                                                                                                                                                                                                                   |                     | 20   | ns    | VDD < 2.7V         |

| SP36          | TDOV2SC,<br>TDOV2SCL | SDOx Data Output Setup to<br>First SCKx Edge | 15                                                                                                                                                                                                                                                                                  | —                   | _    | ns    | —                  |

| SP40          | TDIV2scH,            | Setup Time of SDIx Data Input to             | 15                                                                                                                                                                                                                                                                                  | _                   | _    | ns    | VDD > 2.7V         |

|               | TDIV2scL             | SCKx Edge                                    | 20                                                                                                                                                                                                                                                                                  | —                   |      | ns    | VDD < 2.7V         |

| SP41          | TscH2DIL,            | Hold Time of SDIx Data Input                 | 15                                                                                                                                                                                                                                                                                  | —                   | _    | ns    | VDD > 2.7V         |

|               | TscL2DIL             | to SCKx Edge                                 | 20                                                                                                                                                                                                                                                                                  | —                   | _    | ns    | VDD < 2.7V         |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 50 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

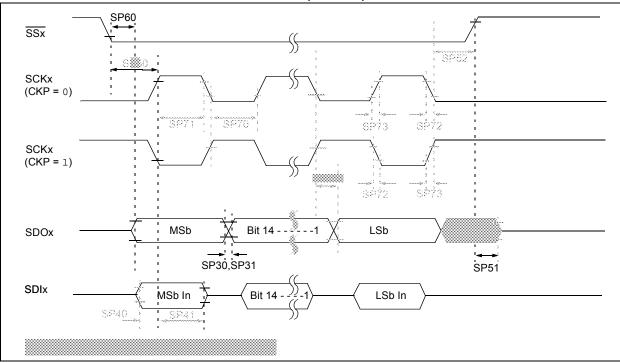

#### FIGURE 30-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

#### TABLE 30-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        | RACTERIS              | TICS                                                                      | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                        |      |       |                    |  |

|---------------|-----------------------|---------------------------------------------------------------------------|-------------------------------------------------------|------------------------|------|-------|--------------------|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                                            | Min.                                                  | Typical <sup>(2)</sup> | Max. | Units | Conditions         |  |

| SP70          | TscL                  | SCKx Input Low Time (Note 3)                                              | Tsck/2                                                | _                      | _    | ns    | —                  |  |

| SP71          | TscH                  | SCKx Input High Time (Note 3)                                             | Tsck/2                                                | —                      | _    | ns    | —                  |  |

| SP72          | TscF                  | SCKx Input Fall Time                                                      | _                                                     | 5                      | 10   | ns    | —                  |  |

| SP73          | TscR                  | SCKx Input Rise Time                                                      | —                                                     | 5                      | 10   | ns    | —                  |  |

| SP30          | TDOF                  | SDOx Data Output Fall Time (Note 4)                                       | —                                                     | —                      | _    | ns    | See parameter DO32 |  |

| SP31          | TDOR                  | SDOx Data Output Rise Time (Note 4)                                       | —                                                     | —                      | _    | ns    | See parameter DO31 |  |

| SP35          | TscH2doV,             | SDOx Data Output Valid after                                              | _                                                     | —                      | 20   | ns    | VDD > 2.7V         |  |

|               | TscL2DoV              | SCKx Edge                                                                 | _                                                     | —                      | 30   | ns    | VDD < 2.7V         |  |

| SP40          | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge                                | 10                                                    | —                      | _    | ns    | —                  |  |

| SP41          | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                 | 10                                                    | —                      |      | ns    | —                  |  |

| SP50          | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ Input | 175                                                   | —                      |      | ns    | _                  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 50 ns.

- **4:** Assumes 50 pF load on all SPIx pins.

#### TABLE 30-32: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHA               |         | ISTICS                     |                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |                                |  |

|----------------------|---------|----------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------|--|

| Param.<br>No. Symbol |         | Charact                    | eristics                      | Min. <sup>(1)</sup>                                                                                                                                                                                                                                                                 | Max. | Units | Conditions                     |  |

| IM10                 | TLO:SCL | Clock Low Time             | 100 kHz mode TPB * (BRG +     |                                                                                                                                                                                                                                                                                     | _    | μs    | —                              |  |

|                      |         |                            | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                     |      | μS    | —                              |  |

|                      |         |                            | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                     | —    | μs    | _                              |  |

| IM11                 | THI:SCL | Clock High Time            | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                     |      | μS    | —                              |  |

|                      |         |                            | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                     | _    | μS    | —                              |  |

|                      |         |                            | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                     |      | μs    | -                              |  |

| IM20                 | TF:SCL  | SDAx and SCLx              | 100 kHz mode                  | —                                                                                                                                                                                                                                                                                   | 300  | ns    | CB is specified to be          |  |

|                      |         | Fall Time                  | 400 kHz mode                  | 20 + 0.1 Св                                                                                                                                                                                                                                                                         | 300  | ns    | from 10 to 400 pF              |  |

|                      |         |                            | 1 MHz mode<br><b>(Note 2)</b> | _                                                                                                                                                                                                                                                                                   | 100  | ns    |                                |  |

| IM21                 | TR:SCL  | SDAx and SCLx<br>Rise Time | 100 kHz mode                  | —                                                                                                                                                                                                                                                                                   | 1000 | ns    | CB is specified to be          |  |

|                      |         |                            | 400 kHz mode                  | 20 + 0.1 Св                                                                                                                                                                                                                                                                         | 300  | ns    | from 10 to 400 pF              |  |

|                      |         |                            | 1 MHz mode<br><b>(Note 2)</b> | _                                                                                                                                                                                                                                                                                   | 300  | ns    |                                |  |

| IM25 Tsu:d           | TSU:DAT | Data Input                 | 100 kHz mode                  | 250                                                                                                                                                                                                                                                                                 |      | ns    | —                              |  |

|                      |         | Setup Time                 | 400 kHz mode                  | 100                                                                                                                                                                                                                                                                                 | _    | ns    |                                |  |

|                      |         |                            | 1 MHz mode<br><b>(Note 2)</b> | 100                                                                                                                                                                                                                                                                                 |      | ns    |                                |  |

| IM26                 | THD:DAT | Data Input                 | 100 kHz mode                  | 0                                                                                                                                                                                                                                                                                   |      | μS    | —                              |  |

|                      |         | Hold Time                  | 400 kHz mode                  | 0                                                                                                                                                                                                                                                                                   | 0.9  | μS    |                                |  |

|                      |         |                            | 1 MHz mode<br>(Note 2)        | 0                                                                                                                                                                                                                                                                                   | 0.3  | μS    |                                |  |

| IM30                 | TSU:STA | Start Condition            | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                     |      | μS    | Only relevant for              |  |

|                      |         | Setup Time                 | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                     | _    | μS    | Repeated Start condition       |  |

|                      |         |                            | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                     | _    | μS    | condition                      |  |

| IM31                 | THD:STA | Start Condition            | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                     |      | μS    | After this period, the         |  |

|                      |         | Hold Time                  | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                     | -    | μS    | first clock pulse is generated |  |

|                      |         |                            | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                     |      | μS    | generaleu                      |  |

| IM33                 | Tsu:sto | Stop Condition             | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                     | _    | μS    |                                |  |

|                      |         | Setup Time                 | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                     |      | μS    |                                |  |

|                      |         |                            | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                     | _    | μs    |                                |  |

| IM34                 | THD:STO | Stop Condition             | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                     |      | ns    | —                              |  |

|                      |         | Hold Time                  | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                     | _    | ns    |                                |  |

|                      |         |                            | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                     | _    | ns    |                                |  |

**Note 1:** BRG is the value of the  $I^2C$  Baud Rate Generator.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** The typical value for this parameter is 104 ns.

#### TABLE 31-3: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARACT                                                     | ERISTICS               |      | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |        |  |  |  |  |

|----------------------------------------------------------------|------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|--|--|

| Parameter<br>No.                                               | Typical <sup>(2)</sup> | Max. | Units Conditions                                                                                                                                |        |  |  |  |  |

| Idle Current (IIDLE): Core Off, Clock on Base Current (Note 1) |                        |      |                                                                                                                                                 |        |  |  |  |  |

| MDC34a                                                         | 8                      | 13   | mA                                                                                                                                              | 50 MHz |  |  |  |  |

Note 1: The test conditions for IIDLE current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- + CPU is in Idle mode (CPU core Halted), and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

| DC CHAR                           | ACTERIST               | ICS     | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |            |                                                 |  |  |  |  |

|-----------------------------------|------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------------|--|--|--|--|

| Param.<br>No.                     | Typical <sup>(2)</sup> | Max.    | Units                                                                                                                                            | Conditions |                                                 |  |  |  |  |

| Power-Down Current (IPD) (Note 1) |                        |         |                                                                                                                                                  |            |                                                 |  |  |  |  |

| MDC40k                            | 10                     | 25      | μA                                                                                                                                               | -40°C      | Base Power-Down Current                         |  |  |  |  |

| MDC40n                            | 250                    | 500     | μA                                                                                                                                               | +85°C      | Base Power-Down Current                         |  |  |  |  |

| Module D                          | ifferential (          | Current |                                                                                                                                                  |            |                                                 |  |  |  |  |

| MDC41e                            | 10                     | 55      | μA                                                                                                                                               | 3.6V       | Watchdog Timer Current: AIWDT (Note 3)          |  |  |  |  |

| MDC42e                            | 23                     | 55      | μA                                                                                                                                               | 3.6V       | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3) |  |  |  |  |

| MDC43d                            | 1100                   | 1300    | μA                                                                                                                                               | 3.6V       | ADC: Aladc (Notes 3,4)                          |  |  |  |  |

#### TABLE 31-4: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** The test conditions for IPD current measurements are as follows:

• Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- · OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Sleep mode, and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

NOTES:

### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives