Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VFTLA Exposed Pad                                                           |

| Supplier Device Package    | 44-VTLA (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx150f128d-i-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 5: PIN NAMES FOR 28-PIN GENERAL PURPOSE DEVICES

#### 28-PIN QFN (TOP VIEW)<sup>(1,2,3.4)</sup>

PIC32MX110F016B PIC32MX120F032B PIC32MX130F064B PIC32MX130F256B PIC32MX150F128B PIC32MX170F256B

28

1

| Pin # | Full Pin Name                         | Pin # | Full Pin Name                                  |

|-------|---------------------------------------|-------|------------------------------------------------|

| 1     | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0  | 15    | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 2     | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1 | 16    | Vss                                            |

| 3     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2  | 17    | VCAP                                           |

| 4     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3    | 18    | PGED2/RPB10/CTED11/PMD2/RB10                   |

| 5     | Vss                                   | 19    | PGEC2/TMS/RPB11/PMD1/RB11                      |

| 6     | OSC1/CLKI/RPA2/RA2                    | 20    | AN12/PMD0/RB12                                 |

| 7     | OSC2/CLKO/RPA3/PMA0/RA3               | 21    | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 8     | SOSCI/RPB4/RB4                        | 22    | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 9     | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4        | 23    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 10    | Vdd                                   | 24    | AVss                                           |

| 11    | PGED3/RPB5/PMD7/RB5                   | 25    | AVDD                                           |

| 12    | PGEC3/RPB6/PMD6/RB6                   | 26    | MCLR                                           |

| 13    | TDI/RPB7/CTED3/PMD5/INT0/RB7          | 27    | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          |

| 14    | TCK/RPB8/SCL1/CTED10/PMD4/RB8         | 28    | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                |

1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: Shaded pins are 5V tolerant.

44

1

#### TABLE 14: PIN NAMES FOR 44-PIN USB DEVICES

#### 44-PIN VTLA (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX210F016D PIC32MX220F032D PIC32MX230F064D PIC32MX230F256D PIC32MX250F128D PIC32MX270F256D

| Pin # | Full Pin Name                                    | Pin # | Full Pin Name                             |

|-------|--------------------------------------------------|-------|-------------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                         | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 2     | RPC6/PMA1/RC6                                    | 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 3     | RPC7/PMA0/RC7                                    | 25    | AN6/RPC0/RC0                              |

| 4     | RPC8/PMA5/RC8                                    | 26    | AN7/RPC1/RC1                              |

| 5     | RPC9/CTED7/PMA6/RC9                              | 27    | AN8/RPC2/PMA2/RC2                         |

| 6     | Vss                                              | 28    | Vdd                                       |

| 7     | VCAP                                             | 29    | Vss                                       |

| 8     | PGED2/RPB10/D+/CTED11/RB10                       | 30    | OSC1/CLKI/RPA2/RA2                        |

| 9     | PGEC2/RPB11/D-/RB11                              | 31    | OSC2/CLKO/RPA3/RA3                        |

| 10    | VUSB3V3                                          | 32    | TDO/RPA8/PMA8/RA8                         |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                       | 33    | SOSCI/RPB4/RB4                            |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10             | 34    | SOSCO/RPA4/T1CK/CTED9/RA4                 |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7         | 35    | TDI/RPA9/PMA9/RA9                         |

| 14    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 | 36    | AN12/RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            | 37    | RPC4/PMA4/RC4                             |

| 16    | AVss                                             | 38    | RPC5/PMA3/RC5                             |

| 17    | AVDD                                             | 39    | Vss                                       |

| 18    | MCLR                                             | 40    | Vdd                                       |

| 19    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 | 41    | RPB5/USBID/RB5                            |

| 20    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       | 42    | VBUS                                      |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        | 43    | RPB7/CTED3/PMD5/INT0/RB7                  |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       | 44    | RPB8/SCL1/CTED10/PMD4/RB8                 |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX210F016D and PIC32MX220F032D devices.

5: Shaded pins are 5V tolerant.

#### 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to documents listed in the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

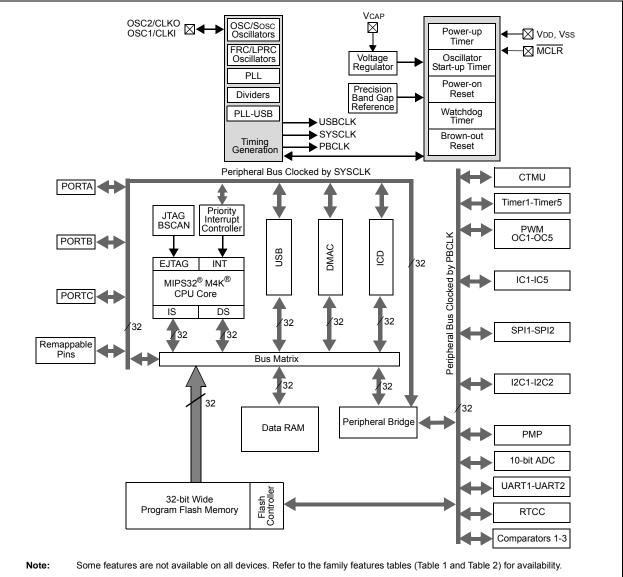

**BLOCK DIAGRAM**

This document contains device-specific information for PIC32MX1XX/2XX 28/36/44-pin Family devices.

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX1XX/2XX 28/36/44-pin Family of devices.

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

FIGURE 1-1:

# 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source.For detailed information, refer to **Section 3.** "Memory Organization" (DS60001115), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family microcontrollers provide 4 GB unified virtual memory address space. All memory regions, including program, data memory, Special Function Registers (SFRs), and Configuration registers, reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, the data memory can be made executable, allowing PIC32MX1XX/2XX 28/36/44-pin Family devices to execute from data memory.

Key features include:

- 32-bit native data width

- Separate User (KUSEG) and Kernel (KSEG0/KSEG1) mode address space

- · Flexible program Flash memory partitioning

- Flexible data RAM partitioning for data and program space

- Separate boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Simple memory mapping with Fixed Mapping Translation (FMT) unit

- Cacheable (KSEG0) and non-cacheable (KSEG1) address regions

# 4.1 PIC32MX1XX/2XX 28/36/44-pin Family Memory Layout

PIC32MX1XX/2XX 28/36/44-pin Family microcontrollers implement two address schemes: virtual and physical. All hardware resources, such as program memory, data memory and peripherals, are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by bus master peripherals, such as DMA and the Flash controller, that access memory independently of the CPU.

The memory maps for the PIC32MX1XX/2XX 28/36/44-pin Family devices are illustrated in Figure 4-1 through Figure 4-6.

Table 4-1 provides SFR memory map details.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | _                 | _                 | —                 | _                 | —                 | _                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | _                 | —                 | _                 | —                 | —                | —                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |

| 15:8         | BMXDUDBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | BMXDU             | DBA<7:0>          |                   |                  |                  |  |  |  |

### REGISTER 4-3: BMXDUDBA: DATA RAM USER DATA BASE ADDRESS REGISTER

# Legend:

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-10 BMXDUDBA<15:10>: DRM User Data Base Address bits

When non-zero, the value selects the relative base address for User mode data space in RAM, the value must be greater than BMXDKPBA.

#### bit 9-0 BMXDUDBA<9:0>: Read-Only bits This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

## REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER (CONTINUED)

bit 6 **CRCAPP:** CRC Append Mode bit<sup>(1)</sup>

- 1 = The DMA transfers data from the source into the CRC but NOT to the destination. When a block transfer completes the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC obeying WBO as it writes the data to the destination

- bit 5 **CRCTYP:** CRC Type Selection bit

- 1 = The CRC module will calculate an IP header checksum

- 0 = The CRC module will calculate a LFSR CRC

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 CRCCH<2:0>: CRC Channel Select bits

- 111 = CRC is assigned to Channel 7

- 110 = CRC is assigned to Channel 6

- 101 = CRC is assigned to Channel 5

- 100 = CRC is assigned to Channel 4

- 011 = CRC is assigned to Channel 3

- 010 = CRC is assigned to Channel 2

- 001 = CRC is assigned to Channel 1

- 000 = CRC is assigned to Channel 0

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

# 10.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 Full-Speed and Low-Speed embedded host, Full-Speed device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 10-1.

The clock generator provides the 48 MHz clock required for USB Full-Speed and Low-Speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module. The PIC32 USB module includes the following features:

- · USB Full-Speed support for Host and Device

- Low-Speed Host support

- USB OTG support

- · Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- · Transaction handshaking performed by hardware

- · Endpoint buffering anywhere in system RAM

- · Integrated DMA to access system RAM and Flash

- Note: The implementation and use of the USB specifications, as well as other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc., also referred to as USB-IF (www.usb.org). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

|              |                   |                   |                          |                   | -                     |                       |                  |                      |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

| 31:24        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 31.24        | —                 | —                 | —                        | _                 | —                     | —                     |                  | _                    |

| 22:16        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 23:16        | —                 | —                 | —                        | -                 | —                     | _                     | _                | _                    |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 15.0         | —                 | —                 | —                        | -                 | —                     | _                     | _                | _                    |

|              | R-x               | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |

| 7:0          | JSTATE            | TATE SE0          | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST           | USBEN <sup>(4)</sup> |

|              | JUNATE            | 320               | TOKBUSY <sup>(1,5)</sup> | USBROI            | TIOSTEIN /            | RESUMENT              | FFDROI           | SOFEN <sup>(5)</sup> |

#### REGISTER 10-11: U1CON: USB CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **JSTATE:** Live Differential Receiver JSTATE flag bit 1 = JSTATE was detected on the USB

- 0 = No JSTATE was detected on the

- bit 6 **SE0:** Live Single-Ended Zero flag bit 1 = Single-Ended Zero was detected on the USB

- 0 = No Single-Ended Zero was detected

- bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

- 1 = Token and packet processing is disabled (set upon SETUP token received)

- 0 = Token and packet processing is enabled

- TOKBUSY: Token Busy Indicator bit<sup>(1,5)</sup>

- 1 = Token is being executed by the USB module

- 0 = No token is being executed

#### bit 4 USBRST: Module Reset bit<sup>(5)</sup>

- 1 = USB reset generated

- 0 = USB reset terminated

- bit 3 HOSTEN: Host Mode Enable bit<sup>(2)</sup>

- 1 = USB host capability is enabled

- 0 = USB host capability is disabled

- bit 2 RESUME: RESUME Signaling Enable bit<sup>(3)</sup>

- 1 = RESUME signaling is activated

- 0 = RESUME signaling is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

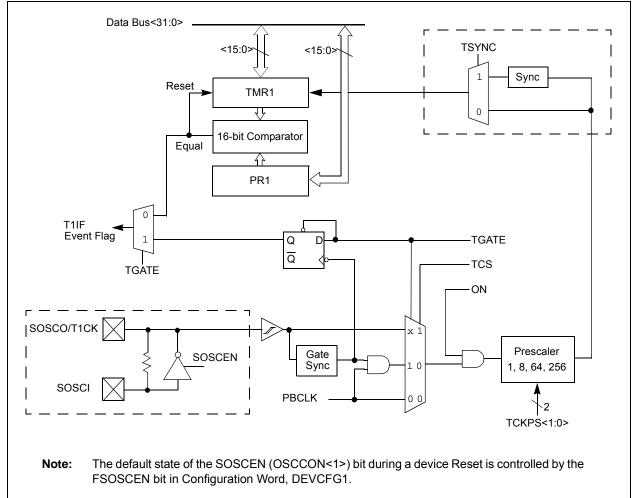

# 12.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features one synchronous/asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can also be used with the Low-Power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications.

FIGURE 12-1: TIMER1 BLOCK DIAGRAM

The following modes are supported:

- · Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

## 12.1 Additional Supported Features

- · Selectable clock prescaler

- Timer operation during CPU Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

Figure 12-1 illustrates a general block diagram of Timer1.

# 12.2 Timer1 Control Registers

# TABLE 12-1: TIMER1 REGISTER MAP

| ess                       |                                 | 0         |                 | Bits  |       |       |       |       |      | s    |        |      |       |        |      |       |      |      |            |

|---------------------------|---------------------------------|-----------|-----------------|-------|-------|-------|-------|-------|------|------|--------|------|-------|--------|------|-------|------|------|------------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15           | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7   | 22/6 | 21/5  | 20/4   | 19/3 | 18/2  | 17/1 | 16/0 | All Resets |

| 0600                      | T1CON                           | 31:16     | _               | _     | _     | _     | _     | —     | _    | —    | _      | —    | —     | —      | _    | —     | _    | _    | 0000       |

| 0600                      | TICON                           | 15:0      | ON              | —     | SIDL  | TWDIS | TWIP  | —     | _    | —    | TGATE  | _    | TCKPS | S<1:0> | —    | TSYNC | TCS  | _    | 0000       |

| 0610                      | TMR1                            | 31:16     | —               | -     | —     | —     | —     | —     | —    | —    | —      | —    | _     | _      | —    | —     | —    | —    | 0000       |

| 0010                      |                                 | 15:0      | TMR1<15:0> 0000 |       |       |       |       |       |      |      | 0000   |      |       |        |      |       |      |      |            |

| 0620                      | PR1                             | 31:16     | —               | _     | _     | _     | _     | —     | -    | —    | —      | _    | —     | _      | _    | _     | _    |      | 0000       |

| 0020                      | FRI                             | 15:0      |                 |       |       |       |       |       |      | PR1< | :15:0> |      |       |        |      |       |      |      | FFFF       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | -                 |                   |                      | —                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   |                   |                   | _                    | —                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | —                    | —                 | _                 | _                | _                |

| 7:0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

#### REGISTER 16-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | V = Writable bit U = Unimplemented bit, read |                    |  |

|-------------------|------------------|----------------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                         | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Peripheral On bit<sup>(1)</sup>

- 1 = Output Compare peripheral is enabled

- 0 = Output Compare peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

#### bit 12-6 Unimplemented: Read as '0'

- bit 5 OC32: 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 OCFLT: PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (cleared in hardware only)

- 0 = No PWM Fault condition has occurred

- bit 3 **OCTSEL:** Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin enabled

- 110 = PWM mode on OCx; Fault pin disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

# **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

**2:** This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

NOTES:

### TABLE 30-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARA                                | CTERISTICS             | 6    | (unless other | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |  |  |  |  |  |

|-----------------------------------------|------------------------|------|---------------|------------------------------------------------------|--------------------|--|--|--|--|--|

| Parameter<br>No.                        | Typical <sup>(3)</sup> | Max. | Units         | Units Conditions                                     |                    |  |  |  |  |  |

| Operating Current (IDD) (Notes 1, 2, 5) |                        |      |               |                                                      |                    |  |  |  |  |  |

| DC20                                    | 2                      | 3    | mA            | 4 M⊦                                                 | łz (Note 4)        |  |  |  |  |  |

| DC21                                    | 7                      | 10.5 | mA            | 1                                                    | 0 MHz              |  |  |  |  |  |

| DC22                                    | 10                     | 15   | mA            | 20 MI                                                | Hz (Note 4)        |  |  |  |  |  |

| DC23                                    | 15                     | 23   | mA            | 30 MI                                                | Hz <b>(Note 4)</b> |  |  |  |  |  |

| DC24                                    | 20                     | 30   | mA            | 40 MHz                                               |                    |  |  |  |  |  |

| DC25                                    | 100                    | 150  | μA            | +25°C, 3.3V LPRC (31 kHz) (Note 4)                   |                    |  |  |  |  |  |

**Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

- 2: The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, Program Flash, and SRAM data memory are operational, SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- CPU executing while(1) statement from Flash

- RTCC and JTAG are disabled

- **3:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: IPD electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

#### TABLE 30-9: DC CHARACTERISTICS: I/O PIN INPUT INJECTION CURRENT SPECIFICATIONS

| DC CHA        | ARACTER | ISTICS                                                                | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |   |                       |    |                                                                                                                                       |  |

|---------------|---------|-----------------------------------------------------------------------|------------------------------------------------------|---|-----------------------|----|---------------------------------------------------------------------------------------------------------------------------------------|--|

| Param.<br>No. | Symbol  | Characteristics                                                       | Min. Typ. <sup>(1)</sup> Max. Units Conditions       |   |                       |    |                                                                                                                                       |  |

| Dl60a         | licl    | Input Low Injection<br>Current                                        | 0                                                    |   | <sub>-5</sub> (2,5)   | mA | This parameter applies to all pins,<br>with the exception of the power<br>pins.                                                       |  |

| DI60b         | ІІСН    | Input High Injection<br>Current                                       | 0                                                    | — | +5 <sup>(3,4,5)</sup> | mA | This parameter applies to all pins,<br>with the exception of all 5V tolerant<br>pins, and the SOSCI, SOSCO,<br>OSC1, D+, and D- pins. |  |

| DI60c         | ∑lict   | Total Input Injection<br>Current (sum of all I/O<br>and Control pins) | -20 <b>(6)</b>                                       | — | +20 <b>(6)</b>        | mA | Absolute instantaneous sum of all $\pm$ input injection currents from all I/O pins (   IICL +   IICH   ) $\leq \sum$ IICT )           |  |

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: VIL source < (VSS - 0.3). Characterized but not tested.

**3:** VIH source > (VDD + 0.3) for non-5V tolerant pins only.

4: Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

5: Injection currents > | 0 | can affect the ADC results by approximately 4 to 6 counts (i.e., VIH Source > (VDD + 0.3) or VIL source < (VSS - 0.3)).

6: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. If Note 2, IICL = (((Vss - 0.3) - VIL source) / Rs). If Note 3, IICH = ((IICH source - (VDD + 0.3)) / RS). RS = Resistance between input source voltage and device pin. If (Vss - 0.3) ≤ VSOURCE ≤ (VDD + 0.3), injection current = 0.

| DC CHARACTERISTICS |        |                                      |                                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |     |        |                                               |  |  |

|--------------------|--------|--------------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|-----------------------------------------------|--|--|

| Param.<br>No.      | Symbol | Characteristics                      | Min. Typical <sup>(1)</sup> Max. Units Conditions |                                                                                                                                                                                                                                                                                     |     |        |                                               |  |  |

|                    |        | Program Flash Memory <sup>(3)</sup>  |                                                   |                                                                                                                                                                                                                                                                                     |     |        |                                               |  |  |

| D130               | Eр     | Cell Endurance                       | 20,000                                            | —                                                                                                                                                                                                                                                                                   | _   | E/W    | —                                             |  |  |

| D131               | Vpr    | VDD for Read                         | 2.3                                               | —                                                                                                                                                                                                                                                                                   | 3.6 | V      | —                                             |  |  |

| D132               | VPEW   | VDD for Erase or Write               | 2.3                                               | —                                                                                                                                                                                                                                                                                   | 3.6 | V      | —                                             |  |  |

| D134               | Tretd  | Characteristic Retention             | 20                                                | —                                                                                                                                                                                                                                                                                   | _   | Year   | Provided no other specifications are violated |  |  |

| D135               | IDDP   | Supply Current during<br>Programming | _                                                 | 10                                                                                                                                                                                                                                                                                  | _   | mA     | —                                             |  |  |

|                    | Tww    | Word Write Cycle Time                | —                                                 | 411                                                                                                                                                                                                                                                                                 | _   | es     | See Note 4                                    |  |  |

| D136               | Trw    | Row Write Cycle Time                 | —                                                 | 6675                                                                                                                                                                                                                                                                                | _   | Cycles | See Note 2,4                                  |  |  |

| D137               | TPE    | Page Erase Cycle Time                | —                                                 | 20011                                                                                                                                                                                                                                                                               | _   |        | See Note 4                                    |  |  |

|                    | TCE    | Chip Erase Cycle Time                | —                                                 | 80180                                                                                                                                                                                                                                                                               | _   | FRC    | See Note 4                                    |  |  |

#### TABLE 30-12: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: The minimum SYSCLK for row programming is 4 MHz. Care should be taken to minimize bus activities during row programming, such as suspending any memory-to-memory DMA operations. If heavy bus loads are expected, selecting Bus Matrix Arbitration mode 2 (rotating priority) may be necessary. The default Arbitration mode is mode 1 (CPU has lowest priority).

**3:** Refer to the *"PIC32 Flash Programming Specification"* (DS60001145) for operating conditions during programming and erase cycles.

4: This parameter depends on FRC accuracy (See Table 30-19) and FRC tuning values (See Register 8-2).

#### TABLE 30-24: TIMER2, 3, 4, 5 EXTERNAL CLOCK TIMING REQUIREMENTS

|               |           |                                                           |                                | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                                              |       |                |                                     |                       |

|---------------|-----------|-----------------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------|----------------|-------------------------------------|-----------------------|

| Param.<br>No. | Symbol    | Characteristics <sup>(1)</sup>                            |                                | Min.                                                                                                                                                                                               | Max.                                         | Units | its Conditions |                                     |                       |

| TB10          | ТтхН      | TxCK<br>High Time                                         | Synchron<br>prescaler          | ous, with                                                                                                                                                                                          | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns            | —     | ns             | Must also meet<br>parameter<br>TB15 | value<br>(1, 2, 4, 8, |

| TB11          | ΤτχL      | TxCK<br>Low Time                                          | Synchronous, with<br>prescaler |                                                                                                                                                                                                    | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns            | —     | ns             | Must also meet<br>parameter<br>TB15 | 16, 32, 64,<br>256)   |

| TB15          | ΤτχΡ      | TxCK<br>Input                                             | nput prescaler                 |                                                                                                                                                                                                    | [(Greater of [(25 ns or<br>2 Трв)/N] + 30 ns | _     | ns             | VDD > 2.7V                          |                       |

|               |           | Period                                                    |                                |                                                                                                                                                                                                    | [(Greater of [(25 ns or<br>2 TPB)/N] + 50 ns | _     | ns             | VDD < 2.7V                          |                       |

| TB20          | TCKEXTMRL | Delay from External TxCK<br>Clock Edge to Timer Increment |                                | _                                                                                                                                                                                                  | 1                                            | Трв   |                |                                     |                       |

Note 1: These parameters are characterized, but not tested in manufacturing.

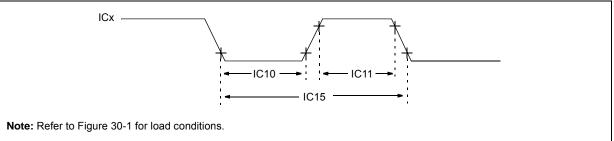

#### FIGURE 30-7: INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS

#### TABLE 30-25: INPUT CAPTURE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |  |                                   |      |       |                                         |                                  |

|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-----------------------------------|------|-------|-----------------------------------------|----------------------------------|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup>                                                                                                                                                                                                                                                    |  | Min.                              | Max. | Units | Conditions                              |                                  |

| IC10               | TccL   | ICx Input Low Time                                                                                                                                                                                                                                                                |  | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns | _    | ns    | Must also<br>meet<br>parameter<br>IC15. | N = prescale<br>value (1, 4, 16) |

| IC11               | ТссН   | ICx Input High Time                                                                                                                                                                                                                                                               |  | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns | —    | ns    | Must also<br>meet<br>parameter<br>IC15. |                                  |

| IC15               | TCCP   | ICx Input Period                                                                                                                                                                                                                                                                  |  | [(25 ns or 2 Трв)/N]<br>+ 50 ns   | _    | ns    | —                                       |                                  |

| Note 1: | These parameters are | characterized, but not | t tested in manufacturing. |

|---------|----------------------|------------------------|----------------------------|

|---------|----------------------|------------------------|----------------------------|

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

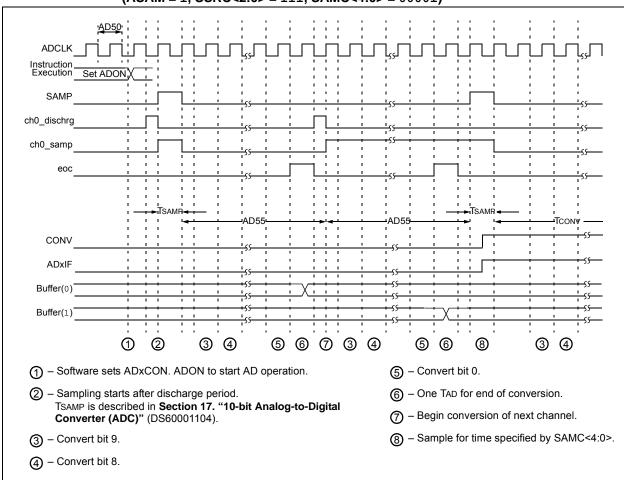

#### FIGURE 30-19: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 1, SSRC<2:0> = 111, SAMC<4:0> = 00001)

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

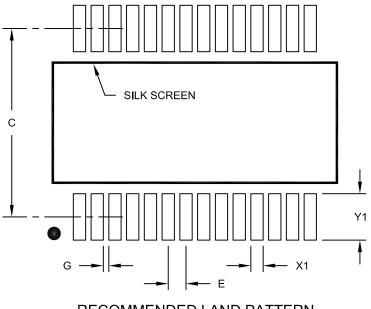

### 28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | Units | Ν    | /ILLIMETER | S    |

|--------------------------|-------|------|------------|------|

| Dimension                | MIN   | NOM  | MAX        |      |

| Contact Pitch            |       |      | 0.65 BSC   |      |

| Contact Pad Spacing      | С     |      | 7.20       |      |

| Contact Pad Width (X28)  | X1    |      |            | 0.45 |

| Contact Pad Length (X28) | Y1    |      |            | 1.75 |

| Distance Between Pads    | G     | 0.20 |            |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

# **Revision F (February 2014)**

This revision includes the addition of the following devices:

In addition, this revision includes the following major changes as described in Table A-5, as well as minor updates to text and formatting, which were incorporated throughout the document.

- PIC32MX170F256B PIC32MX270F256B

- PIC32MX170F256D

PIC32MX270F256D

### TABLE A-5: MAJOR SECTION UPDATES

| Section                                                                                                                           | Update Description                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32-bit Microcontrollers (up to 256<br>KB Flash and 64 KB SRAM) with<br>Audio and Graphics Interfaces,<br>USB, and Advanced Analog | Added new devices to the family features (see Table 1 and Table 2).<br>Updated pin diagrams to include new devices (see " <b>Pin Diagrams</b> ").    |

| 1.0 "Device Overview"                                                                                                             | Added Note 3 reference to the following pin names: VBUS, VUSB3V3, VBUSON, D+, D-, and USBID.                                                         |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"                                                                          | Replaced Figure 2-1: Recommended Minimum Connection.<br>Updated Figure 2-2: MCLR Pin Connections.<br>Added <b>2.9 "Sosc Design Recommendation"</b> . |

| 4.0 "Memory Organization"                                                                                                         | Added memory tables for devices with 64 KB RAM (see Table 4-4 through Table 4-5).                                                                    |

|                                                                                                                                   | Changed the Virtual Addresses for all registers and updated the PWP bits in the DEVCFG: Device Configuration Word Summary (see Table 4-17).          |

|                                                                                                                                   | Updated the ODCA, ODCB, and ODCC port registers (see Table 4-19, Table 4-20, and Table 4-21).                                                        |

|                                                                                                                                   | The RTCTIME, RTCDATE, ALRMTIME, and ALRMDATE registers were updated (see Table 4-25).                                                                |

|                                                                                                                                   | Added Data Ram Size value for 64 KB RAM devices (see Register 4-5).                                                                                  |

|                                                                                                                                   | Added Program Flash Size value for 256 KB Flash devices (see Register 4-5).                                                                          |

| 12.0 "Timer1"                                                                                                                     | The Timer1 block diagram was updated to include the 16-bit data bus (see Figure 12-1).                                                               |

| 13.0 "Timer2/3, Timer4/5"                                                                                                         | The Timer2-Timer5 block diagram (16-bit) was updated to include the 16-bit data bus (see Figure 13-1).                                               |

|                                                                                                                                   | The Timer2/3, Timer4/5 block diagram (32-bit) was updated to include the 32-<br>bit data bus (see Figure 13-1).                                      |

| 19.0 "Parallel Master Port (PMP)"                                                                                                 | The CSF<1:0> bit value definitions for '00' and '01' were updated (see Register 19-1).                                                               |

|                                                                                                                                   | Bit 14 in the Parallel Port Address register (PMADDR) was updated (see Register 19-3).                                                               |

| 20.0 "Real-Time Clock and                                                                                                         | The following registers were updated:                                                                                                                |

| Calendar (RTCC)"                                                                                                                  | RTCTIME (see Register 20-3)                                                                                                                          |

|                                                                                                                                   | RTCDATE (see Register 20-4)                                                                                                                          |

|                                                                                                                                   | ALRMTIME (see Register 20-5)                                                                                                                         |

|                                                                                                                                   | ALRMDATE (see Register 20-6)                                                                                                                         |

| 26.0 "Special Features"                                                                                                           | Updated the PWP bits (see Register 26-1).                                                                                                            |

| 29.0 "Electrical Characteristics"                                                                                                 | Added parameters DO50 and DO50a to the Capacitive Loading Requirements on Output Pins (see Table 29-14).                                             |

|                                                                                                                                   | Added Note 5 to the IDD DC Characteristics (see Table 29-5).                                                                                         |

|                                                                                                                                   | Added Note 4 to the IIDLE DC Characteristics (see Table 29-6).                                                                                       |

|                                                                                                                                   | Added Note 5 to the IPD DC Characteristics (see Table 29-7).                                                                                         |

|                                                                                                                                   | Updated the conditions for parameters USB321 (VOL) and USB322 (VOH) in the OTG Electrical Specifications (see Table 29-38).                          |

| Product Identification System                                                                                                     | Added 40 MHz speed information.                                                                                                                      |