Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VFTLA Exposed Pad                                                           |

| Supplier Device Package    | 44-VTLA (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx150f128d-v-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

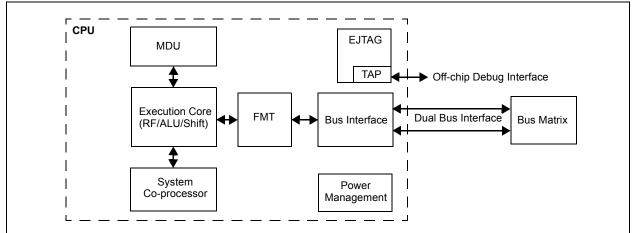

# 3.0 CPU

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS60001113), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). Resources for the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core are available at: www.imgtec.com.

The MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core is the heart of the PIC32MX1XX/2XX family processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the destinations.

# 3.1 Features

- 5-stage pipeline

- 32-bit address and data paths

- MIPS32 Enhanced Architecture (Release 2)

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- Bit field manipulation instructions

- MIPS16e<sup>®</sup> code compression

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE and RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8 and 16-bit data types

- Simple Fixed Mapping Translation (FMT) mechanism

- · Simple dual bus interface

- Independent 32-bit address and data buses

- Transactions can be aborted to improve interrupt latency

- · Autonomous multiply/divide unit

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (*rs*) sign extension-dependent)

- Power control

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- EJTAG debug and instruction trace

- Support for single stepping

- Virtual instruction and data address/value

- Breakpoints

# FIGURE 3-1: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE BLOCK DIAGRAM

# TABLE 4-1: SFR MEMORY MAP

|                           | Virtual A | ddress          |

|---------------------------|-----------|-----------------|

| Peripheral                | Base      | Offset<br>Start |

| Watchdog Timer            |           | 0x0000          |

| RTCC                      |           | 0x0200          |

| Timer1-5                  |           | 0x0600          |

| Input Capture 1-5         |           | 0x2000          |

| Output Compare 1-5        |           | 0x3000          |

| IC1 and IC2               |           | 0x5000          |

| SPI1 and SPI2             |           | 0x5800          |

| UART1 and UART2           |           | 0x6000          |

| PMP                       |           | 0x7000          |

| ADC                       | 0xBF80    | 0x9000          |

| CVREF                     |           | 0x9800          |

| Comparator                |           | 0xA000          |

| CTMU                      |           | 0xA200          |

| Oscillator                |           | 0xF000          |

| Device and Revision ID    |           | 0xF220          |

| Peripheral Module Disable |           | 0xF240          |

| Flash Controller          |           | 0xF400          |

| Reset                     |           | 0xF600          |

| PPS                       |           | 0xFA04          |

| Interrupts                |           | 0x1000          |

| Bus Matrix                |           | 0x2000          |

| DMA                       | 0xBF88    | 0x3000          |

| USB                       |           | 0x5050          |

| PORTA-PORTC               |           | 0x6000          |

| Configuration             | 0xBFC0    | 0x0BF0          |

# 9.1 DMA Control Registers

# TABLE 9-1: DMA GLOBAL REGISTER MAP

| ess                         |                                 | 0         |       |       |       |         |         |       |      | Bi       | ts        |      |      |      |      |      |           |      | s         |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|---------|---------|-------|------|----------|-----------|------|------|------|------|------|-----------|------|-----------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12   | 27/11   | 26/10 | 25/9 | 24/8     | 23/7      | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1      | 16/0 | All Reset |

| 2000                        | DMACON                          | 31:16     | _     | _     | -     | —       | —       | _     | —    | —        | —         | -    | -    | _    | -    | -    | —         | _    | 0000      |

| 3000                        | DIVIACON                        | 15:0      | ON    | —     | _     | SUSPEND | DMABUSY | —     | _    | —        | _         | —    | —    | —    | —    | —    | —         | _    | 0000      |

| 2010                        | DMASTAT                         | 31:16     | -     | _     | —     | —       | —       | —     | —    | —        | _         | _    | _    | _    | _    | —    | —         | _    | 0000      |

| 3010                        | DIVIASTAT                       | 15:0      | -     | _     | —     | —       | —       | —     | —    | —        | _         | _    | _    | _    | RDWR | DI   | MACH<2:0> | .(2) | 0000      |

| 3020                        | DMAADDR                         | 31:16     |       |       |       |         |         |       |      | DMAADD   | D-31:05   |      |      |      |      |      |           |      | 0000      |

| 3020                        | DIVIAADDR                       | 15:0      |       |       |       |         |         |       |      | DIVIAADL | vix~51.02 |      |      |      |      |      |           |      | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

## TABLE 9-2: DMA CRC REGISTER MAP

| ess                         |                                 | â         |       |               | -     |       |       |           |      | В      | ts       |        | -      |      |      |      |           |      |            |

|-----------------------------|---------------------------------|-----------|-------|---------------|-------|-------|-------|-----------|------|--------|----------|--------|--------|------|------|------|-----------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14         | 29/13 | 28/12 | 27/11 | 26/10     | 25/9 | 24/8   | 23/7     | 22/6   | 21/5   | 20/4 | 19/3 | 18/2 | 17/1      | 16/0 | All Resets |

| 2020                        | DCRCCON                         | 31:16     | —     | _             | BYTO  | <1:0> | WBO   | —         | —    | BITO   | _        | —      | —      | _    | _    | _    | —         | _    | 0000       |

| 3030                        | DURUUUN                         | 15:0      | —     | _             | —     |       |       | PLEN<4:0> |      |        | CRCEN    | CRCAPP | CRCTYP | —    | —    | C    | CRCCH<2:0 | >    | 0000       |

| 2040                        | DCRCDATA                        | 31:16     |       |               |       |       |       |           |      |        | TA<31:0> |        |        |      |      |      |           |      | 0000       |

| 3040                        | DURUDAIA                        | 15:0      |       |               |       |       |       |           |      | DURUDA | IA~51.02 |        |        |      |      |      |           |      | 0000       |

| 3050                        | DCRCXOR                         | 31:16     |       | DCRCXOR<31:0> |       |       |       |           |      |        |          |        |        |      |      |      |           |      |            |

| 3050                        | DUNUAUR                         | 15:0      |       |               |       |       |       |           |      | DCRCAU | N-51.02  |        |        |      |      |      |           |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| REGISTE | R 9-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER (CONTINUED)                                                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | CHDHIF: Channel Destination Half Full Interrupt Flag bit                                                                                                                                   |

|         | <ul> <li>1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)</li> <li>0 = No interrupt is pending</li> </ul>                                           |

| bit 3   | CHBCIF: Channel Block Transfer Complete Interrupt Flag bit                                                                                                                                 |

|         | <ul> <li>1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs</li> <li>0 = No interrupt is pending</li> </ul> |

| bit 2   | CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit                                                                                                                                  |

|         | <ul><li>1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)</li><li>0 = No interrupt is pending</li></ul>                                                          |

| bit 1   | CHTAIF: Channel Transfer Abort Interrupt Flag bit                                                                                                                                          |

|         | <ul> <li>1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted</li> <li>0 = No interrupt is pending</li> </ul>                                          |

| bit 0   | CHERIF: Channel Address Error Interrupt Flag bit                                                                                                                                           |

|         | <ul> <li>1 = A channel address error has been detected (either the source or the destination address is invalid)</li> <li>0 = No interrupt is pending</li> </ul>                           |

DS60001168J-page 96

# REGISTER 10-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 **PPBRST:** Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the EVEN Buffer Descriptor banks

- 0 = Even/Odd buffer pointers are not Reset

- bit 0 USBEN: USB Module Enable bit<sup>(4)</sup>

- 1 = USB module and supporting circuitry is enabled

- 0 = USB module and supporting circuitry is disabled

SOFEN: SOF Enable bit<sup>(5)</sup>

- 1 = SOF token is sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

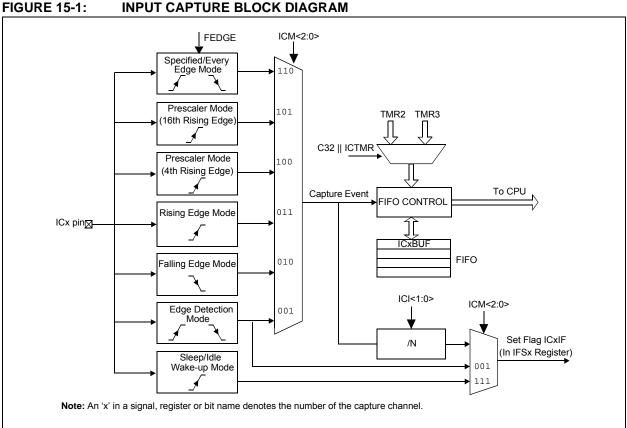

#### **INPUT CAPTURE** 15.0

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- · Simple capture event modes:

- Capture timer value on every rising and falling edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- · Device wake-up from capture pin during Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values (interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled)

- · Input capture can also be used to provide additional sources of external interrupts

Figure 15-1 illustrates a general block diagram of the Input Capture module.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | _                 | —                 | _                 | _                 | —                 | _                 | _                | —                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | _                 | —                 | _                 | _                 | —                 | _                 | _                | —                |  |  |  |  |

| 45.0         | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | _                 | PTEN14            | _                 | _                 | —                 |                   | PTEN<10:8>       |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | PTEN              | <7:0>             |                   |                  |                  |  |  |  |  |

# REGISTER 20-4: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-15 Unimplemented: Read as '0'

- bit 15-14 **PTEN14:** PMCS1 Address Port Enable bits

- 1 = PMA14 functions as either PMA14 or PMCS1<sup>(1)</sup>

- 0 = PMA14 functions as port I/O

- bit 13-11 Unimplemented: Read as '0'

- bit 10-2 PTEN<10:2>: PMP Address Port Enable bits

- 1 = PMA<10:2> function as PMP address lines

- 0 = PMA<10:2> function as port I/O

#### bit 1-0 PTEN<1:0>: PMALH/PMALL Address Port Enable bits

- 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL<sup>(2)</sup>

- 0 = PMA1 and PMA0 pads functions as port I/O

- Note 1: The use of this pin as PMA14 or CS1 is selected by the CSF<1:0> bits in the PMCON register.

- 2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by bits ADRMUX<1:0> in the PMCON register.

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------------|------------------|--|--|--|

| 24.24        | U-0                     | U-0               | U-0               | U-0               | U-0                    | U-0               | R/W-0                  | R/W-0            |  |  |  |

| 31:24        | —                       |                   | _                 | _                 | —                      | —                 | CAL<9                  | :8>              |  |  |  |

| 00.40        | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0                  | R/W-0             | R/W-0                  | R/W-0            |  |  |  |

| 23:16        | CAL<7:0>                |                   |                   |                   |                        |                   |                        |                  |  |  |  |

| 45.0         | R/W-0                   | U-0               | R/W-0             | U-0               | U-0                    | U-0               | U-0                    | U-0              |  |  |  |

| 15:8         | ON <sup>(1,2)</sup>     | _                 | SIDL              | _                 | —                      | _                 | _                      |                  |  |  |  |

| 7.0          | R/W-0                   | R-0               | U-0               | U-0               | R/W-0                  | R-0               | R-0                    | R/W-0            |  |  |  |

| 7:0          | RTSECSEL <sup>(3)</sup> | RTCCLKON          |                   | _                 | RTCWREN <sup>(4)</sup> | RTCSYNC           | HALFSEC <sup>(5)</sup> | RTCOE            |  |  |  |

|              |                         |                   |                   |                   |                        |                   |                        |                  |  |  |  |

# REGISTER 21-1: RTCCON: RTC CONTROL REGISTER

# Legend:

| Logonal           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-26 Unimplemented: Read as '0'

bit 25-16 CAL<9:0>: RTC Drift Calibration bits, which contain a signed 10-bit integer value 0111111111 = Maximum positive adjustment, adds 511 RTC clock pulses every one minute 000000001 = Minimum positive adjustment, adds 1 RTC clock pulse every one minute 000000000 = No adjustment 1111111111 = Minimum negative adjustment, subtracts 1 RTC clock pulse every one minute 100000000 = Maximum negative adjustment, subtracts 512 clock pulses every one minute ON: RTCC On bit<sup>(1,2)</sup> bit 15 1 = RTCC module is enabled 0 = RTCC module is disabled bit 14 Unimplemented: Read as '0' bit 13 SIDL: Stop in Idle Mode bit 1 = Disables the PBCLK to the RTCC when the device enters Idle mode 0 = Continue normal operation when the device enters Idle mode bit 12-8 Unimplemented: Read as '0' bit 7 RTSECSEL: RTCC Seconds Clock Output Select bit<sup>(3)</sup> 1 = RTCC Seconds Clock is selected for the RTCC pin 0 = RTCC Alarm Pulse is selected for the RTCC pin bit 6 RTCCLKON: RTCC Clock Enable Status bit 1 = RTCC Clock is actively running 0 = RTCC Clock is not running **Note 1:** The ON bit is only writable when RTCWREN = 1. 2: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. 3: Requires RTCOE = 1 (RTCCON<0>) for the output to be active. 4: The RTCWREN bit can be set only when the write sequence is enabled. 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

**Note:** This register is reset only on a Power-on Reset (POR).

© 2011-2016 Microchip Technology Inc.

|              |                         |                      |                    | OOMINGE IN              |                     |                   |                  |                  |

|--------------|-------------------------|----------------------|--------------------|-------------------------|---------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6    | Bit<br>29/21/13/5  | Bit<br>28/20/12/4       | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0                     | U-0                  | U-0                | U-0                     | U-0                 | U-0               | U-0              | U-0              |

| 31:24        | —                       | -                    | —                  | —                       | _                   | —                 | _                | _                |

| 22:16        | U-0                     | U-0                  | U-0                | U-0                     | U-0                 | U-0               | U-0              | U-0              |

| 23:16        | —                       | -                    | —                  | —                       | _                   | —                 | _                | —                |

| 45.0         | R/W-0                   | R/W-0                | R/W-0              | R-0                     | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ALRMEN <sup>(1,2)</sup> | CHIME <sup>(2)</sup> | PIV <sup>(2)</sup> | ALRMSYNC <sup>(3)</sup> |                     | AMASK             | <3:0> <b>(2)</b> |                  |

| 7.0          | R/W-0                   | R/W-0                | R/W-0              | R/W-0                   | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                         |                      |                    | ARPT<7:0                | <sub>&gt;</sub> (2) |                   |                  |                  |

| 1.0          |                         |                      |                    | ARPT<7:0                | >(2)                |                   |                  |                  |

### REGISTER 21-2: RTCALRM: RTC ALARM CONTROL REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

|-------------------|------------------|-----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ALRMEN: Alarm Enable bit<sup>(1,2)</sup>

- 1 = Alarm is enabled

- 0 = Alarm is disabled

### bit 14 CHIME: Chime Enable bit<sup>(2)</sup>

- 1 = Chime is enabled ARPT<7:0> is allowed to rollover from 0x00 to 0xFF

- 0 = Chime is disabled ARPT<7:0> stops once it reaches 0x00

#### bit 13 **PIV:** Alarm Pulse Initial Value bit<sup>(2)</sup>

When ALRMEN = 0, PIV is writable and determines the initial value of the Alarm Pulse. When ALRMEN = 1, PIV is read-only and returns the state of the Alarm Pulse.

# bit 12 ALRMSYNC: Alarm Sync bit<sup>(3)</sup>

- 1 = ARPT<7:0> and ALRMEN may change as a result of a half second rollover during a read. The ARPT must be read repeatedly until the same value is read twice. This must be done since multiple bits may be changing, which are then synchronized to the PB clock domain

- 0 = ARPT<7:0> and ALRMEN can be read without concerns of rollover because the prescaler is > 32 RTC clocks away from a half-second rollover

#### bit 11-8 AMASK<3:0>: Alarm Mask Configuration bits<sup>(2)</sup>

- 0000 = Every half-second

- 0001 = Every second

- 0010 = Every 10 seconds

- 0011 = Every minute

- 0100 = Every 10 minutes

- 0101 = Every hour

- 0110 = Once a day

- 0111 = Once a week

- 1000 = Once a month

- 1001 = Once a year (except when configured for February 29, once every four years)

- 1010 = Reserved; do not use

- 1011 = Reserved; do not use

- 11xx = Reserved; do not use

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

Note: This register is reset only on a Power-on Reset (POR).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 |                     | _                 | _                 | _                 | —                | _                |

| 00.40        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                   | _                 | _                 |                   | —                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 15:8         | ON <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | _                 | —                 | —                 | —                | COUT             |

| 7.0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7:0          | EVPOL             | _<1:0>            |                     | CREF              | _                 | _                 | CCH              | <1:0>            |

### REGISTER 23-1: CMXCON: COMPARATOR CONTROL REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

- bit 14 **COE:** Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

- bit 12-9 Unimplemented: Read as '0'

- bit 8 **COUT:** Comparator Output bit

- 1 = Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 **EVPOL<1:0>:** Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

- bit 4 CREF: Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CXINA pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the CxIND pin

- 01 = Comparator inverting input is connected to the CxINC pin

- 00 = Comparator inverting input is connected to the CxINB pin

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

# REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED)

- bit 10 EDGSEQEN: Edge Sequence Enable bit 1 = Edge1 must occur before Edge2 can occur 0 = No edge sequence is needed IDISSEN: Analog Current Source Control bit<sup>(2)</sup> bit 9 1 = Analog current source output is grounded 0 = Analog current source output is not grounded bit 8 **CTTRIG:** Trigger Control bit 1 = Trigger output is enabled 0 = Trigger output is disabled bit 7-2 ITRIM<5:0>: Current Source Trim bits 011111 = Maximum positive change from nominal current 011110 000001 = Minimum positive change from nominal current 000000 = Nominal current output specified by IRNG<1:0> 111111 = Minimum negative change from nominal current 100010 100001 = Maximum negative change from nominal current bit 1-0 IRNG<1:0>: Current Range Select bits<sup>(3)</sup> 11 = 100 times base current 10 = 10 times base current

- 01 = Base current level

- 00 = 1000 times base current<sup>(4)</sup>

- Note 1: When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- Refer to the CTMU Current Source Specifications (Table 30-41) in Section 30.0 "Electrical 3: Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

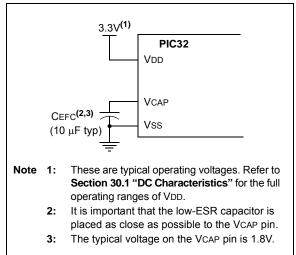

# 27.3 On-Chip Voltage Regulator

All PIC32MX1XX/2XX 28/36/44-pin Family devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX1XX/2XX 28/36/44-pin Family family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 30.1 "DC Characteristics"**.

| Note: | It is important that the low-ESR capacitor |

|-------|--------------------------------------------|

|       | is placed as close as possible to the VCAP |

|       | pin.                                       |

# 27.3.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

# 27.3.2 ON-CHIP REGULATOR AND BOR

PIC32MX1XX/2XX 28/36/44-pin Family devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specific in **Section 30.1 "DC Characteristics"**.

# FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

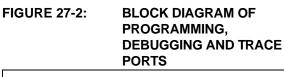

# 27.4 Programming and Diagnostics

PIC32MX1XX/2XX 28/36/44-pin Family devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

Figure 27-2 illustrates a block diagram of the programming, debugging, and trace ports.

# TABLE 30-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS                   |                   |                                                                  |         | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |       |            |   |  |

|--------------------------------------|-------------------|------------------------------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|---|--|

| Param.<br>No. Symbol Characteristics |                   | Min.                                                             | Тур.    | Max.                                                                                                                                                                                                                                                                                | Units | Conditions |   |  |

| Operati                              | Operating Voltage |                                                                  |         |                                                                                                                                                                                                                                                                                     |       |            |   |  |

| DC10                                 | Vdd               | Supply Voltage (Note 2)                                          | 2.3     |                                                                                                                                                                                                                                                                                     | 3.6   | V          | — |  |

| DC12                                 | Vdr               | RAM Data Retention Voltage<br>(Note 1)                           | 1.75    | _                                                                                                                                                                                                                                                                                   | —     | V          | _ |  |

| DC16                                 | VPOR              | VDD Start Voltage<br>to Ensure Internal Power-on Reset<br>Signal | 1.75    | —                                                                                                                                                                                                                                                                                   | 2.1   | V          | _ |  |

| DC17                                 | SVDD              | VDD Rise Rate<br>to Ensure Internal Power-on Reset<br>Signal     | 0.00005 | _                                                                                                                                                                                                                                                                                   | 0.115 | V/μs       | _ |  |

**Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

2: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 30-11 for BOR values.

| DC CHARACTERISTICS |        |                                                           |      | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |          |                                                                                         |  |

|--------------------|--------|-----------------------------------------------------------|------|-------------------------------------------------------|------|----------|-----------------------------------------------------------------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics                                           | Min. | Typical                                               | Max. | x. Units | Comments                                                                                |  |

| D300               | VIOFF  | Input Offset Voltage                                      | -    | ±7.5                                                  | ±25  | mV       | AVDD = VDD,<br>AVSS = VSS                                                               |  |

| D301               | VICM   | Input Common Mode Voltage                                 | 0    | -                                                     | Vdd  | V        | AVDD = VDD,<br>AVss = Vss<br>(Note 2)                                                   |  |

| D302               | CMRR   | Common Mode Rejection Ratio                               | 55   | —                                                     | _    | dB       | Max VICM = (VDD - 1)V<br>(Note 2)                                                       |  |

| D303A              | TRESP  | Large Signal Response Time                                | _    | 150                                                   | 400  | ns       | AVDD = VDD, AVSS = VSS<br>(Note 1,2)                                                    |  |

| D303B              | TSRESP | Small Signal Response Time                                | -    | 1                                                     | _    | μS       | This is defined as an input<br>step of 50 mV with 15 mV<br>of overdrive <b>(Note 2)</b> |  |

| D304               | ON2ov  | Comparator Enabled to Output<br>Valid                     | _    | _                                                     | 10   | μs       | Comparator module is<br>configured before setting<br>the comparator ON bit<br>(Note 2)  |  |

| D305               | IVREF  | Internal Voltage Reference                                | 1.14 | 1.2                                                   | 1.26 | V        | —                                                                                       |  |

| D312               | TSET   | Internal Comparator Voltage<br>DRC Reference Setting time | —    | —                                                     | 10   | μs       | (Note 3)                                                                                |  |

# TABLE 30-13: COMPARATOR SPECIFICATIONS

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

**2:** These parameters are characterized but not tested.

**3:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

**4:** The Comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

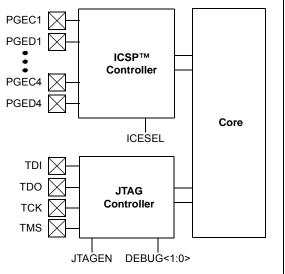

| TABLE 30-22: RESETS TIMING |         |                                                                                                                                            |                                                                                                                                                                                                    |                              |      |       |            |  |

|----------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|-------|------------|--|

|                            |         |                                                                                                                                            | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                              |      |       |            |  |

| Param.<br>No.              | Symbol  | Characteristics <sup>(1)</sup>                                                                                                             | Min.                                                                                                                                                                                               | Typical <sup>(2)</sup>       | Max. | Units | Conditions |  |

| SY00                       | Τρυ     | Power-up Period<br>Internal Voltage Regulator Enabled                                                                                      | —                                                                                                                                                                                                  | 400                          | 600  | μS    | _          |  |

| SY02                       | TSYSDLY | System Delay Period:<br>Time Required to Reload Device<br>Configuration Fuses plus SYSCLK<br>Delay before First instruction is<br>Fetched. | _                                                                                                                                                                                                  | 1 μs +<br>8 SYSCLK<br>cycles | _    | _     | _          |  |

| SY20                       | TMCLR   | MCLR Pulse Width (low)                                                                                                                     | 2                                                                                                                                                                                                  | _                            | _    | μS    | —          |  |

| SY30                       | TBOR    | BOR Pulse Width (low)                                                                                                                      |                                                                                                                                                                                                    | 1                            | _    | μS    | —          |  |

These parameters are characterized, but not tested in manufacturing. Note 1:

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Characterized by design but not tested.

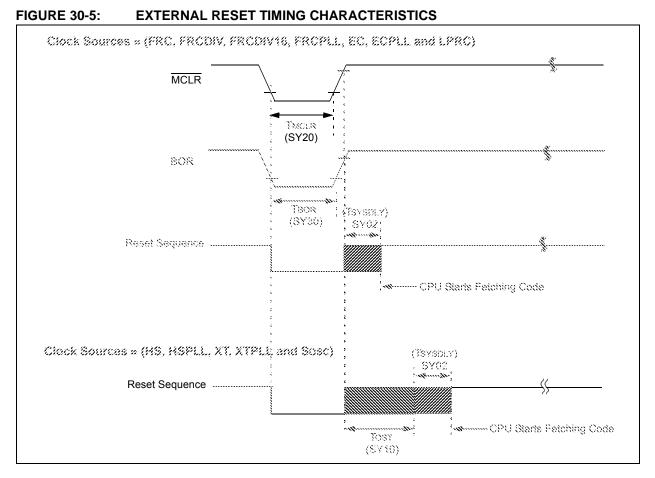

### TABLE 30-34: ADC MODULE SPECIFICATIONS

|               |            |                                                      | Standard Operating Conditions (see Note 5): 2.5V to 3.6V (unless otherwise stated) |              |                                  |                                               |                                                                                                         |  |  |

|---------------|------------|------------------------------------------------------|------------------------------------------------------------------------------------|--------------|----------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|

|               |            |                                                      |                                                                                    |              |                                  | ≤ +85°C for Industrial<br>≤ +105°C for V-temp |                                                                                                         |  |  |

| Param.<br>No. | Symbol     | Characteristics                                      | Min.                                                                               | Typical      | Max.                             | Units                                         | Conditions                                                                                              |  |  |

| Device        | Supply     |                                                      |                                                                                    |              |                                  |                                               |                                                                                                         |  |  |

| AD01          | AVdd       | Module VDD Supply                                    | Greater of<br>VDD – 0.3<br>or 2.5                                                  | —            | Lesser of<br>VDD + 0.3 or<br>3.6 | V                                             | _                                                                                                       |  |  |

| AD02          | AVss       | Module Vss Supply                                    | Vss                                                                                | _            | AVdd                             | V                                             | (Note 1)                                                                                                |  |  |

| Referen       | ce Inputs  | ·                                                    |                                                                                    |              |                                  |                                               | ·                                                                                                       |  |  |

| AD05<br>AD05a | Vrefh      | Reference Voltage High                               | AVss + 2.0<br>2.5                                                                  | _            | AVDD<br>3.6                      | V<br>V                                        | (Note 1)<br>VREFH = AVDD (Note 3)                                                                       |  |  |

| AD06          | Vrefl      | Reference Voltage Low                                | AVss                                                                               | —            | Vrefh – 2.0                      | V                                             | (Note 1)                                                                                                |  |  |

| AD07          | Vref       | Absolute Reference<br>Voltage (VREFH – VREFL)        | 2.0                                                                                | _            | AVDD                             | V                                             | (Note 3)                                                                                                |  |  |

| AD08<br>AD08a | IREF       | Current Drain                                        | _                                                                                  | 250<br>      | 400<br>3                         | μΑ<br>μΑ                                      | ADC operating<br>ADC off                                                                                |  |  |

| Analog        | Input      | ·                                                    |                                                                                    |              |                                  |                                               |                                                                                                         |  |  |

| AD12          | VINH-VINL  | Full-Scale Input Span                                | VREFL                                                                              | —            | Vrefh                            | V                                             | —                                                                                                       |  |  |

| AD13          | VINL       | Absolute VINL Input<br>Voltage                       | AVss – 0.3                                                                         | _            | AVDD/2                           | V                                             | _                                                                                                       |  |  |

| AD14          | Vin        | Absolute Input Voltage                               | AVss - 0.3                                                                         | _            | AVDD + 0.3                       | V                                             | —                                                                                                       |  |  |

| AD15          | —          | Leakage Current                                      | _                                                                                  | ±0.001       | ±0.610                           | μA                                            | $V_{INL} = AV_{SS} = V_{REFL} = 0V,$<br>$AV_{DD} = V_{REFH} = 3.3V$<br>Source Impedance = 10 k $\Omega$ |  |  |

| AD17          | RIN        | Recommended<br>Impedance of Analog<br>Voltage Source | _                                                                                  | _            | 5k                               | Ω                                             | (Note 1)                                                                                                |  |  |

| ADC Ac        | curacy – N | leasurements with Exte                               | rnal VREF+/V                                                                       | REF-         |                                  |                                               |                                                                                                         |  |  |

| AD20c         | Nr         | Resolution                                           |                                                                                    | 10 data bits | S                                | bits                                          | —                                                                                                       |  |  |

| AD21c         | INL        | Integral Non-linearity                               | > -1                                                                               | _            | < 1                              | LSb                                           | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.3V                                                        |  |  |

| AD22c         | DNL        | Differential Non-linearity                           | > -1                                                                               | _            | < 1                              | LSb                                           | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.3V<br>(Note 2)                                            |  |  |

| AD23c         | Gerr       | Gain Error                                           | > -1                                                                               | —            | < 1                              | LSb                                           | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.3V                                                        |  |  |

| AD24c         | Eoff       | Offset Error                                         | > -1                                                                               | _            | < 1                              | Lsb                                           | VINL = AVSS = 0V,<br>AVDD = 3.3V                                                                        |  |  |

| AD25c         | _          | Monotonicity                                         | _                                                                                  | _            |                                  | _                                             | Guaranteed                                                                                              |  |  |

Note 1: These parameters are not characterized or tested in manufacturing.

2: With no missing codes.

**3:** These parameters are characterized, but not tested in manufacturing.

**4:** Characterized with a 1 kHz sine wave.

**5:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

| AC CHARACTERISTICS |           |                                                                      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                        |         |       |                                                           |  |

|--------------------|-----------|----------------------------------------------------------------------|------------------------------------------------------|------------------------|---------|-------|-----------------------------------------------------------|--|

| Param.<br>No.      | Symbol    | Characteristics                                                      | Min.                                                 | Typical <sup>(1)</sup> | Max.    | Units | Conditions                                                |  |

| Clock P            | arameters | S                                                                    | •                                                    | •                      |         |       | ·                                                         |  |

| AD50               | TAD       | ADC Clock Period <sup>(2)</sup>                                      | 65                                                   | _                      | —       | ns    | See Table 30-35                                           |  |

| Convers            | sion Rate |                                                                      |                                                      |                        |         |       | ·                                                         |  |

| AD55               | TCONV     | Conversion Time                                                      | _                                                    | 12 Tad                 | —       | _     | —                                                         |  |

| AD56               | FCNV      | Throughput Rate                                                      | _                                                    | —                      | 1000    | ksps  | AVDD = 3.0V to 3.6V                                       |  |

|                    |           | (Sampling Speed)                                                     | —                                                    | —                      | 400     | ksps  | AVDD = 2.5V to 3.6V                                       |  |

| AD57               | TSAMP     | Sample Time                                                          | 1 Tad                                                | —                      | —       | —     | TSAMP must be $\geq$ 132 ns                               |  |

| Timing             | Paramete  | rs                                                                   |                                                      |                        |         |       |                                                           |  |

| AD60               | TPCS      | Conversion Start from Sample<br>Trigger <sup>(3)</sup>               | _                                                    | 1.0 Tad                |         | _     | Auto-Convert Trigger<br>(SSRC<2:0> = 111)<br>not selected |  |

| AD61               | TPSS      | Sample Start from Setting<br>Sample (SAMP) bit                       | 0.5 Tad                                              | —                      | 1.5 Tad | _     | —                                                         |  |

| AD62               | TCSS      | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(3)</sup>   | —                                                    | 0.5 Tad                | —       |       | _                                                         |  |

| AD63               | TDPU      | Time to Stabilize Analog Stage from ADC Off to ADC On <sup>(3)</sup> | _                                                    | _                      | 2       | μS    | —                                                         |  |

# TABLE 30-36: ANALOG-TO-DIGITAL CONVERSION TIMING REQUIREMENTS

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

**3:** Characterized by design but not tested.

**4:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

# FIGURE 30-19: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 1, SSRC<2:0> = 111, SAMC<4:0> = 00001)

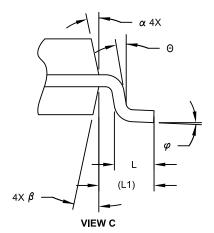

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |           |      |  |  |

|--------------------------|-------------|-----------|-----------|------|--|--|

| Dimension                | Limits      | MIN       | NOM       | MAX  |  |  |

| Number of Pins           | N           |           | 28        |      |  |  |

| Pitch                    | е           |           | 1.27 BSC  |      |  |  |

| Overall Height           | A           | -         | -         | 2.65 |  |  |

| Molded Package Thickness | A2          | 2.05      | -         | -    |  |  |

| Standoff §               | A1          | 0.10      | -         | 0.30 |  |  |

| Overall Width            | E           |           | 10.30 BSC |      |  |  |

| Molded Package Width     | E1          | 7.50 BSC  |           |      |  |  |

| Overall Length           | D           | 17.90 BSC |           |      |  |  |

| Chamfer (Optional)       | h           | 0.25      | -         | 0.75 |  |  |

| Foot Length              | L           | 0.40      | -         | 1.27 |  |  |

| Footprint                | L1          | 1.40 REF  |           |      |  |  |

| Lead Angle               | Θ           | 0°        | -         | -    |  |  |

| Foot Angle               | $\varphi$   | 0°        | -         | 8°   |  |  |

| Lead Thickness           | С           | 0.18      | -         | 0.33 |  |  |

| Lead Width               | b           | 0.31      | -         | 0.51 |  |  |

| Mold Draft Angle Top     | α           | 5°        | -         | 15°  |  |  |

| Mold Draft Angle Bottom  | β           | 5°        | -         | 15°  |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

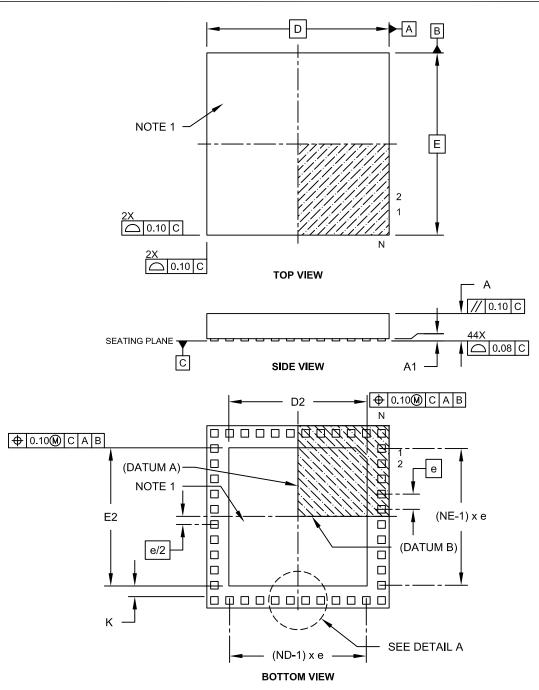

# 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

Microchip Technology Drawing C04-157C Sheet 1 of 2