Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Becano                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 44-VTLA (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx150f128dt-i-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-1: **PINOUT I/O DESCRIPTIONS**

|          |                   | Pin Nu                                      | nber <sup>(1)</sup>                    |                                        |             |                |                                                                                                                                                                                                |

|----------|-------------------|---------------------------------------------|----------------------------------------|----------------------------------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | 28-pin<br>QFN     | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC           | 36-pin<br>VTLA                         | 44-pin<br>QFN/<br>TQFP/<br>VTLA        | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                    |

| AN0      | 27                | 2                                           | 33                                     | 19                                     |             | Analog         | Analog input channels.                                                                                                                                                                         |

| AN1      | 28                | 3                                           | 34                                     | 20                                     | I           | Analog         |                                                                                                                                                                                                |

| AN2      | 1                 | 4                                           | 35                                     | 21                                     |             | Analog         |                                                                                                                                                                                                |

| AN3      | 2                 | 5                                           | 36                                     | 22                                     |             | Analog         |                                                                                                                                                                                                |

| AN4      | 3                 | 6                                           | 1                                      | 23                                     | I           | Analog         |                                                                                                                                                                                                |

| AN5      | 4                 | 7                                           | 2                                      | 24                                     | I           | Analog         |                                                                                                                                                                                                |

| AN6      | _                 | _                                           | 3                                      | 25                                     | I           | Analog         |                                                                                                                                                                                                |

| AN7      | _                 | _                                           | 4                                      | 26                                     | I           | Analog         |                                                                                                                                                                                                |

| AN8      | _                 | _                                           | _                                      | 27                                     | I           | Analog         |                                                                                                                                                                                                |

| AN9      | 23                | 26                                          | 29                                     | 15                                     | I           | Analog         |                                                                                                                                                                                                |

| AN10     | 22                | 25                                          | 28                                     | 14                                     | I           | Analog         |                                                                                                                                                                                                |

| AN11     | 21                | 24                                          | 27                                     | 11                                     | I           | Analog         |                                                                                                                                                                                                |

| AN12     | 20 <sup>(2)</sup> | 23 <sup>(2)</sup>                           | 26 <sup>(2)</sup><br>11 <sup>(3)</sup> | 10 <sup>(2)</sup><br>36 <sup>(3)</sup> | 1           | Analog         | *                                                                                                                                                                                              |

| CLKI     | 6                 | 9                                           | 7                                      | 30                                     | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                         |

| CLKO     | 7                 | 10                                          | 8                                      | 31                                     | 0           | _              | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes. Always associated<br>with OSC2 pin function. |

| OSC1     | 6                 | 9                                           | 7                                      | 30                                     | I           | ST/CMOS        | -                                                                                                                                                                                              |

| OSC2     | 7                 | 10                                          | 8                                      | 31                                     | 0           | -              | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes.                                              |

| SOSCI    | 8                 | 11                                          | 9                                      | 33                                     | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal<br>input; CMOS otherwise.                                                                                                                              |

| SOSCO    | 9                 | 12                                          | 10                                     | 34                                     | 0           | —              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                |

| REFCLKI  | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | Reference Input Clock                                                                                                                                                                          |

| REFCLKO  | PPS               | PPS                                         | PPS                                    | PPS                                    | 0           | —              | Reference Output Clock                                                                                                                                                                         |

| IC1      | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | Capture Inputs 1-5                                                                                                                                                                             |

| IC2      | PPS               | PPS                                         | PPS                                    | PPS                                    | 1           | ST             | 1                                                                                                                                                                                              |

| IC3      | PPS               | PPS                                         | PPS                                    | PPS                                    | 1           | ST             | 1                                                                                                                                                                                              |

| IC4      | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | 1                                                                                                                                                                                              |

| IC5      | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | 1                                                                                                                                                                                              |

|          | ST = Schm         | MOS compa<br>itt Trigger in<br>input buffer |                                        |                                        | •           | O = Outp       | Analog inputP = PowerutI = Inputeripheral Pin Select— = N/A                                                                                                                                    |

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability. 2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site:

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- *"MPLAB<sup>®</sup> ICD 3 Design Advisory"* (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

## 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

## 2.7 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

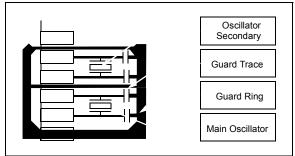

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

## FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

## 2.8 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

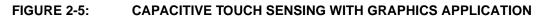

## 2.9 Typical Application Connection Examples

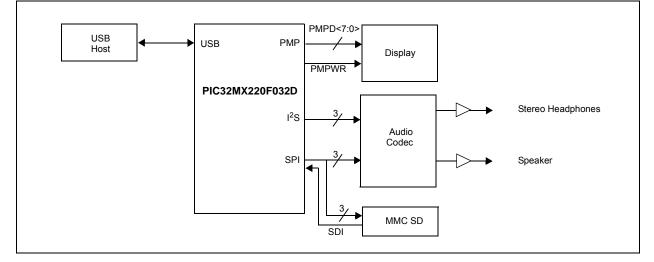

Examples of typical application connections are shown in Figure 2-5 and Figure 2-6.

FIGURE 2-6: AUDIO PLAYBACK APPLICATION

NOTES:

|              |                   |                      | OULEAIO           |                   |                   |                       |                  |                  |

|--------------|-------------------|----------------------|-------------------|-------------------|-------------------|-----------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0                  | R/W-y             | R/W-y             | R/W-y             | R/W-0                 | R/W-0            | R/W-1            |

| 31:24        | —                 | —                    | Р                 | LLODIV<2:0        | <b>`</b>          | F                     | RCDIV<2:0>       |                  |

| 00.40        | U-0               | R-0                  | R-1               | R/W-y             | R/W-y             | R/W-y                 | R/W-y            | R/W-y            |

| 23:16        | —                 | SOSCRDY              | PBDIVRDY          | PBDI              | /<1:0>            | Р                     | LLMULT<2:0>      | •                |

| 45.0         | U-0               | R-0                  | R-0               | R-0               | U-0               | R/W-y                 | R/W-y            | R/W-y            |

| 15:8         | —                 |                      | COSC<2:0>         |                   | —                 |                       | NOSC<2:0>        |                  |

| 7:0          | R/W-0             | R-0                  | R-0               | R/W-0             | R/W-0             | R/W-0                 | R/W-y            | R/W-0            |

| 7:0          | CLKLOCK           | ULOCK <sup>(1)</sup> | SLOCK             | SLPEN             | CF                | UFRCEN <sup>(1)</sup> | SOSCEN           | OSWEN            |

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| Legend:           | y = Value set from Co | onfiguration bits on POR |                    |

|-------------------|-----------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bi     | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-30 **Unimplemented:** Read as '0'

#### bit 29-27 **PLLODIV<2:0>:** Output Divider for PLL

- 111 = PLL output divided by 256

- 110 = PLL output divided by 64

- 101 = PLL output divided by 32

- 100 = PLL output divided by 16

- 011 = PLL output divided by 8

- 010 = PLL output divided by 4

- 001 = PLL output divided by 2

- 000 = PLL output divided by 1

#### bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2 (default setting)

- 000 = FRC divided by 1

- bit 23 Unimplemented: Read as '0'

- bit 22 SOSCRDY: Secondary Oscillator (Sosc) Ready Indicator bit

- 1 = The Secondary Oscillator is running and is stable

- 0 = The Secondary Oscillator is still warming up or is turned off

- bit 21 **PBDIVRDY:** Peripheral Bus Clock (PBCLK) Divisor Ready bit

- 1 = PBDIV<1:0> bits can be written

- 0 = PBDIV<1:0> bits cannot be written

- bit 20-19 **PBDIV<1:0>:** Peripheral Bus Clock (PBCLK) Divisor bits

- 11 = PBCLK is SYSCLK divided by 8 (default)

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

Note 1: This bit is only available on PIC32MX2XX devices.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | —                 | _                 | —                 | —                 | _                 | _                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | _                 | —                 | —                 | —                 | _                | —                |  |  |  |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |  |  |

| 15:8         | ON <sup>(1)</sup> | —                 | _                 | SUSPEND           | DMABUSY           | _                 | _                | —                |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

## REGISTER 9-1: DMACON: DMA CONTROLLER CONTROL REGISTER

#### Legend:

| 0                 |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | nd as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: DMA On bit<sup>(1)</sup>

- 1 = DMA module is enabled

- 0 = DMA module is disabled

- bit 14-13 **Unimplemented:** Read as '0'

- bit 12 SUSPEND: DMA Suspend bit

- 1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

- 0 = DMA operates normally

### bit 11 DMABUSY: DMA Module Busy bit

- 1 = DMA module is active

- 0 = DMA module is disabled and not actively transferring data

- bit 10-0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| INE OIOT     | LK 10-J.          |                   |                   |                   |                        |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | -                 | —                 | _                      | _                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | -                 | —                 | _                      | _                 | —                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 |                   | —                 | _                      | —                 | —                | —                |

| 7:0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0                  | U-0               | R/W-0            | R/W-0            |

| 7:0          | UACTPND           |                   |                   | USLPGRD           | USBBUSY <sup>(1)</sup> | _                 | USUSPEND         | USBPWR           |

## REGISTER 10-5: U1PWRC: USB POWER CONTROL REGISTER

## Legend:

| zogonai           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB bus activity has been detected; however, an interrupt is pending, which has yet to be generated

0 = An interrupt is not pending

- bit 6-5 Unimplemented: Read as '0'

- bit 4 USLPGRD: USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

- bit 3 USBBUSY: USB Module Busy bit<sup>(1)</sup>

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- bit 2 Unimplemented: Read as '0'

- bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

- bit 0 USBPWR: USB Operation Enable bit

- 1 = USB module is turned on

- 0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

## **Note 1:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

### TABLE 11-4: PORTB REGISTER MAP

| ess                         |                  |           |               |               |               |                              |               |               |              | Bits         |              |                             |              |              |              |              |              |              |            |

|-----------------------------|------------------|-----------|---------------|---------------|---------------|------------------------------|---------------|---------------|--------------|--------------|--------------|-----------------------------|--------------|--------------|--------------|--------------|--------------|--------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range | 31/15         | 30/14         | 29/13         | 28/12                        | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6                        | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All Resets |

|                             |                  | 31:16     | _             |               | —             |                              | _             | —             | —            | —            | _            | —                           | _            |              | —            | _            | —            | —            | 0000       |

| 0100                        | ANGLED           | 15:0      | ANSB15        | ANSB14        | ANSB13        | ANSB12 <sup>(2)</sup>        | —             | —             | —            | —            | _            | _                           | _            | _            | ANSB3        | ANSB2        | ANSB1        | ANSB0        | EOOF       |

| 6110                        | TRISB            | 31:16     | -             | _             | _             | 1                            | _             | —             | —            | —            | -            | —                           | -            | -            | —            | -            | _            | _            | 0000       |

| 0110                        | IIKIOD           | 15:0      | TRISB15       | TRISB14       | TRISB13       | TRISB12 <sup>(2)</sup>       | TRISB11       | TRISB10       | TRISB9       | TRISB8       | TRISB7       | TRISB6 <sup>(2)</sup>       | TRISB5       | TRISB4       | TRISB3       | TRISB2       | TRISB1       | TRISB0       | FFFF       |

| 6120                        | PORTB            | 31:16     | _             | _             | _             |                              | _             | _             | _            | _            |              | _                           | -            |              |              |              |              |              | 0000       |

| 0120                        | FORTB            | 15:0      | RB15          | RB14          | RB13          | RB12 <sup>(2)</sup>          | RB11          | RB10          | RB9          | RB8          | RB7          | RC6 <sup>(2)</sup>          | RB5          | RB4          | RB3          | RB2          | RB1          | RB0          | xxxx       |

| 6130                        | LATB             | 31:16     | -             | _             | _             |                              | -             | _             | _            | _            |              | _                           |              |              | _            |              | _            | _            | 0000       |

| 0150                        | LAID             | 15:0      | LATB15        | LATB14        | LATB13        | LATB12 <sup>(2)</sup>        | LATB11        | LATB10        | LATB9        | LATB8        | LATB7        | LATB6 <sup>(2)</sup>        | LATB5        | LATB4        | LATB3        | LATB2        | LATB1        | LATB0        | xxxx       |

| C1 4 0                      | 0000             | 31:16     |               | _             | —             | —                            | _             | _             | _            | —            | _            | _                           |              | —            | _            | —            | _            | —            | 0000       |

| 6140                        | ODCB             | 15:0      | ODCB15        | ODCB14        | ODCB13        | ODCB12 <sup>(2)</sup>        | ODCB11        | ODCB10        | ODCB9        | ODCB8        | ODCB7        | ODCB6                       | ODCB5        | ODCB4        | ODCB3        | ODCB2        | ODCB1        | ODCB0        | 0000       |

| 6150                        |                  | 31:16     | -             | —             | —             | -                            | _             | _             | _            | —            | -            | _                           | _            | _            | _            | -            | _            | —            | 0000       |

| 6150                        | CNPUB            | 15:0      | CNPUB15       | CNPUB14       | CNPUB13       | CNPUB12 <sup>(2)</sup>       | CNPUB11       | CNPUB10       | CNPUB9       | CNPUB8       | CNPUB7       | CNPUB6 <sup>(2)</sup>       | CNPUB5       | CNPUB4       | CNPUB3       | CNPUB2       | CNPUB1       | CNPUB0       | 0000       |

| 6160                        | CNPDB            | 31:16     | -             | _             | _             |                              | -             | _             | _            | _            |              | _                           |              |              | _            |              | _            | _            | 0000       |

| 0100                        | CNPDB            | 15:0      | CNPDB15       | CNPDB14       | CNPDB13       | CNPDB12 <sup>(2)</sup>       | CNPDB11       | CNPDB10       | CNPDB9       | CNPDB8       | CNPDB7       | CNPDB6 <sup>(2)</sup>       | CNPDB5       | CNPDB4       | CNPDB3       | CNPDB2       | CNPDB1       | CNPDB0       | 0000       |

| 6170                        | CNCONB           | 31:16     | -             | _             | _             |                              | -             | _             | _            | _            |              | _                           |              |              | _            |              | _            | _            | 0000       |

| 0170                        | CINCOINE         | 15:0      | ON            | _             | SIDL          |                              | -             | _             | _            | _            |              | _                           |              |              | _            |              | _            | _            | 0000       |

| C400                        |                  | 31:16     |               | —             | —             | -                            | —             | —             | —            | _            |              | —                           | Ι            | -            | —            | -            | —            | -            | 0000       |

| 6180                        | CNENB            | 15:0      | CNIEB15       | CNIEB14       | CNIEB13       | CNIEB11 <sup>(2)</sup>       | CNIEB11       | CNIEB10       | CNIEB9       | CNIEB8       | CNIEB7       | CNIEB6(2)                   | CNIEB5       | CNIEB4       | CNIEB3       | CNIEB2       | CNIEB1       | CNIEB0       | 0000       |

|                             |                  | 31:16     | —             |               | —             |                              | _             | —             | —            | —            | _            | —                           | _            | _            | —            | _            | _            | —            | 0000       |

| 6190                        | CNSTATB          | 15:0      | CN<br>STATB15 | CN<br>STATB14 | CN<br>STATB13 | CN<br>STATB12 <sup>(2)</sup> | CN<br>STATB11 | CN<br>STATB10 | CN<br>STATB9 | CN<br>STATB8 | CN<br>STATB7 | CN<br>STATB6 <sup>(2)</sup> | CN<br>STATB5 | CN<br>STATB4 | CN<br>STATB3 | CN<br>STATB2 | CN<br>STATB1 | CN<br>STATB0 | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This bit is not available on PIC32MX2XX devices. The reset value for the TRISB register when this bit is not available is 0x0000EFBF.

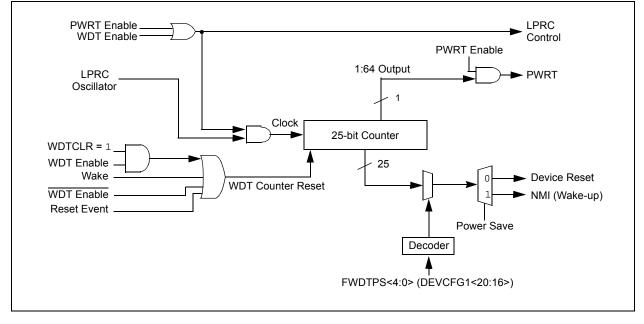

## 14.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114), which are available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32). The WDT, when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are some of the key features of the WDT module:

- · Configuration or software controlled

- User-configurable time-out period

- Can wake the device from Sleep or Idle mode

Figure 14-1 illustrates a block diagram of the WDT and Power-up timer.

## FIGURE 14-1: WATCHDOG TIMER AND POWER-UP TIMER BLOCK DIAGRAM

## 17.1 SPI Control Registers

## TABLE 17-1: SPI1 AND SPI2 REGISTER MAP

| ess                         |                                 | Ċ,        |               |         |        |              |              |              |           | Bi     | ts      |           |        |        |             |          |        |         |            |

|-----------------------------|---------------------------------|-----------|---------------|---------|--------|--------------|--------------|--------------|-----------|--------|---------|-----------|--------|--------|-------------|----------|--------|---------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14   | 29/13  | 28/12        | 27/11        | 26/10        | 25/9      | 24/8   | 23/7    | 22/6      | 21/5   | 20/4   | 19/3        | 18/2     | 17/1   | 16/0    | All Resets |

| 5800                        | SPI1CON                         | 31:16     | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2:( | )>     | MCLKSEL | —         | _      | -      | —           | _        | SPIFE  | ENHBUF  | 0000       |

| 3800                        | SFILCON                         | 15:0      | ON            | _       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP       | CKE    | SSEN    | CKP       | MSTEN  | DISSDI | STXISE      | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| 5910                        | SPI1STAT                        | 31:16     | —             | _       | _      |              | RXE          | BUFELM<4:    | 0>        |        | —       | —         | -      |        | TX          | BUFELM<4 | :0>    |         | 0000       |

| 5610                        |                                 | 15:0      | _             | —       | —      | FRMERR       | SPIBUSY      | —            | —         | SPITUR | SRMT    | SPIROV    | SPIRBE | —      | SPITBE      | —        | SPITBF | SPIRBF  | 0008       |

| 5820                        | SPI1BUF                         | 31:16     |               |         |        |              |              |              |           | DATA<  | 31.0>   |           |        |        |             |          |        |         | 0000       |

| 3020                        |                                 | 15:0      |               |         |        |              |              |              |           | Brance | .01.0   |           |        |        |             |          |        |         | 0000       |

| 5830                        | SPI1BRG                         | 31:16     | —             | —       | _      | —            | —            | —            | —         | —      | —       | —         | —      | —      | —           | —        | —      | —       | 0000       |

| 0000                        |                                 | 15:0      | _             | —       | _      |              |              |              |           |        | E       | 3RG<12:0> |        |        |             |          |        |         | 0000       |

|                             |                                 | 31:16     | —             | —       | —      | —            | —            | —            | —         | —      | —       | —         | _      | _      | —           | _        | —      | —       | 0000       |

| 5840                        | SPI1CON2                        | 15:0      | SPI<br>SGNEXT | —       |        | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | —         | -      | -      | AUD<br>MONO | _        | AUDMC  | )D<1:0> | 0000       |

| 5400                        | SPI2CON                         | 31:16     | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2:( | )>     | MCLKSEL | —         |        |        | _           |          | SPIFE  | ENHBUF  | 0000       |

| 5A00                        | 3F1200N                         | 15:0      | ON            | _       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP       | CKE    | SSEN    | CKP       | MSTEN  | DISSDI | STXISE      | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| 5410                        | SPI2STAT                        | 31:16     | —             | _       |        |              | RXE          | BUFELM<4:    | 0>        |        | _       | -         |        |        | TX          | BUFELM<4 | :0>    |         | 0000       |

| SATU                        | 3F1231AI                        | 15:0      | _             | _       | _      | FRMERR       | SPIBUSY      | _            | _         | SPITUR | SRMT    | SPIROV    | SPIRBE | _      | SPITBE      | _        | SPITBF | SPIRBF  | 0008       |

| 5A20                        | SPI2BUF                         | 31:16     |               |         |        |              |              |              |           | DATA<  | 31.0>   |           |        |        |             |          |        |         | 0000       |

| 5420                        |                                 | 15:0      |               |         |        |              |              |              |           | Brance |         |           |        |        |             |          |        |         | 0000       |

| 5A30                        | SPI2BRG                         | 31:16     | —             | —       | _      | —            | —            | —            | —         | —      | —       | —         | —      | —      | —           | —        | —      | —       | 0000       |

| 5730                        |                                 | 15:0      |               | —       | —      |              |              |              |           |        | E       | 3RG<12:0> |        |        |             |          |        |         | 0000       |

|                             |                                 | 31:16     | —             | —       | —      | _            | —            | _            | —         | —      | —       | —         | _      | —      | —           | —        | —      | —       | 0000       |

| 5A40                        | SPI2CON2                        | 15:0      | SPI<br>SGNEXT | —       | _      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | —         | _      | _      | AUD<br>MONO | _        | AUDMC  | )D<1:0> | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except SPIxBUF have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 31:24        |                   | _                 | _                 |                   | R                 | XBUFELM<4:        | 0>               |                  |

| 22:16        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23:16        |                   | _                 | —                 |                   | Tک                | KBUFELM<4:0       | )>               |                  |

| 45.0         | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |

| 15:8         |                   | —                 | _                 | FRMERR            | SPIBUSY           | —                 | —                | SPITUR           |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |

| 7:0          | SRMT              | SPIROV            | SPIRBE            | _                 | SPITBE            | —                 | SPITBF           | SPIRBF           |

### REGISTER 17-3: SPIxSTAT: SPI STATUS REGISTER

| Legend:           | C = Clearable bit | HS = Set in hardware     |                    |

|-------------------|-------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 15-13 Unimplemented: Read as '0'

- bit 12 **FRMERR:** SPI Frame Error status bit

- 1 = Frame error detected

- 0 = No Frame error detected

- This bit is only valid when FRMEN = 1.

- bit 11 SPIBUSY: SPI Activity Status bit

- 1 = SPI peripheral is currently busy with some transactions

- 0 = SPI peripheral is currently idle

- bit 10-9 Unimplemented: Read as '0'

- bit 8 SPITUR: Transmit Under Run bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or writing a '0' to SPITUR.

- bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 SPIROV: Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

This bit is set in hardware; can bit only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or by writing a '0' to SPIROV.

- bit 5 **SPIRBE:** RX FIFO Empty bit (valid only when ENHBUF = 1) 1 = RX FIFO is empty (CRPTR = SWPTR)

- 0 = RX FIFO is not empty (CRPTR  $\neq$  SWPTR)

- bit 4 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | _                 | —                 | -                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 |                   | _                 | —                 | -                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | IREN              | RTSMD             | _                 | UEN              | <1:0>            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL             | <1:0>            | STSEL            |

### REGISTER 19-1: UXMODE: UARTX MODE REGISTER

## Legend:

| Logona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: UARTx Enable bit<sup>(1)</sup>

- 1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by the UEN<1:0> and UTXEN control bits.

- 0 = UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal.

- bit 14 Unimplemented: Read as '0'

#### bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

- bit 12 IREN: IrDA Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- bit 11 **RTSMD:** Mode Selection for UxRTS Pin bit

- $1 = \overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

- bit 10 Unimplemented: Read as '0'

- bit 9-8 UEN<1:0>: UARTx Enable bits

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX, UxCTS and UxRTS pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up enabled

- 0 = Wake-up disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|--------------------|-------------------|---------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                  | _                 | _                   | _                 | -                | _                |

| 00.40        | U-0               | U-0               | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | —                  | —                 | _                   | _                 | -                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0              | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL               | ADRMUX<1:0>       |                     | PMPTTL            | PTWREN           | PTRDEN           |

| 7.0          | R/W-0             | R/W-0             | R/W-0              | U-0               | R/W-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | CSF<              | 1:0> <b>(2)</b>   | ALP <sup>(2)</sup> |                   | CS1P <sup>(2)</sup> | _                 | WRSP             | RDSP             |

### REGISTER 20-1: PMCON: PARALLEL PORT CONTROL REGISTER

### Legend:

| 0                                 |                  |                                    |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Parallel Master Port Enable bit<sup>(1)</sup>

- 1 = PMP enabled

- 0 = PMP disabled, no off-chip access performed

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

- bit 12-11 ADRMUX<1:0>: Address/Data Multiplexing Selection bits

- 11 = Lower 8 bits of address are multiplexed on PMD<7:0> pins; upper 8 bits are not used

- 10 = All 16 bits of address are multiplexed on PMD<7:0> pins

- 01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins, upper bits are on PMA<10:8> and PMA<14>

- 00 = Address and data appear on separate pins

- bit 10 **PMPTTL:** PMP Module TTL Input Buffer Select bit

- 1 = PMP module uses TTL input buffers

- 0 = PMP module uses Schmitt Trigger input buffer

- bit 9 **PTWREN:** Write Enable Strobe Port Enable bit

- 1 = PMWR/PMENB port enabled

- 0 = PMWR/PMENB port disabled

- bit 8 PTRDEN: Read/Write Strobe Port Enable bit

- 1 = PMRD/PMWR port enabled

- 0 = PMRD/PMWR port disabled

- bit 7-6 CSF<1:0>: Chip Select Function bits<sup>(2)</sup>

- 11 = Reserved

- 10 = PMCS1 functions as Chip Select

- 01 = PMCS1 functions as PMA<14>

- 00 = PMCS1 functions as PMA<14>

- bit 5 ALP: Address Latch Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMALL and PMALH)

- $0 = \text{Active-low} (\overline{\text{PMALL}} \text{ and } \overline{\text{PMALH}})$

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

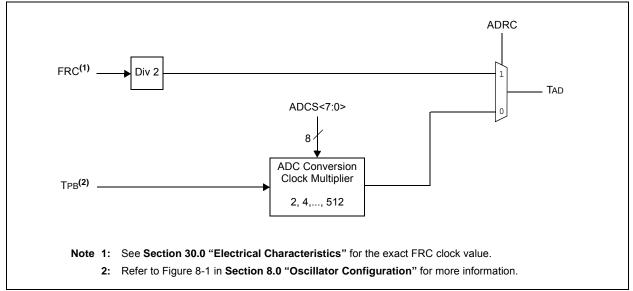

## REGISTER 22-3: AD1CON3: ADC CONTROL REGISTER 3

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4        | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|--------------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | —                 | —                 | _                        | —                 | —                 | —                | -                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | —                 | _                        | —                 | —                 | _                | -                |  |  |  |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0                    | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | ADRC              | _                 | —                 | SAMC<4:0> <sup>(1)</sup> |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0                    | R/W-0             | R/W-0             | R/W              | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | ADCS<7:0> <sup>(2)</sup> |                   |                   |                  |                  |  |  |  |

## Legend:

| =ogona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ADRC: ADC Conversion Clock Source bit

- 1 = Clock derived from FRC

- 0 = Clock derived from Peripheral Bus Clock (PBCLK)

- bit 14-13 Unimplemented: Read as '0'

- - 00000001 =TPB • 2 • (ADCS<7:0> + 1) = 4 • TPB = TAD 00000000 =TPB • 2 • (ADCS<7:0> + 1) = 2 • TPB = TAD

- **Note 1:** This bit is only used if the SSRC<2:0> bits (AD1CON1<7:5>) = 111.

- **2:** This bit is not used if the ADRC (AD1CON3<15>) bit = 1.

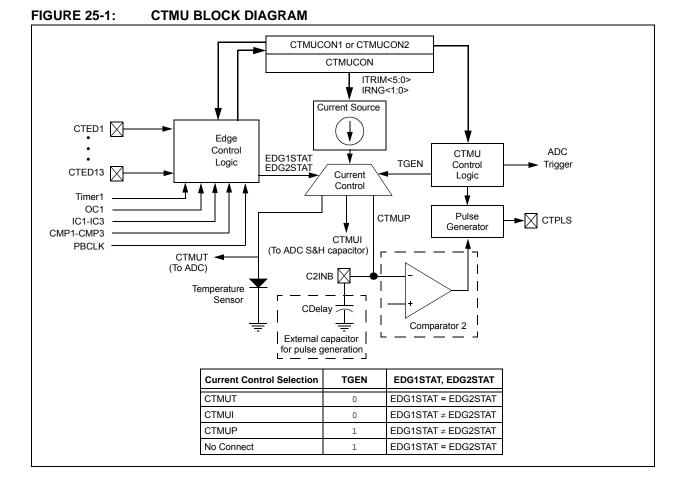

## 25.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Charge Time Measurement Unit (CTMU) is a flexible analog module that has a configurable current source with a digital configuration circuit built around it. The CTMU can be used for differential time measurement between pulse sources and can be used for generating an asynchronous pulse. By working with other on-chip analog modules, the CTMU can be used for high resolution time measurement, measure capacitance, measure relative changes in capacitance or generate output pulses with a specific time delay. The CTMU is ideal for interfacing with capacitive-based sensors.

- Up to 13 channels available for capacitive or time measurement input

- · On-chip precision current source

- 16-edge input trigger sources

- · Selection of edge or level-sensitive inputs

- · Polarity control for each edge source

- Control of edge sequence

- Control of response to edges

- · High precision time measurement

- Time delay of external or internal signal asynchronous to system clock

- · Integrated temperature sensing diode

- · Control of current source during auto-sampling

- · Four current source ranges

- · Time measurement resolution of one nanosecond

A block diagram of the CTMU is shown in Figure 25-1.

© 2011-2016 Microchip Technology Inc.

## TABLE 30-9: DC CHARACTERISTICS: I/O PIN INPUT INJECTION CURRENT SPECIFICATIONS

| DC CHARACTERISTICS |        |                                                                       | $ \begin{array}{ l l l l l l l l l l l l l l l l l l l$ |   |                       |    |                                                                                                                                       |

|--------------------|--------|-----------------------------------------------------------------------|---------------------------------------------------------|---|-----------------------|----|---------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics                                                       | Min. Typ. <sup>(1)</sup> Max. Units Conditions          |   |                       |    | Conditions                                                                                                                            |

| Dl60a              | licl   | Input Low Injection<br>Current                                        | 0                                                       |   | <sub>-5</sub> (2,5)   | mA | This parameter applies to all pins,<br>with the exception of the power<br>pins.                                                       |

| DI60b              | ІІСН   | Input High Injection<br>Current                                       | 0                                                       | — | +5 <sup>(3,4,5)</sup> | mA | This parameter applies to all pins,<br>with the exception of all 5V tolerant<br>pins, and the SOSCI, SOSCO,<br>OSC1, D+, and D- pins. |

| DI60c              | ∑lict  | Total Input Injection<br>Current (sum of all I/O<br>and Control pins) | -20 <b>(6)</b>                                          | — | +20 <b>(6)</b>        | mA | Absolute instantaneous sum of all $\pm$ input injection currents from all I/O pins (   IICL +   IICH   ) $\leq \sum$ IICT )           |

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: VIL source < (VSS - 0.3). Characterized but not tested.

**3:** VIH source > (VDD + 0.3) for non-5V tolerant pins only.

4: Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

5: Injection currents > | 0 | can affect the ADC results by approximately 4 to 6 counts (i.e., VIH Source > (VDD + 0.3) or VIL source < (VSS - 0.3)).

6: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. If Note 2, IICL = (((Vss - 0.3) - VIL source) / Rs). If Note 3, IICH = ((IICH source - (VDD + 0.3)) / RS). RS = Resistance between input source voltage and device pin. If (Vss - 0.3) ≤ VSOURCE ≤ (VDD + 0.3), injection current = 0.

| DC CHARACTERISTICS |                        |                                      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |      |        |                                               |  |

|--------------------|------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|--------|-----------------------------------------------|--|

| Param.<br>No.      | Symbol Characteristics |                                      |                                                                                                                                                                                                                                                                                     | Typical <sup>(1)</sup> | Max. | Units  | Conditions                                    |  |

|                    |                        | Program Flash Memory <sup>(3)</sup>  |                                                                                                                                                                                                                                                                                     |                        |      |        |                                               |  |

| D130               | Eр                     | Cell Endurance                       | 20,000                                                                                                                                                                                                                                                                              | —                      | _    | E/W    | —                                             |  |

| D131               | Vpr                    | VDD for Read                         | 2.3                                                                                                                                                                                                                                                                                 | —                      | 3.6  | V      | —                                             |  |

| D132               | VPEW                   | VDD for Erase or Write               | 2.3                                                                                                                                                                                                                                                                                 | —                      | 3.6  | V      | —                                             |  |

| D134               | Tretd                  | Characteristic Retention             | 20                                                                                                                                                                                                                                                                                  | —                      | _    | Year   | Provided no other specifications are violated |  |

| D135               | IDDP                   | Supply Current during<br>Programming | _                                                                                                                                                                                                                                                                                   | 10                     | _    | mA     | —                                             |  |

|                    | Tww                    | Word Write Cycle Time                | —                                                                                                                                                                                                                                                                                   | 411                    | _    | es     | See Note 4                                    |  |

| D136               | Trw                    | Row Write Cycle Time                 | —                                                                                                                                                                                                                                                                                   | 6675                   | _    | Cycles | See Note 2,4                                  |  |

| D137               | TPE                    | Page Erase Cycle Time                | —                                                                                                                                                                                                                                                                                   | 20011                  | _    |        | See Note 4                                    |  |

|                    | TCE                    | Chip Erase Cycle Time                | —                                                                                                                                                                                                                                                                                   | 80180                  | _    | FRC    | See Note 4                                    |  |

## TABLE 30-12: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: The minimum SYSCLK for row programming is 4 MHz. Care should be taken to minimize bus activities during row programming, such as suspending any memory-to-memory DMA operations. If heavy bus loads are expected, selecting Bus Matrix Arbitration mode 2 (rotating priority) may be necessary. The default Arbitration mode is mode 1 (CPU has lowest priority).

**3:** Refer to the *"PIC32 Flash Programming Specification"* (DS60001145) for operating conditions during programming and erase cycles.

4: This parameter depends on FRC accuracy (See Table 30-19) and FRC tuning values (See Register 8-2).

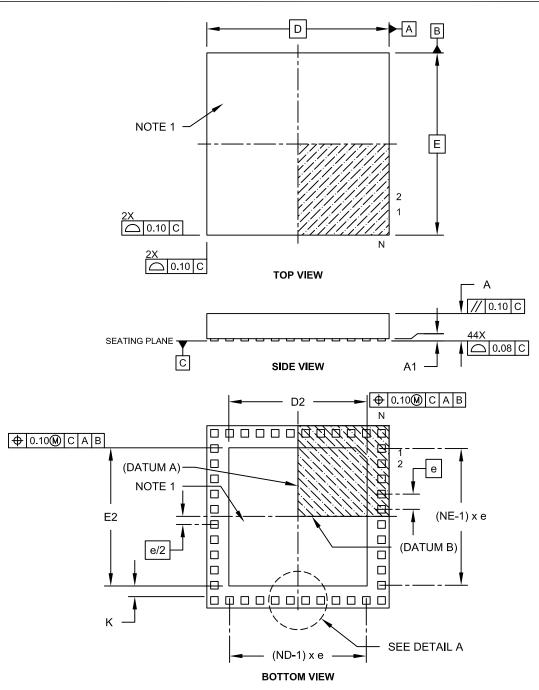

## 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

Microchip Technology Drawing C04-157C Sheet 1 of 2