#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XEI

| Betans                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx150f128dt-v-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 4:PIN NAMES FOR 28-PIN USB DEVICES

| 28                                              | 28-PIN SOIC, SPDIP, SSOP (TOP VIEW) <sup>(1,2,3)</sup>                                                                                                                                                                                                                                                                                                                                  |                                                                |                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

|                                                 | 1<br>SSOP                                                                                                                                                                                                                                                                                                                                                                               | 28                                                             | 1 28 1 28<br>SOIC SPDIP                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |

|                                                 | PIC32MX210F016B<br>PIC32MX220F032B<br>PIC32MX230F064B<br>PIC32MX230F256B<br>PIC32MX250F128B<br>PIC32MX270F256B                                                                                                                                                                                                                                                                          |                                                                |                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                         |                                                                |                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |  |

| Pin #                                           | Full Pin Name                                                                                                                                                                                                                                                                                                                                                                           | Pin #                                                          | Full Pin Name                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |

| <b>Pin #</b>                                    | Full Pin Name                                                                                                                                                                                                                                                                                                                                                                           | <b>Pin #</b>                                                   | Full Pin Name                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                         |                                                                |                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |  |

| 1                                               | MCLR                                                                                                                                                                                                                                                                                                                                                                                    | 15                                                             | VBUS                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |

| 1                                               | MCLR                                                                                                                                                                                                                                                                                                                                                                                    | 15                                                             | VBUS                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |

|                                                 | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0                                                                                                                                                                                                                                                                                                                                        | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |

| 1                                               | MCLR                                                                                                                                                                                                                                                                                                                                                                                    | 15                                                             | VBUS                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |

| 2                                               | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0                                                                                                                                                                                                                                                                                                                                        | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |

| 3                                               | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1                                                                                                                                                                                                                                                                                                                                              | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |

| 1                                               | MCLR                                                                                                                                                                                                                                                                                                                                                                                    | 15                                                             | VBUS                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |

| 2                                               | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0                                                                                                                                                                                                                                                                                                                                        | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |

| 3                                               | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1                                                                                                                                                                                                                                                                                                                                              | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |

| 4                                               | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0                                                                                                                                                                                                                                                                                                                                               | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |

| 1                                               | MCLR      PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0      PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1      PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0      PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1                                                                                                                                                                               | 15                                                             | VBUS                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 19                                                             | Vss                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |  |

| 1                                               | MCLR      PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0      PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1      PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0      PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1      AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2                                                                                                                                | 15                                                             | VBUS                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 19                                                             | Vss                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |  |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 20                                                             | Vcap                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |

| 1                                               | MCLR      PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0      PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1      PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0      PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1      AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2      AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3                                                                                   | 15                                                             | VBUS                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 19                                                             | Vss                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |  |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 20                                                             | Vcap                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |

| 7                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 21                                                             | PGED2/RPB10/D+/CTED11/RB10                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |

| 1                                               | MCLR      PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0      PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1      PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0      PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1      AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2      AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3      Vss                                                                          | 15                                                             | VBUS                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 19                                                             | Vss                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |  |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 20                                                             | Vcap                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |

| 7                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 21                                                             | PGED2/RPB10/D+/CTED11/RB10                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |

| 8                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 22                                                             | PGEC2/RPB11/D-/RB11                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |  |

| 1                                               | MCLR      PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0      PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1      PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0      PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1      AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2      AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3      Vss      OSC1/CLKI/RPA2/RA2                                                  | 15                                                             | VBUS                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 19                                                             | Vss                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |  |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 20                                                             | VCAP                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |

| 7                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 21                                                             | PGED2/RPB10/D+/CTED11/RB10                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |

| 8                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 22                                                             | PGEC2/RPB11/D-/RB11                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |  |

| 9                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 23                                                             | VUSB3V3                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10 | MCLR      PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0      PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1      PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0      PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1      AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2      AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3      Vss      OSC1/CLKI/RPA2/RA2      OSC2/CLKO/RPA3/PMA0/RA3                     | 15<br>16<br>17<br>18<br>19<br>20<br>21<br>21<br>22<br>23<br>24 | VBUS<br>TDI/RPB7/CTED3/PMD5/INT0/RB7<br>TCK/RPB8/SCL1/CTED10/PMD4/RB8<br>TDO/RPB9/SDA1/CTED4/PMD3/RB9<br>VSS<br>VCAP<br>PGED2/RPB10/D+/CTED11/RB10<br>PGEC2/RPB11/D-/RB11<br>VUSB3V3<br>AN11/RPB13/CTPLS/PMRD/RB13 |  |  |  |  |  |  |  |  |  |  |  |

| 1                                               | MCLR      PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0      PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1      PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0      PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1      AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2      AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3      Vss      OSC1/CLKI/RPA2/RA2      OSC2/CLKO/RPA3/PMA0/RA3      SOSCI/RPB4/RB4 | 15                                                             | VBUS                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 19                                                             | Vss                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |  |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 20                                                             | VcAP                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |

| 7                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 21                                                             | PGED2/RPB10/D+/CTED11/RB10                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |

| 8                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 22                                                             | PGEC2/RPB11/D-/RB11                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |  |

| 9                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 23                                                             | VUSB3V3                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |

| 10                                              |                                                                                                                                                                                                                                                                                                                                                                                         | 24                                                             | AN11/RPB13/CTPLS/PMRD/RB13                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |

| 11                                              |                                                                                                                                                                                                                                                                                                                                                                                         | 25                                                             | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

#### TABLE 1-1: **PINOUT I/O DESCRIPTIONS**

|          |                   | Pin Nu                                      | nber <sup>(1)</sup>                    |                                        |             |                |                                                                                                                                                                                                |  |  |  |  |  |

|----------|-------------------|---------------------------------------------|----------------------------------------|----------------------------------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin Name | 28-pin<br>QFN     | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC           | 36-pin<br>VTLA                         | 44-pin<br>QFN/<br>TQFP/<br>VTLA        | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                    |  |  |  |  |  |

| AN0      | 27                | 2                                           | 33                                     | 19                                     | I           | Analog         | Analog input channels.                                                                                                                                                                         |  |  |  |  |  |

| AN1      | 28                | 3                                           | 34                                     | 20                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |  |  |

| AN2      | 1                 | 4                                           | 35                                     | 21                                     |             | Analog         |                                                                                                                                                                                                |  |  |  |  |  |

| AN3      | 2                 | 5                                           | 36                                     | 22                                     |             | Analog         |                                                                                                                                                                                                |  |  |  |  |  |

| AN4      | 3                 | 6                                           | 1                                      | 23                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |  |  |

| AN5      | 4                 | 7                                           | 2                                      | 24                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |  |  |

| AN6      | _                 | _                                           | 3                                      | 25                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |  |  |

| AN7      | _                 | _                                           | 4                                      | 26                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |  |  |

| AN8      | _                 | _                                           | _                                      | 27                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |  |  |

| AN9      | 23                | 26                                          | 29                                     | 15                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |  |  |

| AN10     | 22                | 25                                          | 28                                     | 14                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |  |  |

| AN11     | 21                | 24                                          | 27                                     | 11                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |  |  |

| AN12     | 20 <sup>(2)</sup> | 23 <sup>(2)</sup>                           | 26 <sup>(2)</sup><br>11 <sup>(3)</sup> | 10 <sup>(2)</sup><br>36 <sup>(3)</sup> | 1           | Analog         | *                                                                                                                                                                                              |  |  |  |  |  |

| CLKI     | 6                 | 9                                           | 7                                      | 30                                     | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                         |  |  |  |  |  |

| CLKO     | 7                 | 10                                          | 8                                      | 31                                     | 0           | _              | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes. Always associated<br>with OSC2 pin function. |  |  |  |  |  |

| OSC1     | 6                 | 9                                           | 7                                      | 30                                     | I           | ST/CMOS        | -                                                                                                                                                                                              |  |  |  |  |  |

| OSC2     | 7                 | 10                                          | 8                                      | 31                                     | 0           | -              | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes.                                              |  |  |  |  |  |

| SOSCI    | 8                 | 11                                          | 9                                      | 33                                     | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal<br>input; CMOS otherwise.                                                                                                                              |  |  |  |  |  |

| SOSCO    | 9                 | 12                                          | 10                                     | 34                                     | 0           | —              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                |  |  |  |  |  |

| REFCLKI  | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | Reference Input Clock                                                                                                                                                                          |  |  |  |  |  |

| REFCLKO  | PPS               | PPS                                         | PPS                                    | PPS                                    | 0           | —              | Reference Output Clock                                                                                                                                                                         |  |  |  |  |  |

| IC1      | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | Capture Inputs 1-5                                                                                                                                                                             |  |  |  |  |  |

| IC2      | PPS               | PPS                                         | PPS                                    | PPS                                    | 1           | ST             | 1                                                                                                                                                                                              |  |  |  |  |  |

| IC3      | PPS               | PPS                                         | PPS                                    | PPS                                    | 1           | ST             | 1                                                                                                                                                                                              |  |  |  |  |  |

| IC4      | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | 1                                                                                                                                                                                              |  |  |  |  |  |

| IC5      | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | 1                                                                                                                                                                                              |  |  |  |  |  |

|          | ST = Schm         | MOS compa<br>itt Trigger in<br>input buffer |                                        |                                        | •           | O = Outp       | Analog inputP = PowerutI = Inputeripheral Pin Select— = N/A                                                                                                                                    |  |  |  |  |  |

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability. 2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

|              |                        | Pin Nu                                      | mber <sup>(1)</sup> |                                 |             | -                   |                                                            |

|--------------|------------------------|---------------------------------------------|---------------------|---------------------------------|-------------|---------------------|------------------------------------------------------------|

| Pin Name     | 28-pin<br>QFN          | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC           | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type      | Description                                                |

| RC0          | —                      | —                                           | 3                   | 25                              | I/O         | ST                  | PORTC is a bidirectional I/O port                          |

| RC1          | —                      | —                                           | 4                   | 26                              | I/O         | ST                  |                                                            |

| RC2          | —                      | —                                           | _                   | 27                              | I/O         | ST                  |                                                            |

| RC3          | —                      | —                                           | 11                  | 36                              | I/O         | ST                  | _                                                          |

| RC4          | —                      | —                                           | _                   | 37                              | I/O         | ST                  | _                                                          |

| RC5          | —                      |                                             |                     | 38                              | I/O         | ST                  | _                                                          |

| RC6          |                        | —                                           | _                   | 2                               | I/O         | ST                  | _                                                          |

| RC7          | —                      |                                             | —                   | 3                               | I/O         | ST                  | _                                                          |

| RC8          | —                      | —                                           | —                   | 4                               | I/O         | ST                  | _                                                          |

| RC9          |                        | - 40                                        | 20                  | 5                               | I/O         | ST                  | Time and an element all all in must                        |

| T1CK<br>T2CK | 9<br>PPS               | 12                                          | 10                  | 34                              |             | ST                  | Timer1 external clock input                                |

| T3CK         | PPS<br>PPS             | PPS<br>PPS                                  | PPS<br>PPS          | PPS<br>PPS                      |             | ST<br>ST            | Timer2 external clock input<br>Timer3 external clock input |

| T4CK         | PPS                    | PPS                                         | PPS                 | PPS                             | 1           | ST                  | Timer4 external clock input                                |

| T5CK         | PPS                    | PPS                                         | PPS                 | PPS                             |             | ST                  | Timer5 external clock input                                |

|              | PPS                    | PPS                                         | PPS                 | PPS                             |             | ST                  | UART1 clear to send                                        |

| U1RTS        | PPS                    | PPS                                         | PPS                 | PPS                             |             | 51                  |                                                            |

| U1RX         | PPS<br>PPS             | PPS<br>PPS                                  | PPS<br>PPS          | PPS<br>PPS                      | 0           | ST                  | UART1 ready to send<br>UART1 receive                       |

| U1TX         | PPS                    | PPS                                         | PPS                 | PPS                             | -           |                     |                                                            |

|              |                        |                                             |                     |                                 | 0           |                     | UART1 transmit                                             |

| U2CTS        | PPS                    | PPS                                         | PPS                 | PPS                             | I           | ST                  | UART2 clear to send                                        |

| U2RTS        | PPS                    | PPS                                         | PPS                 | PPS                             | 0           |                     | UART2 ready to send                                        |

| U2RX         | PPS                    | PPS                                         | PPS                 | PPS                             | I           | ST                  | UART2 receive                                              |

| U2TX         | PPS                    | PPS                                         | PPS                 | PPS                             | 0           |                     | UART2 transmit                                             |

| SCK1         | 22                     | 25                                          | 28                  | 14                              | I/O         | ST                  | Synchronous serial clock input/output for SPI1             |

| SDI1         | PPS                    | PPS                                         | PPS                 | PPS                             | I           | ST                  | SPI1 data in                                               |

| SDO1         | PPS                    | PPS                                         | PPS                 | PPS                             | 0           | _                   | SPI1 data out                                              |

| SS1          | PPS                    | PPS                                         | PPS                 | PPS                             | I/O         | ST                  | SPI1 slave synchronization or frame pulse I/O              |

| SCK2         | 23                     | 26                                          | 29                  | 15                              | I/O         | ST                  | Synchronous serial clock input/output for SPI2             |

| SDI2         | PPS                    | PPS                                         | PPS                 | PPS                             |             | ST                  | SPI2 data in                                               |

| SDO2         | PPS                    | PPS                                         | PPS                 | PPS                             | 0           | _                   | SPI2 data out                                              |

| SS2          | PPS                    | PPS                                         | PPS                 | PPS                             | I/O         | ST                  | SPI2 slave synchronization or frame pulse I/O              |

| SCL1         | 14                     | 17                                          | 18                  | 44                              | I/O         | ST                  | Synchronous serial clock input/output for<br>I2C1          |

|              | ST = Schm<br>TTL = TTL | MOS compa<br>itt Trigger in<br>input buffer | put with CN         | MOS levels                      |             | O = Outp<br>PPS = P | Analog input P = Power                                     |

####

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

## 3.2 Architecture Overview

The MIPS32 M4K processor core contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- Dual Internal Bus interfaces

- Power Management

- MIPS16e<sup>®</sup> Support

- · Enhanced JTAG (EJTAG) Controller

### 3.2.1 EXECUTION UNIT

The MIPS32 M4K processor core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- · 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

- Shifter and store aligner

## 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The MIPS32 M4K processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32 core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16-bit wide *rs*, 15 iterations are skipped and for a 24-bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32 core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

# TABLE 3-1:MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE HIGH-PERFORMANCE INTEGERMULTIPLY/DIVIDE UNIT LATENCIES AND REPEAT RATES

| Opcode                  | Operand Size (mul <i>rt</i> ) (div <i>rs</i> ) | Latency | Repeat Rate |

|-------------------------|------------------------------------------------|---------|-------------|

| MULT/MULTU, MADD/MADDU, | 16 bits                                        | 1       | 1           |

| MSUB/MSUBU              | 32 bits                                        | 2       | 2           |

| MUL                     | 16 bits                                        | 2       | 1           |

|                         | 32 bits                                        | 3       | 2           |

| DIV/DIVU                | 8 bits                                         | 12      | 11          |

|                         | 16 bits                                        | 19      | 18          |

|                         | 24 bits                                        | 26      | 25          |

|                         | 32 bits                                        | 33      | 32          |

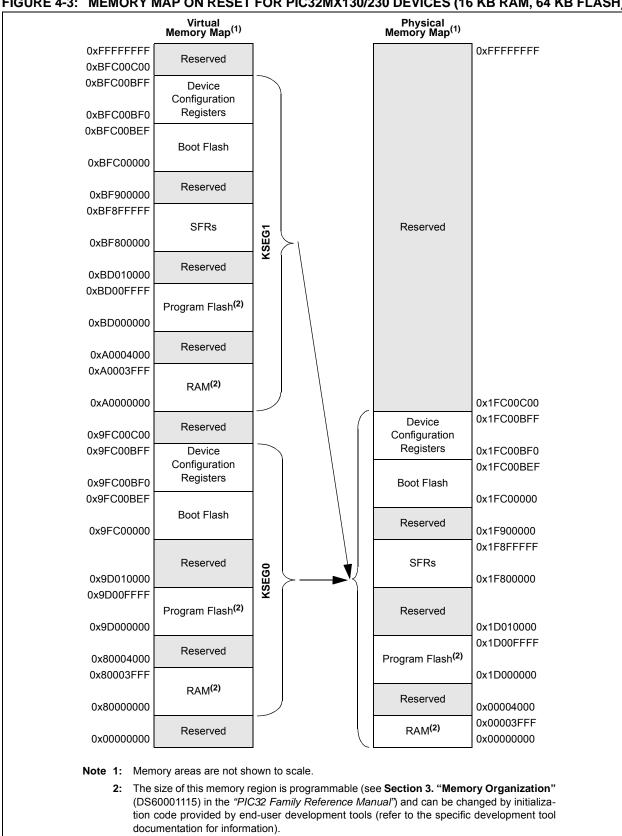

### FIGURE 4-3: MEMORY MAP ON RESET FOR PIC32MX130/230 DEVICES (16 KB RAM, 64 KB FLASH)

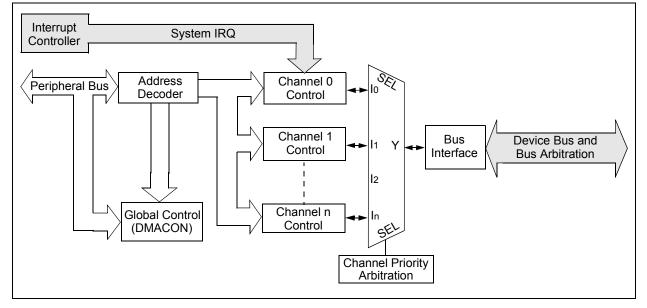

# 9.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32, such as Peripheral Bus devices: SPI, UART, PMP, etc., or memory itself. Figure 9-1 show a block diagram of the DMA Controller module.

The DMA Controller module has the following key features:

- Four identical channels, each featuring:

- Auto-increment source and destination address registers