#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Dectano                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256КВ (256К х 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

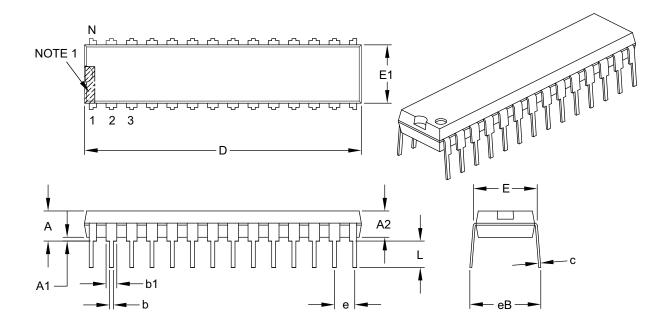

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx170f256b-50i-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-1: **PINOUT I/O DESCRIPTIONS**

|          |                   | Pin Nu                                      | nber <sup>(1)</sup>                    |                                        |             |                |                                                                                                                                                                                                |

|----------|-------------------|---------------------------------------------|----------------------------------------|----------------------------------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | 28-pin<br>QFN     | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC           | 36-pin<br>VTLA                         | 44-pin<br>QFN/<br>TQFP/<br>VTLA        | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                    |

| AN0      | 27                | 2                                           | 33                                     | 19                                     |             | Analog         | Analog input channels.                                                                                                                                                                         |

| AN1      | 28                | 3                                           | 34                                     | 20                                     | I           | Analog         |                                                                                                                                                                                                |

| AN2      | 1                 | 4                                           | 35                                     | 21                                     |             | Analog         |                                                                                                                                                                                                |

| AN3      | 2                 | 5                                           | 36                                     | 22                                     |             | Analog         |                                                                                                                                                                                                |

| AN4      | 3                 | 6                                           | 1                                      | 23                                     | I           | Analog         |                                                                                                                                                                                                |

| AN5      | 4                 | 7                                           | 2                                      | 24                                     | I           | Analog         |                                                                                                                                                                                                |

| AN6      | _                 | _                                           | 3                                      | 25                                     | I           | Analog         |                                                                                                                                                                                                |

| AN7      | _                 | _                                           | 4                                      | 26                                     | I           | Analog         |                                                                                                                                                                                                |

| AN8      | _                 | _                                           | _                                      | 27                                     | I           | Analog         |                                                                                                                                                                                                |

| AN9      | 23                | 26                                          | 29                                     | 15                                     | I           | Analog         |                                                                                                                                                                                                |

| AN10     | 22                | 25                                          | 28                                     | 14                                     | I           | Analog         |                                                                                                                                                                                                |

| AN11     | 21                | 24                                          | 27                                     | 11                                     | I           | Analog         |                                                                                                                                                                                                |

| AN12     | 20 <sup>(2)</sup> | 23 <sup>(2)</sup>                           | 26 <sup>(2)</sup><br>11 <sup>(3)</sup> | 10 <sup>(2)</sup><br>36 <sup>(3)</sup> | 1           | Analog         | *                                                                                                                                                                                              |

| CLKI     | 6                 | 9                                           | 7                                      | 30                                     | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                         |

| CLKO     | 7                 | 10                                          | 8                                      | 31                                     | 0           | _              | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes. Always associated<br>with OSC2 pin function. |

| OSC1     | 6                 | 9                                           | 7                                      | 30                                     | I           | ST/CMOS        | -                                                                                                                                                                                              |

| OSC2     | 7                 | 10                                          | 8                                      | 31                                     | 0           | -              | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes.                                              |

| SOSCI    | 8                 | 11                                          | 9                                      | 33                                     | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal<br>input; CMOS otherwise.                                                                                                                              |

| SOSCO    | 9                 | 12                                          | 10                                     | 34                                     | 0           | —              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                |

| REFCLKI  | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | Reference Input Clock                                                                                                                                                                          |

| REFCLKO  | PPS               | PPS                                         | PPS                                    | PPS                                    | 0           | —              | Reference Output Clock                                                                                                                                                                         |

| IC1      | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | Capture Inputs 1-5                                                                                                                                                                             |

| IC2      | PPS               | PPS                                         | PPS                                    | PPS                                    | 1           | ST             | 1                                                                                                                                                                                              |

| IC3      | PPS               | PPS                                         | PPS                                    | PPS                                    | 1           | ST             | 1                                                                                                                                                                                              |

| IC4      | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | 1                                                                                                                                                                                              |

| IC5      | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | 1                                                                                                                                                                                              |

|          | ST = Schm         | MOS compa<br>itt Trigger in<br>input buffer |                                        |                                        | •           | O = Outp       | Analog inputP = PowerutI = Inputeripheral Pin Select— = N/A                                                                                                                                    |

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability. 2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

| ILCIOI I     |                   |                   |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 |                   | —                | —                |

|              | U-0               | U-0               | U-0               | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |

| 23:16        | _                 | —                 | _                 | BMX<br>ERRIXI     | BMX<br>ERRICD     | BMX<br>ERRDMA     | BMX<br>ERRDS     | BMX<br>ERRIS     |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | —                 | -                 | —                 | _                 |                  | —                |

|              | U-0               | R/W-1             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-1            |

| 7:0          | _                 | BMX<br>WSDRM      | _                 | _                 | _                 | E                 | 3MXARB<2:0       | >                |

## REGISTER 4-1: BMXCON: BUS MATRIX CONFIGURATION REGISTER

### Legend:

| 5                 |                  |                                    |

|-------------------|------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

## bit 31-21 Unimplemented: Read as '0'

|          | Ommplemented. Read as 0                                                                                                                                                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 20   | BMXERRIXI: Enable Bus Error from IXI bit                                                                                                                                                                                              |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> </ul>                 |

| bit 19   | BMXERRICD: Enable Bus Error from ICD Debug Unit bit                                                                                                                                                                                   |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from ICD</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from ICD</li> </ul>                                       |

| bit 18   | BMXERRDMA: Bus Error from DMA bit                                                                                                                                                                                                     |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from DMA</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from DMA</li> </ul>                                       |

| bit 17   | BMXERRDS: Bus Error from CPU Data Access bit (disabled in Debug mode)                                                                                                                                                                 |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU data access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU data access</li> </ul>               |

| bit 16   | BMXERRIS: Bus Error from CPU Instruction Access bit (disabled in Debug mode)                                                                                                                                                          |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> </ul> |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 6    | BMXWSDRM: CPU Instruction or Data Access from Data RAM Wait State bit                                                                                                                                                                 |

|          | <ul> <li>1 = Data RAM accesses from CPU have one wait state for address setup</li> <li>0 = Data RAM accesses from CPU have zero wait states for address setup</li> </ul>                                                              |

| bit 5-3  | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 2-0  | BMXARB<2:0>: Bus Matrix Arbitration Mode bits                                                                                                                                                                                         |

|          | 111 = Reserved (using these Configuration modes will produce undefined behavior)                                                                                                                                                      |

|          | •                                                                                                                                                                                                                                     |

|          | •                                                                                                                                                                                                                                     |

|          | <ul><li>011 = Reserved (using these Configuration modes will produce undefined behavior)</li><li>010 = Arbitration Mode 2</li></ul>                                                                                                   |

|          | 001 = Arbitration Mode 1 (default)<br>000 = Arbitration Mode 0                                                                                                                                                                        |

|          |                                                                                                                                                                                                                                       |

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

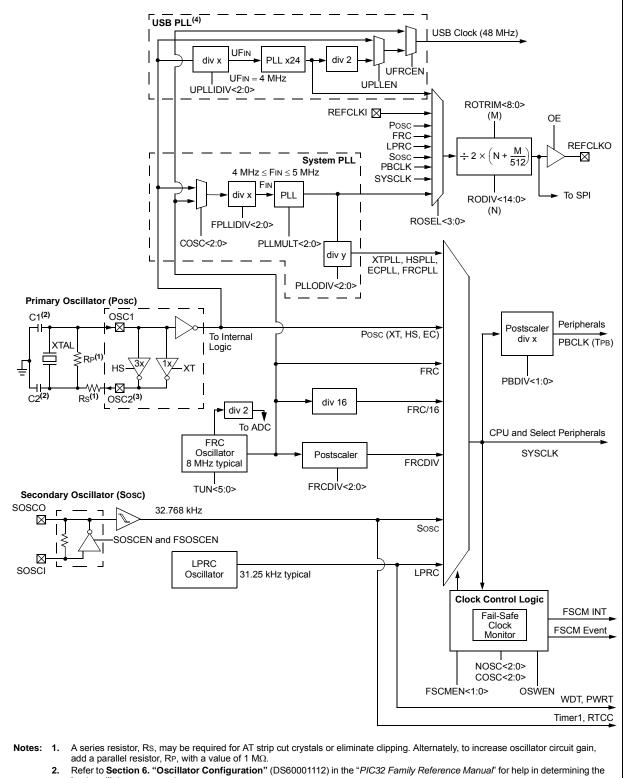

## FIGURE 8-1: OSCILLATOR DIAGRAM

Refer to Section 6. "Oscillator Configuration" (DS60001112) in the "PIC32 Family Reference Manual" for help in determinin best oscillator components.

3. The PBCLK out is only available on the OSC2 pin in certain clock modes.

4. The USB PLL is only available on PIC32MX2XX devices.

## 8.1 Oscillator Control Regiters

| TAB                         | LE 8-1:                         | 09        | SCILLA | ATOR O | CONTR                                    | OL REG     | ISTER I   | MAP   |           |      |         |                      |          |       |        |                       |           |       |                     |

|-----------------------------|---------------------------------|-----------|--------|--------|------------------------------------------|------------|-----------|-------|-----------|------|---------|----------------------|----------|-------|--------|-----------------------|-----------|-------|---------------------|

| ess                         |                                 | 0         |        |        |                                          |            |           |       |           |      | Bits    |                      |          |       |        |                       |           |       | ú                   |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15  | 30/14  | 29/13                                    | 28/12      | 27/11     | 26/10 | 25/9      | 24/8 | 23/7    | 22/6                 | 21/5     | 20/4  | 19/3   | 18/2                  | 17/1      | 16/0  | All Reset           |

| F000                        | OSCCON                          | 31:16     | —      | _      | Р                                        | LLODIV<2:0 | )>        | F     | RCDIV<2:0 | )>   | —       | SOSCRDY              | PBDIVRDY | PBDI\ | /<1:0> | PL                    | LMULT<2:0 | >     | x1xx <sup>(2)</sup> |

| FUUU                        | 030001                          | 15:0      | —      |        | COSC<2:0                                 | V          | Ι         |       | NOSC<2:0  | >    | CLKLOCK | ULOCK <sup>(3)</sup> | SLOCK    | SLPEN | CF     | UFRCEN <sup>(3)</sup> | SOSCEN    | OSWEN | xxxx(2)             |

| F010                        | OSCTUN                          | 31:16     | _      | _      |                                          | _          | _         |       |           | _    | _       | _                    | _        | _     |        | _                     | —         | _     | 0000                |

| 1010                        | 030101                          | 15:0      | _      | _      |                                          | _          | _         |       |           | _    | _       | _                    |          |       | TUN    | l<5:0>                |           |       | 0000                |

| 5000                        |                                 | 31:16     | _      |        |                                          |            |           |       |           |      | RODIV<1 | 4:0>                 |          |       |        |                       |           |       | 0000                |

| F020                        | REFOCON                         | 15:0      | ON     |        | SIDL OE RSLP - DIVSWEN ACTIVE ROSEL<3:0> |            |           |       |           |      |         | 0000                 |          |       |        |                       |           |       |                     |

| F000                        | DEEOTDIM                        | 31:16     |        |        |                                          | R          | OTRIM<8:0 | )>    |           |      |         | _                    | _        | _     | _      | _                     | _         | _     | 0000                |

| F030                        | REFOTRIM                        | 15:0      | _      | _      |                                          | _          | _         |       |           | -    | _       | _                    | _        | _     |        | _                     | —         | _     | 0000                |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

3: This bit is only available on PIC32MX2XX devices.

## REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- bit 3-0 ROSEL<3:0>: Reference Clock Source Select bits<sup>(1)</sup>

- 1111 = Reserved; do not use

- 1001 = Reserved; do not use 1000 = REFCLKI 0111 = System PLL output 0110 = USB PLL output 0101 = Sosc 0100 = LPRC 0011 = FRC 0010 = POSC 0001 = PBCLK 0000 = SYSCLK

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- 2: This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

## 9.1 DMA Control Registers

#### TABLE 9-1: DMA GLOBAL REGISTER MAP

| ess                         |                                 | Ċ,        |       |       |       |         |         |       |      | Bi       | ts        |      |      |      |      |      |           |      | s         |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|---------|---------|-------|------|----------|-----------|------|------|------|------|------|-----------|------|-----------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12   | 27/11   | 26/10 | 25/9 | 24/8     | 23/7      | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1      | 16/0 | All Reset |

| 2000                        | DMACON                          | 31:16     | _     | _     | -     | —       | —       | _     | —    | —        | —         | -    | -    | _    | -    | -    | —         | _    | 0000      |

| 3000                        | DIVIACON                        | 15:0      | ON    | —     | _     | SUSPEND | DMABUSY | —     | _    | —        | _         | —    | —    | _    | —    | —    | —         | _    | 0000      |

| 2010                        | DMASTAT                         | 31:16     | -     | _     | —     | —       | —       | —     | —    | —        | _         | _    | _    | _    | _    | —    | —         | _    | 0000      |

| 3010                        | DIVIASTAT                       | 15:0      | -     | _     | —     | —       | —       | —     | —    | —        | _         | _    | _    | _    | RDWR | DI   | MACH<2:0> | .(2) | 0000      |

| 3020                        | DMAADDR                         | 31:16     |       |       |       |         |         |       |      | DMAADD   | D-31:05   |      |      |      |      |      |           |      | 0000      |

| 3020                        | DIVIAADDR                       | 15:0      |       |       |       |         |         |       |      | DIVIAADL | vix~51.02 |      |      |      |      |      |           |      | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### TABLE 9-2: DMA CRC REGISTER MAP

| ess                         |                                 | â         |       |                                                                                                                                                                                                                                                                                                       | -             |       |       |       |      | В      | ts       |      | -    |      |      |      |      |      |            |

|-----------------------------|---------------------------------|-----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------|-------|-------|------|--------|----------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14                                                                                                                                                                                                                                                                                                 | 29/13         | 28/12 | 27/11 | 26/10 | 25/9 | 24/8   | 23/7     | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 2020                        | DCRCCON                         | 31:16     | —     | _                                                                                                                                                                                                                                                                                                     | BYTO          | <1:0> | WBO   | —     | —    | BITO   | _        | —    | —    | _    | _    | _    | —    | _    | 0000       |

| 3030                        | DURUUUN                         | 15:0      | —     | -         BYTO<1:0>         WBO         -         -         BITO         -         -         -         -         -         -         -         0000           -         -         -         PLEN<4:0>         CRCEN         CRCAPP         CRCTYP         -         -         CRCCH<2:0>         0000 |               |       |       |       |      |        |          |      |      |      |      |      |      |      |            |

| 2040                        | DCRCDATA                        | 31:16     |       |                                                                                                                                                                                                                                                                                                       |               |       |       |       |      |        | TA<31:0> |      |      |      |      |      |      |      | 0000       |

| 3040                        | DURUDAIA                        | 15:0      |       |                                                                                                                                                                                                                                                                                                       |               |       |       |       |      | DURUDA | IA~51.02 |      |      |      |      |      |      |      | 0000       |

| 3050                        | DCRCXOR                         | 31:16     |       |                                                                                                                                                                                                                                                                                                       | DCRCXOR<31:0> |       |       |       |      |        |          |      |      |      |      |      |      |      |            |

| 3050                        | DUNUAUR                         | 15:0      |       |                                                                                                                                                                                                                                                                                                       |               |       |       |       |      | DCRCAU | N-51.02  |      |      |      |      |      |      |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

## TABLE 9-3: DMA CHANNELS 0-3 REGISTER MAP (CONTINUED)

| ess                         |                                 | ē             |        |                   |       |       | -      |       |      | Bi     | ts      |        |        |        |              |        |        |        | s          |

|-----------------------------|---------------------------------|---------------|--------|-------------------|-------|-------|--------|-------|------|--------|---------|--------|--------|--------|--------------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14             | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7    | 22/6   | 21/5   | 20/4   | 19/3         | 18/2   | 17/1   | 16/0   | All Resets |

| 3280                        | DCH2CPTR                        | 31:16         | —      | _                 | —     | _     |        | _     |      | —      |         | _      | _      |        |              | _      | _      |        | 0000       |

| 5200                        | DONZOFIK                        | 15:0          |        |                   |       |       |        |       |      | CHCPT  | R<15:0> |        |        |        |              |        |        |        | 0000       |

| 3290                        | DCH2DAT                         | 31:16         | _      | _                 | —     | —     |        | _     |      | —      | _       | _      | —      | _      | —            | _      | _      |        | 0000       |

| 3290                        | DCHZDAI                         | 15:0          | _      |                   | _     | _     |        | -     |      | -      |         |        |        | CHPDA  | AT<7:0>      |        |        |        | 0000       |

| 2240                        | DCH3CON                         | 31:16         | _      | _                 | _     | _     | _      | _     | _    | _      | _       | _      | _      | _      | _            | _      | _      | _      | 0000       |

| 32A0                        | DCH3CON                         | 15:0          | CHBUSY |                   |       |       |        |       |      |        |         |        |        | 0000   |              |        |        |        |            |

| 3280                        | DCH3ECON                        | 31:16         | —      |                   |       |       |        |       |      |        |         |        |        | OOFF   |              |        |        |        |            |

| 5200                        |                                 | 15:0          |        |                   |       | CHSIR | Q<7:0> |       |      |        | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN       | _      | _      | _      | FF00       |

| 32C0                        | DCH3INT                         | 31:16         | —      | —                 | —     | —     | -      | _     | -    | —      | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE       | CHCCIE | CHTAIE | CHERIE | 0000       |

| 0200                        |                                 | 15:0          | —      |                   |       | _     | —      | _     | —    | —      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF       | CHCCIF | CHTAIF | CHERIF | 0000       |

| 32D0                        | DCH3SSA                         | 31:16<br>15:0 |        |                   |       |       |        |       |      | CHSSA  | <31:0>  |        |        |        |              |        |        |        | 0000       |

|                             |                                 | 31:16         |        |                   |       |       |        |       |      |        |         |        |        |        |              |        |        |        | 0000       |

| 32E0                        | DCH3DSA                         | 15:0          |        |                   |       |       |        |       |      | CHDSA  | <31:0>  |        |        |        |              |        |        |        | 0000       |

| 0050                        | DOI 100017                      | 31:16         |        | _                 |       |       | _      | _     | _    |        |         |        |        |        |              | _      |        | _      | 0000       |

| 32FU                        | DCH3SSIZ                        | 15:0          |        |                   |       |       |        |       |      | CHSSIZ | 2<15:0> |        |        |        |              |        |        |        | 0000       |

| 2200                        | DCH3DSIZ                        | 31:16         | —      | —                 | —     | —     | _      | —     | _    | —      | _       | —      | —      | —      | —            | _      | —      | _      | 0000       |

| 3300                        | DCH3D3IZ                        | 15:0          |        |                   |       |       |        |       |      | CHDSIZ | 2<15:0> |        |        |        |              |        |        |        | 0000       |

| 3310                        | DCH3SPTR                        | 31:16         | —      | _                 | —     | _     |        |       |      | _      | —       |        | _      |        | _            |        |        |        | 0000       |

| 3310                        | DOI IJOF I K                    | 15:0          |        |                   |       |       |        |       |      | CHSPTF | ۲<15:0> |        |        |        |              |        |        |        | 0000       |

| 3320                        | DCH3DPTR                        | 31:16         | —      | —                 | —     | —     | _      | _     | _    | —      | _       | _      | —      | —      | —            | _      | —      | _      | 0000       |

| 0020                        |                                 | 15:0          |        |                   |       |       |        |       |      | CHDPT  | R<15:0> |        |        |        |              |        |        |        | 0000       |

| 3330                        | <b>DCH3CSIZ</b>                 | 31:16         | —      | _                 | —     | —     | —      | —     | —    | —      | —       | —      | —      | —      | —            | —      | —      | —      | 0000       |

|                             |                                 | 15:0          |        |                   |       |       |        |       |      |        |         |        |        | 0000   |              |        |        |        |            |

| 3340                        | DCH3CPTR                        | 31:16         | _      | —                 | —     | —     | _      | —     | _    | —      | _       | —      | —      | —      | —            | —      | —      | _      | 0000       |

|                             |                                 | 15:0          |        | CHCPTR<15:0> 0000 |       |       |        |       |      |        |         |        |        |        |              |        |        |        |            |

| 3350                        | DCH3DAT                         | 31:16         | —      | _                 | —     | _     | _      | _     | —    | _      | _       | —      | —      | -      | —<br>T :7 0: | —      | —      | —      | 0000       |

| <u> </u>                    |                                 | 15:0          | —      | —                 | —     | —     | —      | —     | —    | _      |         |        |        | CHPDA  | AT<7:0>      |        |        |        | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24     |                   |                   |                   | CHSSA<            | 31:24>            |                   |                  |                  |

| 00:40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16     |                   |                   |                   | CHSSA<            | 23:16>            |                   |                  |                  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8      |                   |                   |                   | CHSSA             | <15:8>            |                   |                  |                  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0       |                   |                   |                   | CHSSA             | <7:0>             |                   |                  |                  |

## **REGISTER 9-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER**

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0

CHSSA<31:0> Channel Source Start Address bits

Channel source start address.

Note: This must be the physical address of the source.

#### **REGISTER 9-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | CHDSA<            | 31:24>            |                   |                  |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | CHDSA<            | 23:16>            |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CHDSA             | <15:8>            |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHDSA             | <7:0>             |                   |                  |                  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **CHDSA<31:0>:** Channel Destination Start Address bits Channel destination start address.

$\ensuremath{\textbf{Note:}}$  This must be the physical address of the destination.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 51.24        |                   | _                 |                   | —                 | —                 |                   |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 |                   | —                 | —                 |                   | -                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | _                 | —                 | _                 | —                 | —                 | -                 | -                | —                |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0            |

| 7:0          | UTEYE             | UOEMON            | _                 | USBSIDL           | _                 | _                 | _                | UASUSPND         |

#### REGISTER 10-20: U1CNFG1: USB CONFIGURATION 1 REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7 UTEYE: USB Eye-Pattern Test Enable bit

- 1 = Eye-Pattern Test is enabled

- 0 = Eye-Pattern Test is disabled

#### bit 6 **UOEMON:** USB OE Monitor Enable bit

1 = OE signal is active; it indicates intervals during which the D+/D- lines are driving

0 = OE signal is inactive

#### bit 5 Unimplemented: Read as '0'

- bit 4 USBSIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

#### bit 3-1 Unimplemented: Read as '0'

#### bit 0 UASUSPND: Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (U1PWRC<1>) in Register 10-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (U1PWRC<1>) to suspend the module, including the USB 48 MHz clock.

## 11.3 Peripheral Pin Select

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin-count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only option.

The Peripheral Pin Select (PPS) configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The PPS configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

## 11.3.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the PPS feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

## 11.3.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digitalonly peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital-only peripheral modules are never included in the PPS feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin.

Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

### 11.3.3 CONTROLLING PERIPHERAL PIN SELECT

PPS features are controlled through two sets of SFRs: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

## 11.3.4 INPUT MAPPING

The inputs of the PPS options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The [*pin name*]R registers, where [*pin name*] refers to the peripheral pins listed in Table 11-1, are used to configure peripheral input mapping (see Register 11-1). Each register contains sets of 4 bit fields. Programming these bit fields with an appropriate value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field is shown in Table 11-1.

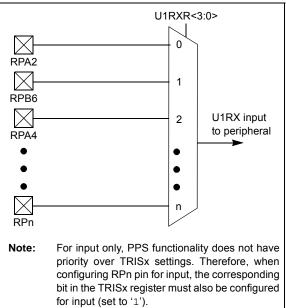

For example, Figure 11-2 illustrates the remappable pin selection for the U1RX input.

#### FIGURE 11-2: REMAPPABLE INPUT EXAMPLE FOR U1RX

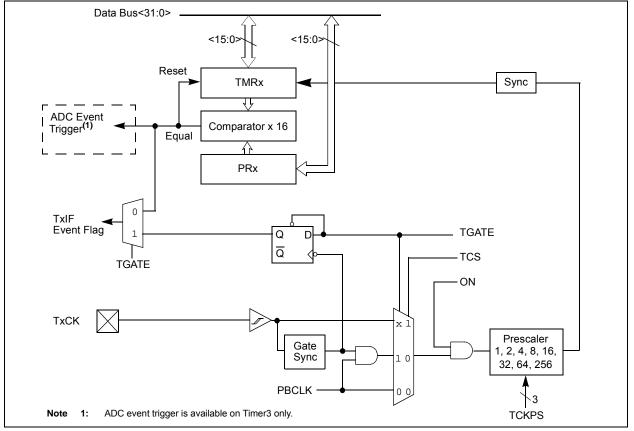

## 13.0 TIMER2/3, TIMER4/5

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features four synchronous 16-bit timers (default) that can operate as a freerunning interval timer for various timing applications and counting external events. The following modes are supported:

- Synchronous internal 16-bit timer

- Synchronous internal 16-bit gated timer

- · Synchronous external 16-bit timer

Two 32-bit synchronous timers are available by combining Timer2 with Timer3 and Timer4 with Timer5. The 32-bit timers can operate in three modes:

- Synchronous internal 32-bit timer

- · Synchronous internal 32-bit gated timer

- Synchronous external 32-bit timer

| Note: | In this chapter, references to registers, |

|-------|-------------------------------------------|

|       | TxCON, TMRx and PRx, use 'x' to           |

|       | represent Timer2 through Timer5 in 16-bit |

|       | modes. In 32-bit modes, 'x' represents    |

|       | Timer2 or Timer4 and 'y' represents       |

|       | Timer3 or Timer5.                         |

## **13.1 Additional Supported Features**

- · Selectable clock prescaler

- Timers operational during CPU idle

- Time base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

- ADC event trigger (Timer3 in 16-bit mode, Timer2/3 in 32-bit mode)

- Fast bit manipulation using CLR, SET and INV registers

Figure 13-1 and Figure 13-2 illustrate block diagrams of Timer2/3 and Timer4/5.

## FIGURE 13-1: TIMER2-TIMER5 BLOCK DIAGRAM (16-BIT)

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04-04     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 02:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | —                 | -                 | -                 | _                 | _                 | -                | —                |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8      | 0N <sup>(1)</sup> | —                 | SIDL              | _                 | _                 | _                 | FEDGE            | C32              |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |

|           | ICTMR             | ICI<              | 1:0>              | ICOV              | ICBNE             |                   | ICM<2:0>         |                  |

## REGISTER 15-1: ICxCON: INPUT CAPTURE 'x' CONTROL REGISTER

## Legend:

| R = Readable bit                        | W = Writable bit | U = Unimplemented bit |                  |

|-----------------------------------------|------------------|-----------------------|------------------|

| -n = Bit Value at POR: ('0', '1', x = u | nknown)          | P = Programmable bit  | r = Reserved bit |

| bit 31-16 | Unimplemented: Read as '0'                                                                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | <b>ON:</b> Input Capture Module Enable bit <sup>(1)</sup>                                                                                                                                |

|           | 1 = Module is enabled                                                                                                                                                                    |

|           | 0 = Disable and reset module, disable clocks, disable interrupt generation and allow SFR modifications                                                                                   |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 13    | SIDL: Stop in Idle Control bit                                                                                                                                                           |

|           | <ul> <li>1 = Halt in Idle mode</li> <li>0 = Continue to operate in Idle mode</li> </ul>                                                                                                  |

| bit 12-10 | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 9     | FEDGE: First Capture Edge Select bit (only used in mode 6, ICM<2:0> = 110)                                                                                                               |

|           | 1 = Capture rising edge first                                                                                                                                                            |

|           | 0 = Capture falling edge first                                                                                                                                                           |

| bit 8     | C32: 32-bit Capture Select bit                                                                                                                                                           |

|           | 1 = 32-bit timer resource capture                                                                                                                                                        |

|           | 0 = 16-bit timer resource capture                                                                                                                                                        |

| bit 7     | ICTMR: Timer Select bit (Does not affect timer selection when C32 (ICxCON<8>) is '1')                                                                                                    |

|           | 0 = Timer3 is the counter source for capture                                                                                                                                             |

|           | 1 = Timer2 is the counter source for capture                                                                                                                                             |

| bit 6-5   | ICI<1:0>: Interrupt Control bits                                                                                                                                                         |

|           | <ul> <li>11 = Interrupt on every fourth capture event</li> <li>10 = Interrupt on every third capture event</li> </ul>                                                                    |

|           | 01 = Interrupt on every second capture event                                                                                                                                             |

|           | 00 = Interrupt on every capture event                                                                                                                                                    |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                                                 |

|           | 1 = Input capture overflow has occurred                                                                                                                                                  |

|           | 0 = No input capture overflow has occurred                                                                                                                                               |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                                                             |

|           | <ul> <li>1 = Input capture buffer is not empty; at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>                                        |

| Note 1:   | When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. |

|           | STOCEN Gyole infinediately following the instruction that deals the module's ON bit.                                                                                                     |

NOTES:

#### 22.1 **ADC Control Registers**

## TABLE 22-1: ADC REGISTER MAP

| $ \frac{5}{900} = \frac{1}{150} = 1$ | ess                      |                        |           |        |           |        |        |        |        |          | Bi          | ts       |           |       |         |         |       |        |       |            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------|-----------|--------|-----------|--------|--------|--------|--------|----------|-------------|----------|-----------|-------|---------|---------|-------|--------|-------|------------|

| 900         ADICONI(***)         31:16         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Virtual Addr<br>(BF80_#) |                        | Bit Range | 31/15  | 30/14     | 29/13  | 28/12  | 27/11  | 26/10  | 25/9     | 24/8        | 23/7     | 22/6      | 21/5  | 20/4    | 19/3    | 18/2  | 17/1   | 16/0  | All Resets |

| 150         ON         -         SIDL         -         -         ONM         SIRC20>         CRRSM         -         AM         SMM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          | AD1CON1(1)             | 31:16     | _      | —         | _      |        | _      |        | _        | —           |          |           | —     | —       | —       | —     | _      | —     | 0000       |

| 9010         ADICONUN         15.0         VCFG<2.0>         OFFCAL         —         CSCNA         —         —         BUFS         —         SMPI<3:0>         BUFM         A           9020         ADICON301         31:16         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         DC         ADC         ADC         AD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9000                     | ADICONIC               | 15:0      | ON     | _         | SIDL   | —      | _      | -      | ORM<2:0> | >           |          | SSRC<2:0> | >     | CLRASAM | _       | ASAM  | SAMP   | DONE  | 0000       |

| Image: constraint of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9010                     |                        |           |        | —         |        |        | —      | —      | _        | —           | —        | _         |       | —       | —       | —     | _      |       | 0000       |