Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 50MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

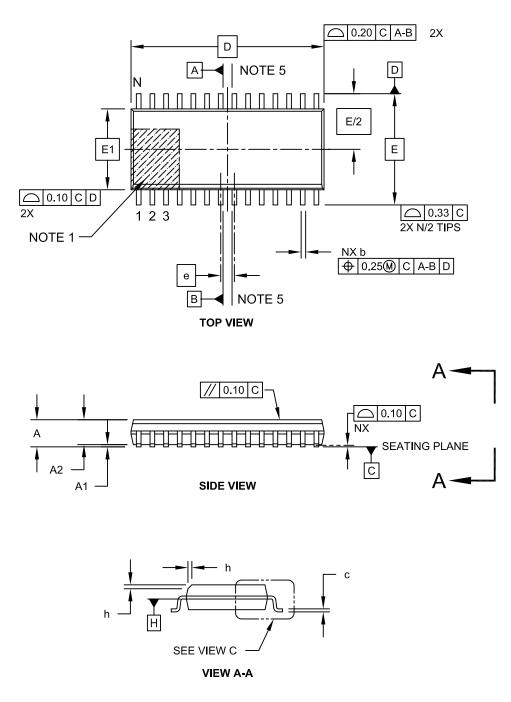

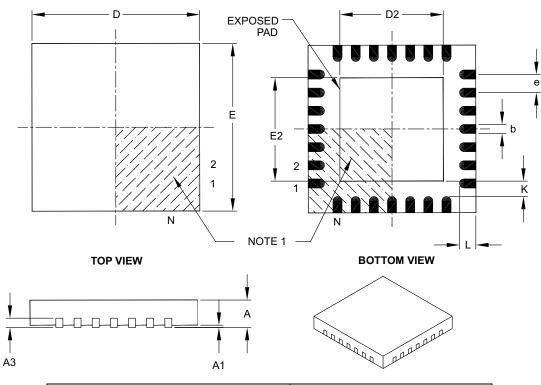

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                    |

| Supplier Device Package    | 28-SSOP                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx170f256bt-50i-ss |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-1: **PINOUT I/O DESCRIPTIONS**

|          |                   | Pin Nu                                      | nber <sup>(1)</sup>                    |                                        |             |                |                                                                                                                                                                                                |  |  |  |  |

|----------|-------------------|---------------------------------------------|----------------------------------------|----------------------------------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name | 28-pin<br>QFN     | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC           | 36-pin<br>VTLA                         | 44-pin<br>QFN/<br>TQFP/<br>VTLA        | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                    |  |  |  |  |

| AN0      | 27                | 2                                           | 33                                     | 19                                     |             | Analog         | Analog input channels.                                                                                                                                                                         |  |  |  |  |

| AN1      | 28                | 3                                           | 34                                     | 20                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |  |

| AN2      | 1                 | 4                                           | 35                                     | 21                                     |             | Analog         |                                                                                                                                                                                                |  |  |  |  |

| AN3      | 2                 | 5                                           | 36                                     | 22                                     |             | Analog         |                                                                                                                                                                                                |  |  |  |  |

| AN4      | 3                 | 6                                           | 1                                      | 23                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |  |

| AN5      | 4                 | 7                                           | 2                                      | 24                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |  |

| AN6      | _                 | _                                           | 3                                      | 25                                     | 1           | Analog         |                                                                                                                                                                                                |  |  |  |  |

| AN7      | _                 | _                                           | 4                                      | 26                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |  |

| AN8      | _                 | _                                           | _                                      | 27                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |  |

| AN9      | 23                | 26                                          | 29                                     | 15                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |  |

| AN10     | 22                | 25                                          | 28                                     | 14                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |  |

| AN11     | 21                | 24                                          | 27                                     | 11                                     | I           | Analog         |                                                                                                                                                                                                |  |  |  |  |

| AN12     | 20 <sup>(2)</sup> | 23 <sup>(2)</sup>                           | 26 <sup>(2)</sup><br>11 <sup>(3)</sup> | 10 <sup>(2)</sup><br>36 <sup>(3)</sup> | 1           | Analog         | *                                                                                                                                                                                              |  |  |  |  |

| CLKI     | 6                 | 9                                           | 7                                      | 30                                     | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                         |  |  |  |  |

| CLKO     | 7                 | 10                                          | 8                                      | 31                                     | 0           | _              | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes. Always associated<br>with OSC2 pin function. |  |  |  |  |

| OSC1     | 6                 | 9                                           | 7                                      | 30                                     | I           | ST/CMOS        | -                                                                                                                                                                                              |  |  |  |  |

| OSC2     | 7                 | 10                                          | 8                                      | 31                                     | 0           | -              | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes.                                              |  |  |  |  |

| SOSCI    | 8                 | 11                                          | 9                                      | 33                                     | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal<br>input; CMOS otherwise.                                                                                                                              |  |  |  |  |

| SOSCO    | 9                 | 12                                          | 10                                     | 34                                     | 0           | —              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                |  |  |  |  |

| REFCLKI  | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | Reference Input Clock                                                                                                                                                                          |  |  |  |  |

| REFCLKO  | PPS               | PPS                                         | PPS                                    | PPS                                    | 0           | —              | Reference Output Clock                                                                                                                                                                         |  |  |  |  |

| IC1      | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | Capture Inputs 1-5                                                                                                                                                                             |  |  |  |  |

| IC2      | PPS               | PPS                                         | PPS                                    | PPS                                    | 1           | ST             | 1                                                                                                                                                                                              |  |  |  |  |

| IC3      | PPS               | PPS                                         | PPS                                    | PPS                                    | 1           | ST             | 1                                                                                                                                                                                              |  |  |  |  |

| IC4      | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | 1                                                                                                                                                                                              |  |  |  |  |

| IC5      | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | 1                                                                                                                                                                                              |  |  |  |  |

|          | ST = Schm         | MOS compa<br>itt Trigger in<br>input buffer |                                        |                                        | •           | O = Outp       | Analog inputP = PowerutI = Inputeripheral Pin Select— = N/A                                                                                                                                    |  |  |  |  |

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability. 2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

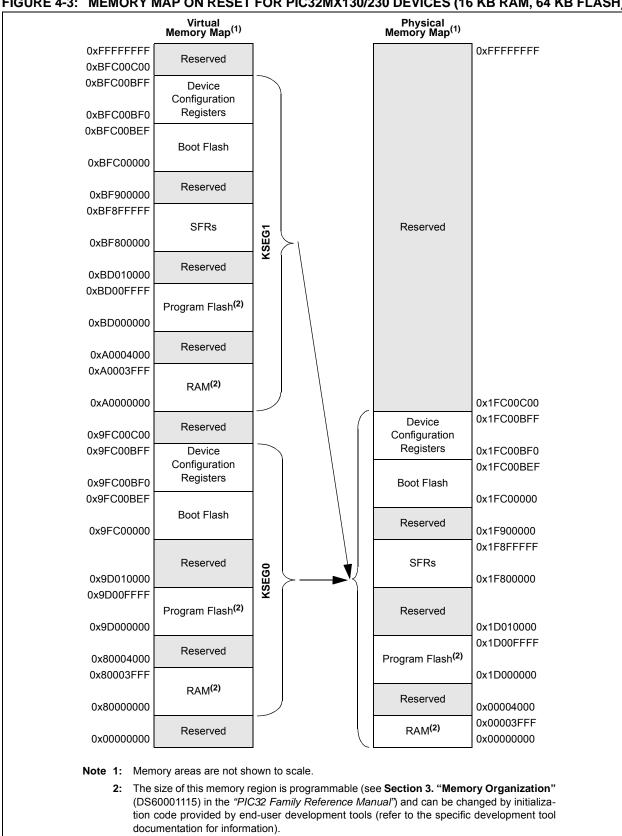

#### FIGURE 4-3: MEMORY MAP ON RESET FOR PIC32MX130/230 DEVICES (16 KB RAM, 64 KB FLASH)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        | ROTRIM<8:1>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 00.40        | R/W-0             | R-0               | R-0 U-0           |                   | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | ROTRIM<0>         | _                 | _                 | _                 | —                 | _                 | —                | —                |  |  |  |  |  |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0 U-0           |                   | U-0              | U-0              |  |  |  |  |  |

| 15:8         | —                 | _                 | _                 | _                 | —                 | _                 | —                | —                |  |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 7:0          | _                 | _                 | _                 | _                 | —                 | _                 | _                | —                |  |  |  |  |  |

#### REGISTER 8-4: REFOTRIM: REFERENCE OSCILLATOR TRIM REGISTER

#### Legend:

| Logona.           |                  |                                    |                    |  |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |  |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

Note: While the ON (REFOCON<15>) bit is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

### TABLE 9-3: DMA CHANNELS 0-3 REGISTER MAP (CONTINUED)

| ess                         |                                   | ē         |                  |       |       |       | -      |       |      | Bi     | ts      |        |        |        |              |        |        |        | s          |

|-----------------------------|-----------------------------------|-----------|------------------|-------|-------|-------|--------|-------|------|--------|---------|--------|--------|--------|--------------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup>   | Bit Range | 31/15            | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7    | 22/6   | 21/5   | 20/4   | 19/3         | 18/2   | 17/1   | 16/0   | All Resets |

| 3280                        | DCH2CPTR                          | 31:16     | —                | _     | —     | _     |        | _     |      | —      |         | _      | _      |        |              | _      | _      |        | 0000       |

| 5200                        | DONZOFIK                          | 15:0      | CHCPTR<15:0> 000 |       |       |       |        |       |      |        |         |        |        |        | 0000         |        |        |        |            |

| 3290                        | DCH2DAT                           | 31:16     | _                | _     | —     | —     |        | _     |      | —      | _       | _      | —      | _      | —            | _      | _      |        | 0000       |

| 3290                        | DCHZDAI                           | 15:0      | _                |       | _     | _     |        | -     |      | -      |         |        |        | CHPDA  | AT<7:0>      |        |        |        | 0000       |

| 2240                        | 2A0 DCH3CON                       | 31:16     | _                | _     | _     | _     | _      | _     | _    | _      | _       | _      | _      | _      | _            | _      | _      | _      | 0000       |

| 32AU                        | DCH3CON                           | 15:0      | CHBUSY           | _     | _     | _     |        |       |      | CHCHNS | CHEN    | CHAED  | CHCHN  | CHAEN  | —            | CHEDET | CHPR   | l<1:0> | 0000       |

| 3280                        | DCH3ECON                          | 31:16     | —                | _     | —     | —     | _      | _     | _    | —      |         |        |        | CHAIR  | Q<7:0>       |        |        |        | OOFF       |

| 5200                        |                                   | 15:0      |                  |       |       | CHSIR | Q<7:0> |       |      |        | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN       | _      | _      | _      | FF00       |

| 32C0                        | DCH3INT                           | 31:16     | —                | —     | —     | —     | -      | _     | -    | —      | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE       | CHCCIE | CHTAIE | CHERIE | 0000       |

| 0200                        |                                   | 15:0      | —                |       |       | _     | —      | _     | _    | —      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF       | CHCCIF | CHTAIF | CHERIF | 0000       |

| 32D0                        | DCH3SSA 31:16<br>15:0 CHSSA<31:0> |           |                  |       |       |       |        |       |      |        |         |        | 0000   |        |              |        |        |        |            |

|                             |                                   | 31:16     | 000              |       |       |       |        |       |      |        |         |        |        |        | 0000         |        |        |        |            |

| 32E0                        | DCH3DSA                           | 15:0      |                  |       |       |       |        |       |      | CHDSA  | <31:0>  |        |        |        |              |        |        |        | 0000       |

| 0050                        | 00100017                          | 31:16     |                  | _     |       |       | _      | _     | _    |        |         |        |        |        |              | _      |        | _      | 0000       |

| 32FU                        | DCH3SSIZ                          | 15:0      |                  |       |       |       |        |       |      | CHSSIZ | 2<15:0> |        |        |        |              |        |        |        | 0000       |

| 2200                        | DCH3DSIZ                          | 31:16     | —                | —     | —     | —     | _      | —     | _    | —      | _       | —      | —      | —      | —            | _      | —      | _      | 0000       |

| 3300                        | DCH3D3IZ                          | 15:0      |                  |       |       |       |        |       |      | CHDSIZ | 2<15:0> |        |        |        |              |        |        |        | 0000       |

| 3310                        | DCH3SPTR                          | 31:16     | —                | _     | —     | _     |        |       |      | _      | —       |        | _      |        | _            |        |        |        | 0000       |

| 3310                        | DOI IJOF I K                      | 15:0      |                  |       |       |       |        |       |      | CHSPTF | ۲<15:0> |        |        |        |              |        |        |        | 0000       |

| 3320                        | DCH3DPTR                          | 31:16     | —                | —     | —     | —     | _      | _     | _    | —      | _       | _      | —      | —      | —            | _      | —      | _      | 0000       |

| 0020                        |                                   | 15:0      |                  |       |       |       |        |       |      | CHDPT  | R<15:0> |        |        |        |              |        |        |        | 0000       |

| 3330                        | <b>DCH3CSIZ</b>                   | 31:16     | —                | _     | —     | —     | —      | —     | —    | —      | —       | —      | —      | —      | —            | —      | —      | —      | 0000       |

|                             |                                   | 15:0      |                  |       |       |       |        |       |      | CHCSIZ | 2<15:0> |        |        |        |              |        |        |        | 0000       |

| 3340                        | DCH3CPTR                          | 31:16     | _                | —     | —     | —     | _      | —     | _    | —      | _       | —      | —      | —      | —            | —      | —      | _      | 0000       |

|                             |                                   | 15:0      |                  |       |       |       |        |       |      | CHCPT  | ≺<15:0> |        |        |        |              |        |        |        | 0000       |

| 3350                        | DCH3DAT                           | 31:16     | —                | _     | —     | _     | _      | _     | —    | _      | _       | —      | —      | -      | —<br>T :7 0: | —      | —      | —      | 0000       |

| <u> </u>                    |                                   | 15:0      | —                | —     | —     | —     | —      | —     | —    | _      |         |        |        | CHPDA  | AT<7:0>      |        |        |        | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | CHSDIE            | CHSHIE            | CHDDIE            | CHDHIE            | CHBCIE            | CHCCIE            | CHTAIE           | CHERIE           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | _                 | —                 | —                 | _                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CHSDIF            | CHSHIF            | CHDDIF            | CHDHIF            | CHBCIF            | CHCCIF            | CHTAIF           | CHERIF           |

#### **REGISTER 9-9:** DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER

#### Legend:

| •                 |                  |                                    |                    |  |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |  |

| bit 31-24  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| bit 23     | CHSDIE: Channel Source Done Interrupt Enable bit<br>1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| bit 22     | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| DIL 22     | CHSHIE: Channel Source Half Empty Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| bit 21     | <b>CHDDIE:</b> Channel Destination Done Interrupt Enable bit<br>1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|            | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| bit 20     | CHDHIE: Channel Destination Half Full Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| bit 19     | <b>CHBCIE:</b> Channel Block Transfer Complete Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| bit 18     | CHCCIE: Channel Cell Transfer Complete Interrupt Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|            | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| bit 17     | CHTAIE: Channel Transfer Abort Interrupt Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|            | <ul><li>1 = Interrupt is enabled</li><li>0 = Interrupt is disabled</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| bit 16     | CHERIE: Channel Address Error Interrupt Enable bit<br>1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| bit 15-8   | 0 = Interrupt is disabled<br>Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| bit 7      | CHSDIF: Channel Source Done Interrupt Flag bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|            | <ul> <li>1 = Channel Source Pointer has reached end of source (CHSPTR = CHSSIZ)</li> <li>0 = No interrupt is pending</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| bit 6      | <b>CHSHIF:</b> Channel Source Half Empty Interrupt Flag bit<br>1 = Channel Source Pointer has reached midpoint of source (CHSPTR = CHSSIZ/2)<br>0 = No interrupt is pending                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | )   |

| bit 5      | <b>CHDDIF:</b> Channel Destination Done Interrupt Flag bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|            | <ul> <li>1 = Channel Destination Pointer has reached end of destination (CHDPTR = CHDSI</li> <li>0 = No interrupt is pending</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IZ) |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| © 2011-201 | 16 Microchip Technology Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DS  |

| 2 2011 20  | is more any restricted from the second s | 20  |

DS60001168J-page 95

| REGISTE | R 9-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER (CONTINUED)                                                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | CHDHIF: Channel Destination Half Full Interrupt Flag bit                                                                                                                                   |

|         | <ul> <li>1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)</li> <li>0 = No interrupt is pending</li> </ul>                                           |

| bit 3   | CHBCIF: Channel Block Transfer Complete Interrupt Flag bit                                                                                                                                 |

|         | <ul> <li>1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs</li> <li>0 = No interrupt is pending</li> </ul> |

| bit 2   | CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit                                                                                                                                  |

|         | <ul><li>1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)</li><li>0 = No interrupt is pending</li></ul>                                                          |

| bit 1   | CHTAIF: Channel Transfer Abort Interrupt Flag bit                                                                                                                                          |

|         | <ul> <li>1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted</li> <li>0 = No interrupt is pending</li> </ul>                                          |

| bit 0   | CHERIF: Channel Address Error Interrupt Flag bit                                                                                                                                           |

|         | <ul> <li>1 = A channel address error has been detected (either the source or the destination address is invalid)</li> <li>0 = No interrupt is pending</li> </ul>                           |

DS60001168J-page 96

### PIC32MX1XX/2XX 28/36/44-PIN FAMILY

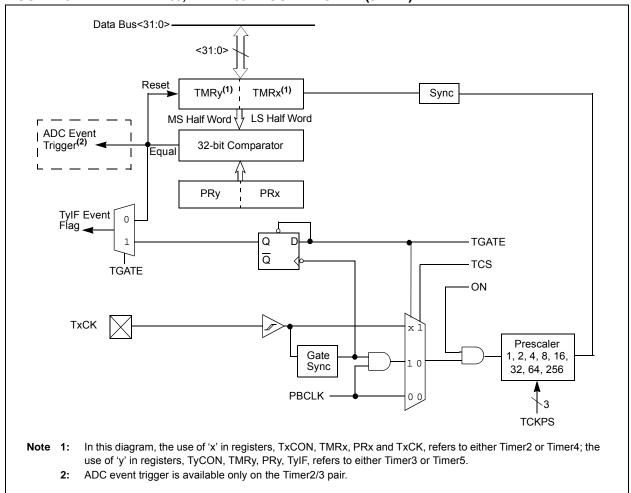

#### FIGURE 13-2: TIMER2/3, TIMER4/5 BLOCK DIAGRAM (32-BIT)

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| REGISTE      | N 15-1. IX           | CON. TIFL         |                     |                   | LOISTEN            |                   |                    |                  |

|--------------|----------------------|-------------------|---------------------|-------------------|--------------------|-------------------|--------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |

| 31:24        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |

| 31.24        | —                    |                   | —                   | -                 | —                  | -                 | —                  | —                |

| 00.40        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |

| 23:16        | —                    | -                 | —                   | _                 | _                  | _                 | —                  | —                |

| 45.0         | R/W-0                | U-0               | R/W-0               | U-0               | U-0                | U-0               | U-0                | U-0              |

| 15:8         | ON <sup>(1,3)</sup>  | _                 | SIDL <sup>(4)</sup> | _                 | —                  | —                 | —                  | —                |

| 7:0          | R/W-0                | R/W-0             | R/W-0               | R/W-0             | R/W-0              | U-0               | R/W-0              | U-0              |

| 7:0          | TGATE <sup>(3)</sup> | Т                 | CKPS<2:0>(          | 3)                | T32 <sup>(2)</sup> | —                 | TCS <sup>(3)</sup> | —                |

#### REGISTER 13-1: TXCON: TYPE B TIMER CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

#### bit 31-16 **Unimplemented:** Read as '0'

- bit 15 **ON:** Timer On bit<sup>(1,3)</sup>

- 1 = Module is enabled

- 0 = Module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit<sup>(4)</sup>

- 1 = Discontinue module operation when the device enters Idle mode0 = Continue module operation when the device enters Idle mode

#### bit 12-8 Unimplemented: Read as '0'

- bit 7 **TGATE:** Timer Gated Time Accumulation Enable bit<sup>(3)</sup>

- When TCS = 1:

This bit is ignored and is read as '0'.

When TCS = 0:

1 = Gated time accumulation is enabled

0 = Gated time accumulation is disabled

#### bit 6-4 **TCKPS<2:0>:** Timer Input Clock Prescale Select bits<sup>(3)</sup>

- 111 = 1:256 prescale value

- 110 = 1:64 prescale value

- 101 = 1:32 prescale value

- 100 = 1:16 prescale value

- 011 = 1:8 prescale value

- 010 = 1:4 prescale value

- 001 = 1:2 prescale value

#### 000 = 1:1 prescale value

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3, and Timer5). All timer functions are set through the even numbered timers.

- 4: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

#### 15.1 **Input Capture Control Registers**

|                             | ABLE 15-1: INPUT CAPTURE 1-INPUT CAPTURE 5 REGISTER MAP |               |       |              |       |              |       |       |       |        |        |      |      |      |       |      |          |

|-----------------------------|---------------------------------------------------------|---------------|-------|--------------|-------|--------------|-------|-------|-------|--------|--------|------|------|------|-------|------|----------|

| ess                         |                                                         |               |       |              |       |              |       |       |       | Bi     | ts     |      |      |      |       |      |          |

| Virtual Address<br>(BF80_#) | Register<br>Name                                        | Bit Range     | 31/15 | 30/14        | 29/13 | 28/12        | 27/11 | 26/10 | 25/9  | 24/8   | 23/7   | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1     |

|                             | IC1CON <sup>(1)</sup>                                   | 31:16         |       | _            | —     | —            | —     | —     | _     | —      | —      | —    |      | —    | —     | —    | —        |

| 2000                        | 101001                                                  | 15:0          | ON    | —            | SIDL  | —            | —     | —     | FEDGE | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |

| 2010                        | IC1BUF                                                  | 31:16<br>15:0 |       | IC1BUF<31:0> |       |              |       |       |       |        |        |      |      |      |       |      |          |

| 2200                        | IC2CON <sup>(1)</sup>                                   | 31:16         |       | —            | —     | —            | —     | —     | —     | —      | _      | —    | _    | —    | _     | —    | —        |

|                             | 1020011                                                 | 15:0          | ON    | —            | SIDL  | —            |       | —     | FEDGE | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |

| 2210                        | IC2BUF                                                  | 31:16<br>15:0 |       | IC2BUF<31:0> |       |              |       |       |       |        |        |      |      |      |       |      |          |

| 2400                        | IC3CON <sup>(1)</sup>                                   | 31:16         | -     | _            | —     | _            | -     | _     | —     | _      | —      | -    | _    | —    | _     | _    | —        |

| 2400                        | 1030011                                                 | 15:0          | ON    | —            | SIDL  | —            |       | —     | FEDGE | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |

| 2410                        | IC3BUF                                                  | 31:16<br>15:0 |       |              |       |              |       |       |       | IC3BUF | <31:0> |      |      |      |       |      |          |

| 2600                        | IC4CON <sup>(1)</sup>                                   | 31:16         | -     | _            | —     | _            | -     | _     | —     | —      | —      | _    | _    | —    | —     | _    | —        |

| 2000                        | 1040010                                                 | 15:0          | ON    | —            | SIDL  | —            |       | —     | FEDGE | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |

| 2610                        | IC4BUF                                                  | 31:16<br>15:0 |       |              |       | IC4BUF<31:0> |       |       |       |        |        |      |      |      |       |      |          |

| 2800                        | IC5CON <sup>(1)</sup>                                   | 31:16         | -     | _            | —     | _            | -     | _     | —     | —      | —      | _    | _    | —    | —     | _    | —        |

| 2000                        | 1030011                                                 | 15:0          | ON    | —            | SIDL  | —            | —     | —     | FEDGE | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |

| 2810                        | IC5BUF                                                  | 31:16<br>15:0 |       |              |       |              |       |       |       | IC5BUF | <31:0> |      |      |      |       |      |          |

#### Т

Legend:

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information. Note 1:

All Resets

0000

0000 xxxx xxxx 0000 0000 xxxx xxxx 0000 0000 xxxx xxxx 0000 0000 xxxx xxxx 0000 0000 xxxx xxxx

16/0

—

NOTES:

#### 19.1 UART Control Registers

#### TABLE 19-1: UART1 AND UART2 REGISTER MAP

| np for point | ess                         |                  | 6         |        |        |        |       |        |       |       | Bi          | ts               |         |       |             |        |       |        |       | 6          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------|-----------|--------|--------|--------|-------|--------|-------|-------|-------------|------------------|---------|-------|-------------|--------|-------|--------|-------|------------|

| 6000         01MODe <sup>1</sup> 15.0         ON         -         SIDL         IREN         RTSMD         -         UEN<1.0>         WAKE         LPBACK         ABAUD         RXINV         BRGH         PDEL<1.0>         STSL         0.00           610         U1STA(1)         31.16         -         -         -         -         ADM_EN         VERSE         ADM         ADM_EN         RIDE         PERR         PERR         OERR         VERSO         0000           0107         116         -         -         -         -         -         -         -         -         0000         0000           01080         116         -         -         -         -         -         -         -         -         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15  | 30/14  | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8        | 23/7             | 22/6    | 21/5  | 20/4        | 19/3   | 18/2  | 17/1   | 16/0  | All Resets |