Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

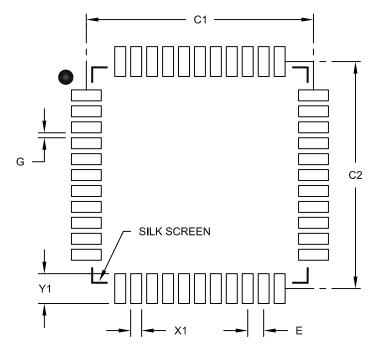

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx170f256d-50i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|              |                        | Pin Nu                                      | mber <sup>(1)</sup> |                                 |             | -                   |                                                            |

|--------------|------------------------|---------------------------------------------|---------------------|---------------------------------|-------------|---------------------|------------------------------------------------------------|

| Pin Name     | 28-pin<br>QFN          | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC           | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type      | Description                                                |

| RC0          | —                      | —                                           | 3                   | 25                              | I/O         | ST                  | PORTC is a bidirectional I/O port                          |

| RC1          | —                      | —                                           | 4                   | 26                              | I/O         | ST                  |                                                            |

| RC2          | —                      | —                                           | _                   | 27                              | I/O         | ST                  |                                                            |

| RC3          | —                      | —                                           | 11                  | 36                              | I/O         | ST                  | _                                                          |

| RC4          | —                      | —                                           | _                   | 37                              | I/O         | ST                  | _                                                          |

| RC5          | —                      |                                             |                     | 38                              | I/O         | ST                  | _                                                          |

| RC6          |                        | —                                           | _                   | 2                               | I/O         | ST                  | _                                                          |

| RC7          | —                      |                                             | —                   | 3                               | I/O         | ST                  | 4                                                          |

| RC8          | —                      | —                                           | —                   | 4                               | I/O         | ST                  | _                                                          |

| RC9          |                        | - 40                                        | 20                  | 5                               | I/O         | ST                  | Time and an element all all in must                        |

| T1CK<br>T2CK | 9<br>PPS               | 12                                          | 10                  | 34                              |             | ST                  | Timer1 external clock input                                |

| T3CK         | PPS<br>PPS             | PPS<br>PPS                                  | PPS<br>PPS          | PPS<br>PPS                      |             | ST<br>ST            | Timer2 external clock input<br>Timer3 external clock input |

| T4CK         | PPS                    | PPS                                         | PPS                 | PPS                             | 1           | ST                  | Timer4 external clock input                                |

| T5CK         | PPS                    | PPS                                         | PPS                 | PPS                             |             | ST                  | Timer5 external clock input                                |

|              | PPS                    | PPS                                         | PPS                 | PPS                             |             | ST                  | UART1 clear to send                                        |

| U1RTS        | PPS                    | PPS                                         | PPS                 | PPS                             |             | 51                  |                                                            |

| U1RX         | PPS<br>PPS             | PPS<br>PPS                                  | PPS<br>PPS          | PPS<br>PPS                      | 0           | ST                  | UART1 ready to send<br>UART1 receive                       |

| U1TX         | PPS                    | PPS                                         | PPS                 | PPS                             | -           |                     |                                                            |

|              |                        |                                             |                     |                                 | 0           |                     | UART1 transmit                                             |

| U2CTS        | PPS                    | PPS                                         | PPS                 | PPS                             | I           | ST                  | UART2 clear to send                                        |

| U2RTS        | PPS                    | PPS                                         | PPS                 | PPS                             | 0           |                     | UART2 ready to send                                        |

| U2RX         | PPS                    | PPS                                         | PPS                 | PPS                             | I           | ST                  | UART2 receive                                              |

| U2TX         | PPS                    | PPS                                         | PPS                 | PPS                             | 0           |                     | UART2 transmit                                             |

| SCK1         | 22                     | 25                                          | 28                  | 14                              | I/O         | ST                  | Synchronous serial clock input/output for SPI1             |

| SDI1         | PPS                    | PPS                                         | PPS                 | PPS                             | I           | ST                  | SPI1 data in                                               |

| SDO1         | PPS                    | PPS                                         | PPS                 | PPS                             | 0           | _                   | SPI1 data out                                              |

| SS1          | PPS                    | PPS                                         | PPS                 | PPS                             | I/O         | ST                  | SPI1 slave synchronization or frame pulse I/O              |

| SCK2         | 23                     | 26                                          | 29                  | 15                              | I/O         | ST                  | Synchronous serial clock input/output for SPI2             |

| SDI2         | PPS                    | PPS                                         | PPS                 | PPS                             |             | ST                  | SPI2 data in                                               |

| SDO2         | PPS                    | PPS                                         | PPS                 | PPS                             | 0           | _                   | SPI2 data out                                              |

| SS2          | PPS                    | PPS                                         | PPS                 | PPS                             | I/O         | ST                  | SPI2 slave synchronization or frame pulse I/O              |

| SCL1         | 14                     | 17                                          | 18                  | 44                              | I/O         | ST                  | Synchronous serial clock input/output for<br>I2C1          |

|              | ST = Schm<br>TTL = TTL | MOS compa<br>itt Trigger in<br>input buffer | put with CN         | MOS levels                      |             | O = Outp<br>PPS = P | Analog input P = Power                                     |

####

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

NOTES:

# 8.0 OSCILLATOR CONFIGURATION

| Note: | This data sheet summarizes the features<br>of the PIC32MX1XX/2XX 28/36/44-pin<br>Family of devices. It is not intended to be<br>a comprehensive reference source. To<br>complement the information in this data |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|       | sheet, refer to Section 6. "Oscillator                                                                                                                                                                          |  |  |  |  |  |  |  |  |

|       | Configuration" (DS60001112), which is                                                                                                                                                                           |  |  |  |  |  |  |  |  |

|       | available from the Documentation >                                                                                                                                                                              |  |  |  |  |  |  |  |  |

|       | Reference Manual section of the                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|       | Microchip PIC32 web site                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|       | (www.microchip.com/pic32).                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

The PIC32MX1XX/2XX 28/36/44-pin Family oscillator system has the following modules and features:

- Four external and internal oscillator options as clock sources

- On-Chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-Chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Dedicated On-Chip PLL for USB peripheral

A block diagram of the oscillator system is provided in Figure 8-1.

#### REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit Bit<br>29/21/13/5 28/20/12/4 |           | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-----------------------|----------------------------------|-----------|--------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | U-0               | U-0                   | R/W-0                            | R/W-0     | R/W-0              | U-0               | U-0              | R/W-0            |  |  |  |  |

| 31:24        | —                 | _                     | BYTC                             | <1:0>     | WBO <sup>(1)</sup> | —                 | _                | BITO             |  |  |  |  |

| 22:16        | U-0               | U-0                   | U-0                              | U-0       | U-0                | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | —                 | _                     | —                                | _         | —                  | —                 | _                | _                |  |  |  |  |

| 45.0         | U-0               | U-0                   | U-0                              | R/W-0     | R/W-0              | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         |                   | _                     | _                                | PLEN<4:0> |                    |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0                 | R/W-0                            | U-0       | U-0                | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> | CRCTYP                           | _         | _                  | (                 | CRCCH<2:0>       |                  |  |  |  |  |

## Legend:

| Logona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-30 Unimplemented: Read as '0'

- bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (i.e., source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (i.e., reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (i.e., reverse source byte order)

- 00 = No swapping (i.e., source byte order)

- bit 27 **WBO:** CRC Write Byte Order Selection bit<sup>(1)</sup>

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (i.e., reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (i.e., not reflected)

#### <u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (i.e., reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (i.e., not reflected)

#### bit 23-13 Unimplemented: Read as '0'

bit 12-8 **PLEN<4:0>:** Polynomial Length bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): These bits are unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Denotes the length of the polynomial -1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- Note 1: When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

| REGISTE      | REGISTER 9-8: DCHXECON: DMA CHANNEL X EVENT CONTROL REGISTER |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|--------------|--------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                                            | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 24.24        | U-0                                                          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                                                            | —                 | —                 | _                 | —                 | _                 | —                | —                |  |  |  |

| 22:40        | R/W-1                                                        | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |

| 23:16        | CHAIRQ<7:0> <sup>(1)</sup>                                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15:0         | R/W-1                                                        | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |

| 15:8         | CHSIRQ<7:0> <sup>(1)</sup>                                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | S-0                                                          | S-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |  |  |

| 7.0          | CFORCE                                                       | CABORT            | PATEN             | SIRQEN            | AIRQEN            |                   |                  |                  |  |  |  |

#### CISTER 0-8. CIETED

| Legend:           | S = Settable bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# bit 31-24 Unimplemented: Read as '0'

bit

bit

bit

bit

bit

bit

| : 31-24 | Unimplemented: Read as '0'                                                                                                                                       |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23-16   | CHAIRQ<7:0>: Channel Transfer Abort IRQ bits <sup>(1)</sup>                                                                                                      |

|         | 11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag                                                                                 |

|         | •                                                                                                                                                                |

|         | •                                                                                                                                                                |

|         | •                                                                                                                                                                |

|         | 00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag<br>00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag |

| 15-8    | CHSIRQ<7:0>: Channel Transfer Start IRQ bits <sup>(1)</sup>                                                                                                      |

|         | 11111111 = Interrupt 255 will initiate a DMA transfer                                                                                                            |

|         | •                                                                                                                                                                |

|         | •                                                                                                                                                                |

|         | •                                                                                                                                                                |

|         | 00000001 = Interrupt 1 will initiate a DMA transfer                                                                                                              |

| _       | 0000000 = Interrupt 0 will initiate a DMA transfer                                                                                                               |

| :7      | CFORCE: DMA Forced Transfer bit                                                                                                                                  |

|         | <ul> <li>1 = A DMA transfer is forced to begin when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                               |

| 6       | CABORT: DMA Abort Transfer bit                                                                                                                                   |

|         | 1 = A DMA transfer is aborted when this bit is written to a '1'                                                                                                  |

|         | 0 = This bit always reads '0'                                                                                                                                    |

| 5       | PATEN: Channel Pattern Match Abort Enable bit                                                                                                                    |

|         | 1 = Abort transfer and clear CHEN on pattern match                                                                                                               |

|         | 0 = Pattern match is disabled                                                                                                                                    |

| : 4     | SIRQEN: Channel Start IRQ Enable bit                                                                                                                             |

|         | 1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs                                                                                           |

|         |                                                                                                                                                                  |

- - 0 = Interrupt number CHSIRQ is ignored and does not start a transfer

- bit 3 AIRQEN: Channel Abort IRQ Enable bit

- 1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs

- 0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer

- bit 2-0 Unimplemented: Read as '0'

- Note 1: See Table 7-1: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

| REGIST       |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | -                 | —                 | —                 | -                 | -                 | —                 | -                | —                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        | -                 | —                 | —                 | -                 | -                 | —                 | -                | —                |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15.6         |                   | _                 | -                 |                   |                   | —                 |                  | —                |  |  |  |  |

| 7.0          | R/WC-0, HS        | U-0              | R/WC-0, HS       |  |  |  |  |

| 7:0          | IDIF              | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF           | SESENDIF          |                  | VBUSVDIF         |  |  |  |  |

# REGISTER 10-1: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable bit |                    |  |  |  |

|-------------------|-------------------------|----------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, re  | ead as '0'         |  |  |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared       | x = Bit is unknown |  |  |  |

bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIF:** ID State Change Indicator bit

- 1 = A change in the ID state was detected

- 0 = No change in the ID state was detected

- bit 6 T1MSECIF: 1 Millisecond Timer bit

- 1 = 1 millisecond timer has expired

- 0 = 1 millisecond timer has not expired

#### bit 5 LSTATEIF: Line State Stable Indicator bit

- 1 = USB line state has been stable for 1 ms, but different from last time

- 0 = USB line state has not been stable for 1 ms

- bit 4 ACTVIF: Bus Activity Indicator bit

- 1 = Activity on the D+, D-, ID or VBUS pins has caused the device to wake-up

- 0 = Activity has not been detected

- bit 3 SESVDIF: Session Valid Change Indicator bit

- 1 = VBUS voltage has dropped below the session end level

- 0 = VBUS voltage has not dropped below the session end level

- bit 2 SESENDIF: B-Device VBUS Change Indicator bit

- 1 = A change on the session end input was detected

- 0 = No change on the session end input was detected

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIF: A-Device VBUS Change Indicator bit

- 1 = A change on the session valid input was detected

- 0 = No change on the session valid input was detected

#### TABLE 11-5: PORTC REGISTER MAP

| ess                         | -                                 |           |       |       |       |       |       |       |          |                       |                         | Bits                  |                       |                         |          |                       |          |          |            |

|-----------------------------|-----------------------------------|-----------|-------|-------|-------|-------|-------|-------|----------|-----------------------|-------------------------|-----------------------|-----------------------|-------------------------|----------|-----------------------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1,2)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9     | 24/8                  | 23/7                    | 22/6                  | 21/5                  | 20/4                    | 19/3     | 18/2                  | 17/1     | 16/0     | All Resets |

| 6200                        | ANSELC                            | 31:16     |       | _     |       |       | —     | —     | _        | -                     | _                       | -                     | _                     | _                       | —        | _                     | —        |          | 0000       |

| 0200                        | ,                                 | 15:0      | —     | —     | —     | —     | —     | —     |          |                       | —                       |                       |                       | _                       | ANSC3(4) | ANSC2 <sup>(3)</sup>  | ANSC1    | ANSC0    | 000F       |

| 6210                        | TRISC                             | 31:16     | _     | _     | —     | —     | —     | —     | —        | —                     | —                       | —                     | —                     | —                       | —        | —                     | —        |          | 0000       |

| 0210                        | 11100                             | 15:0      | _     | _     | —     | —     | —     | —     | TRISC9   | TRISC8 <sup>(3)</sup> | TRISC7 <sup>(3)</sup>   | TRISC6 <sup>(3)</sup> | TRISC5 <sup>(3)</sup> | TRISC4 <sup>(3)</sup>   | TRISC3   | TRISC2 <sup>(3)</sup> | TRISC1   | TRISC0   | 03FF       |

| 6220                        | PORTC                             | 31:16     | —     | —     | —     | —     | —     | —     | _        |                       | _                       |                       | _                     |                         |          |                       |          |          | 0000       |

| 0220                        |                                   | 15:0      | _     | _     | —     | —     | —     | —     | RC9      | RC8 <sup>(3)</sup>    | RC7 <sup>(3)</sup>      | RC6 <sup>(3)</sup>    | RC5 <sup>(3)</sup>    | RC4 <sup>(3)</sup>      | RC3      | RC2 <sup>(3)</sup>    | RC1      | RC0      | xxxx       |

| 6230                        | LATC                              | 31:16     | _     | _     | —     | —     | —     | —     | _        |                       | _                       |                       |                       | _                       | —        |                       | —        | —        | 0000       |

| 0230                        | LAIC                              | 15:0      |       |       | _     | _     | _     | _     | LATC9    | LATC8 <sup>(3)</sup>  | LATC7 <sup>(3)</sup>    | LATC6 <sup>(3)</sup>  | LATC5 <sup>(3)</sup>  | LATC4 <sup>(3)</sup>    | LATC3    | LATC2 <sup>(3)</sup>  | LATC1    | LATC0    | xxxx       |

| 6240                        | ODCC                              | 31:16     |       |       | _     | _     | _     | _     | _        |                       |                         |                       |                       |                         | _        |                       | _        | _        | 0000       |

| 6240                        | ODCC                              | 15:0      |       |       | _     | _     | _     | _     | ODCC9    | ODCC8 <sup>(3)</sup>  | ODCC7 <sup>(3)</sup>    | ODCC6 <sup>(3)</sup>  | ODCC5 <sup>(3)</sup>  | ODCC4 <sup>(3)</sup>    | ODCC3    | ODCC2 <sup>(3)</sup>  | ODCC1    | ODCC0    | 0000       |

| 0050                        |                                   | 31:16     |       |       | —     | —     | —     | -     | —        | -                     | _                       | -                     | —                     | —                       | —        | —                     | —        | —        | 0000       |

| 6250                        | CNPUC                             | 15:0      | _     | _     | _     | _     | —     | —     | CNPUC9   | CNPUC8 <sup>(3)</sup> | CNPUC7 <sup>(3)</sup>   | CNPUC6 <sup>(3)</sup> | CNPUC5 <sup>(3)</sup> | CNPUC4 <sup>(3)</sup>   | CNPUC3   | CNPUC2 <sup>(3)</sup> | CNPUC1   | CNPUC0   | 0000       |

| 0000                        |                                   | 31:16     | _     | _     | _     | _     | _     | _     | —        | _                     | _                       | _                     | _                     | —                       | _        | —                     | _        | _        | 0000       |

| 6260                        | CNPDC                             | 15:0      | _     | _     | —     | —     | —     | —     | CNPDC9   | CNPDC8 <sup>(3)</sup> | CNPDC7 <sup>(3)</sup>   | CNPDC6 <sup>(3)</sup> | CNPDC5 <sup>(3)</sup> | CNPDC4 <sup>(3)</sup>   | CNPDC3   | CNPDC2 <sup>(3)</sup> | CNPDC1   | CNPDC0   | 0000       |

| 0070                        | anaana                            | 31:16     | _     | _     | —     | —     | —     | —     | _        | _                     | _                       | _                     | —                     | —                       | —        | _                     | —        | —        | 0000       |

| 6270                        | CNCONC                            | 15:0      | ON    | _     | SIDL  | _     | —     | —     | _        | _                     | _                       | _                     | _                     | —                       | —        | _                     | —        | _        | 0000       |

|                             |                                   | 31:16     | _     | _     | _     |       | —     | _     |          |                       | _                       |                       | _                     | _                       | _        | _                     | —        | —        | 0000       |

| 6280                        | CNENC                             | 15:0      | _     | _     | _     |       | —     | _     | CNIEC9   | CNIEC8(3)             | CNIEC7 <sup>(3)</sup>   | CNIEC6(3)             | CNIEC5 <sup>(3)</sup> | CNIEC4 <sup>(3)</sup>   | CNIEC3   | CNIEC2 <sup>(3)</sup> | CNIEC1   | CNIEC0   | 0000       |

|                             |                                   | 31:16     | _     | _     | _     | _     | _     | _     | _        |                       | _                       |                       | _                     | _                       | —        |                       | —        | —        | 0000       |

| 6290                        | CNSTATC                           | 15:0      | _     | _     | _     | _     | _     | _     | CNSTATC9 | CNSTATC8(3)           | CNSTATC7 <sup>(3)</sup> | CNSTATC6(3)           | CNSTATC5(3)           | CNSTATC4 <sup>(3)</sup> | CNSTATC3 | CNSTATC2(3)           | CNSTATC1 | CNSTATC0 | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: PORTC is not available on 28-pin devices.

3: This bit is only available on 44-pin devices.

4: This bit is only available on USB-enabled devices with 36 or 44 pins.

#### REGISTER 17-2: SPIxCON2: SPI CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0        |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|-------------------------|

| 21.24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 31:24        | —                    | —                 | —                 | —                 | —                        | —                 | _                | —                       |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 23.10        | —                    | —                 | —                 | —                 | —                        | —                 | _                | —                       |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                   |

| 10.0         | SPISGNEXT            | —                 | —                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                  |

| 7:0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                   |

| 7:0          | AUDEN <sup>(1)</sup> | _                 | _                 | —                 | AUDMONO <sup>(1,2)</sup> | —                 | AUDMOD           | )<1:0> <sup>(1,2)</sup> |

#### Legend:

| R = Readable bit  | Readable bit W = Writable bit |                      | as '0'             |

|-------------------|-------------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

- 1 = Data from RX FIFO is sign extended

- 0 = Data from RX FIFO is not sign extended

- bit 14-13 Unimplemented: Read as '0'

- bit 12 **FRMERREN:** Enable Interrupt Events via FRMERR bit

- 1 = Frame Error overflow generates error events

- 0 = Frame Error does not generate error events

- bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit

- 1 = Receive overflow generates error events

- 0 = Receive overflow does not generate error events

- bit 10 SPITUREN: Enable Interrupt Events via SPITUR bit

- 1 = Transmit underrun generates error events

- 0 = Transmit underrun does not generate error events

- bit 9 IGNROV: Ignore Receive Overflow bit (for Audio Data Transmissions)

- 1 = A ROV is not a critical error; during ROV data in the FIFO is not overwritten by receive data

0 = A ROV is a critical error that stops SPI operation

- bit 8 **IGNTUR:** Ignore Transmit Underrun bit (for Audio Data Transmissions)

- 1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty

- 0 = A TUR is a critical error that stops SPI operation

- bit 7 AUDEN: Enable Audio CODEC Support bit<sup>(1)</sup>

- 1 = Audio protocol enabled

- 0 = Audio protocol disabled

- bit 6-5 Unimplemented: Read as '0'

- bit 3 AUDMONO: Transmit Audio Data Format bit<sup>(1,2)</sup>

- 1 = Audio data is mono (Each data word is transmitted on both left and right channels)

- 0 = Audio data is stereo

- bit 2 Unimplemented: Read as '0'

- bit 1-0 AUDMOD<1:0>: Audio Protocol Mode bit<sup>(1,2)</sup>

- 11 = PCM/DSP mode

- 10 = Right-Justified mode

- 01 = Left-Justified mode

- $00 = I^2S \mod$

- **Note 1:** This bit can only be written when the ON bit = 0.

- **2:** This bit is only valid for AUDEN = 1.

# REGISTER 19-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | <ul> <li>ABAUD: Auto-Baud Enable bit</li> <li>1 = Enable baud rate measurement on the next character – requires reception of Sync character (0x55); cleared by hardware upon completion</li> <li>0 = Baud rate measurement disabled or completed</li> </ul> |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | RXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                           |

| bit 3   | BRGH: High Baud Rate Enable bit<br>1 = High-Speed mode – 4x baud clock enabled<br>0 = Standard Speed mode – 16x baud clock enabled                                                                                                                          |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits<br>11 = 9-bit data, no parity<br>10 = 8-bit data, odd parity<br>01 = 8-bit data, even parity<br>00 = 8-bit data, no parity                                                                                       |

| bit 0   | <b>STSEL:</b> Stop Selection bit<br>1 = 2 Stop bits<br>0 = 1 Stop bit                                                                                                                                                                                       |

**Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

### REGISTER 22-3: AD1CON3: ADC CONTROL REGISTER 3

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

|              | —                 | —                 | —                 | _                 | —                 | —                 | —                | -                |  |  |

| 00.10        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | _                 | —                 | —                 | _                | -                |  |  |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | ADRC              | _                 | —                 |                   |                   | SAMC<4:0>(1)      |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W              | R/W-0            |  |  |

| 7:0          |                   |                   |                   | ADCS<             | 7:0> <b>(2)</b>   |                   | I                |                  |  |  |

# Legend:

| =ogona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ADRC: ADC Conversion Clock Source bit

- 1 = Clock derived from FRC

- 0 = Clock derived from Peripheral Bus Clock (PBCLK)

- bit 14-13 Unimplemented: Read as '0'

- - 00000001 =TPB • 2 • (ADCS<7:0> + 1) = 4 • TPB = TAD 00000000 =TPB • 2 • (ADCS<7:0> + 1) = 2 • TPB = TAD

- **Note 1:** This bit is only used if the SSRC<2:0> bits (AD1CON1<7:5>) = 111.

- 2: This bit is not used if the ADRC (AD1CON3<15>) bit = 1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4   | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|------------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 51.24        | EDG1MOD           | EDG1POL           |                   | EDG1S               | EDG2STAT          | EDG1STAT          |                        |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | U-0                    | U-0              |

| 23.10        | EDG2MOD           | EDG2POL           |                   | EDG2S               | —                 | —                 |                        |                  |

| 15:8         | R/W-0             | U-0               | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 15.0         | ON                | —                 | CTMUSIDL          | TGEN <sup>(1)</sup> | EDGEN             | EDGSEQEN          | IDISSEN <sup>(2)</sup> | CTTRIG           |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 7.0          |                   |                   | ITRIM             | 1<5:0>              |                   |                   | IRNG<1:0               | <1:0>            |

### REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER

## Legend:

| Logona.           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

- bit 31 EDG1MOD: Edge1 Edge Sampling Select bit

- 1 = Input is edge-sensitive

- 0 = Input is level-sensitive

- bit 30 EDG1POL: Edge 1 Polarity Select bit

- 1 = Edge1 programmed for a positive edge response

- 0 = Edge1 programmed for a negative edge response

- bit 29-26 EDG1SEL<3:0>: Edge 1 Source Select bits

- 1111 = C3OUT pin is selected

- 1110 = C2OUT pin is selected

- 1101 = C1OUT pin is selected

- 1100 = IC3 Capture Event is selected

- 1011 = IC2 Capture Event is selected

- 1010 = IC1 Capture Event is selected

- 1001 = CTED8 pin is selected

- 1000 = CTED7 pin is selected

- 0111 = CTED6 pin is selected

- 0110 = CTED5 pin is selected

- 0101 = CTED4 pin is selected

- 0100 = CTED3 pin is selected

- 0011 = CTED1 pin is selected

- 0010 = CTED2 pin is selected

- 0001 = OC1 Compare Event is selected 0000 = Timer1 Event is selected

#### bit 25 EDG2STAT: Edge2 Status bit

Indicates the status of Edge2 and can be written to control edge source

- 1 = Edge2 has occurred

- 0 = Edge2 has not occurred

- Note 1: When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 30-41) in Section 30.0 "Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | R/P              | R/P              |  |

|              | —                 | _                 | _                 | _                 | —                 | —                 | FWDTWINSZ<1:0>   |                  |  |

| 00.40        | R/P               | R/P               | r-1               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 23:16        | FWDTEN            | WINDIS            | _                 |                   | WDTPS<4:0>        |                   |                  |                  |  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | r-1               | R/P               | R/P              | R/P              |  |

| 15:8         | FCKSM             | 1<1:0>            | FPBDI             | /<1:0> —          |                   | OSCIOFNC          | POSCM            | OD<1:0>          |  |

| 7.0          | R/P               | r-1               | R/P               | r-1               | r-1               | R/P               | R/P              | R/P              |  |

| 7:0          | IESO              | _                 | FSOSCEN           | _                 | —                 | F                 | NOSC<2:0>        |                  |  |

#### REGISTER 27-2: DEVCFG1: DEVICE CONFIGURATION WORD 1

| Legend:           | r = Reserved bit | P = Programmable bit               |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-26 Reserved: Write '1'

bit 25-24 FWDTWINSZ<1:0>: Watchdog Timer Window Size bits

- 11 = Window size is 25%

- 10 = Window size is 37.5%

- 01 = Window size is 50%

- 00 = Window size is 75%

#### bit 23 FWDTEN: Watchdog Timer Enable bit

- 1 = Watchdog Timer is enabled and cannot be disabled by software

- 0 = Watchdog Timer is not enabled; it can be enabled in software

#### bit 22 WINDIS: Watchdog Timer Window Enable bit

- 1 = Watchdog Timer is in non-Window mode

- 0 = Watchdog Timer is in Window mode

#### bit 21 Reserved: Write '1'

#### bit 20-16 WDTPS<4:0>: Watchdog Timer Postscale Select bits

| 10100 <b>= 1:1048576</b>                                     |

|--------------------------------------------------------------|

| 10011 <b>= 1:524288</b>                                      |

| 10010 <b>= 1:262144</b>                                      |

| 10001 <b>= 1:131072</b>                                      |

| 10000 <b>= 1:65536</b>                                       |

| 01111 <b>= 1:32768</b>                                       |

| 01110 <b>= 1:16384</b>                                       |

| 01101 = 1:8192                                               |

| 01100 = 1:4096                                               |

| 01011 = <b>1:2048</b>                                        |

| 01010 = 1:1024                                               |

| 01001 = 1:512                                                |

| 01000 <b>= 1:256</b>                                         |

| 00111 <b>= 1:128</b>                                         |

| 00110 <b>= 1:64</b>                                          |

| 00101 <b>= 1:32</b>                                          |

| 00100 <b>= 1:16</b>                                          |

| 00011 <b>= 1:8</b>                                           |

| 00010 <b>= 1</b> :4                                          |

| 00001 = 1:2                                                  |

| 00000 = 1:1                                                  |

| All other combinations not shown result in operation = 10100 |

| ······································                       |

**Note 1:** Do not disable the Posc (POSCMOD = 11) when using this oscillator source.

### REGISTER 27-2: DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

#### bit 15-14 FCKSM<1:0>: Clock Switching and Monitor Selection Configuration bits

- 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled

- 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled

- 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled

- bit 13-12 FPBDIV<1:0>: Peripheral Bus Clock Divisor Default Value bits

- 11 = PBCLK is SYSCLK divided by 8

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- bit 11 Reserved: Write '1'

- bit 10 OSCIOFNC: CLKO Enable Configuration bit

- 1 = CLKO output disabled

- 0 = CLKO output signal active on the OSCO pin; Primary Oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 or 00)

#### bit 9-8 **POSCMOD<1:0>:** Primary Oscillator Configuration bits

- 11 = Primary Oscillator is disabled

- 10 = HS Oscillator mode is selected

- 01 = XT Oscillator mode is selected

- 00 = External Clock mode is selected

- bit 7 IESO: Internal External Switchover bit

- 1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled)

- 0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled)

- bit 6 **Reserved:** Write '1'

- bit 5 **FSOSCEN:** Secondary Oscillator Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

- bit 4-3 Reserved: Write '1'

- bit 2-0 **FNOSC<2:0>:** Oscillator Selection bits

- 111 = Fast RC Oscillator with divide-by-N (FRCDIV)

- 110 = FRCDIV16 Fast RC Oscillator with fixed divide-by-16 postscaler

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XT+PLL, HS+PLL, EC+PLL)

- 010 = Primary Oscillator (XT, HS, EC)<sup>(1)</sup>

- 001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)

- 000 = Fast RC Oscillator (FRC)

- **Note 1:** Do not disable the Posc (POSCMOD = 11) when using this oscillator source.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.04        | R/P               | R/P               | R/P               | R/P               | r-1               | r-1               | r-1              | r-1              |  |

| 31:24        | FVBUSONIO         | FUSBIDIO          | IOL1WAY           | PMDL1WAY          | _                 |                   | _                | _                |  |

| 23:16        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |  |

| 23.10        | —                 | —                 | _                 | —                 | _                 | _                 | -                | _                |  |

| 15.0         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 15:8         | USERID<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 7:0          |                   |                   |                   | USERID<           | 7:0>              |                   |                  |                  |  |

#### REGISTER 27-4: DEVCFG3: DEVICE CONFIGURATION WORD 3

| Legend:           | r = Reserved bit | P = Programmable bit   |                    |  |

|-------------------|------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

bit 31 FVBUSONIO: USB VBUSON Selection bit

- 1 = VBUSON pin is controlled by the USB module 0 = VBUSON pin is controlled by the port function

- bit 30 **FUSBIDIO:** USB USBID Selection bit 1 = USBID pin is controlled by the USB module 0 = USBID pin is controlled by the port function

- bit 29 IOL1WAY: Peripheral Pin Select Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 28 PMDI1WAY: Peripheral Module Disable Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 27-16 Reserved: Write '1'

- bit 15-0 USERID<15:0>: User ID bits

This is a 16-bit value that is user-defined and is readable via ICSP™ and JTAG.

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |  |

|--------------|-----------------------------|-------------------|---------------------|-------------------|-------------------|-------------------|-----------------------|------------------|--|

|              | R                           | R                 | R                   | R                 | R                 | R                 | R                     | R                |  |

| 31:24        |                             | VER<              | 3:0> <sup>(1)</sup> |                   |                   | DEVID<            | 27:24> <sup>(1)</sup> |                  |  |

| 00.40        | R                           | R                 | R                   | R                 | R                 | R                 | R                     | R                |  |

| 23:16        | DEVID<23:16> <sup>(1)</sup> |                   |                     |                   |                   |                   |                       |                  |  |

| 45.0         | R                           | R                 | R                   | R                 | R                 | R                 | R                     | R                |  |

| 15:8         | DEVID<15:8> <sup>(1)</sup>  |                   |                     |                   |                   |                   |                       |                  |  |

| 7.0          | R                           | R                 | R                   | R                 | R                 | R                 | R                     | R                |  |

| 7:0          |                             |                   |                     | DEVID             | <7:0>(1)          |                   |                       |                  |  |

### REGISTER 27-6: DEVID: DEVICE AND REVISION ID REGISTER

### Legend:

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 DEVID<27:0>: Device ID bits<sup>(1)</sup>

**Note 1:** See the "*PIC32 Flash Programming Specification*" (DS60001145) for a list of Revision and Device ID values.

# 28.0 INSTRUCTION SET

The PIC32MX1XX/2XX family instruction set complies with the MIPS32<sup>®</sup> Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- · Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

**Note:** Refer to *"MIPS32<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set"* at www.imgtec.com for more information.

### TABLE 30-32: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHA        |         | ISTICS                              |                               | $\label{eq:standard} \begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |      |       |                                |  |  |

|---------------|---------|-------------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------|--|--|

| Param.<br>No. | Symbol  | Charact                             | eristics                      | Min. <sup>(1)</sup>                                                                                                                                                                                                                                                                                 | Max. | Units | Conditions                     |  |  |

| IM10 TLO:SCL  |         | Clock Low Time                      | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                                     | —    | μS    | —                              |  |  |

|               |         |                                     | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                                     | _    | μS    | —                              |  |  |

|               |         |                                     | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                                     | _    | μs    | _                              |  |  |

| IM11          | THI:SCL | Clock High Time                     | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                                     | _    | μS    | —                              |  |  |

|               |         |                                     | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                                     | —    | μS    | —                              |  |  |

|               |         |                                     | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                                     | —    | μs    | —                              |  |  |

| IM20          | TF:SCL  | SDAx and SCLx                       | 100 kHz mode                  | —                                                                                                                                                                                                                                                                                                   | 300  | ns    | CB is specified to be          |  |  |

|               |         | Fall Time                           | 400 kHz mode                  | 20 + 0.1 Св                                                                                                                                                                                                                                                                                         | 300  | ns    | from 10 to 400 pF              |  |  |

|               |         |                                     | 1 MHz mode<br><b>(Note 2)</b> | _                                                                                                                                                                                                                                                                                                   | 100  | ns    |                                |  |  |

| IM21 TR:SCL   | TR:SCL  | SDAx and SCLx<br>Rise Time          | 100 kHz mode                  | —                                                                                                                                                                                                                                                                                                   | 1000 | ns    | CB is specified to be          |  |  |

|               |         |                                     | 400 kHz mode                  | 20 + 0.1 Св                                                                                                                                                                                                                                                                                         | 300  | ns    | from 10 to 400 pF              |  |  |

|               |         |                                     | 1 MHz mode<br><b>(Note 2)</b> | _                                                                                                                                                                                                                                                                                                   | 300  | ns    |                                |  |  |

| IM25 TSU:DAT  | TSU:DAT | Data Input<br>Setup Time            | 100 kHz mode                  | 250                                                                                                                                                                                                                                                                                                 | _    | ns    | —                              |  |  |

|               |         |                                     | 400 kHz mode                  | 100                                                                                                                                                                                                                                                                                                 | —    | ns    |                                |  |  |

|               |         |                                     | 1 MHz mode<br><b>(Note 2)</b> | 100                                                                                                                                                                                                                                                                                                 | _    | ns    |                                |  |  |

| IM26          | THD:DAT | Data Input<br>Hold Time             | 100 kHz mode                  | 0                                                                                                                                                                                                                                                                                                   | _    | μS    | —                              |  |  |

|               |         |                                     | 400 kHz mode                  | 0                                                                                                                                                                                                                                                                                                   | 0.9  | μs    |                                |  |  |

|               |         |                                     | 1 MHz mode<br>(Note 2)        | 0                                                                                                                                                                                                                                                                                                   | 0.3  | μs    |                                |  |  |

| IM30          | TSU:STA | STA Start Condition<br>Setup Time   | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                                     | _    | μS    | Only relevant for              |  |  |

|               |         |                                     | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                                     | —    | μS    | Repeated Start condition       |  |  |

|               |         |                                     | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                                     | —    | μs    | condition                      |  |  |

| IM31          | THD:STA | ID:STA Start Condition<br>Hold Time | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                                     |      | μS    | After this period, the         |  |  |

|               |         |                                     | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                                     | —    | μS    | first clock pulse is generated |  |  |

|               |         |                                     | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                                     | —    | μS    | generaleu                      |  |  |

| IM33 Tsu:st   | Tsu:sto | Stop Condition<br>Setup Time        | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                                     |      | μS    |                                |  |  |