Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 44-VTLA (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx170f256d-50i-tl |

TABLE 1: PIC32MX1XX 28/36/44-PIN GENERAL PURPOSE FAMILY FEATURES

|                 |      |                                    |                  | Rem             | appab                                  | le Pe | riphe                | rals                               |                    |                     |                  |     | _                                     |      | ls)                          |      |          |      |                                 |

|-----------------|------|------------------------------------|------------------|-----------------|----------------------------------------|-------|----------------------|------------------------------------|--------------------|---------------------|------------------|-----|---------------------------------------|------|------------------------------|------|----------|------|---------------------------------|

| Device          | Pins | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins | Timers <sup>(2)</sup> /Capture/Compare | UART  | SPI/I <sup>2</sup> S | External Interrupts <sup>(3)</sup> | Analog Comparators | USB On-The-Go (OTG) | l <sup>2</sup> C | PMP | DMA Channels (Programmable/Dedicated) | СТМО | 10-bit 1 Msps ADC (Channels) | RTCC | I/O Pins | JTAG | Packages                        |

| PIC32MX110F016B | 28   | 16+3                               | 4                | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2                | Υ   | 4/0                                   | Υ    | 10                           | Υ    | 21       | Υ    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX110F016C | 36   | 16+3                               | 4                | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 12                           | Υ    | 25       | Υ    | VTLA                            |

| PIC32MX110F016D | 44   | 16+3                               | 4                | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 13                           | Y    | 35       | Υ    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX120F032B | 28   | 32+3                               | 8                | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX120F032C | 36   | 32+3                               | 8                | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 12                           | Υ    | 25       | Υ    | VTLA                            |

| PIC32MX120F032D | 44   | 32+3                               | 8                | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2                | Υ   | 4/0                                   | Υ    | 13                           | Υ    | 35       | Υ    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX130F064B | 28   | 64+3                               | 16               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 10                           | Υ    | 21       | Υ    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX130F064C | 36   | 64+3                               | 16               | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 12                           | Υ    | 25       | Υ    | VTLA                            |

| PIC32MX130F064D | 44   | 64+3                               | 16               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Y    | 13                           | Υ    | 35       | Υ    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX150F128B | 28   | 128+3                              | 32               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 10                           | Υ    | 21       | Υ    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX150F128C | 36   | 128+3                              | 32               | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 12                           | Υ    | 25       | Υ    | VTLA                            |

| PIC32MX150F128D | 44   | 128+3                              | 32               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 13                           | Υ    | 35       | Υ    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX130F256B | 28   | 256+3                              | 16               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX130F256D | 44   | 256+3                              | 16               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 13                           | Υ    | 35       | Υ    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX170F256B | 28   | 256+3                              | 64               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Y    | 10                           | Υ    | 21       | Υ    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX170F256D | 44   | 256+3                              | 64               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 13                           | Υ    | 35       | Υ    | VTLA,<br>TQFP,<br>QFN           |

Note 1: This device features 3 KB of boot Flash memory.

**3:** Four out of five external interrupts are remappable.

**<sup>2:</sup>** Four out of five timers are remappable.

#### TABLE 6: PIN NAMES FOR 28-PIN USB DEVICES

28-PIN QFN (TOP VIEW)(1,2,3,4)

PIC32MX210F016B PIC32MX220F032B PIC32MX230F064B PIC32MX230F256B PIC32MX250F128B PIC32MX270F256B

28

| Pin # | Full Pin Name                              |

|-------|--------------------------------------------|

| 1     | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0  |

| 2     | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1 |

| 3     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2  |

| 4     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3    |

| 5     | Vss                                        |

| 6     | OSC1/CLKI/RPA2/RA2                         |

| 7     | OSC2/CLKO/RPA3/PMA0/RA3                    |

| 8     | SOSCI/RPB4/RB4                             |

| 9     | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4             |

| 10    | VDD                                        |

| 11    | TMS/RPB5/USBID/RB5                         |

| 12    | VBUS                                       |

| 13    | TDI/RPB7/CTED3/PMD5/INT0/RB7               |

| 14    | TCK/RPB8/SCL1/CTED10/PMD4/RB8              |

| Pin# | Full Pin Name                                    |

|------|--------------------------------------------------|

| 15   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                     |

| 16   | Vss                                              |

| 17   | VCAP                                             |

| 18   | PGED2/RPB10/D+/CTED11/RB10                       |

| 19   | PGEC2/RPB11/D-/RB11                              |

| 20   | Vusb3v3                                          |

| 21   | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 22   | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 23   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 24   | AVss                                             |

| 25   | AVDD                                             |

| 26   | MCLR                                             |

| 27   | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 28   | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

1

Note 1:

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

- 2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: Shaded pins are 5V tolerant.

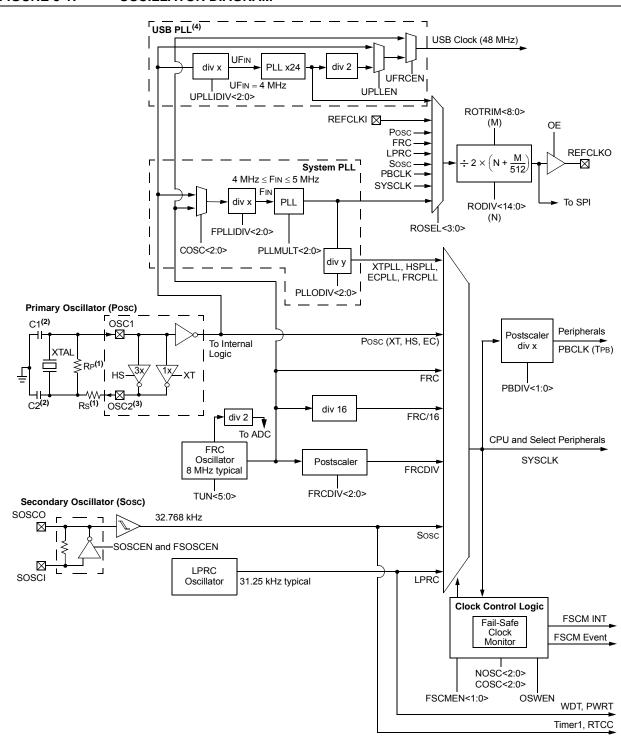

FIGURE 8-1: OSCILLATOR DIAGRAM

- Notes: 1. A series resistor, Rs, may be required for AT strip cut crystals or eliminate clipping. Alternately, to increase oscillator circuit gain, add a parallel resistor, RP, with a value of 1 MΩ.

- Refer to Section 6. "Oscillator Configuration" (DS60001112) in the "PIC32 Family Reference Manual" for help in determining the best oscillator components.

- 3. The PBCLK out is only available on the OSC2 pin in certain clock modes.

- 4. The USB PLL is only available on PIC32MX2XX devices.

#### REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|---------------------|-------------------|-----------------------|------------------|--|--|--|--|

| 04.04        | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0                 | R/W-0            |  |  |  |  |

| 31:24        | _                 |                   | RODIV<14:8>(1,3)  |                   |                     |                   |                       |                  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0                 | R/W-0            |  |  |  |  |

| 23:16        |                   |                   | RODIV<7:0>(1,3)   |                   |                     |                   |                       |                  |  |  |  |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0               | U-0               | R/W-0, HC             | R-0, HS, HC      |  |  |  |  |

| 15:8         | ON                |                   | SIDL              | OE                | RSLP <sup>(2)</sup> |                   | DIVSWEN               | ACTIVE           |  |  |  |  |

|              | U-0               | U-0               | U-0               | U-0               | R/W-0               | R/W-0             | R/W-0                 | R/W-0            |  |  |  |  |

| 7:0          | _                 | _                 |                   | -                 |                     | ROSEL             | .<3:0> <sup>(1)</sup> |                  |  |  |  |  |

**Legend:** HC = Hardware Clearable HS = Hardware Settable

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 Unimplemented: Read as '0'

bit 30-16 RODIV<14:0> Reference Clock Divider bits(1,3)

The value selects the reference clock divider bits. See Figure 8-1 for information.

bit 15 **ON:** Output Enable bit

1 = Reference Oscillator module is enabled

0 = Reference Oscillator module is disabled

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Peripheral Stop in Idle Mode bit

1 = Discontinue module operation when the device enters Idle mode

0 = Continue module operation when the device enters Idle mode

bit 12 **OE:** Reference Clock Output Enable bit

1 = Reference clock is driven out on REFCLKO pin

0 = Reference clock is not driven out on REFCLKO pin

bit 11 RSLP: Reference Oscillator Module Run in Sleep bit (2)

1 = Reference Oscillator module output continues to run in Sleep

0 = Reference Oscillator module output is disabled in Sleep

bit 10 **Unimplemented:** Read as '0'

bit 9 **DIVSWEN:** Divider Switch Enable bit

1 = Divider switch is in progress

0 = Divider switch is complete

bit 8 ACTIVE: Reference Clock Request Status bit

1 = Reference clock request is active

0 = Reference clock request is not active

bit 7-4 Unimplemented: Read as '0'

Note 1: The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

2: This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

#### REGISTER 9-5: DCRCDATA: DMA CRC DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31.24        |                   |                   |                   | DCRCDATA          | A<31:24>          |                   |                  |                  |  |  |  |  |  |

| 22.46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        |                   |                   |                   | DCRCDATA          | A<23:16>          |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         |                   | DCRCDATA<15:8>    |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   |                   |                   | DCRCDA            | TA<7:0>           |                   |                  |                  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (i.e., current IP header checksum value).

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

Bits greater than PLEN will return '0' on any read.

#### REGISTER 9-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        |                   |                   |                   | DCRCXOR           | ?<31:24>          |                   |                  |                  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | DCRCXOF           | ?<23:16>          |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | DCRCXO            | R<15:8>           |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | DCRCXO            | R<7:0>            |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

This register is unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = Enable the XOR input to the Shift register

- 0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

#### **REGISTER 10-10: U1STAT: USB STATUS REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -                 | -                 | -                 | -                 | -                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | _                 | -                 | -                 | -                 | -                 | -                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | -                 | _                 | -                 | -                 | -                 | -                 | -                | _                |

| 7:0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | U-0              | U-0              |

| 7.0          |                   | ENDP <sup>*</sup> | T<3:0>            |                   | DIR               | PPBI              | _                | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-4 ENDPT<3:0>: Encoded Number of Last Endpoint Activity bits

(Represents the number of the Buffer Descriptor Table, updated by the last USB transfer.)

1111 = Endpoint 15

1110 = Endpoint 14

:

.

0001 = Endpoint 1

0000 = Endpoint 0

- bit 3 DIR: Last Buffer Descriptor Direction Indicator bit

- 1 = Last transaction was a transmit (TX) transfer

- 0 = Last transaction was a receive (RX) transfer

- bit 2 **PPBI:** Ping-Pong Buffer Descriptor Pointer Indicator bit

- 1 = The last transaction was to the ODD Buffer Descriptor bank

- 0 = The last transaction was to the EVEN Buffer Descriptor bank

- bit 1-0 Unimplemented: Read as '0'

Note: The U1STAT register is a window into a 4-byte FIFO maintained by the USB module. U1STAT value is only valid when the TRNIF (U1IR<3>) bit is active. Clearing the TRNIF bit advances the FIFO. Data in register is invalid when the TRNIF bit = 0.

**TABLE 11-6:** PERIPHERAL PIN SELECT INPUT REGISTER MAP

| SS                          |                  |           | Bits  |       |       |       |       |       |      |      |      |      |      |      |      |       |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| FA04                        | INT1R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FAU4                        | INTIK            | 15:0      | _     | _     | _     | _     | _     | _     |      | _    | _    | _    |      | _    |      | INT1F | R<3:0> |      | 0000       |

| FA08                        | INT2R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 17100                       | IIVIZIX          | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | INT2F | R<3:0> |      | 0000       |

| FA0C                        | INT3R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 17.00                       | IIIII            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | INT3F | R<3:0> |      | 0000       |

| FA10                        | INT4R            | 31:16     |       |       | _     | _     | _     |       |      |      |      | _    |      |      | _    | _     | _      | _    | 0000       |

| .,                          |                  | 15:0      |       |       |       | _     |       |       |      |      |      | _    |      |      |      | INT4F | R<3:0> | ı    | 0000       |

| FA18                        | T2CKR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T2CKI | R<3:0> |      | 0000       |

| FA1C                        | T3CKR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      |       |       | _     | _     | _     | _     |      |      |      | _    |      |      |      | T3CKI | R<3:0> | ı    | 0000       |

| FA20                        | T4CKR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T4CKI | R<3:0> |      | 0000       |

| FA24                        | T5CKR            | 31:16     |       |       | _     |       | _     |       |      | _    |      | _    |      | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     |       |       | _     |      | _    | _    | _    | _    | _    |      | T5CKI | R<3:0> |      | 0000       |

| FA28                        | IC1R             | 31:16     | _     | _     | _     |       |       | _     |      | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             | _                | 15:0      | _     | _     | _     |       |       | _     |      | _    | _    | _    | _    | _    |      | IC1R  | <3:0>  |      | 0000       |

| FA2C                        | IC2R             | 31:16     | _     | _     | _     |       |       | _     |      | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             | _                | 15:0      | _     | _     | _     |       |       | _     |      | _    |      | _    |      | _    |      | IC2R  | <3:0>  |      | 0000       |

| FA30                        | IC3R             | 31:16     | _     | _     | _     |       |       | _     |      | _    |      | _    |      | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      |       | _     |       |       |       | _     |      | _    |      | _    |      | _    |      | IC3R  | <3:0>  |      | 0000       |

| FA34                        | IC4R             | 31:16     |       |       |       |       |       |       |      |      |      | _    |      |      |      |       |        | _    | 0000       |

|                             |                  | 15:0      |       |       |       |       |       |       |      |      |      | _    |      |      |      | IC4R  | <3:0>  |      | 0000       |

| FA38                        | IC5R             | 31:16     |       | _     |       |       |       | _     |      | _    |      | _    |      | _    | _    | _     |        | _    | 0000       |

|                             |                  | 15:0      | _     | _     |       |       |       | _     |      | _    |      | _    |      | _    |      | IC5R  | <3:0>  |      | 0000       |

| FA48                        | OCFAR            | 31:16     | _     | _     | _     | _     | _     | _     |      | _    | _    | _    |      | _    | _    | _     |        | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     |      | _    | _    | _    |      | _    |      | OCFA  | R<3:0> |      | 0000       |

| FA4C                        | OCFBR            | 31:16     |       | _     | _     | _     | _     | _     |      |      |      | _    |      |      | _    | _     |        | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | OCFB  | R<3:0> |      | 0000       |

| FA50                        | U1RXR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             | •                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U1RX  | R<3:0> |      | 0000       |

### 18.1 I2C Control Registers

#### TABLE 18-1: I2C1 AND I2C2 REGISTER MAP

| ess                         |                                 |               |         |        |       |        |        |       |        | Bi    | ts                           |             |            |              |          |      |      |      |            |

|-----------------------------|---------------------------------|---------------|---------|--------|-------|--------|--------|-------|--------|-------|------------------------------|-------------|------------|--------------|----------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14  | 29/13 | 28/12  | 27/11  | 26/10 | 25/9   | 24/8  | 23/7                         | 22/6        | 21/5       | 20/4         | 19/3     | 18/2 | 17/1 | 16/0 | All Resets |

| 5000                        | I2C1CON                         | 31:16         |         | _      | _     | _      | _      | _     | _      | _     |                              | _           |            | _            |          | _    | _    | _    | 0000       |

|                             |                                 | 15:0          | ON      |        | SIDL  | SCLREL | STRICT | A10M  | DISSLW | SMEN  | GCEN                         | STREN       | ACKDT      | ACKEN        | RCEN     | PEN  | RSEN | SEN  | 1000       |

| 5010                        | I2C1STAT                        | 31:16         |         |        |       | _      |        | _     | -      | -     |                              | -           |            | _            | _        | -    | _    |      | 0000       |

|                             |                                 |               | ACKSTAT | TRSTAT |       | _      |        | BCL   | GCSTAT | ADD10 | IWCOL                        | I2COV       | D_A        | Р            | S        | R_W  | RBF  | TBF  | 0000       |

| 5020                        | I2C1ADD                         | 31:16         | _       |        |       | _      |        |       | _      | _     | _                            | _           | <u> </u>   | <u> </u>     | _        | _    | _    | _    | 0000       |

|                             |                                 | 15:0          | _       |        |       | _      |        |       |        |       |                              |             | Address    | Register     |          |      |      |      | 0000       |

| 5030                        | I2C1MSK                         | 31:16<br>15:0 |         | _      | _     | _      | _      | _     | _      | _     | _                            | _           |            | —<br>!-D!-t  | _        | _    | _    | _    | 0000       |

|                             |                                 | 31:16         | _       | _      | _     | _      | _      | _     |        |       |                              |             | Address Ma | ask Register |          |      |      |      | 0000       |

| 5040                        | I2C1BRG                         | 15:0          | _       |        | _     | _      | _      | _     | _      |       |                              | d Bata Car  | orator Boa | inter        |          | _    | _    | _    | 0000       |

|                             |                                 | 31:16         | _       | _      |       | _      |        |       | _      | _     | Baud Rate Generator Register |             |            |              |          | _    | 0000 |      |            |

| 5050                        | I2C1TRN                         | 15:0          | _       |        |       |        |        | _     |        |       | T "D '                       |             |            |              |          | _    | 0000 |      |            |

|                             |                                 | 31:16         | _       |        |       | _      |        |       | _      |       | _                            | _           | _          |              | Register | _    | _    | _    | 0000       |

| 5060                        | I2C1RCV                         | 15:0          | _       |        |       |        |        |       |        |       | <u> </u>                     | _           |            | Receive      | Pegister |      |      |      | 0000       |

|                             |                                 | 31:16         |         |        |       |        |        |       |        |       |                              | _           | _          |              | —        | _    | _    | _    | 0000       |

| 5100                        | I2C2CON                         | 15:0          | ON      |        | SIDL  | SCLREL | STRICT | A10M  | DISSLW | SMEN  | GCEN                         | STREN       | ACKDT      | ACKEN        | RCEN     | PEN  | RSEN | SEN  | 1000       |

|                             |                                 | 31:16         |         |        | —     |        | _      | _     |        | _     | _                            | —           | _          |              | _        | _    | _    | _    | 0000       |

| 5110                        | I2C2STAT                        |               | ACKSTAT | TRSTAT |       | _      |        | BCL   | GCSTAT | ADD10 | IWCOL                        | I2COV       | DΑ         | Р            | S        | R W  | RBF  | TBF  | 0000       |

|                             |                                 | 31:16         |         | _      | _     | _      | _      |       | _      | _     | _                            | _           |            | _            | _        |      | _    | _    | 0000       |

| 5120                        | I2C2ADD                         | 15:0          | _       |        |       | _      |        | _     |        |       |                              |             | Address    | Register     |          |      |      |      | 0000       |

|                             |                                 | 31:16         | _       | _      | _     | _      | _      | _     | _      | _     | _                            | _           | _          | _            | _        | _    | _    | _    | 0000       |

| 5130                        | I2C2MSK                         | 15:0          | _       | _      | _     | _      |        | _     |        |       |                              |             | Address Ma | sk Register  |          |      |      |      | 0000       |

| 5440                        | 1000000                         | 31:16         | _       | 1      | _     | _      | -      | _     | _      | _     | _                            | _           | _          | _            | _        | _    | _    | _    | 0000       |

| 5140                        | I2C2BRG                         | 15:0          | _       |        | _     | _      |        | •     | •      |       | Bau                          | id Rate Ger | erator Reg | ister        |          |      |      |      | 0000       |

| 5150                        | I2C2TRN                         | 31:16         | _       |        |       | _      | ı      | _     | _      | _     | _                            | _           | _          | _            | _        | _    | _    | _    | 0000       |

| 5 150                       | 12021KN                         | 15:0          | _       |        |       | _      |        |       |        | _     |                              |             |            | Transmit     | Register |      |      |      | 0000       |

| 5160                        | I2C2RCV                         | 31:16         | _       | _      | _     | _      | -      | _     | _      | _     |                              | _           | _          | _            |          |      | _    | _    | 0000       |

| 3 100                       | IZUZRUV                         | 15:0          | _       | _      | _     | _      | _      | _     | _      |       |                              |             |            | Receive      | Register |      |      |      | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### REGISTER 19-2: UxSTA: UARTX STATUS AND CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 31:24        |                   | _                 | _                 | -                 | _                 | -                 | _                | ADM_EN           |

| 22.46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | ADDR<             | <7:0>             |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-1              |

| 15:8         | UTXISE            | L<1:0>            | UTXINV            | URXEN             | UTXBRK            | UTXEN             | UTXBF            | TRMT             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R-1               | R-0               | R-0               | R/W-0            | R-0              |

| 7:0          | URXISE            | L<1:0>            | ADDEN             | RIDLE             | PERR              | FERR              | OERR             | URXDA            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-25 Unimplemented: Read as '0'

bit 24 ADM\_EN: Automatic Address Detect Mode Enable bit

1 = Automatic Address Detect mode is enabled

0 = Automatic Address Detect mode is disabled

bit 23-16 ADDR<7:0>: Automatic Address Mask bits

When the ADM\_EN bit is '1', this value defines the address character to use for automatic address detection.

bit 15-14 UTXISEL<1:0>: TX Interrupt Mode Selection bits

11 = Reserved, do not use

10 = Interrupt is generated and asserted while the transmit buffer is empty

01 = Interrupt is generated and asserted when all characters have been transmitted

00 = Interrupt is generated and asserted while the transmit buffer contains at least one empty space

bit 13 **UTXINV:** Transmit Polarity Inversion bit

If IrDA mode is disabled (i.e., IREN (UxMODE<12>) is '0'):

1 = UxTX Idle state is '0'

0 = UxTX Idle state is '1'

#### If IrDA mode is enabled (i.e., IREN (UxMODE<12>) is '1'):

1 = IrDA encoded UxTX Idle state is '1'

0 = IrDA encoded UxTX Idle state is '0'

bit 12 URXEN: Receiver Enable bit

1 = UARTx receiver is enabled. UxRX pin is controlled by UARTx (if ON = 1)

0 = UARTx receiver is disabled. UxRX pin is ignored by the UARTx module. UxRX pin is controlled by port.

bit 11 UTXBRK: Transmit Break bit

1 = Send Break on next transmission. Start bit followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

0 = Break transmission is disabled or completed

bit 10 UTXEN: Transmit Enable bit

1 = UARTx transmitter is enabled. UxTX pin is controlled by UARTx (if ON = 1).

0 = UARTx transmitter is disabled. Any pending transmission is aborted and buffer is reset. UxTX pin is controlled by port.

bit 9 UTXBF: Transmit Buffer Full Status bit (read-only)

1 = Transmit buffer is full

0 = Transmit buffer is not full, at least one more character can be written

bit 8 **TRMT:** Transmit Shift Register is Empty bit (read-only)

1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed)

0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer

| PIC32M | X1XX/2X | (X 28/3 | 6/44-PI | NFAM | ILY |  |

|--------|---------|---------|---------|------|-----|--|

| NOTES: |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

TABLE 22-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                  | ө        | Bits  |                                                              |       |       |       |       |         |             |           |          |      | v    |      |      |      |      |           |

|-----------------------------|------------------|----------|-------|--------------------------------------------------------------|-------|-------|-------|-------|---------|-------------|-----------|----------|------|------|------|------|------|------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Rang | 31/15 | 30/14                                                        | 29/13 | 28/12 | 27/11 | 26/10 | 25/9    | 24/8        | 23/7      | 22/6     | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Reset |

| 9120                        | ADC1BUFB         | 31:16    |       | ADC Result Word B (ADC1BUFB<31:0>)                           |       |       |       |       |         |             |           |          |      |      |      | 0000 |      |      |           |

| 0120                        | 715015015        | 15:0     |       | 7.55 Noon 110 5 (Nool 15 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |       |       |       |       |         |             |           |          |      |      |      |      |      | 0000 |           |

| 0130                        | ADC1BUFC         | 31:16    |       |                                                              |       |       |       |       | ADC Bos | ult Word C  | (ADC1BLIE | C<31:0>) |      |      |      |      |      |      | 0000      |

| 9130                        | ADCIBUFC         | 15:0     |       | ADC Result Word C (ADC1BUFC<31:0>)                           |       |       |       |       |         |             |           |          |      |      |      | 0000 |      |      |           |

| 0140                        | ADC1BUFD         | 31:16    |       |                                                              |       |       |       |       | ADC Boo | ult Word D  | (ADC1BUF  | D-21:0>) |      |      |      |      |      |      | 0000      |

| 9140                        | ADCIBULD         | 15:0     |       |                                                              |       |       |       |       | ADC Res | uit vvoiu D | (ADC IBUF | D<31.02) |      |      |      |      |      |      | 0000      |

| 0150                        | ADC1BUFE         | 31:16    |       |                                                              |       |       |       |       | ADC Pos | ult Word E  | (ADC1BUF  | E_31:0\) |      |      |      |      |      |      | 0000      |

| 9130                        | ADCIBULE         | 15:0     |       |                                                              |       |       |       |       | ADO RES | uit vvolu E | (ADC IBUE | L~31.0/) |      |      |      |      |      |      | 0000      |

| 0160                        | ADC1BUFF         | 31:16    |       |                                                              |       |       |       |       | ADC Box | ult Mord E  | (ADC1BLIE | E-21:0~\ |      |      |      |      |      |      | 0000      |

| 9100                        | ADCIBUFF         | 15:0     |       |                                                              |       |       |       |       | ADC Res | uit vvoid F | (ADC1BUF  | F\31.02) |      |      |      |      |      |      | 0000      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for details.

### 24.1 Comparator Voltage Reference Control Register

#### TABLE 24-1: COMPARATOR VOLTAGE REFERENCE REGISTER MAP

| ess                         |                                 | ø.        |       |       |       |       |       |       |      | Bits |      |       |      |       |      |      |      |      |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|-------|------|-------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6  | 21/5 | 20/4  | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 0000                        | O) (DOON                        | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _     | _    | _     | _    | _    | _    | _    | 0000       |

| 9800                        | CVRCON                          | 15:0      | ON    | _     | _     | _     |       | _     | _    | _    | _    | CVROE | CVRR | CVRSS |      | CVR< | 3:0> |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### REGISTER 24-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | -                 |                   | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | -                 |                   |                   | _                | _                |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | CVROE             | CVRR              | CVRSS             |                   | CVR<              | <3:0>            |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Comparator Voltage Reference On bit<sup>(1)</sup>

1 = Module is enabled

Setting this bit does not affect other bits in the register.

0 = Module is disabled and does not consume current.Clearing this bit does not affect the other bits in the register.

bit 14-7 Unimplemented: Read as '0'

bit 6 CVROE: CVREFOUT Enable bit

1 = Voltage level is output on CVREFOUT pin

0 = Voltage level is disconnected from CVREFOUT pin

bit 5 CVRR: CVREF Range Selection bit

1 = 0 to 0.67 CVRSRC, with CVRSRC/24 step size

0 = 0.25 CVRSRC to 0.75 CVRSRC, with CVRSRC/32 step size

bit 4 CVRSS: CVREF Source Selection bit

1 = Comparator voltage reference source, CVRSRC = (VREF+) - (VREF-)

0 = Comparator voltage reference source, CVRSRC = AVDD - AVSS

bit 3-0 **CVR<3:0>:** CVREF Value Selection  $0 \le CVR < 3:0 > \le 15$  bits

When CVRR = 1:

CVREF = (CVR<3:0>/24) • (CVRSRC)

When CVRR = 0:

CVREF = 1/4 • (CVRSRC) + (CVR<3:0>/32) • (CVRSRC)

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 27-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2     | Bit<br>25/17/9/1                                              | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|----------------------|-----------------------|---------------------------------------------------------------|------------------|

| 24.24        | r-0               | r-1               | r-1               | R/P               | r-1                  | r-1                   | r-1                                                           | R/P              |

| 31:24        |                   | _                 | _                 | CP                | _                    | _                     |                                                               | BWP              |

| 22.46        | r-1               | r-1               | r-1               | r-1               | r-1                  | R/P                   | R/P                                                           | R/P              |

| 23:16        |                   | _                 | _                 | _                 | _                    | I                     | PWP<8:6> <sup>(3)</sup>                                       |                  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | R/P                  | R/P                   | r-1                                                           | r-1              |

| 15:8         |                   |                   | PWP<              | :5:0>             |                      |                       | 25/17/9/1 24/16/ r-1 R/F — BW R/P R/F PWP<8:6>(3) r-1 r-1 — — | _                |

| 7.0          | r-1               | r-1               | r-1               | R/P               | R/P                  | R/P                   | R/P                                                           | R/P              |

| 7:0          | _                 | _                 |                   | ICESEL            | <1:0> <sup>(2)</sup> | JTAGEN <sup>(1)</sup> | DEBU                                                          | G<1:0>           |

Legend:r = Reserved bitP = Programmable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31 Reserved: Write '0' bit 30-29 Reserved: Write '1' bit 28 CP: Code-Protect bit

Prevents boot and program Flash memory from being read or modified by an external programming device.

1 = Protection is disabled0 = Protection is enabled

bit 27-25 Reserved: Write '1'

bit 24 **BWP:** Boot Flash Write-Protect bit

Prevents boot Flash memory from being modified during code execution.

1 = Boot Flash is writable0 = Boot Flash is not writable

bit 23-19 Reserved: Write '1'

Note 1: This bit sets the value for the JTAGEN bit in the CFGCON register.

- 2: The PGEC4/PGED4 pin pair is not available on all devices. Refer to the "Pin Diagrams" section for availability.

- 3: The PWP<8:7> bits are only available on devices with 256 KB Flash.

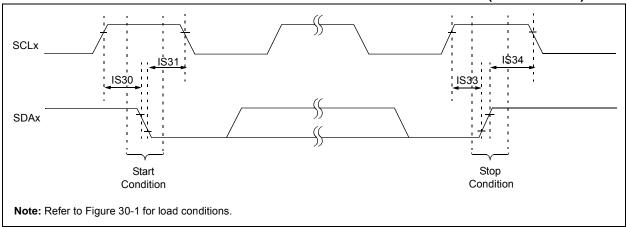

TABLE 30-32: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE) (CONTINUED)

| AC CHA        | RACTER  | ISTICS           |                     | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \leq \text{TA} \leq +105^{\circ}\text{C}$ for V-temp |      |       |                                     |  |  |

|---------------|---------|------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------------------------------------|--|--|

| Param.<br>No. | Symbol  | Characteristics  |                     | Min. <sup>(1)</sup>                                                                                                                                                                                                                                | Max. | Units | Conditions                          |  |  |

| IM40          | TAA:SCL | Output Valid     | 100 kHz mode        | _                                                                                                                                                                                                                                                  | 3500 | ns    | _                                   |  |  |

|               |         | from Clock       | 400 kHz mode        | _                                                                                                                                                                                                                                                  | 1000 | ns    | _                                   |  |  |

|               |         |                  | 1 MHz mode (Note 2) | _                                                                                                                                                                                                                                                  | 350  | ns    | _                                   |  |  |

| IM45          | TBF:SDA | Bus Free Time    | 100 kHz mode        | 4.7                                                                                                                                                                                                                                                | _    | μS    | The amount of time the              |  |  |

|               |         |                  | 400 kHz mode        | 1.3                                                                                                                                                                                                                                                | _    | μS    | bus must be free                    |  |  |

|               |         |                  | 1 MHz mode (Note 2) | 0.5                                                                                                                                                                                                                                                | _    | μS    | before a new transmission can start |  |  |

| IM50          | Св      | Bus Capacitive L | oading              | _                                                                                                                                                                                                                                                  | 400  | pF    | _                                   |  |  |

| IM51          | TPGD    | Pulse Gobbler D  | elay                | 52                                                                                                                                                                                                                                                 | 312  | ns    | See Note 3                          |  |  |

**Note 1:** BRG is the value of the I<sup>2</sup>C Baud Rate Generator.

<sup>2:</sup> Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**<sup>3:</sup>** The typical value for this parameter is 104 ns.

#### FIGURE 30-16: I2Cx BUS START/STOP BITS TIMING CHARACTERISTICS (SLAVE MODE)

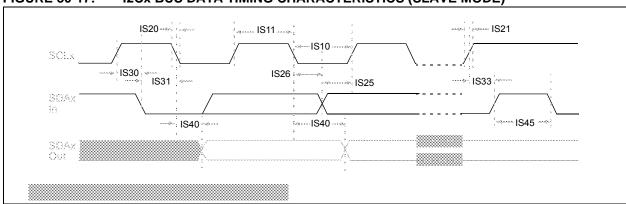

#### FIGURE 30-17: I2Cx BUS DATA TIMING CHARACTERISTICS (SLAVE MODE)

TABLE A-1: MAJOR SECTION UPDATES (CONTINUED)

| Section                        | Update Description                                                                                                                                                                                                                   |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.0 "Memory Organization"      | Added Memory Maps for the new devices (see Figure 4-3 and Figure 4-4).                                                                                                                                                               |

|                                | Removed the BMXCHEDMA bit from the Bus Matrix Register map (see Table 4-1).                                                                                                                                                          |

|                                | Added the REFOTRIM register, added the DIVSWEN bit to the REFOCON registers, added Note 4 to the ULOCK and SOSCEN bits and added the PBDIVRDY bit in the OSCCON register in the in the System Control Register map (see Table 4-16). |

|                                | Removed the ALTI2C1 and ALTI2C2 bits from the DEVCFG3 register and added Note 1 to the UPLLEN and UPLLIDIV<2:0> bits of the DEVCFG2 register in the Device Configuration Word Summary (see Table 4-17).                              |

|                                | Updated Note 1 in the Device and Revision ID Summary (see Table 4-18).                                                                                                                                                               |

|                                | Added Note 2 to the PORTA Register map (see Table 4-19).                                                                                                                                                                             |

|                                | Added the ANSB6 and ANSB12 bits to the ANSELB register in the PORTB Register map (see Table 4-20).                                                                                                                                   |

|                                | Added Notes 2 and 3 to the PORTC Register map (see Table 4-21).                                                                                                                                                                      |

|                                | Updated all register names in the Peripheral Pin Select Register map (see Table 4-23).                                                                                                                                               |

|                                | Added values in support of new devices (16 KB RAM and 32 KB RAM) in the Data RAM Size register (see Register 4-5).                                                                                                                   |

|                                | Added values in support of new devices (64 KB Flash and 128 KB Flash) in the Data RAM Size register (see Register 4-5).                                                                                                              |

| 8.0 "Oscillator Configuration" | Added Note 5 to the PIC32MX1XX/2XX Family Clock Diagram (see Figure 8-1).                                                                                                                                                            |

|                                | Added the PBDIVRDY bit and Note 2 to the Oscillator Control register (see Register 8-1).                                                                                                                                             |

|                                | Added the DIVSWEN bit and Note 3 to the Reference Oscillator Control register (see Register 8-3).                                                                                                                                    |

|                                | Added the REFOTRIM register (see Register 8-4).                                                                                                                                                                                      |

| 21.0 "10-bit Analog-to-Digital | Updated the ADC1 Module Block Diagram (see Figure 21-1).                                                                                                                                                                             |

| Converter (ADC)"               | Updated the Notes in the ADC Input Select register (see Register 21-4).                                                                                                                                                              |

| 24.0 "Charge Time Measurement  | Updated the CTMU Block Diagram (see Figure 24-1).                                                                                                                                                                                    |

| Unit (CTMU)"                   | Added Note 3 to the CTMU Control register (see Register 24-1)                                                                                                                                                                        |

| 26.0 "Special Features"        | Added Note 1 and the PGEC4/PGED4 pin pair to the ICESEL<1:0> bits in DEVCFG0: Device Configuration Word 0 (see Register 26-1).                                                                                                       |

|                                | Removed the ALTI2C1 and ALTI2C2 bits from the Device Configuration Word 3 register (see Register 26-4).                                                                                                                              |

|                                | Removed 26.3.3 "Power-up Requirements".                                                                                                                                                                                              |

|                                | Added Note 3 to the Connections for the On-Chip Regulator diagram (see Figure 26-2).                                                                                                                                                 |

|                                | Updated the Block Diagram of Programming, Debugging and Trace Ports diagram (see Figure 26-3).                                                                                                                                       |

#### **Revision D (February 2012)**

All occurrences of VUSB were changed to: VUSB3V3. In addition, text and formatting changes were incorporated throughout the document.

All other major changes are referenced by their respective section in Table A-3.

TABLE A-3: MAJOR SECTION UPDATES

| Section                                                                                | Update Description                                                                                                                                                                |  |  |  |  |  |

|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| "32-bit Microcontrollers (up to 128                                                    | Corrected a part number error in all pin diagrams.                                                                                                                                |  |  |  |  |  |

| KB Flash and 32 KB SRAM) with Audio and Graphics Interfaces, USB, and Advanced Analog" | Updated the DMA Channels (Programmable/Dedicated) column in the PIC32MX1XX General Purpose Family Features (see Table 1).                                                         |  |  |  |  |  |

| 1.0 "Device Overview"                                                                  | Added the TQFP and VTLA packages to the 44-pin column heading and updated the pin numbers for the SCL1, SCL2, SDA1, and SDA2 pins in the Pinout I/O Descriptions (see Table 1-1). |  |  |  |  |  |

| 7.0 "Interrupt Controller"                                                             | Updated the Note that follows the features.                                                                                                                                       |  |  |  |  |  |

|                                                                                        | Updated the Interrupt Controller Block Diagram (see Figure 7-1).                                                                                                                  |  |  |  |  |  |

| 29.0 "Electrical Characteristics"                                                      | Updated the Maximum values for parameters DC20-DC24, and the Minimum value for parameter DC21 in the Operating Current (IDD) DC Characteristics (see Table 29-5).                 |  |  |  |  |  |

|                                                                                        | Updated all Minimum and Maximum values for the Idle Current (IIDLE) DC Characteristics (see Table 29-6).                                                                          |  |  |  |  |  |

|                                                                                        | Updated the Maximum values for parameters DC40k, DC40l, DC40n, and DC40m in the Power-down Current (IPD) DC Characteristics (see Table 29-7).                                     |  |  |  |  |  |

|                                                                                        | Changed the minimum clock period for SCKx from 40 ns to 50 ns in Note 3 of the SPIx Master and Slave Mode Timing Requirements (see Table 29-26 through Table 29-29).              |  |  |  |  |  |

| 30.0 "DC and AC Device Characteristics Graphs"                                         | Updated the Typical IIDLE Current @ VDD = 3.3V graph (see Figure 30-5).                                                                                                           |  |  |  |  |  |

#### **INDEX**

| Numerics                                      |          | Core Exception Types                      |     |

|-----------------------------------------------|----------|-------------------------------------------|-----|

| 50 MHz Electrical Characteristics             | 301      | EJTAG Debug Support                       |     |

| A                                             |          | Power Management                          |     |

| Α                                             |          | CPU Module                                |     |

| AC Characteristics                            |          | Customer Change Notification Service      |     |

| 10-Bit Conversion Rate Parameters             |          | Customer Support                          |     |

| ADC Specifications                            |          | Customer Support                          | 34  |

| Analog-to-Digital Conversion Requirements     |          | D                                         |     |

| EJTAG Timing Requirements                     |          | DC and AC Characteristics                 |     |

| Internal FRC Accuracy                         |          | Graphs and Tables                         | 30. |

| Internal RC Accuracy                          |          | DC Characteristics                        |     |

| OTG Electrical Specifications                 |          | I/O Pin Input Specifications              |     |

| Parallel Master Port Read Requirements        |          | I/O Pin Output Specifications             |     |

| Parallel Master Port Write                    |          | Idle Current (IDLE)                       |     |

| Parallel Master Port Write Requirements       | 298      |                                           |     |

| Parallel Slave Port Requirements              | 296      | Program Mamon                             |     |

| PLL Clock Timing                              | 271      | Program Memory                            |     |

| Analog-to-Digital Converter (ADC)             | 209      | Temperature and Voltage Specifications    |     |

| Assembler                                     |          | DC Characteristics (50 MHz)               |     |

| MPASM Assembler                               | 254      | Idle Current (IDLE)                       |     |

| В                                             |          | Power-Down Current (IPD)                  |     |

| В                                             |          | Development Support                       |     |

| Block Diagrams                                |          | Direct Memory Access (DMA) Controller     | 8.  |

| ADC Module                                    |          | E                                         |     |

| Comparator I/O Operating Modes                | 219      | Electrical Characteristics                | 25. |

| Comparator Voltage Reference                  |          |                                           |     |

| Connections for On-Chip Voltage Regulator     |          | AC                                        |     |

| Core and Peripheral Modules                   | 19       | Errata External Clock                     | 10  |

| CPU                                           | 33       |                                           | 27/ |

| CTMU Configurations                           |          | Timer1 Timing Requirements                |     |

| Time Measurement                              | 227      | Timer2, 3, 4, 5 Timing Requirements       |     |