Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx170f256d-i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

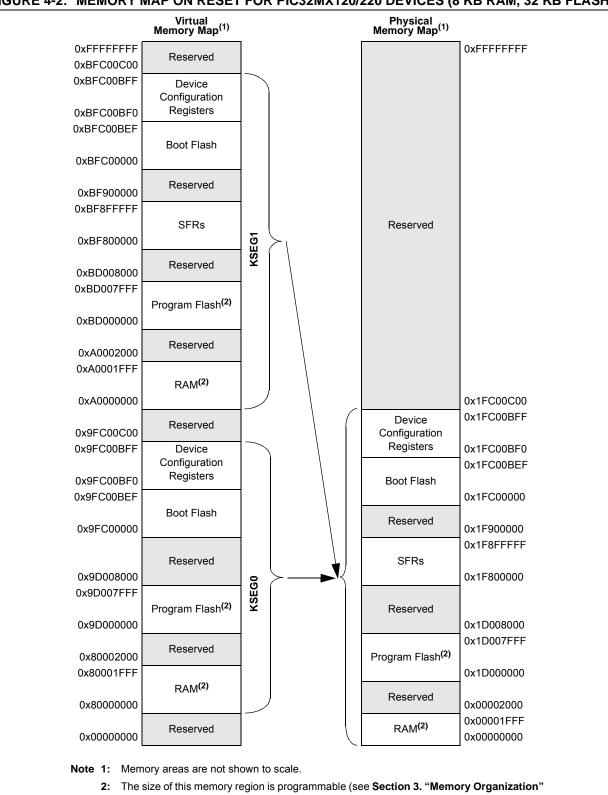

## FIGURE 4-2: MEMORY MAP ON RESET FOR PIC32MX120/220 DEVICES (8 KB RAM, 32 KB FLASH)

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS60001115) in the "*PIC32 Family Reference Manual*") and can be changed by initialization code provided by end-user development tools (refer to the specific development tool documentation for information).

## 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS60001121), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming™ (ICSP™)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which can be downloaded from the Microchip web site.

Note: The Flash page size on PIC32MX-1XX/2XX 28/36/44-pin Family devices is 1 KB and the row size is 128 bytes (256 IW and 32 IW, respectively).

## TABLE 9-3: DMA CHANNELS 0-3 REGISTER MAP (CONTINUED)

| ess                         |                                 |           | Bits   |       |       |       |        |       |      |                      |         |        |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|-----------|--------|-------|-------|-------|--------|-------|------|----------------------|---------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15  | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8                 | 23/7    | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 3170                        | DCH1SSIZ                        | 31:16     | —      | _     | —     | _     |        | _     | _    | _                    | _       |        | -      | _      | -      | —      | _      |        | 0000       |

| 5170                        | DOITIOOIZ                       | 15:0      |        |       |       |       |        |       |      | CHSSIZ               | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 3180                        | DCH1DSIZ                        | 31:16     | _      | _     | —     | —     | —      | —     | _    | -                    | —       | —      | _      |        | _      | —      | _      | —      | 0000       |

| 5100                        | DOITIDOIZ                       | 15:0      |        |       |       |       |        |       |      | CHDSIZ               | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 3190                        | DCH1SPTR                        | 31:16     | _      | —     | —     | —     | —      | —     | —    | —                    | —       | —      | —      | —      | —      | —      | _      | _      | 0000       |

| 0100                        |                                 | 15:0      |        |       |       |       |        |       |      | CHSPTI               | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 31A0                        | DCH1DPTR                        | 31:16     | —      | —     | —     | —     | —      | —     | —    | —                    | —       | —      | —      | —      | —      | —      | —      | —      | 0000       |

| 017.00                      |                                 | 15:0      |        |       |       |       |        |       |      | CHDPT                | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 31B0                        | DCH1CSIZ                        | 31:16     | _      | _     | —     | —     | —      | —     | _    | _                    | —       | —      | _      | —      | —      | —      | —      | -      | 0000       |

| 0.20                        |                                 | 15:0      |        |       |       |       |        |       |      | CHCSIZ               | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 31C0                        | DCH1CPTR                        | 31:16     | _      | _     | _     | —     | —      | —     | _    | _                    | —       | —      | —      |        | —      | —      | —      |        | 0000       |

| 0.00                        |                                 | 15:0      |        |       |       |       |        |       |      | CHCPTI               | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 31D0                        | DCH1DAT                         | 31:16     | —      | _     | —     | —     | —      | —     | —    | _                    | _       | —      | —      |        | —      | —      | —      |        | 0000       |

| 0.20                        |                                 | 15:0      | —      | _     | —     | —     | —      | —     | —    | _                    |         |        |        | CHPDA  |        |        |        |        | 0000       |

| 31F0                        | DCH2CON                         | 31:16     | —      | _     | —     | —     | —      | —     | —    | _                    |         | _      | —      | _      | _      | —      | —      |        | 0000       |

| 0.20                        |                                 |           | CHBUSY | _     | _     | —     | _      | _     |      | CHCHNS               | CHEN    | CHAED  | CHCHN  | CHAEN  | —      | CHEDET | CHPR   | <1:0>  | 0000       |

| 31F0                        | DCH2ECON                        | 31:16     | _      | _     | —     | —     | —      | —     | _    | _                    |         |        |        | CHAIR  |        |        |        |        | 00FF       |

|                             |                                 | 15:0      |        |       |       | CHSIR | Q<7:0> |       |      |                      | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN | _      | —      | —      | FF00       |

| 3200                        | DCH2INT                         | 31:16     | —      | —     | —     | —     | —      | —     | _    | —                    | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 0000       |

|                             |                                 | 15:0      | _      | _     |       | —     | —      | —     |      |                      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3210                        | DCH2SSA                         | 31:16     |        |       |       |       |        |       |      | CHSSA                | <31:0>  |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 15:0      |        |       |       |       |        |       |      |                      |         |        |        |        |        |        |        |        | 0000       |

| 3220                        |                                 | 31:16     |        |       |       |       |        |       |      | CHDSA                | <31:0>  |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 15:0      |        |       |       |       |        |       |      | 1                    |         |        |        |        |        |        |        |        | 0000       |

| 3230                        | DCH2SSIZ                        | 31:16     |        | —     | —     | —     | —      | —     | —    |                      | —       | —      | —      | —      | —      | —      | —      | —      | 0000       |

|                             |                                 | 15:0      |        |       |       |       |        |       |      | CHSSIZ               | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 3240                        | DCH2DSIZ                        | 31:16     |        |       | —     | _     | —      | _     | _    | <u> </u>             | —       | —      | —      | —      | —      | —      | _      | —      | 0000       |

|                             |                                 | 15:0      |        |       |       |       |        |       |      | CHDSIZ               | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 3250                        | DCH2SPTR                        | 31:16     |        |       | —     | _     | —      | _     | _    | <u> </u>             | —       | —      | —      | —      | —      | —      | _      |        | 0000       |

|                             |                                 | 15:0      |        |       |       |       |        |       |      | CHSPTI               | ≺<15:0> |        |        |        |        |        |        |        | 0000       |

| 3260                        | DCH2DPTR                        | 31:16     |        |       | —     | _     | —      | _     | _    | —                    | —       | —      | —      | —      | —      | —      | —      | —      | 0000       |

|                             |                                 | 15:0      |        |       |       |       |        |       |      | CHDPTI               | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 3270                        | DCH2CSIZ                        | 31:16     |        | _     | —     | —     | —      | —     | —    |                      | —       | —      | —      | —      | —      | —      | _      |        | 0000       |

|                             |                                 | 15:0      |        |       |       |       |        |       |      | CHCSI2<br>exadecimal |         |        |        |        |        |        |        |        | 0000       |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| <b>NEGIST</b> | EGISTER 10-1. OTOTGIR. USB OTG INTERROFT STATUS REGISTER |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

|---------------|----------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| Bit<br>Range  | Bit<br>31/23/15/7                                        | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

| 31:24         | U-0                                                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31.24         | -                                                        | —                 | —                 | -                 | -                 | —                 | -                | —                |  |  |  |  |  |

| 23:16         | U-0                                                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23.10         | -                                                        | —                 | —                 | -                 | -                 | —                 | -                | —                |  |  |  |  |  |

| 15:8          | U-0                                                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 15.6          |                                                          | _                 | -                 |                   |                   | —                 |                  | —                |  |  |  |  |  |

| 7.0           | R/WC-0, HS                                               | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS        | U-0              | R/WC-0, HS       |  |  |  |  |  |

| 7:0           | IDIF                                                     | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF           | SESENDIF          |                  | VBUSVDIF         |  |  |  |  |  |

## REGISTER 10-1: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable b  | pit                |

|-------------------|-------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIF:** ID State Change Indicator bit

- 1 = A change in the ID state was detected

- 0 = No change in the ID state was detected

- bit 6 T1MSECIF: 1 Millisecond Timer bit

- 1 = 1 millisecond timer has expired

- 0 = 1 millisecond timer has not expired

#### bit 5 LSTATEIF: Line State Stable Indicator bit

- 1 = USB line state has been stable for 1 ms, but different from last time

- 0 = USB line state has not been stable for 1 ms

- bit 4 ACTVIF: Bus Activity Indicator bit

- 1 = Activity on the D+, D-, ID or VBUS pins has caused the device to wake-up

- 0 = Activity has not been detected

- bit 3 SESVDIF: Session Valid Change Indicator bit

- 1 = VBUS voltage has dropped below the session end level

- 0 = VBUS voltage has not dropped below the session end level

- bit 2 SESENDIF: B-Device VBUS Change Indicator bit

- 1 = A change on the session end input was detected

- 0 = No change on the session end input was detected

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIF: A-Device VBUS Change Indicator bit

- 1 = A change on the session valid input was detected

- 0 = No change on the session valid input was detected

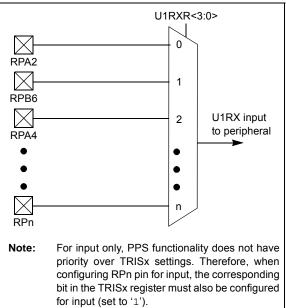

## 11.3 Peripheral Pin Select

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin-count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only option.

The Peripheral Pin Select (PPS) configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The PPS configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

## 11.3.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the PPS feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

## 11.3.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digitalonly peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital-only peripheral modules are never included in the PPS feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin.

Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.3.3 CONTROLLING PERIPHERAL PIN SELECT

PPS features are controlled through two sets of SFRs: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

## 11.3.4 INPUT MAPPING

The inputs of the PPS options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The [*pin name*]R registers, where [*pin name*] refers to the peripheral pins listed in Table 11-1, are used to configure peripheral input mapping (see Register 11-1). Each register contains sets of 4 bit fields. Programming these bit fields with an appropriate value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field is shown in Table 11-1.

For example, Figure 11-2 illustrates the remappable pin selection for the U1RX input.

#### FIGURE 11-2: REMAPPABLE INPUT EXAMPLE FOR U1RX

## TABLE 11-6: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| ssa                         |                  |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |       |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| FA04                        | INT1R            | 31:16     |       | _     |       |       | _     | _     |      |      |      | _    |      |      |      | _     | _      |      | 0000       |

| FA04                        |                  | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | INT1F | R<3:0> |      | 0000       |

| FA08                        | INT2R            | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | _     | —      | —    | 0000       |

| FAUO                        | INTZR            | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | INT2F | R<3:0> |      | 0000       |

| FA0C                        | INT3R            | 31:16     | _     | _     | _     | _     | —     | —     | _    | _    | —    | _    |      | —    | _    |       | —      | —    | 0000       |

| FAUC                        | IN I 3R          | 15:0      |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | INT3F | R<3:0> |      | 0000       |

| 5440                        |                  | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | -    | 0000       |

| FA10                        | INT4R            | 15:0      | -     | _     | _     | _     | —     | —     | _    | _    | _    | _    | _    | _    |      | INT4F | R<3:0> |      | 0000       |

| 5440                        | TAOKA            | 31:16     | _     | _     | _     | _     | —     | —     | _    | _    | _    | _    | _    | _    | _    | _     | _      | —    | 0000       |

| FA18                        | T2CKR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T2CK  | R<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    |      | _    | _    |       | _      | _    | 0000       |

| FA1C                        | T3CKR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    |      | _    |      | T3CK  | R<3:0> | •    | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    |      | _    | _    |       | _      | _    | 0000       |

| FA20                        | T4CKR            | 15:0      |       |       | _     |       | _     | _     | _    | _    | _    |      |      | _    |      | T4CK  | R<3:0> | •    | 0000       |

|                             |                  | 31:16     | _     |       | _     |       | _     | _     | _    | _    | _    |      |      | _    | _    |       | _      | _    | 0000       |

| FA24                        | T5CKR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T5CK  | R<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |       | —      | _    | 0000       |

| FA28                        | IC1R             | 15:0      | _     | _     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    |      | IC1R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      | _    | _     | _      | _    | 0000       |

| FA2C                        | IC2R             | 15:0      | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      |      | IC2R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FA30                        | IC3R             | 15:0      | _     | _     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    |      | IC3R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      | _    | _     | _      | _    | 0000       |

| FA34                        | IC4R             | 15:0      | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      |      | IC4R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      | _    | _     | _      | _    | 0000       |

| FA38                        | IC5R             | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | IC5R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     | _     |       |       | _     | _     |      | _    | _    | _    | _    | _    |      | _     |        | _    | 0000       |

| FA48                        | OCFAR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | OCFA  | R<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FA4C                        | OCFBR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | OCFB  | R<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FA50                        | U1RXR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U1RX  | R<3:0> |      | 0000       |

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

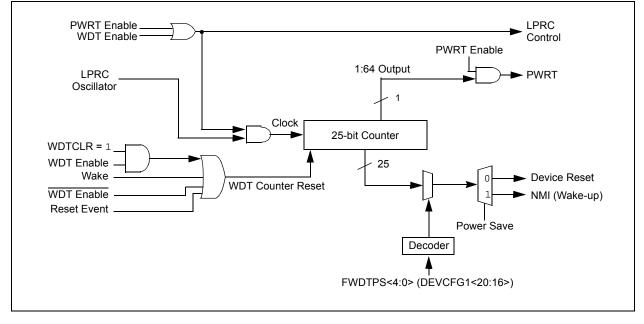

## 14.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114), which are available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32). The WDT, when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are some of the key features of the WDT module:

- · Configuration or software controlled

- User-configurable time-out period

- Can wake the device from Sleep or Idle mode

Figure 14-1 illustrates a block diagram of the WDT and Power-up timer.

## FIGURE 14-1: WATCHDOG TIMER AND POWER-UP TIMER BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | —                 | _                    | _                 | -                 | —                | —                |

| 00.10        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | —                 | _                    | _                 |                   | —                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL              | _                    | _                 | _                 | —                | _                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | —                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

## REGISTER 16-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Peripheral On bit<sup>(1)</sup>

- 1 = Output Compare peripheral is enabled

- 0 = Output Compare peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

#### bit 12-6 Unimplemented: Read as '0'

- bit 5 OC32: 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 OCFLT: PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (cleared in hardware only)

- 0 = No PWM Fault condition has occurred

- bit 3 **OCTSEL:** Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin enabled

- 110 = PWM mode on OCx; Fault pin disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

## **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

**2:** This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

## REGISTER 18-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER

|              |                   |                   |                   | 0                 |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | —                 | —                 | —                 | _                | _                |

| 22:40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |

| Legend:           | HC = Cleared in Hardwar | е                        |                    |

|-------------------|-------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** I<sup>2</sup>C Enable bit<sup>(1)</sup>

bit 12

- 1 = Enables the  $l^2C$  module and configures the SDA and SCL pins as serial port pins

- 0 = Disables the  $I^2$ C module; all  $I^2$ C pins are controlled by PORT functions

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

- **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

- 1 = Release SCLx clock

- 0 = Hold SCLx clock low (clock stretch)

#### If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception.

#### If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware clear at beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 = Strict I<sup>2</sup>C Reserved Address Rule not enabled

#### bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 DISSLW: Disable Slew Rate Control bit

- 1 = Slew rate control disabled

- 0 = Slew rate control enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        |                   | _                     | -                 | _                 | -                 | -                 | _                | _                |  |

| 23:16        | U-0               | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:10        | —                 | —                     |                   | _                 |                   | _                 | _                | _                |  |

|              | U-0               | R/W-0                 | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         |                   | CS1 <sup>(1)</sup>    |                   |                   |                   |                   |                  |                  |  |

|              | —                 | ADDR14 <sup>(2)</sup> | _                 | _                 | _                 |                   | ADDR<10:8>       |                  |  |

| 7:0          | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              | ADDR<7:0>         |                       |                   |                   |                   |                   |                  |                  |  |

#### REGISTER 20-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31-15 **Unimplemented:** Read as '0'

- bit 14 **CS1:** Chip Select 1 bit<sup>(1)</sup>

- 1 = Chip Select 1 is active

- 0 = Chip Select 1 is inactive

- bit 14 ADDR<14>: Destination Address bit 14<sup>(2)</sup>

- bit 13-11 Unimplemented: Read as '0'

- bit 10-0 ADDR<10:0>: Destination Address bits

- Note 1: When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | CH0NB             | _                 | _                 | —                 | CH0SB<3:0>        |                   |                  |                  |  |

| 00.40        | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | CH0NA             | _                 | _                 | —                 |                   | CH0SA             | <3:0>            |                  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         |                   | _                 | _                 | —                 | _                 | —                 | —                | —                |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 7:0          | —                 |                   |                   | —                 | _                 | _                 | _                | _                |  |

## REGISTER 22-4: AD1CHS: ADC INPUT SELECT REGISTER

CHONB: Negative Input Select bit for Sample B

## Legend:

bit 31

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

|        |                      | <ul> <li>1 = Channel 0 negative input is AN1</li> <li>0 = Channel 0 negative input is VREFL</li> </ul>                                                                                                                                                                                                                                          |

|--------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30 | -28                  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                      |

| bit 27 | -24                  | CH0SB<3:0>: Positive Input Select bits for Sample B                                                                                                                                                                                                                                                                                             |

|        |                      | <pre>1111 = Channel 0 positive input is Open<sup>(1)</sup> 1110 = Channel 0 positive input is IVREF<sup>(2)</sup> 1101 = Channel 0 positive input is CTMU temperature sensor (CTMUT)<sup>(3)</sup> 1100 = Channel 0 positive input is AN12<sup>(4)</sup></pre>                                                                                  |

|        |                      | •                                                                                                                                                                                                                                                                                                                                               |

|        |                      | •                                                                                                                                                                                                                                                                                                                                               |

|        |                      | •                                                                                                                                                                                                                                                                                                                                               |

|        |                      | 0001 = Channel 0 positive input is AN1<br>0000 = Channel 0 positive input is AN0                                                                                                                                                                                                                                                                |

| bit 23 |                      | CH0NA: Negative Input Select bit for Sample A Multiplexer Setting <sup>(2)</sup>                                                                                                                                                                                                                                                                |

|        |                      | <ul><li>1 = Channel 0 negative input is AN1</li><li>0 = Channel 0 negative input is VREFL</li></ul>                                                                                                                                                                                                                                             |

| bit 22 | -20                  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                      |

| bit 19 | -16                  | CH0SA<3:0>: Positive Input Select bits for Sample A Multiplexer Setting<br>1111 = Channel 0 positive input is Open <sup>(1)</sup><br>1110 = Channel 0 positive input is IVREF <sup>(2)</sup><br>1101 = Channel 0 positive input is CTMU temperature (CTMUT) <sup>(3)</sup><br>1100 = Channel 0 positive input is AN12 <sup>(4)</sup>            |

|        |                      | •                                                                                                                                                                                                                                                                                                                                               |

|        |                      | •                                                                                                                                                                                                                                                                                                                                               |

|        |                      | •                                                                                                                                                                                                                                                                                                                                               |

|        |                      | 0001 = Channel 0 positive input is AN1<br>0000 = Channel 0 positive input is AN0                                                                                                                                                                                                                                                                |

| bit 15 | -0                   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                      |

| Note   | 1:<br>2:<br>3:<br>4: | This selection is only used with CTMU capacitive and time measurement.<br>See <b>Section 24.0 "Comparator Voltage Reference (CVREF)"</b> for more information.<br>See <b>Section 25.0 "Charge Time Measurement Unit (CTMU)"</b> for more information.<br>AN12 is only available on 44-pin devices. AN6-AN8 are not available on 28-pin devices. |

|        |                      |                                                                                                                                                                                                                                                                                                                                                 |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 51.24        | _                 | —                 |                   | —                 | _                 |                   | -                | —                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | _                 | —                 |                   | —                 | _                 | _                 | _                | —                |  |

| 15:8         | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.6         | -                 | —                 | SIDL              | —                 | _                 | _                 |                  | —                |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |  |

| 7.0          |                   |                   |                   |                   | _                 | C3OUT             | C2OUT            | C10UT            |  |

## REGISTER 23-2: CMSTAT: COMPARATOR STATUS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-14 Unimplemented: Read as '0'

#### bit 13 SIDL: Stop in Idle Control bit

1 = All Comparator modules are disabled when the device enters Idle mode

0 = All Comparator modules continue to operate when the device enters Idle mode

#### bit 12-3 Unimplemented: Read as '0'

#### bit 2 C3OUT: Comparator Output bit

- 1 = Output of Comparator 3 is a '1'

- 0 = Output of Comparator 3 is a '0'

#### bit 1 C2OUT: Comparator Output bit

- 1 = Output of Comparator 2 is a '1'

- 0 = Output of Comparator 2 is a '0'

#### bit 0 **C1OUT:** Comparator Output bit

- 1 = Output of Comparator 1 is a '1'

- 0 = Output of Comparator 1 is a '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 | _                 | —                 | _                 |                   | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | CVROE             | CVRR              | CVRSS             |                   | CVR<              | <3:0>            |                  |

## **REGISTER 24-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER**

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator Voltage Reference On bit<sup>(1)</sup>

- 1 = Module is enabled

- Setting this bit does not affect other bits in the register.

- 0 = Module is disabled and does not consume current.

- Clearing this bit does not affect the other bits in the register.

- bit 14-7 Unimplemented: Read as '0'

- bit 6 **CVROE:** CVREFOUT Enable bit

- 1 = Voltage level is output on CVREFOUT pin

- 0 = Voltage level is disconnected from CVREFOUT pin

- bit 5 CVRR: CVREF Range Selection bit

- 1 = 0 to 0.67 CVRSRC, with CVRSRC/24 step size

- 0 = 0.25 CVRSRC to 0.75 CVRSRC, with CVRSRC/32 step size

- bit 4 **CVRSS:** CVREF Source Selection bit

- 1 = Comparator voltage reference source, CVRSRC = (VREF+) (VREF-)

- 0 = Comparator voltage reference source, CVRSRC = AVDD AVSS

- bit 3-0 **CVR<3:0>:** CVREF Value Selection  $0 \le CVR<3:0> \le 15$  bits

<u>When CVRR = 1:</u> CVREF = (CVR<3:0>/24) • (CVRSRC) <u>When CVRR = 0:</u> CVREF = 1/4 • (CVRSRC) + (CVR<3:0>/32) • (CVRSRC)

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED) bit 24 EDG1STAT: Edge1 Status bit Indicates the status of Edge1 and can be written to control edge source 1 = Edge1 has occurred 0 = Edge1 has not occurred EDG2MOD: Edge2 Edge Sampling Select bit bit 23 1 = Input is edge-sensitive 0 = Input is level-sensitive bit 22 EDG2POL: Edge 2 Polarity Select bit 1 = Edge2 programmed for a positive edge response 0 = Edge2 programmed for a negative edge response bit 21-18 EDG2SEL<3:0>: Edge 2 Source Select bits 1111 = C3OUT pin is selected 1110 = C2OUT pin is selected 1101 = C1OUT pin is selected 1100 = PBCLK clock is selected 1011 = IC3 Capture Event is selected 1010 = IC2 Capture Event is selected 1001 = IC1 Capture Event is selected 1000 = CTED13 pin is selected 0111 = CTED12 pin is selected 0110 = CTED11 pin is selected 0101 = CTED10 pin is selected 0100 = CTED9 pin is selected 0011 = CTED1 pin is selected 0010 = CTED2 pin is selected 0001 = OC1 Compare Event is selected 0000 = Timer1 Event is selected bit 17-16 Unimplemented: Read as '0' bit 15 **ON:** ON Enable bit 1 = Module is enabled 0 = Module is disabled bit 14 Unimplemented: Read as '0' bit 13 CTMUSIDL: Stop in Idle Mode bit 1 = Discontinue module operation when the device enters Idle mode 0 = Continue module operation when the device enters Idle mode TGEN: Time Generation Enable bit<sup>(1)</sup> bit 12 1 = Enables edge delay generation 0 = Disables edge delay generation bit 11 EDGEN: Edge Enable bit 1 = Edges are not blocked 0 = Edges are blocked

- **Note 1:** When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 30-41) in Section 30.0 "Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |  |

|--------------|-----------------------------|-------------------|---------------------|-------------------|----------------------|-------------------|-----------------------|------------------|--|

| 04.04        | R                           | R                 | R                   | R                 | R                    | R                 | R                     | R                |  |

| 31:24        |                             | VER<              | 3:0> <sup>(1)</sup> |                   |                      | DEVID<            | 27:24> <sup>(1)</sup> |                  |  |

| 00.40        | R                           | R                 | R                   | R                 | R                    | R                 | R                     | R                |  |

| 23:16        | DEVID<23:16> <sup>(1)</sup> |                   |                     |                   |                      |                   |                       |                  |  |

| 45.0         | R                           | R                 | R                   | R                 | R                    | R                 | R                     | R                |  |

| 15:8         |                             |                   |                     | DEVID<            | 15:8> <sup>(1)</sup> |                   |                       |                  |  |

| 7.0          | R                           | R                 | R                   | R                 | R                    | R                 | R                     | R                |  |

| 7:0          |                             |                   |                     | DEVID             | <7:0>(1)             |                   |                       |                  |  |

## REGISTER 27-6: DEVID: DEVICE AND REVISION ID REGISTER

## Legend:

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 DEVID<27:0>: Device ID bits<sup>(1)</sup>

**Note 1:** See the "*PIC32 Flash Programming Specification*" (DS60001145) for a list of Revision and Device ID values.

| DC CHARACTERISTICS                 |        |                                                           | (unless | rd Opera<br>s otherwis | se stated | <b>d)</b><br>-40°C ≤ T | (see Note 4): 2.3V to 3.6V<br>$\overline{A} \le +85^{\circ}$ C for Industrial<br>$\overline{A} \le +105^{\circ}$ C for V-temp |

|------------------------------------|--------|-----------------------------------------------------------|---------|------------------------|-----------|------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No.SymbolCharacteristics |        |                                                           | Min.    | Typical                | Max.      | Units                  | Comments                                                                                                                      |

| D300                               | VIOFF  | Input Offset Voltage                                      | -       | ±7.5                   | ±25       | mV                     | AVDD = VDD,<br>AVSS = VSS                                                                                                     |

| D301                               | VICM   | Input Common Mode Voltage                                 | 0       | —                      | Vdd       | V                      | AVDD = VDD,<br>AVss = Vss<br>(Note 2)                                                                                         |

| D302                               | CMRR   | Common Mode Rejection Ratio                               | 55      | —                      | _         | dB                     | Max VICM = (VDD - 1)V<br>(Note 2)                                                                                             |

| D303A                              | Tresp  | Large Signal Response Time                                | _       | 150                    | 400       | ns                     | AVDD = VDD, AVSS = VSS<br>(Note 1,2)                                                                                          |

| D303B                              | TSRESP | Small Signal Response Time                                | -       | 1                      | _         | μS                     | This is defined as an input<br>step of 50 mV with 15 mV<br>of overdrive <b>(Note 2)</b>                                       |

| D304                               | ON2ov  | Comparator Enabled to Output<br>Valid                     | _       | _                      | 10        | μs                     | Comparator module is<br>configured before setting<br>the comparator ON bit<br>(Note 2)                                        |

| D305                               | IVREF  | Internal Voltage Reference                                | 1.14    | 1.2                    | 1.26      | V                      | _                                                                                                                             |

| D312                               | TSET   | Internal Comparator Voltage<br>DRC Reference Setting time | _       | —                      | 10        | μs                     | (Note 3)                                                                                                                      |

### TABLE 30-13: COMPARATOR SPECIFICATIONS

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

**2:** These parameters are characterized but not tested.

**3:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

**4:** The Comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

## TABLE 30-18: PLL CLOCK TIMING SPECIFICATIONS

| AC CHA        | RACTERI | STICS                                                               | (unless ot | d Operating Conditions: 2.3V to 3.6V<br>otherwise stated)<br>g temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |         |       |       |                                      |

|---------------|---------|---------------------------------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|--------------------------------------|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>                                      |            | Min.                                                                                                                                                                                   | Typical | Max.  | Units | Conditions                           |

| OS50          | Fplli   | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range |            | 3.92                                                                                                                                                                                   | _       | 5     | MHz   | ECPLL, HSPLL, XTPLL,<br>FRCPLL modes |

| OS51          | Fsys    | On-Chip VCO System<br>Frequency                                     |            | 60                                                                                                                                                                                     | —       | 120   | MHz   | _                                    |

| OS52          | TLOCK   | PLL Start-up Time (Lock Time)                                       |            | _                                                                                                                                                                                      | _       | 2     | ms    | —                                    |

| OS53          | DCLK    | CLKO Stability <sup>(2)</sup><br>(Period Jitter or Cumulative)      |            | -0.25                                                                                                                                                                                  | —       | +0.25 | %     | Measured over 100 ms<br>period       |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{SYSCLK}{CommunicationClock}}}$$

For example, if SYSCLK = 40 MHz and SPI bit rate = 20 MHz, the effective jitter is as follows:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{40}{20}}} = \frac{D_{CLK}}{1.41}$$

## TABLE 30-19: INTERNAL FRC ACCURACY

| АС СНА        | RACTERISTICS                                    | (unless         | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |            |  |  |  |

|---------------|-------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|--|

| Param.<br>No. | Characteristics                                 | Min.            | Typical                                                                                                                                                                                                                                                                              | Max. | Units | Conditions |  |  |  |

| Internal      | Internal FRC Accuracy @ 8.00 MHz <sup>(1)</sup> |                 |                                                                                                                                                                                                                                                                                      |      |       |            |  |  |  |

| F20b          | FRC                                             | -0.9 — +0.9 % — |                                                                                                                                                                                                                                                                                      |      |       |            |  |  |  |

Note 1: Frequency calibrated at 25°C and 3.3V. The TUN bits can be used to compensate for temperature drift.

#### TABLE 30-20: INTERNAL LPRC ACCURACY

| АС СНА        | RACTERISTICS                    | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |         |      |       |            |  |  |  |

|---------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|--|--|

| Param.<br>No. | Characteristics                 | Min.                                                                                                                                                                                                                                                                                   | Typical | Max. | Units | Conditions |  |  |  |

| LPRC @        | LPRC @ 31.25 kHz <sup>(1)</sup> |                                                                                                                                                                                                                                                                                        |         |      |       |            |  |  |  |

| F21           | LPRC                            | -15 — +15 % —                                                                                                                                                                                                                                                                          |         |      |       |            |  |  |  |

**Note 1:** Change of LPRC frequency as VDD changes.

NOTES:

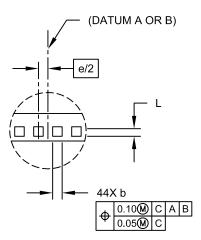

# 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL A

| Units                   |        | MILLIMETERS |      |       |

|-------------------------|--------|-------------|------|-------|

| Dimensior               | Limits | MIN         | NOM  | MAX   |

| Number of Pins          | N      | 44          |      |       |

| Number of Pins per Side | ND     | 12          |      |       |

| Number of Pins per Side | NE     | 10          |      |       |

| Pitch                   | е      | 0.50 BSC    |      |       |

| Overall Height          | A      | 0.80        | 0.90 | 1.00  |

| Standoff                | A1     | 0.025       | -    | 0.075 |

| Overall Width           | E      | 6.00 BSC    |      |       |

| Exposed Pad Width       | E2     | 4.40        | 4.55 | 4.70  |

| Overall Length          | D      | 6.00 BSC    |      |       |

| Exposed Pad Length      | D2     | 4.40        | 4.55 | 4.70  |

| Contact Width           | b      | 0.20        | 0.25 | 0.30  |

| Contact Length          | L      | 0.20        | 0.25 | 0.30  |

| Contact-to-Exposed Pad  | K      | 0.20        | -    | -     |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-157C Sheet 2 of 2