Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx170f256d-v-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 12: PIN NAMES FOR 44-PIN USB DEVICES

# 44-PIN TQFP (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX210F016D PIC32MX220F032D PIC32MX230F064D PIC32MX230F256D PIC32MX250F128D PIC32MX270F256D

44

1

| Pin # | Full Pin Name                                    | Pin # | Full Pin Name                             |

|-------|--------------------------------------------------|-------|-------------------------------------------|

| 1     |                                                  | 23    |                                           |

|       | RPB9/SDA1/CTED4/PMD3/RB9                         | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 2     | RPC6/PMA1/RC6                                    |       | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 3     | RPC7/PMA0/RC7                                    | 25    | AN6/RPC0/RC0                              |

| 4     | RPC8/PMA5/RC8                                    | 26    | AN7/RPC1/RC1                              |

| 5     | RPC9/CTED7/PMA6/RC9                              | 27    | AN8/RPC2/PMA2/RC2                         |

| 6     | Vss                                              | 28    | VDD                                       |

| 7     | VCAP                                             | 29    | Vss                                       |

| 8     | PGED2/RPB10/D+/CTED11/RB10                       | 30    | OSC1/CLKI/RPA2/RA2                        |

| 9     | PGEC2/RPB11/D-/RB11                              | 31    | OSC2/CLKO/RPA3/RA3                        |

| 10    | VUSB3V3                                          | 32    | TDO/RPA8/PMA8/RA8                         |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                       | 33    | SOSCI/RPB4/RB4                            |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10             | 34    | SOSCO/RPA4/T1CK/CTED9/RA4                 |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7         | 35    | TDI/RPA9/PMA9/RA9                         |

| 14    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 | 36    | AN12/RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            | 37    | RPC4/PMA4/RC4                             |

| 16    | AVss                                             | 38    | RPC5/PMA3/RC5                             |

| 17    | AVDD                                             | 39    | Vss                                       |

| 18    | MCLR                                             | 40    | Vdd                                       |

| 19    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 | 41    | RPB5/USBID/RB5                            |

| 20    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       | 42    | VBUS                                      |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        | 43    | RPB7/CTED3/PMD5/INT0/RB7                  |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       | 44    | RPB8/SCL1/CTED10/PMD4/RB8                 |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX210F016D and PIC32MX220F032D devices.

5: Shaded pins are 5V tolerant.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 31:24        | BMXDRMSZ<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 23:16        | BMXDRMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 15:8         | BMXDRMSZ<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

|              |                   |                   |                   | BMXDR             | MSZ<7:0>          |                   |                  |                  |  |  |  |

#### **BMXDRMSZ: DATA RAM SIZE REGISTER REGISTER 4-5:**

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 BMXDRMSZ<31:0>: Data RAM Memory (DRM) Size bits

Static value that indicates the size of the Data RAM in bytes: 0x00001000 = Device has 4 KB RAM 0x00002000 = Device has 8 KB RAM 0x00004000 = Device has 16 KB RAM 0x00008000 = Device has 32 KB RAM 0x00010000 = Device has 64 KB RAM

### **REGISTER 4-6: BMXPUPBA: PROGRAM FLASH (PFM) USER PROGRAM BASE ADDRESS** REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | _                 | —                 | —                 | _                 | _                 | —                 | —                | —                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | _                 | _                 | _                 | _                 | BMXPUPBA<19:16>   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8         | BMXPUPBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          |                   | BMXPUPBA<7:0>     |                   |                   |                   |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-20 Unimplemented: Read as '0'

bit 19-11 BMXPUPBA<19:11>: Program Flash (PFM) User Program Base Address bits

# bit 10-0 BMXPUPBA<10:0>: Read-Only bits This value is always '0', which forces 2 KB increments

Note 1: At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXPFMSZ.

# 8.1 Oscillator Control Regiters

| TABLE 8-1: OSCILLATOR CONTROL REGISTER MAP |                                 |           |       |              |          |       |           |       |                     |        |         |                      |       |        |      |                       |        |                     |           |

|--------------------------------------------|---------------------------------|-----------|-------|--------------|----------|-------|-----------|-------|---------------------|--------|---------|----------------------|-------|--------|------|-----------------------|--------|---------------------|-----------|

| ess                                        |                                 | Bits      |       |              |          |       |           |       |                     |        |         |                      |       | ú      |      |                       |        |                     |           |

| Virtual Address<br>(BF80_#)                | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14        | 29/13    | 28/12 | 27/11     | 26/10 | 25/9                | 24/8   | 23/7    | 22/6                 | 21/5  | 20/4   | 19/3 | 18/2                  | 17/1   | 16/0                | All Reset |

| F000                                       | OSCCON                          | 31:16     | —     | PLLODIV<2:0> |          |       |           | F     | FRCDIV<2:0> — SOSCR |        | SOSCRDY | PBDIVRDY             | PBDI\ | /<1:0> | PL   | LMULT<2:0             | >      | x1xx <sup>(2)</sup> |           |

| FUUU                                       | 030001                          | 15:0      | —     |              | COSC<2:0 | V     | Ι         |       | NOSC<2:0            | >      | CLKLOCK | ULOCK <sup>(3)</sup> | SLOCK | SLPEN  | CF   | UFRCEN <sup>(3)</sup> | SOSCEN | OSWEN               | xxxx(2)   |

| F010                                       | OSCTUN                          | 31:16     | _     | _            |          | _     | _         |       |                     | _      | _       | _                    | _     | _      |      | _                     | —      | _                   | 0000      |

| 1010                                       | 030101                          | 15:0      | _     | _            |          | _     | _         |       |                     | _      | _       | _                    |       |        | TUN  | l<5:0>                |        |                     | 0000      |

| 5000                                       |                                 | 31:16     | _     |              |          |       |           |       |                     |        | RODIV<1 | 4:0>                 |       |        |      |                       |        |                     | 0000      |

| F020                                       | REFOCON                         | 15:0      | ON    |              | SIDL     | OE    | RSLP      | -     | DIVSWEN             | ACTIVE | —       | —                    |       |        |      | ROSE                  | _<3:0> |                     | 0000      |

| F000                                       | DEFOTDIM                        | 31:16     |       |              |          | R     | OTRIM<8:0 | )>    |                     |        |         | _                    | _     | _      | _    | _                     | _      | _                   | 0000      |

| F030                                       | REFOTRIM                        | 15:0      | _     | _            |          | _     | _         |       |                     | -      | _       | _                    | _     | _      |      | _                     | —      | _                   | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

3: This bit is only available on PIC32MX2XX devices.

| REGIST       | REGISTER 10-1. UTUTGIR. USB UTG INTERROFT STATUS REGISTER |                   |                   |                   |                   |                   |                  |                  |  |

|--------------|-----------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7                                         | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 31:24        | U-0                                                       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | -                                                         | —                 | —                 | -                 | -                 | —                 | -                | —                |  |

| 23:16        | U-0                                                       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | -                                                         | —                 | —                 | -                 | -                 | —                 | -                | —                |  |

| 15:8         | U-0                                                       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.6         |                                                           | _                 | -                 |                   |                   | —                 |                  | —                |  |

| 7.0          | R/WC-0, HS                                                | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS        | U-0              | R/WC-0, HS       |  |

| 7:0          | IDIF                                                      | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF           | SESENDIF          |                  | VBUSVDIF         |  |

# REGISTER 10-1: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable b  | pit                |

|-------------------|-------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIF:** ID State Change Indicator bit

- 1 = A change in the ID state was detected

- 0 = No change in the ID state was detected

- bit 6 T1MSECIF: 1 Millisecond Timer bit

- 1 = 1 millisecond timer has expired

- 0 = 1 millisecond timer has not expired

# bit 5 LSTATEIF: Line State Stable Indicator bit

- 1 = USB line state has been stable for 1 ms, but different from last time

- 0 = USB line state has not been stable for 1 ms

- bit 4 ACTVIF: Bus Activity Indicator bit

- 1 = Activity on the D+, D-, ID or VBUS pins has caused the device to wake-up

- 0 = Activity has not been detected

- bit 3 SESVDIF: Session Valid Change Indicator bit

- 1 = VBUS voltage has dropped below the session end level

- 0 = VBUS voltage has not dropped below the session end level

- bit 2 SESENDIF: B-Device VBUS Change Indicator bit

- 1 = A change on the session end input was detected

- 0 = No change on the session end input was detected

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIF: A-Device VBUS Change Indicator bit

- 1 = A change on the session valid input was detected

- 0 = No change on the session valid input was detected

# REGISTER 10-7: U1IE: USB INTERRUPT ENABLE REGISTER

|              |                   | •                 |                   |                   |                   |                   |                       |                                                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|--------------------------------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0                                 |

| 31:24        | U-0                   | U-0                                              |

| 51.24        | —                 | —                 | —                 | —                 | —                 | —                 | —                     | —                                                |

| 23:16        | U-0                   | U-0                                              |

| 23.10        | -                 | —                 | —                 | —                 | —                 | —                 | —                     | —                                                |

| 15:8         | U-0                   | U-0                                              |

| 15.0         | _                 | —                 | _                 | _                 | —                 | _                 | _                     | —                                                |

|              | R/W-0                 | R/W-0                                            |

| 7:0          | STALLIE           | ATTACHIE          | RESUMEIE          | IDLEIE            | TRNIE             | SOFIE             | UERRIE <sup>(1)</sup> | URSTIE <sup>(2)</sup><br>DETACHIE <sup>(3)</sup> |

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-8 Unimplemented: Read as '0'

| bit 7 | STALLIE: STALL Handshake Interrupt Enable bit |

|-------|-----------------------------------------------|

|       |                                               |

- 1 = STALL interrupt is enabled

- 0 = STALL interrupt is disabled

- bit 6 ATTACHIE: ATTACH Interrupt Enable bit

- 1 = ATTACH interrupt is enabled 0 = ATTACH interrupt is disabled

- bit 5 **RESUMEIE:** RESUME Interrupt Enable bit

- 1 = RESUME interrupt is enabled

- 0 = RESUME interrupt is disabled

- bit 4 IDLEIE: Idle Detect Interrupt Enable bit

- 1 = Idle interrupt is enabled

- 0 = Idle interrupt is disabled

- bit 3 TRNIE: Token Processing Complete Interrupt Enable bit

- 1 = TRNIF interrupt is enabled

- 0 = TRNIF interrupt is disabled

- bit 2 SOFIE: SOF Token Interrupt Enable bit

- 1 = SOFIF interrupt is enabled

- 0 = SOFIF interrupt is disabled

- bit 1 UERRIE: USB Error Interrupt Enable bit<sup>(1)</sup>

- 1 = USB Error interrupt is enabled

- 0 = USB Error interrupt is disabled

- bit 0 URSTIE: USB Reset Interrupt Enable bit<sup>(2)</sup>

- 1 = URSTIF interrupt is enabled

- 0 = URSTIF interrupt is disabled

# DETACHIE: USB Detach Interrupt Enable bit<sup>(3)</sup>

- 1 = DATTCHIF interrupt is enabled

- 0 = DATTCHIF interrupt is disabled

**Note 1:** For an interrupt to propagate USBIF, the UERRIE (U1IE<1>) bit must be set.

- 2: Device mode.

- 3: Host mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        |                   | —                 |                   | —                 |                   |                   |                  | —                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        |                   | —                 |                   | —                 | -                 |                   |                  | —                |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.0         | -                 | —                 | -                 | —                 | _                 | -                 | —                | —                |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          | LSPDEN            | DEVADDR<6:0>      |                   |                   |                   |                   |                  |                  |  |  |

# REGISTER 10-12: U1ADDR: USB ADDRESS REGISTER

# Legend:

| U                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7 LSPDEN: Low-Speed Enable Indicator bit

1 = Next token command to be executed at Low-Speed

0 = Next token command to be executed at Full-Speed

bit 6-0 **DEVADDR<6:0>:** 7-bit USB Device Address bits

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | —                 | —                 | -                 | —                 | _                 | —                |                  |  |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | —                 | _                 | —                 | _                 | —                |                  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0         | —                 | —                 | —                 | -                 | —                 | _                 | —                | -                |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   | FRML<7:0>         |                   |                   |                   |                   |                  |                  |  |  |  |

# REGISTER 10-13: U1FRML: USB FRAME NUMBER LOW REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **FRML<7:0>:** The 11-bit Frame Number Lower bits

The register bits are updated with the current frame number whenever a SOF TOKEN is received.

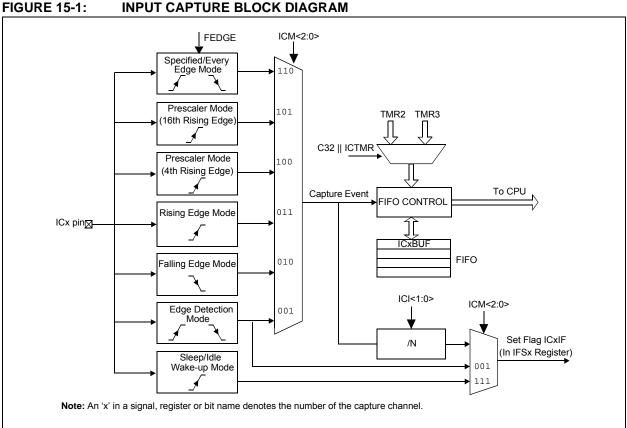

#### **INPUT CAPTURE** 15.0

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- · Simple capture event modes:

- Capture timer value on every rising and falling edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- · Device wake-up from capture pin during Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values (interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled)

- · Input capture can also be used to provide additional sources of external interrupts

Figure 15-1 illustrates a general block diagram of the Input Capture module.

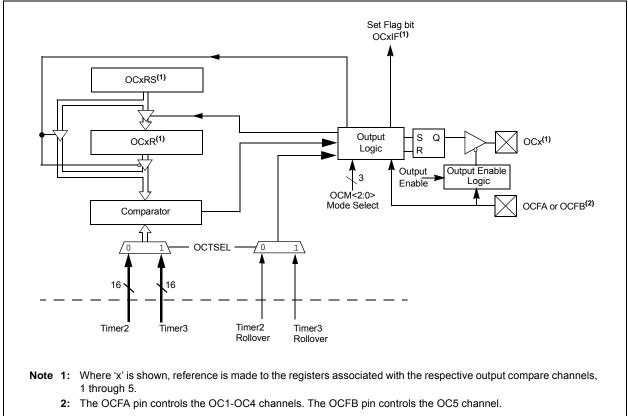

# 16.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 16. "Output Compare" (DS60001111), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Output Compare module is used to generate a single pulse or a train of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation. The following are some of the key features:

- · Multiple Output Compare Modules in a device

- Programmable interrupt generation on compare event

- Single and Dual Compare modes

- Single and continuous output pulse generation

- Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 31:24        |                   | _                 | RXBUFELM<4:0>     |                   |                   |                   |                  |                  |

| 22:16        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23:16        |                   | _                 | —                 | TXBUFELM<4:0>     |                   |                   |                  |                  |

| 45.0         | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |

| 15:8         |                   | —                 | _                 | FRMERR            | SPIBUSY           | —                 | —                | SPITUR           |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |

| 7:0          | SRMT              | SPIROV            | SPIRBE            | _                 | SPITBE            | —                 | SPITBF           | SPIRBF           |

# REGISTER 17-3: SPIxSTAT: SPI STATUS REGISTER

| Legend:           | C = Clearable bit | HS = Set in hardware     |                    |

|-------------------|-------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 15-13 Unimplemented: Read as '0'

- bit 12 **FRMERR:** SPI Frame Error status bit

- 1 = Frame error detected

- 0 = No Frame error detected

- This bit is only valid when FRMEN = 1.

- bit 11 SPIBUSY: SPI Activity Status bit

- 1 = SPI peripheral is currently busy with some transactions

- 0 = SPI peripheral is currently idle

- bit 10-9 Unimplemented: Read as '0'

- bit 8 SPITUR: Transmit Under Run bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or writing a '0' to SPITUR.

- bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 SPIROV: Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

This bit is set in hardware; can bit only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or by writing a '0' to SPIROV.

- bit 5 **SPIRBE:** RX FIFO Empty bit (valid only when ENHBUF = 1) 1 = RX FIFO is empty (CRPTR = SWPTR)

- 0 = RX FIFO is not empty (CRPTR  $\neq$  SWPTR)

- bit 4 Unimplemented: Read as '0'

# REGISTER 19-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | <ul> <li>ABAUD: Auto-Baud Enable bit</li> <li>1 = Enable baud rate measurement on the next character – requires reception of Sync character (0x55); cleared by hardware upon completion</li> <li>0 = Baud rate measurement disabled or completed</li> </ul> |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | RXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                           |

| bit 3   | BRGH: High Baud Rate Enable bit<br>1 = High-Speed mode – 4x baud clock enabled<br>0 = Standard Speed mode – 16x baud clock enabled                                                                                                                          |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits<br>11 = 9-bit data, no parity<br>10 = 8-bit data, odd parity<br>01 = 8-bit data, even parity<br>00 = 8-bit data, no parity                                                                                       |

| bit 0   | <b>STSEL:</b> Stop Selection bit<br>1 = 2 Stop bits<br>0 = 1 Stop bit                                                                                                                                                                                       |

**Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   |                   | _                 | _                 | _                 | -                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | _                 | _                 | -                 | -                 | _                 | _                | —                |

| 45.0         | R-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 15:8         | BUSY              | IRQM              | <1:0>             | INCM              | <1:0>             | _                 | MODE             | <1:0>            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | WAITB             | <1:0> <b>(1)</b>  |                   | WAITM<3:0>(1)     |                   |                   | WAITE            | <1:0>(1)         |

# REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER

# Legend:

| 0                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-16 Unimplemented: Read as '0'

- bit 15 **BUSY:** Busy bit (Master mode only)

- 1 = Port is busy

- 0 = Port is not busy

# bit 14-13 IRQM<1:0>: Interrupt Request Mode bits

- 11 = Reserved, do not use

- 10 = Interrupt generated when Read Buffer 3 is read or Write Buffer 3 is written (Buffered PSP mode) or on a read or write operation when PMA<1:0> =11 (Addressable Slave mode only)

- 01 = Interrupt generated at the end of the read/write cycle

- 00 = No Interrupt generated

## bit 12-11 INCM<1:0>: Increment Mode bits

- 11 = Slave mode read and write buffers auto-increment (MODE<1:0> = 00 only)

- 10 = Decrement ADDR<10:2> and ADDR<14> by 1 every read/write cycle<sup>(2)</sup>

- 01 = Increment ADDR<10:2> and ADDR<14> by 1 every read/write cycle<sup>(2)</sup>

- 00 = No increment or decrement of address

- bit 10 Unimplemented: Read as '0'

- bit 9-8 MODE<1:0>: Parallel Port Mode Select bits

- 11 = Master mode 1 (PMCS1, PMRD/PMWR, PMENB, PMA<x:0>, and PMD<7:0>)

- 10 = Master mode 2 (PMCS1, PMRD, PMWR, PMA<x:0>, and PMD<7:0>)

- 01 = Enhanced Slave mode, control signals (PMRD, PMWR, PMCS1, PMD<7:0>, and PMA<1:0>)

- 00 = Legacy Parallel Slave Port, control signals (PMRD, PMWR, PMCS1, and PMD<7:0>)

- bit 7-6 WAITB<1:0>: Data Setup to Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Data wait of 4 TPB; multiplexed address phase of 4 TPB

- 10 = Data wait of 3 TPB; multiplexed address phase of 3 TPB

- 01 = Data wait of 2 TPB; multiplexed address phase of 2 TPB

- 00 = Data wait of 1 TPB; multiplexed address phase of 1 TPB (default)

# bit 5-2 WAITM<3:0>: Data Read/Write Strobe Wait States bits<sup>(1)</sup>

- 1111 = Wait of 16 Трв •

- . 0001 = Wait of 2 Трв 0000 = Wait of 1 Трв (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bit A14 is not subject to auto-increment/decrement if configured as Chip Select CS1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 | —                 | —                 | _                 |                   | —                | _                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | —                 | _                 | —                 | —                 | —                | _                |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | CSSL15            | CSSL14            | CSSL13            | CSSL12            | CSSL11            | CSSL10            | CSSL9            | CSSL8            |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | CSSL7             | CSSL6             | CSSL5             | CSSL4             | CSSL3             | CSSL2             | CSSL1            | CSSL0            |  |

# REGISTER 22-5: AD1CSSL: ADC INPUT SCAN SELECT REGISTER

# Legend:

| Logena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CSSL<15:0>: ADC Input Pin Scan Selection bits<sup>(1,2)</sup>

1 = Select ANx for input scan

0 = Skip ANx for input scan

- **Note 1:** CSSL = ANx, where 'x' = 0-12; CSSL13 selects CTMU input for scan; CSSL14 selects IVREF for scan; CSSL15 selects Vss for scan.

- 2: On devices with less than 13 analog inputs, all CSSLx bits can be selected; however, inputs selected for scan without a corresponding input on the device will convert to VREFL.

# **30.1 DC Characteristics**

# TABLE 30-1: OPERATING MIPS VS. VOLTAGE

| Characteristic | VDD Range                 | Temp. Range     | Max. Frequency                     |

|----------------|---------------------------|-----------------|------------------------------------|

| Gharacteristic | (in Volts) <sup>(1)</sup> | (in °C)         | PIC32MX1XX/2XX 28/36/44-pin Family |

| DC5            | 2.3-3.6V                  | -40°C to +85°C  | 40 MHz                             |

| DC5b           | 2.3-3.6V                  | -40°C to +105°C | 40 MHz                             |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 30-11 for BOR values.

# TABLE 30-2: THERMAL OPERATING CONDITIONS

| Rating                                                                               | Symbol | Min.           | Typical     | Max. | Unit |

|--------------------------------------------------------------------------------------|--------|----------------|-------------|------|------|

| Industrial Temperature Devices                                                       |        |                |             |      |      |

| Operating Junction Temperature Range                                                 | TJ     | -40            | —           | +125 | °C   |

| Operating Ambient Temperature Range                                                  | TA     | -40            | —           | +85  | °C   |

| V-temp Temperature Devices                                                           |        |                |             |      |      |

| Operating Junction Temperature Range                                                 | TJ     | -40            | —           | +140 | °C   |

| Operating Ambient Temperature Range                                                  | TA     | -40            | —           | +105 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>PINT = VDD x (IDD – S IOH) | PD     | PD PINT + PI/O |             |      | w    |

| I/O Pin Power Dissipation:<br>I/O = S (({VDD – VOH} x IOH) + S (VOL x IOL))          |        |                |             |      |      |

| Maximum Allowed Power Dissipation                                                    | Pdmax  | (              | Tj — Ta)/θJ | A    | W    |

# TABLE 30-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristics                          | Symbol | Typical | Max. | Unit | Notes |

|------------------------------------------|--------|---------|------|------|-------|

| Package Thermal Resistance, 28-pin SSOP  | θJA    | 71      | _    | °C/W | 1     |

| Package Thermal Resistance, 28-pin SOIC  | θJA    | 50      | —    | °C/W | 1     |

| Package Thermal Resistance, 28-pin SPDIP | θJA    | 42      | _    | °C/W | 1     |

| Package Thermal Resistance, 28-pin QFN   | θJA    | 35      | —    | °C/W | 1     |

| Package Thermal Resistance, 36-pin VTLA  | θJA    | 31      | —    | °C/W | 1     |

| Package Thermal Resistance, 44-pin QFN   | θJA    | 32      | _    | °C/W | 1     |

| Package Thermal Resistance, 44-pin TQFP  | θJA    | 45      |      | °C/W | 1     |

| Package Thermal Resistance, 44-pin VTLA  | θJA    | 30      | _    | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

| DC CHA        |                        | STICS                                                     | (unless                     | rd Opera<br>s otherwis | se stated | <b>d)</b><br>-40°C ≤ T | (see Note 4): 2.3V to 3.6V<br>$\overline{A} \le +85^{\circ}$ C for Industrial<br>$\overline{A} \le +105^{\circ}$ C for V-temp |          |  |

|---------------|------------------------|-----------------------------------------------------------|-----------------------------|------------------------|-----------|------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------|--|

| Param.<br>No. | Symbol Characteristics |                                                           | Symbol Characteristics Min. |                        | Typical   | Max.                   | Units                                                                                                                         | Comments |  |

| D300          | VIOFF                  | Input Offset Voltage                                      | -                           | ±7.5                   | ±25       | mV                     | AVDD = VDD,<br>AVSS = VSS                                                                                                     |          |  |

| D301          | VICM                   | Input Common Mode Voltage                                 | 0                           | -                      | Vdd       | V                      | AVDD = VDD,<br>AVss = Vss<br>(Note 2)                                                                                         |          |  |

| D302          | CMRR                   | Common Mode Rejection Ratio                               | 55                          | —                      | _         | dB                     | Max VICM = (VDD - 1)V<br>(Note 2)                                                                                             |          |  |

| D303A         | TRESP                  | Large Signal Response Time                                | _                           | 150                    | 400       | ns                     | AVDD = VDD, AVSS = VSS<br>(Note 1,2)                                                                                          |          |  |

| D303B         | TSRESP                 | Small Signal Response Time                                | -                           | 1                      | _         | μS                     | This is defined as an input<br>step of 50 mV with 15 mV<br>of overdrive <b>(Note 2)</b>                                       |          |  |

| D304          | ON2ov                  | Comparator Enabled to Output<br>Valid                     | _                           | _                      | 10        | μs                     | Comparator module is<br>configured before setting<br>the comparator ON bit<br>(Note 2)                                        |          |  |

| D305          | IVREF                  | Internal Voltage Reference                                | 1.14                        | 1.2                    | 1.26      | V                      | —                                                                                                                             |          |  |

| D312          | TSET                   | Internal Comparator Voltage<br>DRC Reference Setting time | —                           | —                      | 10        | μs                     | (Note 3)                                                                                                                      |          |  |

# TABLE 30-13: COMPARATOR SPECIFICATIONS

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

**2:** These parameters are characterized but not tested.

**3:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

**4:** The Comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

### FIGURE 30-10: SPIx MODULE MASTER MODE (CKE = 0) TIMING CHARACTERISTICS SCKx (CKP = 0) SP11 SP10 SP21 SP20 SCKx (CKP = 1) SP35 SP20 SP21 SDOx MSb Bit 14 -1 LSb **SP31** SP30 SDIx LSb In MSb In Bit 14 SP40 'SP41' Note: Refer to Figure 30-1 for load conditions.

# TABLE 30-28: SPIx MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHA        | RACTERIST             | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |        |                        |      |       |                    |

|---------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------|------|-------|--------------------|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                                                                                                                                                                                                                                                      | Min.   | Typical <sup>(2)</sup> | Max. | Units | Conditions         |

| SP10          | TscL                  | SCKx Output Low Time<br>(Note 3)                                                                                                                                                                                                                                                    | Тѕск/2 | _                      |      | ns    | _                  |

| SP11          | TscH                  | SCKx Output High Time<br>(Note 3)                                                                                                                                                                                                                                                   | Тѕск/2 | —                      | _    | ns    | _                  |

| SP20          | TscF                  | SCKx Output Fall Time (Note 4)                                                                                                                                                                                                                                                      | —      | —                      |      | ns    | See parameter DO32 |

| SP21          | TscR                  | SCKx Output Rise Time<br>(Note 4)                                                                                                                                                                                                                                                   | —      | —                      | _    | ns    | See parameter DO31 |

| SP30          | TDOF                  | SDOx Data Output Fall Time (Note 4)                                                                                                                                                                                                                                                 | —      | —                      | _    | ns    | See parameter DO32 |

| SP31          | TDOR                  | SDOx Data Output Rise Time (Note 4)                                                                                                                                                                                                                                                 | —      | _                      | _    | ns    | See parameter DO31 |

| SP35          | TscH2doV,             | SDOx Data Output Valid after                                                                                                                                                                                                                                                        | —      | —                      | 15   | ns    | VDD > 2.7V         |

|               | TscL2doV              | SCKx Edge                                                                                                                                                                                                                                                                           |        | _                      | 20   | ns    | VDD < 2.7V         |

| SP40          | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                                                                                                                                                          | 10     | —                      | —    | ns    | —                  |

| SP41          | TSCH2DIL,<br>TSCL2DIL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                                                                                                                                                           | 10     | —                      |      | ns    |                    |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 50 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

# TABLE 30-33: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE) (CONTINUED)

| AC CHA        | RACTERIS | STICS             |                               |      |      |       | ons: 2.3V to 3.6V<br>$^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |

|---------------|----------|-------------------|-------------------------------|------|------|-------|----------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No. | Symbol   | Charact           | eristics                      | Min. | Max. | Units | Conditions                                                                                                                 |

| IS34          | THD:STO  | Stop Condition    | 100 kHz mode                  | 4000 | _    | ns    | —                                                                                                                          |

|               |          | Hold Time         | 400 kHz mode                  | 600  | —    | ns    |                                                                                                                            |

|               |          |                   | 1 MHz mode<br>(Note 1)        | 250  |      | ns    |                                                                                                                            |

| IS40          | TAA:SCL  | Output Valid from | 100 kHz mode                  | 0    | 3500 | ns    | —                                                                                                                          |

|               |          | Clock             | 400 kHz mode                  | 0    | 1000 | ns    |                                                                                                                            |

|               |          |                   | 1 MHz mode<br><b>(Note 1)</b> | 0    | 350  | ns    |                                                                                                                            |

| IS45          | TBF:SDA  | Bus Free Time     | 100 kHz mode                  | 4.7  | —    | μs    | The amount of time the bus                                                                                                 |

|               |          |                   | 400 kHz mode                  | 1.3  |      | μS    | must be free before a new                                                                                                  |

|               |          |                   | 1 MHz mode<br>(Note 1)        | 0.5  | -    | μS    | transmission can start                                                                                                     |

| IS50          | Св       | Bus Capacitive Lo | ading                         | _    | 400  | pF    | —                                                                                                                          |

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

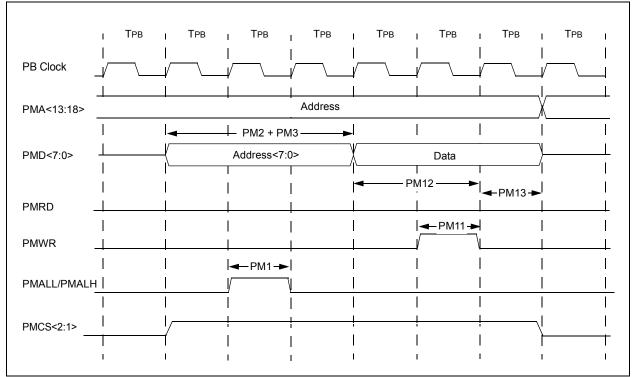

| AC CHARACTERISTICS |         |                                                                      | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |       |      |       |            |

|--------------------|---------|----------------------------------------------------------------------|-------------------------------------------------------|-------|------|-------|------------|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                       | Min.                                                  | Тур.  | Max. | Units | Conditions |

| PM1                | Tlat    | PMALL/PMALH Pulse Width                                              |                                                       | 1 Трв | _    | _     | _          |

| PM2                | TADSU   | Address Out Valid to<br>PMALL/PMALH Invalid (address<br>setup time)  | _                                                     | 2 Трв | _    | _     | _          |

| PM3                | Tadhold | PMALL/PMALH Invalid to<br>Address Out Invalid (address<br>hold time) | —                                                     | 1 Трв | _    | —     | _          |

| PM4                | TAHOLD  | PMRD Inactive to Address Out<br>Invalid<br>(address hold time)       | 5                                                     | _     | _    | ns    | _          |

| PM5                | Trd     | PMRD Pulse Width                                                     | _                                                     | 1 Трв | _    | _     | —          |

| PM6                | TDSU    | PMRD or PMENB Active to Data<br>In Valid (data setup time)           | 15                                                    | —     | —    | ns    | _          |

| PM7                | TDHOLD  | PMRD or PMENB Inactive to Data In Invalid (data hold time)           | —                                                     | 80    | —    | ns    |            |

# TABLE 30-38: PARALLEL MASTER PORT READ TIMING REQUIREMENTS

Note 1: These parameters are characterized, but not tested in manufacturing.

# 31.1 DC Characteristics

# TABLE 31-1: OPERATING MIPS VS. VOLTAGE

| Characteristic | VDD Range                 | Temp. Range    | Max. Frequency                     |

|----------------|---------------------------|----------------|------------------------------------|

| Characteristic | (in Volts) <sup>(1)</sup> | (in °C)        | PIC32MX1XX/2XX 28/36/44-pin Family |

| MDC5           | 2.3-3.6V                  | -40°C to +85°C | 50 MHz                             |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 30-11 for BOR values.

# TABLE 31-2: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARA                            | CTERISTICS             | 5    | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |        |  |  |  |

|-------------------------------------|------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|--|

| Parameter<br>No.                    | Typical <sup>(3)</sup> | Max. | Units Conditions                                                                                                                                |        |  |  |  |

| Operating Current (IDD) (Note 1, 2) |                        |      |                                                                                                                                                 |        |  |  |  |

| MDC24                               | 25                     | 37   | mA                                                                                                                                              | 50 MHz |  |  |  |

**Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

- 2: The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, Program Flash, and SRAM data memory are operational, SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- CPU executing while(1) statement from Flash

- 3: RTCC and JTAG are disabled

- **4:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

# 28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

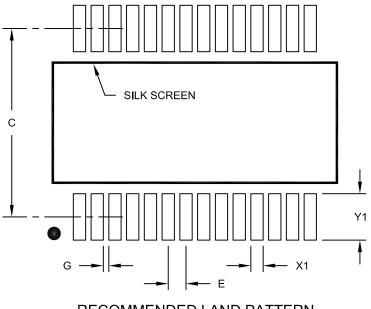

RECOMMENDED LAND PATTERN

|                          | Ν                | /ILLIMETER | S    |      |

|--------------------------|------------------|------------|------|------|

| Dimension                | Dimension Limits |            |      |      |

| Contact Pitch            | E                |            |      |      |

| Contact Pad Spacing      | С                |            | 7.20 |      |

| Contact Pad Width (X28)  | X1               |            |      | 0.45 |

| Contact Pad Length (X28) | Y1               |            |      | 1.75 |

| Distance Between Pads    | G                | 0.20       |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

# **Worldwide Sales and Service**

### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

# ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

# ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

# EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

**Poland - Warsaw** Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820