Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                   |                                                                                |

|--------------------------|--------------------------------------------------------------------------------|

| oduct Status             | Obsolete                                                                       |

| ore Processor            | MIPS32® M4K™                                                                   |

| ore Size                 | 32-Bit Single-Core                                                             |

| peed                     | 40MHz                                                                          |

| onnectivity              | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| eripherals               | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                |

| umber of I/O             | 35                                                                             |

| ogram Memory Size        | 256KB (256K x 8)                                                               |

| ogram Memory Type        | FLASH                                                                          |

| PROM Size                | -                                                                              |

| M Size                   | 64K x 8                                                                        |

| ltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| ta Converters            | A/D 13x10b                                                                     |

| cillator Type            | Internal                                                                       |

| erating Temperature      | -40°C ~ 105°C (TA)                                                             |

| ounting Type             | Surface Mount                                                                  |

| ckage / Case             | 44-VFTLA Exposed Pad                                                           |

| pplier Device Package    | 44-VTLA (6x6)                                                                  |

| rchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx170f256d-v-tl |

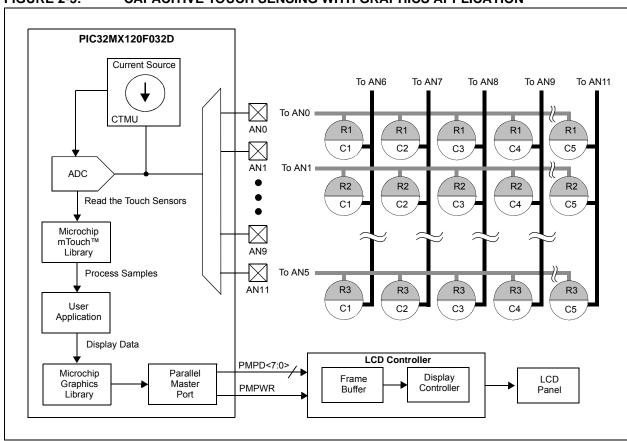

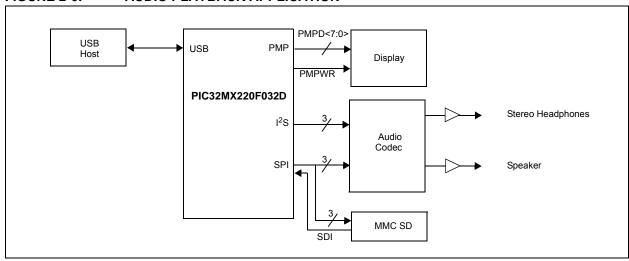

# 2.9 Typical Application Connection Examples

Examples of typical application connections are shown in Figure 2-5 and Figure 2-6.

FIGURE 2-5: CAPACITIVE TOUCH SENSING WITH GRAPHICS APPLICATION

FIGURE 2-6: AUDIO PLAYBACK APPLICATION

#### 4.0 MEMORY ORGANIZATION

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. For detailed information, refer to **Section 3.** "**Memory Organization**" (DS60001115), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family microcontrollers provide 4 GB unified virtual memory address space. All memory regions, including program, data memory, Special Function Registers (SFRs), and Configuration registers, reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, the data memory can be made executable, allowing PIC32MX1XX/2XX 28/36/44-pin Family devices to execute from data memory.

#### Key features include:

- · 32-bit native data width

- Separate User (KUSEG) and Kernel (KSEG0/KSEG1) mode address space

- · Flexible program Flash memory partitioning

- Flexible data RAM partitioning for data and program space

- · Separate boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Simple memory mapping with Fixed Mapping Translation (FMT) unit

- Cacheable (KSEG0) and non-cacheable (KSEG1) address regions

# 4.1 PIC32MX1XX/2XX 28/36/44-pin Family Memory Layout

PIC32MX1XX/2XX 28/36/44-pin Family microcontrollers implement two address schemes: virtual and physical. All hardware resources, such as program memory, data memory and peripherals, are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by bus master peripherals, such as DMA and the Flash controller, that access memory independently of the CPU.

The memory maps for the PIC32MX1XX/2XX 28/36/44-pin Family devices are illustrated in Figure 4-1 through Figure 4-6.

Table 4-1 provides SFR memory map details.

#### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0 U-0           |                   | U-0 U-0           |                  | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 |                   | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | _                 | _                 | MVEC              | _                 | TPC<2:0>          |                  |                  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 **Unimplemented:** Read as '0' bit 15-13 **Unimplemented:** Read as '0'

bit 12 MVEC: Multi Vector Configuration bit

1 = Interrupt controller configured for Multi-vectored mode

0 = Interrupt controller configured for Single-vectored mode

bit 11 Unimplemented: Read as '0'

bit 10-8 TPC<2:0>: Interrupt Proximity Timer Control bits

111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer

101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer

100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer

011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

001 = Interrupts of group priority 1 start the Interrupt Proximity timer

000 = Disables Interrupt Proximity timer

bit 7-5 **Unimplemented:** Read as '0'

bit 4 **INT4EP:** External Interrupt 4 Edge Polarity Control bit

1 = Rising edge

0 = Falling edge

bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

1 = Rising edge 0 = Falling edge

bit 2

INT2EP: External Interrupt 2 Edge Polarity Control bit

1 = Rising edge0 = Falling edge

bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

1 = Rising edge 0 = Falling edge

bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

1 = Rising edge 0 = Falling edge

# 8.0 OSCILLATOR CONFIGURATION

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 6. "Oscillator Configuration"** (DS60001112), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32MX1XX/2XX 28/36/44-pin Family oscillator system has the following modules and features:

- Four external and internal oscillator options as clock sources

- On-Chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-Chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- · Dedicated On-Chip PLL for USB peripheral

A block diagram of the oscillator system is provided in Figure 8-1.

| PIC32M2 | X1XX/2X | X 28/36 | /44-PIN | FAMIL | . Y |  |

|---------|---------|---------|---------|-------|-----|--|

| NOTES:  |         |         |         |       |     |  |

|         |         |         |         |       |     |  |

|         |         |         |         |       |     |  |

|         |         |         |         |       |     |  |

|         |         |         |         |       |     |  |

|         |         |         |         |       |     |  |

|         |         |         |         |       |     |  |

|         |         |         |         |       |     |  |

|         |         |         |         |       |     |  |

|         |         |         |         |       |     |  |

|         |         |         |         |       |     |  |

|         |         |         |         |       |     |  |

|         |         |         |         |       |     |  |

|         |         |         |         |       |     |  |

|         |         |         |         |       |     |  |

|         |         |         |         |       |     |  |

|         |         |         |         |       |     |  |

|         |         |         |         |       |     |  |

|         |         |         |         |       |     |  |

|         |         |         |         |       |     |  |

|         |         |         |         |       |     |  |

**FIGURE 10-1:** PIC32MX1XX/2XX 28/36/44-PIN FAMILY FAMILY USB INTERFACE DIAGRAM FRC Oscillator 8 MHz Typical TUN<5:0>(3) Primary Oscillator UFIN(4) (Posc) Div x PLL Div 2 UFRCEN<sup>(2)</sup> osc1 UPLLIDIV<sup>(5)</sup> UPLLEN<sup>(5)</sup> OSC2 **USB Module** USB SRP Charge Voltage Comparators Bus X SRP Discharge 48 MHz USB Clock(6) Full Speed Pull-up D+(1) Registers and Control Interface Host Pull-down SIE Transceiver ow Speed Pull-up D-(1) DMA System ŔAM Host Pull-down ID Pull-up ID<sup>(1)</sup> VBUSON<sup>(1)</sup> VUSB3V3 Transceiver Power 3.3V Pins can be used as digital input/output when USB is not enabled. Note 1: This bit field is contained in the OSCCON register. This bit field is contained in the OSCTRM register. 4: USB PLL UFIN requirements: 4 MHz. This bit field is contained in the DEVCFG2 register. A 48 MHz clock is required for proper USB operation.

#### REGISTER 10-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 |            |                        | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------|----------------------|-------------------|------------|------------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                  | U-0                  | U-0 U-0           |            | U-0                    | U-0              |

| 31.24        | _                 | _                 | -                    | _                    | _                 | _          | _                      | _                |

| 22:46        | U-0               | U-0 U-0           |                      | U-0 U-0              |                   | U-0        | U-0                    | U-0              |

| 23:16        | -                 |                   | 1                    | -                    |                   | _          | -                      | _                |

| 15:8         | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0        | U-0                    | U-0              |

| 15.6         | -                 | -                 | -                    | -                    | -                 | _          |                        | _                |

|              | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS           | R/WC-0, HS        | R/WC-0, HS | R/WC-0, HS             | R/WC-0, HS       |

| 7:0          | BTSEF             | BMXEF             | DMAEF <sup>(1)</sup> | BTOEF <sup>(2)</sup> | DFN8EF            | CRC16EF    | CRC5EF <sup>(4)</sup>  | PIDEF            |

|              | BISEF             | DIVIALI           | DIVIALITY            | BIOEL                | DENOLE            | CKCTOLF    | EOFEF <sup>(3,5)</sup> | FIDER            |

Legend:WC = Write '1' to clearHS = Hardware Settable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 BTSEF: Bit Stuff Error Flag bit

1 = Packet rejected due to bit stuff error

0 = Packet accepted

bit 6 BMXEF: Bus Matrix Error Flag bit

1 = The base address, of the Buffer Descriptor Table, or the address of an individual buffer pointed to by a Buffer Descriptor Table entry, is invalid.

0 = No address error

bit 5 **DMAEF:** DMA Error Flag bit<sup>(1)</sup>

1 = USB DMA error condition detected

0 = No DMA error

bit 4 **BTOEF:** Bus Turnaround Time-Out Error Flag bit<sup>(2)</sup>

1 = Bus turnaround time-out has occurred

0 = No bus turnaround time-out

bit 3 **DFN8EF:** Data Field Size Error Flag bit

1 = Data field received is not an integral number of bytes

0 = Data field received is an integral number of bytes

bit 2 CRC16EF: CRC16 Failure Flag bit

1 = Data packet rejected due to CRC16 error

0 = Data packet accepted

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- 2: This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

#### REGISTER 10-11: U1CON: USB CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|

| 24.24        | U-0               | U-0               | U-0 U-0                  |                   | U-0                   | U-0                   | U-0              | U-0                  |

| 31:24        | _                 | _                 | _                        | _                 | -                     |                       | _                | _                    |

| 22:46        | U-0 U-0           |                   | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 23:16        | _                 | -                 |                          | _                 | 1                     |                       | _                | _                    |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 15.6         | _                 | _                 | _                        | _                 | -                     |                       | _                | _                    |

|              | R-x R             |                   | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |

| 7:0          | JSTATE            | 050               | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST           | USBEN <sup>(4)</sup> |

|              | JOIAIE            | SE0               | TOKBUSY <sup>(1,5)</sup> | USBRST            | HOSTEN                | RESUME                | FFDRSI           | SOFEN <sup>(5)</sup> |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

1 = JSTATE was detected on the USB

0 = No JSTATE was detected

bit 6 SE0: Live Single-Ended Zero flag bit

1 = Single-Ended Zero was detected on the USB

0 = No Single-Ended Zero was detected

bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

1 = Token and packet processing is disabled (set upon SETUP token received)

0 = Token and packet processing is enabled

TOKBUSY: Token Busy Indicator bit (1,5)

1 = Token is being executed by the USB module

0 = No token is being executed

bit 4 USBRST: Module Reset bit<sup>(5)</sup>

1 = USB reset generated

0 = USB reset terminated

bit 3 **HOSTEN:** Host Mode Enable bit<sup>(2)</sup>

1 = USB host capability is enabled

0 = USB host capability is disabled

bit 2 **RESUME:** RESUME Signaling Enable bit<sup>(3)</sup>

1 = RESUME signaling is activated

0 = RESUME signaling is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

#### REGISTER 10-12: U1ADDR: USB ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -                 | _                 |                   |                   | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | -                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | LSPDEN            |                   |                   | D                 | EVADDR<6:0        | )>                |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 LSPDEN: Low-Speed Enable Indicator bit

1 = Next token command to be executed at Low-Speed0 = Next token command to be executed at Full-Speed

bit 6-0 **DEVADDR<6:0>:** 7-bit USB Device Address bits

#### REGISTER 10-13: U1FRML: USB FRAME NUMBER LOW REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21:24        | U-0               | U-0               | U-0               | U-0 U-0           |                   | U-0               | U-0              | U-0              |

| 31:24        | -                 | _                 | _                 |                   |                   | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | 1                 | -                 | _                 | -                 | -                 | _                 | -                | -                |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | FRML              | <7:0>             |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-0 FRML<7:0>: The 11-bit Frame Number Lower bits

The register bits are updated with the current frame number whenever a SOF TOKEN is received.

#### REGISTER 10-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 |         |     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------|-----|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0 U-0           |         | U-0 | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -       | _   | _                 | 1                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0     | U-0 | U-0               | U-0               | U-0              | U-0              |

| 23.10        | 1                 | -                 | 1       |     | 1                 | 1                 | 1                | _                |

| 15:8         | U-0               | U-0               | U-0     | U-0 | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _       | _   | _                 | _                 | _                | _                |

| 7:0          | U-0               | U-0               | U-0 U-0 |     | U-0               | R-0 R-0           |                  | R-0              |

| 7.0          | _                 | _                 | _       | _   | _                 |                   | FRMH<2:0>        |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-3 Unimplemented: Read as '0'

bit 2-0 FRMH<2:0>: The Upper 3 bits of the Frame Numbers bits

The register bits are updated with the current frame number whenever a SOF TOKEN is received.

#### **REGISTER 10-15: U1TOK: USB TOKEN REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | -                 | _                 | -                   | _                 | -                 | _                 | -                | _                |  |  |

| 22:46        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                 | _                 | _                   | _                 | _                 | _                 | _                | _                |  |  |

| 15:8         | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.6         | -                 | _                 | -                   | _                 | -                 | _                 | -                | -                |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          |                   | PID<              | 3:0> <sup>(1)</sup> |                   | EP<3:0>           |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR  $(1)^2$  = Bit is set  $(0)^2$  = Bit is cleared  $(0)^2$  = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-4 PID<3:0>: Token Type Indicator bits<sup>(1)</sup>

1101 = SETUP (TX) token type transaction 1001 = IN (RX) token type transaction

0001 = OUT (TX) token type transaction

Note: All other values are reserved and must not be used.

bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits

The four bit value must specify a valid endpoint.

Note 1: All other values are reserved and must not be used.

#### REGISTER 10-20: U1CNFG1: USB CONFIGURATION 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 |         |         | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------|---------|-------------------|-------------------|------------------|------------------|

| 24:24        | U-0               | U-0               | U-0 U-0 |         | U-0 U-0           |                   | U-0              | U-0              |

| 31:24        | _                 | -                 | 1       | _       | -                 | -                 | _                |                  |

| 22:46        | U-0               | U-0               | U-0     | U-0     | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | -       | _       | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0     | U-0     | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _       | _       | _                 | _                 | _                | _                |

| 7.0          | R/W-0             | R/W-0             | U-0     | R/W-0   | U-0               | U-0               | U-0              | R/W-0            |

| 7:0          | UTEYE             | UOEMON            | _       | USBSIDL | _                 | _                 | _                | UASUSPND         |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 UTEYE: USB Eye-Pattern Test Enable bit

1 = Eye-Pattern Test is enabled0 = Eye-Pattern Test is disabled

bit 6 **UOEMON:** USB OE Monitor Enable bit

1 = OE signal is active; it indicates intervals during which the D+/D- lines are driving

0 = OE signal is inactive

bit 5 Unimplemented: Read as '0'

bit 4 USBSIDL: Stop in Idle Mode bit

1 = Discontinue module operation when the device enters Idle mode

0 = Continue module operation when the device enters Idle mode

bit 3-1 Unimplemented: Read as '0'

bit 0 **UASUSPND:** Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (U1PWRC<1>) in Register 10-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (U1PWRC<1>) to suspend the module, including the USB 48 MHz clock.

| TABLE 11-6: | PERIPHERAL | . PIN SELECT | INPUT REG | SISTER MAP |

|-------------|------------|--------------|-----------|------------|

|             |            |              |           |            |

| sse                         |                  |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |       |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| FA04                        | INT1R            | 31:16     | _     | _     | _     | _     | _     | _     |      | _    |      | _    | _    |      | _    | _     |        | _    | 0000       |

| FAU4                        | INTIR            | 15:0      | _     | _     | _     | -     | -     | _     | 1    | _    | I    | _    | _    |      |      | INT1F | !<3:0> |      | 0000       |

| FA08                        | INT2R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FAUO                        | INTER            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    |      | INT2F | <3:0>  |      | 0000       |

| FA0C                        | INT3R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FAUC                        | INTOR            | 15:0      | _     | _     | _     | -     | -     | _     | 1    | _    | I    | _    | _    |      |      | INT3F | !<3:0> |      | 0000       |

| FA10                        | INT4R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FAIU                        | IIN I 4FC        | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    |      | INT4F | <3:0>  |      | 0000       |

| FA18                        | T2CKR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FATO                        | IZUKK            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    |      | T2CK  | R<3:0> |      | 0000       |

| E440                        | TACKD            | 31:16     | _     | _     | _     | -     | -     | _     | 1    | _    | I    | _    | _    |      | _    | _     | -      | _    | 0000       |

| FA1C                        | T3CKR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    |      | T3CKI | R<3:0> |      | 0000       |

| EA 20                       | TACKD            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FA20                        | T4CKR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    |      | T4CK  | R<3:0> |      | 0000       |

| FA24                        | TECKD            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FAZ4                        | T5CKR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    |      | T5CKI | R<3:0> |      | 0000       |

| E4.00                       | IO4D             | 31:16     | _     | _     | _     | -     | -     | _     | 1    | _    | I    | _    | _    |      | _    | _     | -      | _    | 0000       |

| FA28                        | IC1R             | 15:0      | _     | _     | _     | -     | -     | _     | 1    | _    | I    | _    | _    |      |      | IC1R  | <3:0>  |      | 0000       |

| E400                        | ICOD             | 31:16     | _     | _     | _     | -     | -     | _     | 1    | _    | I    | _    | _    |      | _    | _     | -      | _    | 0000       |

| FA2C                        | IC2R             | 15:0      | _     | _     | _     | -     | -     | _     | 1    | _    | I    | _    | _    |      |      | IC2R  | <3:0>  |      | 0000       |

| FA30                        | IOAD             | 31:16     | _     | _     | _     | -     | -     | _     | 1    | _    | I    | _    | _    |      | _    | _     | -      | _    | 0000       |

| FASU                        | IC3R             | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    |      | IC3R  | <3:0>  |      | 0000       |

| EA 2.4                      | IC4D             | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FA34                        | IC4R             | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    |      | IC4R  | <3:0>  |      | 0000       |

| EA 20                       | IC5R             | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FA38                        | ICSK             | 15:0      | _     | _     | _     | _     | _     | _     |      | _    | _    | _    | _    | _    |      | IC5R  | <3:0>  |      | 0000       |

| EA 40                       | OCEAD            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FA48                        | OCFAR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | OCFAI | R<3:0> |      | 0000       |

| EAAC                        | OCFBR            | 31:16     | _     | _     | _     | _     | _     | _     | -    | _    | _    | _    | _    | _    | _    | _     | -      | _    | 0000       |

| FA4C                        | OCERK            | 15:0      |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | OCFBI | R<3:0> |      | 0000       |

| EVEC                        | LIADVD           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FA50                        | U1RXR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U1RXI | R<3:0> |      | 0000       |

#### REGISTER 15-1: ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | _                 | _                 | _                 | _                 | _                 | -                 | _                | -                |

| 22:46     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | _                 | _                 | _                 | _                 | _                 | _                 | _                | 1                |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8      | ON <sup>(1)</sup> | _                 | SIDL              | _                 | _                 | -                 | FEDGE            | C32              |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | ICTMR             | ICI<1:0>          |                   | ICOV              | ICBNE             | ICM<2:0>          |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit

-n = Bit Value at POR: ('0', '1', x = unknown) P = Programmable bit r = Reserved bit

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Input Capture Module Enable bit<sup>(1)</sup>

1 = Module is enabled

0 = Disable and reset module, disable clocks, disable interrupt generation and allow SFR modifications

bit 14 **Unimplemented:** Read as '0' bit 13 **SIDL:** Stop in Idle Control bit

1 = Halt in Idle mode

0 = Continue to operate in Idle mode

bit 12-10 Unimplemented: Read as '0'

bit 9 **FEDGE:** First Capture Edge Select bit (only used in mode 6, ICM<2:0> = 110)

1 = Capture rising edge first0 = Capture falling edge firstC32: 32-bit Capture Select bit

bit 8 **C32:** 32-bit Capture Select bit 1 = 32-bit timer resource capture

1 = 32-bit timer resource capture 0 = 16-bit timer resource capture

bit 7 ICTMR: Timer Select bit (Does not affect timer selection when C32 (ICxCON<8>) is '1')

0 = Timer3 is the counter source for capture1 = Timer2 is the counter source for capture

bit 6-5 ICI<1:0>: Interrupt Control bits

11 = Interrupt on every fourth capture event

10 = Interrupt on every third capture event

01 = Interrupt on every second capture event

00 = Interrupt on every capture event

bit 4 ICOV: Input Capture Overflow Status Flag bit (read-only)

1 = Input capture overflow has occurred0 = No input capture overflow has occurred

bit 3 ICBNE: Input Capture Buffer Not Empty Status bit (read-only)

1 = Input capture buffer is not empty; at least one more capture value can be read

0 = Input capture buffer is empty

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 17-3: SPIXSTAT: SPI STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 31:24        |                   | _                 | _                 | RXBUFELM<4:0>     |                   |                   |                  |                  |  |  |

| 22.46        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23:16        | _                 | _                 | _                 | TXBUFELM<4:0>     |                   |                   |                  |                  |  |  |

| 45.0         | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |  |  |

| 15:8         | _                 | _                 | _                 | FRMERR            | SPIBUSY           | _                 | _                | SPITUR           |  |  |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |  |  |

| 7:0          | SRMT              | SPIROV            | SPIRBE            | _                 | SPITBE            | _                 | SPITBF           | SPIRBF           |  |  |

| Legend:           | C = Clearable bit HS = Set in hardware |                                    |                    |  |

|-------------------|----------------------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit                       | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set                       | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-29 Unimplemented: Read as '0'

bit 28-24 RXBUFELM<4:0>: Receive Buffer Element Count bits (valid only when ENHBUF = 1)

bit 23-21 Unimplemented: Read as '0'

bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

bit 15-13 Unimplemented: Read as '0'

bit 12 FRMERR: SPI Frame Error status bit

1 = Frame error detected

0 = No Frame error detected

This bit is only valid when FRMEN = 1.

bit 11 SPIBUSY: SPI Activity Status bit

1 = SPI peripheral is currently busy with some transactions

0 = SPI peripheral is currently idle

bit 10-9 **Unimplemented:** Read as '0'

bit 8 SPITUR: Transmit Under Run bit

1 = Transmit buffer has encountered an underrun condition

0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or writing a '0' to SPITUR.

bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

1 = When SPI module shift register is empty

0 = When SPI module shift register is not empty

bit 6 **SPIROV:** Receive Overflow Flag bit

1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

0 = No overflow has occurred

This bit is set in hardware; can bit only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or by writing a '0' to SPIROV.

bit 5 SPIRBE: RX FIFO Empty bit (valid only when ENHBUF = 1)

1 = RX FIFO is empty (CRPTR = SWPTR)

0 = RX FIFO is not empty (CRPTR ≠ SWPTR)

bit 4 Unimplemented: Read as '0'

#### REGISTER 18-1: I2CXCON: I<sup>2</sup>C CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | -                 | -                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |

**Legend:** HC = Cleared in Hardware

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** I<sup>2</sup>C Enable bit<sup>(1)</sup>

1 = Enables the I<sup>2</sup>C module and configures the SDA and SCL pins as serial port pins

$0 = \text{Disables the } I^2\text{C module}$ ; all  $I^2\text{C pins are controlled by PORT functions}$

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Discontinue module operation when the device enters Idle mode

0 = Continue module operation when the device enters Idle mode

bit 12 **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

1 = Release SCLx clock

0 = Hold SCLx clock low (clock stretch)

#### If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception.

#### If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware clear at beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 = Strict I<sup>2</sup>C Reserved Address Rule not enabled

- bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 DISSLW: Disable Slew Rate Control bit

- 1 = Slew rate control disabled

- 0 = Slew rate control enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 19-1: UxMODE: UARTX MODE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | 1                 | _                 | _                 | -                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | IREN              | RTSMD             | _                 | UEN.             | <1:0>            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL<1:0>        |                  | STSEL            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-16 Unimplemented: Read as '0'

bit 15 ON: UARTx Enable bit(1)

- 1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by the UEN<1:0> and UTXEN control bits.

- 0 = UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal.

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

- bit 12 IREN: IrDA Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- bit 11 RTSMD: Mode Selection for UxRTS Pin bit

- $1 = \overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

- bit 10 Unimplemented: Read as '0'

- bit 9-8 **UEN<1:0>:** UARTx Enable bits

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX,  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins are enabled and used

- 01 = UxTX, UxRX and  $\overline{\text{UxRTS}}$  pins are enabled and used;  $\overline{\text{UxCTS}}$  pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up enabled

- 0 = Wake-up disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### TABLE 30-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |        |                                                                  | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industria $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |      |       |       |            |  |  |

|--------------------|--------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|------------|--|--|

| Param.<br>No.      | Symbol | Characteristics                                                  | Min.                                                                                                                                                                                                                                          | Тур. | Max.  | Units | Conditions |  |  |

| Operating Voltage  |        |                                                                  |                                                                                                                                                                                                                                               |      |       |       |            |  |  |

| DC10               | VDD    | Supply Voltage (Note 2)                                          | 2.3                                                                                                                                                                                                                                           | _    | 3.6   | V     | _          |  |  |

| DC12               | VDR    | RAM Data Retention Voltage (Note 1)                              | 1.75                                                                                                                                                                                                                                          | _    | _     | V     | _          |  |  |

| DC16               | VPOR   | VDD Start Voltage<br>to Ensure Internal Power-on Reset<br>Signal | 1.75                                                                                                                                                                                                                                          | _    | 2.1   | V     | _          |  |  |

| DC17               | SVDD   | VDD Rise Rate<br>to Ensure Internal Power-on Reset<br>Signal     | 0.00005                                                                                                                                                                                                                                       | _    | 0.115 | V/μs  | _          |  |  |

**Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

<sup>2:</sup> Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 30-11 for BOR values.

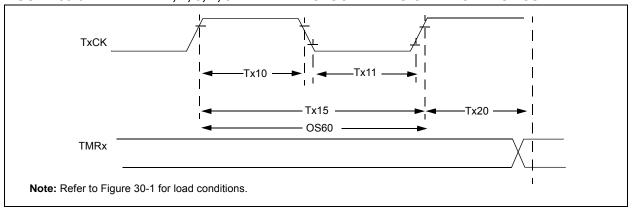

### FIGURE 30-6: TIMER1, 2, 3, 4, 5 EXTERNAL CLOCK TIMING CHARACTERISTICS

#### TABLE 30-23: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS

|                                   | <u> </u>                                                              |                                                                         |  |  |  |

|-----------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|

| AC CHARACTERISTICS <sup>(1)</sup> | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) |                                                                         |  |  |  |

|                                   | Operating temperature                                                 | -40°C ≤ TA ≤ +85°C for Industrial                                       |  |  |  |

|                                   |                                                                       | $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |  |  |  |

| Param.<br>No. | Symbol    | Characteristics <sup>(2)</sup>                                                                              |                              | Min.                                       | Typical | Max. | Units | Conditions                         |

|---------------|-----------|-------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------------------|---------|------|-------|------------------------------------|

| TA10          | ТтхН      | TxCK<br>High Time                                                                                           | Synchronous, with prescaler  | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns          | _       | _    | ns    | Must also meet parameter TA15      |

|               |           |                                                                                                             | Asynchronous, with prescaler | 10                                         | _       | _    | ns    | _                                  |

| TA11 TTXL     |           | TxCK<br>Low Time                                                                                            | Synchronous, with prescaler  | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns          | _       | _    | ns    | Must also meet parameter TA15      |

|               |           |                                                                                                             | Asynchronous, with prescaler | 10                                         | _       | _    | ns    | _                                  |

| TA15          | ТтхР      | TxCK<br>Input Period                                                                                        | Synchronous, with prescaler  | [(Greater of 25 ns or<br>2 TPB)/N] + 30 ns | _       | _    | ns    | VDD > 2.7V                         |

|               |           |                                                                                                             |                              | [(Greater of 25 ns or 2 TPB)/N] + 50 ns    | _       | _    | ns    | VDD < 2.7V                         |

|               |           |                                                                                                             | Asynchronous, with prescaler | 20                                         | _       | _    | ns    | V <sub>DD</sub> > 2.7V<br>(Note 3) |

|               |           |                                                                                                             |                              | 50                                         | _       | _    | ns    | V <sub>DD</sub> < 2.7V<br>(Note 3) |

| OS60          | Fт1       | SOSC1/T1CK Oscillator<br>Input Frequency Range<br>(oscillator enabled by setting<br>the TCS (T1CON<1>) bit) |                              | 32                                         | _       | 100  | kHz   | _                                  |

| TA20          | TCKEXTMRL | Delay from External TxCK<br>Clock Edge to Timer<br>Increment                                                |                              | _                                          | _       | 1    | Трв   | _                                  |

Note 1: Timer1 is a Type A timer.

2: This parameter is characterized, but not tested in manufacturing.

**3:** N = Prescale Value (1, 8, 64, 256).

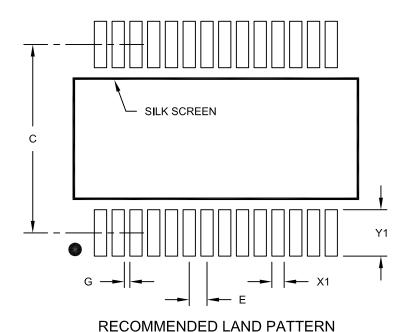

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Units MILLIMETERS **Dimension Limits** MIN MOM MAX Contact Pitch 0.65 BSC Ε Contact Pad Spacing С 7.20 Contact Pad Width (X28) X1 0.45 <u>Y1</u> Contact Pad Length (X28) 1.75 G 0.20 Distance Between Pads

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

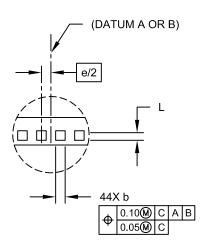

# 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**DETAIL A**

|                         | Units  | N             | ILLIMETER | S     |  |

|-------------------------|--------|---------------|-----------|-------|--|

| Dimension               | Limits | MIN           | NOM       | MAX   |  |

| Number of Pins          | Ν      |               | 44        |       |  |

| Number of Pins per Side | ND     |               | 12        |       |  |

| Number of Pins per Side | NE     |               | 10        |       |  |

| Pitch                   | е      | 0.50 BSC      |           |       |  |

| Overall Height          | Α      | 0.80          | 0.90      | 1.00  |  |

| Standoff                | A1     | 0.025         | -         | 0.075 |  |

| Overall Width           | Е      | 6.00 BSC      |           |       |  |

| Exposed Pad Width       | E2     | 4.40 4.55 4.7 |           |       |  |

| Overall Length          | D      |               | 6.00 BSC  |       |  |

| Exposed Pad Length      | D2     | 4.40          | 4.55      | 4.70  |  |

| Contact Width           | b      | 0.20          | 0.25      | 0.30  |  |

| Contact Length          | L      | 0.20          | 0.25      | 0.30  |  |

| Contact-to-Exposed Pad  | K      | 0.20          | -         | -     |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-157C Sheet 2 of 2