Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 50MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 13x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 44-QFN (8x8)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx170f256dt-50i-ml |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to documents listed in the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

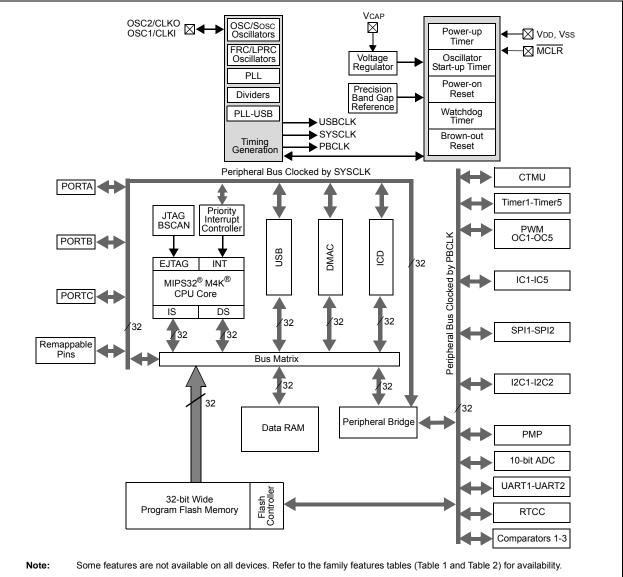

**BLOCK DIAGRAM**

This document contains device-specific information for PIC32MX1XX/2XX 28/36/44-pin Family devices.

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX1XX/2XX 28/36/44-pin Family of devices.

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

FIGURE 1-1:

|          |                                        | Pin Nu                                | mber <sup>(1)</sup>                    |                                        |             |                |                                                                         |  |

|----------|----------------------------------------|---------------------------------------|----------------------------------------|----------------------------------------|-------------|----------------|-------------------------------------------------------------------------|--|

| Pin Name | 28-pin<br>QFN                          | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC     | 36-pin<br>VTLA                         | 44-pin<br>QFN/<br>TQFP/<br>VTLA        | Pin<br>Type | Buffer<br>Type | Description                                                             |  |

| USBID    | <sub>11</sub> (3)                      | 14 <sup>(3)</sup>                     | 15 <b>(3)</b>                          | 41 <sup>(3)</sup>                      | I           | ST             | USB OTG ID detect                                                       |  |

| CTED1    | 27                                     | 2                                     | 33                                     | 19                                     | I           | ST             | CTMU External Edge Input                                                |  |

| CTED2    | 28                                     | 3                                     | 34                                     | 20                                     | I           | ST             | 7                                                                       |  |

| CTED3    | 13                                     | 16                                    | 17                                     | 43                                     | I           | ST             | 7                                                                       |  |

| CTED4    | 15                                     | 18                                    | 19                                     | 1                                      | I           | ST             | 7                                                                       |  |

| CTED5    | 22                                     | 25                                    | 28                                     | 14                                     | I           | ST             | 7                                                                       |  |

| CTED6    | 23                                     | 26                                    | 29                                     | 15                                     | I           | ST             | 7                                                                       |  |

| CTED7    | _                                      | _                                     | 20                                     | 5                                      | I           | ST             | 7                                                                       |  |

| CTED8    | _                                      |                                       | _                                      | 13                                     | I           | ST             | 7                                                                       |  |

| CTED9    | 9                                      | 12                                    | 10                                     | 34                                     | I           | ST             | 7                                                                       |  |

| CTED10   | 14                                     | 17                                    | 18                                     | 44                                     | I           | ST             | 7                                                                       |  |

| CTED11   | 18                                     | 21                                    | 24                                     | 8                                      | I           | ST             | 7                                                                       |  |

| CTED12   | 2                                      | 5                                     | 36                                     | 22                                     | I           | ST             | 7                                                                       |  |

| CTED13   | 3                                      | 6                                     | 1                                      | 23                                     | I           | ST             | 7                                                                       |  |

| CTPLS    | 21                                     | 24                                    | 27                                     | 11                                     | 0           | _              | CTMU Pulse Output                                                       |  |

| PGED1    | 1                                      | 4                                     | 35                                     | 21                                     | I/O         | ST             | Data I/O pin for Programming/Debuggin<br>Communication Channel 1        |  |

| PGEC1    | 2                                      | 5                                     | 36                                     | 22                                     | Ι           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 1 |  |

| PGED2    | 18                                     | 21                                    | 24                                     | 8                                      | I/O         | ST             | Data I/O pin for Programming/Debuggin<br>Communication Channel 2        |  |

| PGEC2    | 19                                     | 22                                    | 25                                     | 9                                      | I           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 2 |  |

| PGED3    | 11 <sup>(2)</sup><br>27 <sup>(3)</sup> | 14 <sup>(2)</sup><br>2 <sup>(3)</sup> | 15 <sup>(2)</sup><br>33 <sup>(3)</sup> | 41 <sup>(2)</sup><br>19 <sup>(3)</sup> | I/O         | ST             | Data I/O pin for Programming/Debuggin<br>Communication Channel 3        |  |

|          | 12 <b>(2)</b>                          | 15 <b>(2)</b>                         | 16 <b>(2)</b>                          | 42 <sup>(2)</sup>                      |             | OT             | Clock input pin for Programming/                                        |  |

| PGEC3    | 28 <sup>(3)</sup>                      | 3 <b>(3)</b>                          | 34 <sup>(3)</sup>                      | 20 <sup>(3)</sup>                      |             | ST             | Debugging Communication Channel 3                                       |  |

| PGED4    | —                                      | —                                     | 3                                      | 12                                     | I/O         | ST             | Data I/O pin for Programming/Debuggir<br>Communication Channel 4        |  |

| PGEC4    | —                                      | —                                     | 4                                      | 13                                     | I           | ST             | Clock input pin for Programming/<br>Debugging Communication Channel 4   |  |

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

TTL = TTL input buffer PPS = Peripheral Pin Select

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

**2:** Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

— = N/A

## 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUs

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

## 2.1 Basic Connection Requirements

Getting started with the PIC32MX1XX/2XX 28/36/44pin Family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes (see **2.5** "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.7 "External Oscillator Pins")

The following pins may be required:

• VREF+/VREF- pins – used when external voltage reference for the ADC module is implemented

Note: The AVDD and AVss pins must be connected, regardless of ADC use and the ADC voltage reference source.

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1  $\mu$ F (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu F$  to 0.001  $\mu F$ . Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu F$  in parallel with 0.001  $\mu F$ .

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

#### TABLE 4-1: SFR MEMORY MAP

|                           | Virtual A | ddress          |

|---------------------------|-----------|-----------------|

| Peripheral                | Base      | Offset<br>Start |

| Watchdog Timer            |           | 0x0000          |

| RTCC                      |           | 0x0200          |

| Timer1-5                  |           | 0x0600          |

| Input Capture 1-5         |           | 0x2000          |

| Output Compare 1-5        |           | 0x3000          |

| IC1 and IC2               |           | 0x5000          |

| SPI1 and SPI2             |           | 0x5800          |

| UART1 and UART2           |           | 0x6000          |

| PMP                       |           | 0x7000          |

| ADC                       | 0xBF80    | 0x9000          |

| CVREF                     |           | 0x9800          |

| Comparator                |           | 0xA000          |

| CTMU                      |           | 0xA200          |

| Oscillator                |           | 0xF000          |

| Device and Revision ID    |           | 0xF220          |

| Peripheral Module Disable |           | 0xF240          |

| Flash Controller          |           | 0xF400          |

| Reset                     |           | 0xF600          |

| PPS                       |           | 0xFA04          |

| Interrupts                |           | 0x1000          |

| Bus Matrix                |           | 0x2000          |

| DMA                       | 0xBF88    | 0x3000          |

| USB                       |           | 0x5050          |

| PORTA-PORTC               |           | 0x6000          |

| Configuration             | 0xBFC0    | 0x0BF0          |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        |                   | —                 | —                 | _                 | _                 | _                 | _                | —                |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | _                 | -                 | _                 |                   |                  | —                |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 15:8         | CHSPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          | CHSPTR<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |

### REGISTER 9-14: DCHxSPTR: DMA CHANNEL 'x' SOURCE POINTER REGISTER

#### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSPTR<15:0>: Channel Source Pointer bits

**Note:** When in Pattern Detect mode, this register is reset on a pattern detect.

#### REGISTER 9-15: DCHxDPTR: DMA CHANNEL 'x' DESTINATION POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        |                   |                   | _                 | _                 | —                 |                   | —                | —                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        |                   |                   | _                 | _                 | —                 |                   | —                | —                |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 15:8         | CHDPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          |                   |                   |                   | CHDPTF            | R<7:0>            |                   |                  |                  |  |

| Legend:           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

| bit 31-16 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

bit 15-0 CHDPTR<15:0>: Channel Destination Pointer bits

1111111111111111 = Points to byte 65,535 of the destination

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### REGISTER 10-10: U1STAT: USB STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   |                   |                   | _                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | —                 |                   |                   |                   | _                 | _                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | _                 | —                 |                   |                   |                   | _                 | _                | —                |

| 7.0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | U-0              | U-0              |

| 7:0          |                   | ENDP              | T<3:0>            |                   | DIR               | PPBI              |                  |                  |

### Legend:

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      | ead as '0'         |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7-4 **ENDPT<3:0>:** Encoded Number of Last Endpoint Activity bits (Represents the number of the Buffer Descriptor Table, updated by the last USB transfer.)

- 1111 = Endpoint 15 1110 = Endpoint 14 . . 0001 = Endpoint 1 0000 = Endpoint 0

- bit 3 **DIR:** Last Buffer Descriptor Direction Indicator bit

- 1 = Last transaction was a transmit (TX) transfer

- 0 = Last transaction was a receive (RX) transfer

- bit 2 **PPBI:** Ping-Pong Buffer Descriptor Pointer Indicator bit

- 1 = The last transaction was to the ODD Buffer Descriptor bank

- 0 = The last transaction was to the EVEN Buffer Descriptor bank

- bit 1-0 Unimplemented: Read as '0'

**Note:** The U1STAT register is a window into a 4-byte FIFO maintained by the USB module. U1STAT value is only valid when the TRNIF (U1IR<3>) bit is active. Clearing the TRNIF bit advances the FIFO. Data in register is invalid when the TRNIF bit = 0.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 |                   | _                 | —                 |                   | -                | -                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 |                   | _                 | —                 |                   | -                | -                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | _                 |                   | _                 | —                 |                   | -                | -                |

| 7.0          | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | LSPD              | RETRYDIS          |                   | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |

#### REGISTER 10-21: U1EP0-U1EP15: USB ENDPOINT CONTROL REGISTER

#### Legend:

| ======================================= |                  |                                    |                    |

|-----------------------------------------|------------------|------------------------------------|--------------------|

| R = Readable bit                        | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR                       | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 LSPD: Low-Speed Direct Connection Enable bit (Host mode and U1EP0 only)

- 1 = Direct connection to a Low-Speed device enabled

- 0 = Direct connection to a Low-Speed device disabled; hub required with PRE\_PID

- bit 6 **RETRYDIS:** Retry Disable bit (Host mode and U1EP0 only)

- 1 = Retry NAKed transactions disabled

- 0 = Retry NAKed transactions enabled; retry done in hardware

#### bit 5 Unimplemented: Read as '0'

bit 4 **EPCONDIS:** Bidirectional Endpoint Control bit

If EPTXEN = 1 and EPRXEN = 1:

1 = Disable Endpoint n from Control transfers; only TX and RX transfers allowed

0 = Enable Endpoint n for Control (SETUP) transfers; TX and RX transfers also allowed Otherwise, this bit is ignored.

- bit 3 **EPRXEN:** Endpoint Receive Enable bit

- 1 = Endpoint n receive is enabled

- 0 = Endpoint n receive is disabled

- bit 2 EPTXEN: Endpoint Transmit Enable bit

- 1 = Endpoint n transmit is enabled

- 0 = Endpoint n transmit is disabled

- bit 1 EPSTALL: Endpoint Stall Status bit

- 1 = Endpoint n was stalled

- 0 = Endpoint n was not stalled

- bit 0 EPHSHK: Endpoint Handshake Enable bit

- 1 = Endpoint Handshake is enabled

- 0 = Endpoint Handshake is disabled (typically used for isochronous endpoints)

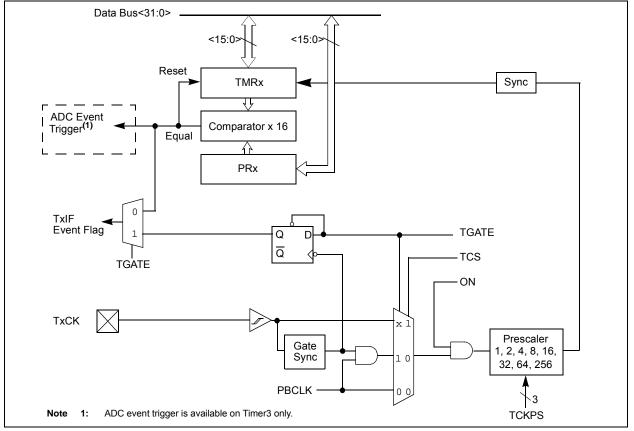

## 13.0 TIMER2/3, TIMER4/5

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features four synchronous 16-bit timers (default) that can operate as a freerunning interval timer for various timing applications and counting external events. The following modes are supported:

- Synchronous internal 16-bit timer

- Synchronous internal 16-bit gated timer

- · Synchronous external 16-bit timer

Two 32-bit synchronous timers are available by combining Timer2 with Timer3 and Timer4 with Timer5. The 32-bit timers can operate in three modes:

- Synchronous internal 32-bit timer

- · Synchronous internal 32-bit gated timer

- Synchronous external 32-bit timer

| Note: | In this chapter, references to registers, |

|-------|-------------------------------------------|

|       | TxCON, TMRx and PRx, use 'x' to           |

|       | represent Timer2 through Timer5 in 16-bit |

|       | modes. In 32-bit modes, 'x' represents    |

|       | Timer2 or Timer4 and 'y' represents       |

|       | Timer3 or Timer5.                         |

## **13.1 Additional Supported Features**

- · Selectable clock prescaler

- Timers operational during CPU idle

- Time base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

- ADC event trigger (Timer3 in 16-bit mode, Timer2/3 in 32-bit mode)

- Fast bit manipulation using CLR, SET and INV registers

Figure 13-1 and Figure 13-2 illustrate block diagrams of Timer2/3 and Timer4/5.

## FIGURE 13-1: TIMER2-TIMER5 BLOCK DIAGRAM (16-BIT)

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

## REGISTER 18-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER

|              |                   |                   |                   | 0                 |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | —                 | —                 | —                 | _                | _                |

| 22:40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |

| Legend:           | HC = Cleared in Hardwar | е                        |                    |

|-------------------|-------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** I<sup>2</sup>C Enable bit<sup>(1)</sup>

bit 12

- 1 = Enables the  $l^2C$  module and configures the SDA and SCL pins as serial port pins

- 0 = Disables the  $I^2C$  module; all  $I^2C$  pins are controlled by PORT functions

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

- **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

- 1 = Release SCLx clock

- 0 = Hold SCLx clock low (clock stretch)

#### If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception.

#### If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware clear at beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 = Strict I<sup>2</sup>C Reserved Address Rule not enabled

#### bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 DISSLW: Disable Slew Rate Control bit

- 1 = Slew rate control disabled

- 0 = Slew rate control enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

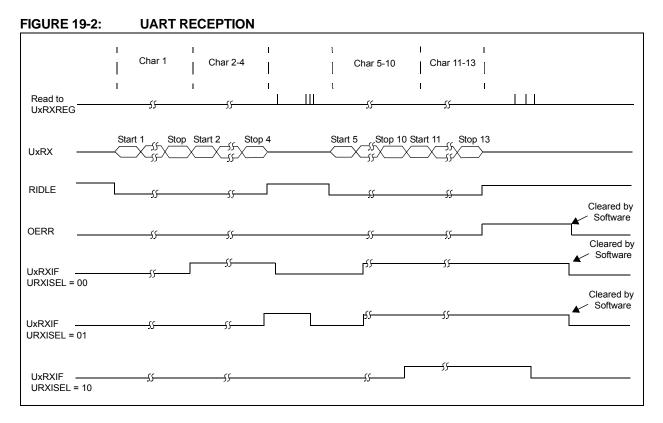

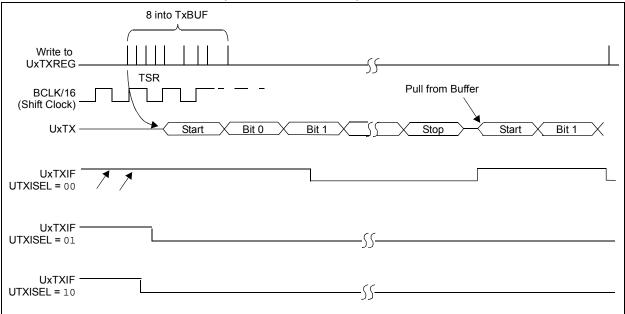

Figure 19-2 and Figure 19-3 illustrate typical receive and transmit timing for the UART module.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|--------------------|-------------------|---------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                  | _                 | _                   | _                 | -                | _                |

| 00.40        | U-0               | U-0               | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                  | _                 | _                   | _                 | -                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0              | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL               | ADRMU             | JX<1:0>             | PMPTTL            | PTWREN           | PTRDEN           |

| 7.0          | R/W-0             | R/W-0             | R/W-0              | U-0               | R/W-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | CSF<              | 1:0> <b>(2)</b>   | ALP <sup>(2)</sup> | _                 | CS1P <sup>(2)</sup> | _                 | WRSP             | RDSP             |

#### REGISTER 20-1: PMCON: PARALLEL PORT CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Parallel Master Port Enable bit<sup>(1)</sup>

- 1 = PMP enabled

- 0 = PMP disabled, no off-chip access performed

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

- bit 12-11 ADRMUX<1:0>: Address/Data Multiplexing Selection bits

- 11 = Lower 8 bits of address are multiplexed on PMD<7:0> pins; upper 8 bits are not used

- 10 = All 16 bits of address are multiplexed on PMD<7:0> pins

- 01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins, upper bits are on PMA<10:8> and PMA<14>

- 00 = Address and data appear on separate pins

- bit 10 **PMPTTL:** PMP Module TTL Input Buffer Select bit

- 1 = PMP module uses TTL input buffers

- 0 = PMP module uses Schmitt Trigger input buffer

- bit 9 **PTWREN:** Write Enable Strobe Port Enable bit

- 1 = PMWR/PMENB port enabled

- 0 = PMWR/PMENB port disabled

- bit 8 PTRDEN: Read/Write Strobe Port Enable bit

- 1 = PMRD/PMWR port enabled

- 0 = PMRD/PMWR port disabled

- bit 7-6 CSF<1:0>: Chip Select Function bits<sup>(2)</sup>

- 11 = Reserved

- 10 = PMCS1 functions as Chip Select

- 01 = PMCS1 functions as PMA<14>

- 00 = PMCS1 functions as PMA<14>

- bit 5 ALP: Address Latch Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMALL and PMALH)

- $0 = \text{Active-low} (\overline{\text{PMALL}} \text{ and } \overline{\text{PMALH}})$

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                     | -                 | _                 | -                 | -                 | _                | _                |

| 23:16        | U-0               | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:10        | —                 | —                     |                   | _                 |                   | _                 | _                | _                |

|              | U-0               | R/W-0                 | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   | CS1 <sup>(1)</sup>    |                   |                   |                   | ADDR<10:8>        |                  |                  |

|              | —                 | ADDR14 <sup>(2)</sup> | _                 | _                 | _                 |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | ADDR<7:0>         |                       |                   |                   |                   |                   |                  |                  |

#### REGISTER 20-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31-15 **Unimplemented:** Read as '0'

- bit 14 **CS1:** Chip Select 1 bit<sup>(1)</sup>

- 1 = Chip Select 1 is active

- 0 = Chip Select 1 is inactive

- bit 14 ADDR<14>: Destination Address bit 14<sup>(2)</sup>

- bit 13-11 Unimplemented: Read as '0'

- bit 10-0 ADDR<10:0>: Destination Address bits

- Note 1: When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0 R/W-0       |                  | R/W-0            |  |  |

| 31:24        | CH0NB             | _                 | _                 | —                 | CH0SB<3:0>        |                   |                  |                  |  |  |

| 00.40        | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | CH0NA             | _                 | _                 | —                 | CH0SA<3:0>        |                   |                  |                  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         |                   | _                 | _                 | —                 | _                 | —                 | —                | —                |  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0 U-0           |                   | U-0              | U-0              |  |  |

| 7:0          | —                 |                   |                   | —                 | _                 | _                 | _                | _                |  |  |

## REGISTER 22-4: AD1CHS: ADC INPUT SELECT REGISTER

CHONB: Negative Input Select bit for Sample B

## Legend:

bit 31

| R = Readable bit  | Readable bit W = Writable bit |                      | ead as '0'         |

|-------------------|-------------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown |

|        |                      | <ul> <li>1 = Channel 0 negative input is AN1</li> <li>0 = Channel 0 negative input is VREFL</li> </ul>                                                                                                                                                                                                                                          |

|--------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30 | -28                  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                      |

| bit 27 | -24                  | CH0SB<3:0>: Positive Input Select bits for Sample B                                                                                                                                                                                                                                                                                             |

|        |                      | <pre>1111 = Channel 0 positive input is Open<sup>(1)</sup> 1110 = Channel 0 positive input is IVREF<sup>(2)</sup> 1101 = Channel 0 positive input is CTMU temperature sensor (CTMUT)<sup>(3)</sup> 1100 = Channel 0 positive input is AN12<sup>(4)</sup></pre>                                                                                  |

|        |                      | •                                                                                                                                                                                                                                                                                                                                               |

|        |                      | •                                                                                                                                                                                                                                                                                                                                               |

|        |                      | •                                                                                                                                                                                                                                                                                                                                               |

|        |                      | 0001 = Channel 0 positive input is AN1<br>0000 = Channel 0 positive input is AN0                                                                                                                                                                                                                                                                |

| bit 23 |                      | CH0NA: Negative Input Select bit for Sample A Multiplexer Setting <sup>(2)</sup>                                                                                                                                                                                                                                                                |

|        |                      | <ul><li>1 = Channel 0 negative input is AN1</li><li>0 = Channel 0 negative input is VREFL</li></ul>                                                                                                                                                                                                                                             |

| bit 22 | -20                  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                      |

| bit 19 | -16                  | CH0SA<3:0>: Positive Input Select bits for Sample A Multiplexer Setting<br>1111 = Channel 0 positive input is Open <sup>(1)</sup><br>1110 = Channel 0 positive input is IVREF <sup>(2)</sup><br>1101 = Channel 0 positive input is CTMU temperature (CTMUT) <sup>(3)</sup><br>1100 = Channel 0 positive input is AN12 <sup>(4)</sup>            |

|        |                      | •                                                                                                                                                                                                                                                                                                                                               |

|        |                      | •                                                                                                                                                                                                                                                                                                                                               |

|        |                      | •                                                                                                                                                                                                                                                                                                                                               |

|        |                      | 0001 = Channel 0 positive input is AN1<br>0000 = Channel 0 positive input is AN0                                                                                                                                                                                                                                                                |

| bit 15 | -0                   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                      |

| Note   | 1:<br>2:<br>3:<br>4: | This selection is only used with CTMU capacitive and time measurement.<br>See <b>Section 24.0 "Comparator Voltage Reference (CVREF)"</b> for more information.<br>See <b>Section 25.0 "Charge Time Measurement Unit (CTMU)"</b> for more information.<br>AN12 is only available on 44-pin devices. AN6-AN8 are not available on 28-pin devices. |

|        |                      |                                                                                                                                                                                                                                                                                                                                                 |

### REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED)

- bit 10 EDGSEQEN: Edge Sequence Enable bit 1 = Edge1 must occur before Edge2 can occur 0 = No edge sequence is needed IDISSEN: Analog Current Source Control bit<sup>(2)</sup> bit 9 1 = Analog current source output is grounded 0 = Analog current source output is not grounded bit 8 **CTTRIG:** Trigger Control bit 1 = Trigger output is enabled 0 = Trigger output is disabled bit 7-2 ITRIM<5:0>: Current Source Trim bits 011111 = Maximum positive change from nominal current 011110 000001 = Minimum positive change from nominal current 000000 = Nominal current output specified by IRNG<1:0> 111111 = Minimum negative change from nominal current 100010 100001 = Maximum negative change from nominal current bit 1-0 IRNG<1:0>: Current Range Select bits<sup>(3)</sup> 11 = 100 times base current 10 = 10 times base current

- 01 = Base current level

- 00 = 1000 times base current<sup>(4)</sup>

- Note 1: When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- Refer to the CTMU Current Source Specifications (Table 30-41) in Section 30.0 "Electrical 3: Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

| DC CHARACTERISTICS |        |                     | (unless            | otherwi          | se state | <b>ed)</b><br>-40°C ≤         | <ul> <li><b>5: 2.3V to 3.6V</b></li> <li>≤ TA ≤ +85°C for Industrial</li> <li>≤ TA ≤ +105°C for V-temp</li> </ul> |

|--------------------|--------|---------------------|--------------------|------------------|----------|-------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Param.             | Symbol | Characteristic      | Min.               | Тур.             | Max.     | Units                         | Conditions                                                                                                        |

| DO10               | Vol    | Output Low Voltage  | _                  | _                | 0.4      | V                             | $\text{IOL} \leq 10 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                       |

|                    |        | Output High Voltage | 1.5(1)             | 5 <sup>(1)</sup> |          | IOH $\geq$ -14 mA, VDD = 3.3V |                                                                                                                   |

| DO20               | Vон    | I/O Pins            | 2.0 <sup>(1)</sup> | _                | _        | V                             | IOH $\geq$ -12 mA, VDD = 3.3V                                                                                     |

| D020               | VOH    |                     | 2.4                | _                | _        | v                             | IOH $\geq$ -10 mA, VDD = 3.3V                                                                                     |

|                    |        |                     | 3.0(1)             | —                | —        |                               | $IOH \ge -7 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                               |

## TABLE 30-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

Note 1: Parameters are characterized, but not tested.

### TABLE 30-11: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        |                                                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |         |      |       |            |  |

|--------------------|--------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|

| Param.<br>No.      | Symbol | Characteristics                                           | Min. <sup>(1)</sup>                                                                                                                                                                                                                                                                   | Typical | Max. | Units | Conditions |  |

| BO10               | VBOR   | BOR Event on VDD transition<br>high-to-low <sup>(2)</sup> | 2.0                                                                                                                                                                                                                                                                                   |         | 2.3  | V     | _          |  |

**Note 1:** Parameters are for design guidance only and are not tested in manufacturing.

2: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN.

## TABLE 30-39: PARALLEL MASTER PORT WRITE TIMING REQUIREMENTS

| AC CHARACTERISTICS |         |                                                                           | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |       |      |       |            |

|--------------------|---------|---------------------------------------------------------------------------|-------------------------------------------------------|-------|------|-------|------------|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                            | Min.                                                  | Тур.  | Max. | Units | Conditions |

| PM11               | Twr     | PMWR Pulse Width                                                          | _                                                     | 1 Трв | _    | _     | _          |

| PM12               | TDVSU   | Data Out Valid before PMWR or<br>PMENB goes Inactive (data setup<br>time) | —                                                     | 2 Трв |      | _     | _          |

| PM13               | TDVHOLD | PMWR or PMEMB Invalid to Data<br>Out Invalid (data hold time)             | —                                                     | 1 Трв | _    | _     | —          |

Note 1: These parameters are characterized, but not tested in manufacturing.

## TABLE 30-40: OTG ELECTRICAL SPECIFICATIONS

| AC CHARACTERISTICS |         |                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industria} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-tem} \end{array}$ |      |      |       |                                                                                   |

|--------------------|---------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-----------------------------------------------------------------------------------|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>    | Min.                                                                                                                                                                                                                                                                                | Тур. | Max. | Units | Conditions                                                                        |

| USB313             | VUSB3V3 | USB Voltage                       | 3.0                                                                                                                                                                                                                                                                                 |      | 3.6  | V     | Voltage on VUSB3V3<br>must be in this range<br>for proper USB<br>operation        |

| USB315             | VILUSB  | Input Low Voltage for USB Buffer  | —                                                                                                                                                                                                                                                                                   | —    | 0.8  | V     | —                                                                                 |

| USB316             | VIHUSB  | Input High Voltage for USB Buffer | 2.0                                                                                                                                                                                                                                                                                 | —    | _    | V     | —                                                                                 |

| USB318             | VDIFS   | Differential Input Sensitivity    | _                                                                                                                                                                                                                                                                                   | _    | 0.2  | V     | The difference<br>between D+ and D-<br>must exceed this value<br>while VCM is met |

| USB319             | VCM     | Differential Common Mode Range    | 0.8                                                                                                                                                                                                                                                                                 |      | 2.5  | V     | —                                                                                 |

| USB320             | Zout    | Driver Output Impedance           | 28.0                                                                                                                                                                                                                                                                                | —    | 44.0 | Ω     | —                                                                                 |

| USB321             | Vol     | Voltage Output Low                | 0.0                                                                                                                                                                                                                                                                                 | _    | 0.3  | V     | 1.425 kΩ load<br>connected to VUSB3V3                                             |

| USB322             | Vон     | Voltage Output High               | 2.8                                                                                                                                                                                                                                                                                 | _    | 3.6  | V     | 1.425 kΩ load connected to ground                                                 |

## 31.1 DC Characteristics

## TABLE 31-1: OPERATING MIPS VS. VOLTAGE

| Characteristic | VDD Range                 | Temp. Range    | Max. Frequency                     |  |  |

|----------------|---------------------------|----------------|------------------------------------|--|--|

| Characteristic | (in Volts) <sup>(1)</sup> | (in °C)        | PIC32MX1XX/2XX 28/36/44-pin Family |  |  |

| MDC5           | 2.3-3.6V                  | -40°C to +85°C | 50 MHz                             |  |  |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 30-11 for BOR values.

### TABLE 31-2: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARA         | CTERISTICS                          | 5    | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |            |  |  |  |

|------------------|-------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|

| Parameter<br>No. | Typical <sup>(3)</sup>              | Max. | Units                                                                                                                                           | Conditions |  |  |  |

| Operating (      | Operating Current (IDD) (Note 1, 2) |      |                                                                                                                                                 |            |  |  |  |

| MDC24            | 25                                  | 37   | mA                                                                                                                                              | 50 MHz     |  |  |  |

**Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

- 2: The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, Program Flash, and SRAM data memory are operational, SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- CPU executing while(1) statement from Flash

- 3: RTCC and JTAG are disabled

- **4:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

#### TABLE 31-3: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARACT                                                     | ERISTICS               |      | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |        |  |  |

|----------------------------------------------------------------|------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|

| Parameter<br>No.                                               | Typical <sup>(2)</sup> | Max. | Units Conditions                                                                                                                                    |        |  |  |

| Idle Current (IIDLE): Core Off, Clock on Base Current (Note 1) |                        |      |                                                                                                                                                     |        |  |  |

| MDC34a                                                         | 8                      | 13   | mA                                                                                                                                                  | 50 MHz |  |  |

Note 1: The test conditions for IIDLE current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- + CPU is in Idle mode (CPU core Halted), and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

| DC CHAR                           | ACTERIST               | ICS     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |            |                                                 |  |  |  |

|-----------------------------------|------------------------|---------|------------------------------------------------------|------------|-------------------------------------------------|--|--|--|

| Param.<br>No.                     | Typical <sup>(2)</sup> | Max.    | Units                                                | Conditions |                                                 |  |  |  |

| Power-Down Current (IPD) (Note 1) |                        |         |                                                      |            |                                                 |  |  |  |

| MDC40k                            | 10                     | 25      | μA                                                   | -40°C      | Base Power-Down Current                         |  |  |  |

| MDC40n                            | 250                    | 500     | μA                                                   | +85°C      | Base Power-Down Current                         |  |  |  |

| Module D                          | ifferential (          | Current |                                                      |            |                                                 |  |  |  |

| MDC41e                            | 10                     | 55      | μA                                                   | 3.6V       | Watchdog Timer Current: AIWDT (Note 3)          |  |  |  |

| MDC42e                            | 23                     | 55      | μA                                                   | 3.6V       | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3) |  |  |  |

| MDC43d                            | 1100                   | 1300    | μA                                                   | 3.6V       | ADC: Aladc (Notes 3,4)                          |  |  |  |

### TABLE 31-4: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** The test conditions for IPD current measurements are as follows:

• Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- · OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Sleep mode, and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

## TABLE 31-5: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                                                    | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |         |          |       |                               |

|--------------------|--------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|-------|-------------------------------|

| Param.<br>No.      | Symbol | Characteristics                                                                    | Min.                                                                                                                                                | Typical | Max.     | Units | Conditions                    |

| MOS10              |        | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC<br>4                                                                                                                                             |         | 50<br>50 |       | EC (Note 2)<br>ECPLL (Note 1) |

Note 1: PLL input requirements: 4 MHz  $\leq$  FPLLIN  $\leq$  5 MHz (use PLL prescaler to reduce Fosc). This parameter is characterized, but tested at 10 MHz only at manufacturing.

**2:** This parameter is characterized, but not tested in manufacturing.

## TABLE 31-6:SPIX MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                    | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |         |      |       |            |

|--------------------|--------|------------------------------------|-------------------------------------------------------|---------|------|-------|------------|

| Param.<br>No.      | Symbol | Characteristics                    | Min.                                                  | Typical | Max. | Units | Conditions |

| MSP10              | TscL   | SCKx Output Low Time<br>(Note 1,2) | Тѕск/2                                                |         | —    | ns    | _          |

| MSP11              | TscH   | SCKx Output High Time (Note 1,2)   | Тѕск/2                                                | _       | _    | ns    | _          |

Note 1: These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

## TABLE 31-7: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \end{array}$ |      |      |       |            |

|--------------------|--------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup>      | Min.                                                                                                                                                                                                                  | Тур. | Max. | Units | Conditions |

| MSP10              | TscL   | SCKx Output Low Time<br>(Note 1,2)  | Тѕск/2                                                                                                                                                                                                                | _    | _    | ns    | _          |

| MSP11              | TSCH   | SCKx Output High Time<br>(Note 1,2) | Тѕск/2                                                                                                                                                                                                                | _    | _    | ns    | —          |

**Note 1:** These parameters are characterized, but not tested in manufacturing.