Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| tails                   |                                                                                 |

|-------------------------|---------------------------------------------------------------------------------|

| oduct Status            | Active                                                                          |

| re Processor            | MIPS32® M4K™                                                                    |

| re Size                 | 32-Bit Single-Core                                                              |

| eed                     | 40MHz                                                                           |

| nnectivity              | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| ripherals               | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| mber of I/O             | 35                                                                              |

| gram Memory Size        | 256KB (256K x 8)                                                                |

| gram Memory Type        | FLASH                                                                           |

| ROM Size                | -                                                                               |

| 1 Size                  | 64K x 8                                                                         |

| cage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| a Converters            | A/D 13x10b                                                                      |

| cillator Type           | Internal                                                                        |

| erating Temperature     | -40°C ~ 85°C (TA)                                                               |

| unting Type             | Surface Mount                                                                   |

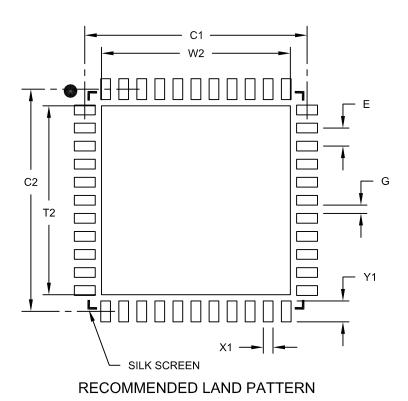

| kage / Case             | 44-VQFN Exposed Pad                                                             |

| oplier Device Package   | 44-QFN (8x8)                                                                    |

| chase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx170f256dt-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 2: PIC32MX2XX 28/36/44-PIN USB FAMILY FEATURES

| (KB)(1)  Remaplable Peripherals  s ators  dicated)  Shannels) |      |                                    |                  |                 |                                        |      |                      |                                    |                    |                     |                  |     | _                                        |      | (s)                          |      |          |      |                                 |

|---------------------------------------------------------------|------|------------------------------------|------------------|-----------------|----------------------------------------|------|----------------------|------------------------------------|--------------------|---------------------|------------------|-----|------------------------------------------|------|------------------------------|------|----------|------|---------------------------------|

| Device                                                        | Pins | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins | Timers <sup>(2)</sup> /Capture/Compare | UART | SPI/I <sup>2</sup> S | External Interrupts <sup>(3)</sup> | Analog Comparators | USB On-The-Go (OTG) | 1 <sup>2</sup> C | РМР | DMA Channels<br>(Programmable/Dedicated) | СТМО | 10-bit 1 Msps ADC (Channels) | RTCC | I/O Pins | JTAG | Packages                        |

| PIC32MX210F016B                                               | 28   | 16+3                               | 4                | 19              | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | Υ                   | 2                | Υ   | 4/2                                      | Υ    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX210F016C                                               | 36   | 16+3                               | 4                | 23              | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | Υ                   | 2                | Υ   | 4/2                                      | Υ    | 12                           | Υ    | 25       | Υ    | VTLA                            |

| PIC32MX210F016D                                               | 44   | 16+3                               | 4                | 31              | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | Υ                   | 2                | Υ   | 4/2                                      | Υ    | 13                           | Υ    | 33       | Υ    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX220F032B                                               | 28   | 32+3                               | 8                | 19              | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | Υ                   | 2                | Υ   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX220F032C                                               | 36   | 32+3                               | 8                | 23              | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | Υ                   | 2                | Υ   | 4/2                                      | Υ    | 12                           | Υ    | 23       | Υ    | VTLA                            |

| PIC32MX220F032D                                               | 44   | 32+3                               | 8                | 31              | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | Υ                   | 2                | Υ   | 4/2                                      | Υ    | 13                           | Υ    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX230F064B                                               | 28   | 64+3                               | 16               | 19              | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | Υ                   | 2                | Υ   | 4/2                                      | Υ    | 9                            | Υ    | 19       | Υ    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX230F064C                                               | 36   | 64+3                               | 16               | 23              | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | Υ                   | 2                | Υ   | 4/2                                      | Υ    | 12                           | Υ    | 23       | Υ    | VTLA                            |

| PIC32MX230F064D                                               | 44   | 64+3                               | 16               | 31              | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | Υ                   | 2                | Υ   | 4/2                                      | Υ    | 13                           | Υ    | 33       | Υ    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX250F128B                                               | 28   | 128+3                              | 32               | 19              | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | Υ                   | 2                | Υ   | 4/2                                      | Υ    | 9                            | Υ    | 19       | Υ    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX250F128C                                               | 36   | 128+3                              | 32               | 23              | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | Υ                   | 2                | Υ   | 4/2                                      | Υ    | 12                           | Υ    | 23       | Υ    | VTLA                            |

| PIC32MX250F128D                                               | 44   | 128+3                              | 32               | 31              | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | Υ                   | 2                | Υ   | 4/2                                      | Υ    | 13                           | Υ    | 33       | Υ    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX230F256B                                               | 28   | 256+3                              | 16               | 20              | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | Υ                   | 2                | Υ   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX230F256D                                               | 44   | 256+3                              | 16               | 31              | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | Υ                   | 2                | Υ   | 4/2                                      | Υ    | 13                           | Υ    | 33       | Υ    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX270F256B                                               | 28   | 256+3                              | 64               | 19              | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | Υ                   | 2                | Υ   | 4/2                                      | Υ    | 9                            | Υ    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX270F256D                                               | 44   | 256+3                              | 64               | 31              | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | Υ                   | 2                | Υ   | 4/2                                      | Υ    | 13                           | Υ    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX270F256DB <sup>(4)</sup> Note 1: This device f         | 44   | 256+3                              | 64               | 31              | 5/5/5                                  | 2    | 2                    | 5                                  | 3                  | Υ                   | 2                | Υ   | 4/2                                      | Υ    | 13                           | Υ    | 33       | Υ    | VTLA,<br>TQFP,<br>QFN           |

Note 1: This device features 3 KB of boot Flash memory.

**<sup>2:</sup>** Four out of five timers are remappable.

**<sup>3:</sup>** Four out of five external interrupts are remappable.

**<sup>4:</sup>** This PIC32 device is targeted to specific audio software packages that are tracked for licensing royalty purposes. All peripherals and electrical characteristics are identical to their corresponding base part numbers.

#### TABLE 13: PIN NAMES FOR 44-PIN GENERAL PURPOSE DEVICES

44-PIN VTLA (TOP VIEW)(1,2,3,5)

PIC32MX110F016D PIC32MX120F032D PIC32MX130F064D PIC32MX130F256D PIC32MX150F128D PIC32MX170F256D

44

| Pin # | Full Pin Name                                  |

|-------|------------------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                       |

| 2     | RPC6/PMA1/RC6                                  |

| 3     | RPC7/PMA0/RC7                                  |

| 4     | RPC8/PMA5/RC8                                  |

| 5     | RPC9/CTED7/PMA6/RC9                            |

| 6     | Vss                                            |

| 7     | VCAP                                           |

| 8     | PGED2/RPB10/CTED11/PMD2/RB10                   |

| 9     | PGEC2/RPB11/PMD1/RB11                          |

| 10    | AN12/PMD0/RB12                                 |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10           |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7       |

| 14    | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 16    | AVss                                           |

| 17    | AVDD                                           |

| 18    | MCLR                                           |

| 19    | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          |

| 20    | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0           |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1          |

| Pin# | Full Pin Name                        |

|------|--------------------------------------|

| 23   | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 |

| 24   | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3   |

| 25   | AN6/RPC0/RC0                         |

| 26   | AN7/RPC1/RC1                         |

| 27   | AN8/RPC2/PMA2/RC2                    |

| 28   | VDD                                  |

| 29   | Vss                                  |

| 30   | OSC1/CLKI/RPA2/RA2                   |

| 31   | OSC2/CLKO/RPA3/RA3                   |

| 32   | TDO/RPA8/PMA8/RA8                    |

| 33   | SOSCI/RPB4/RB4                       |

| 34   | SOSCO/RPA4/T1CK/CTED9/RA4            |

| 35   | TDI/RPA9/PMA9/RA9                    |

| 36   | RPC3/RC3                             |

| 37   | RPC4/PMA4/RC4                        |

| 38   | RPC5/PMA3/RC5                        |

| 39   | Vss                                  |

| 40   | VDD                                  |

| 41   | PGED3/RPB5/PMD7/RB5                  |

| 42   | PGEC3/RPB6/PMD6/RB6                  |

| 43   | RPB7/CTED3/PMD5/INT0/RB7             |

| 44   | RPB8/SCL1/CTED10/PMD4/RB8            |

- Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions

- 2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

- 5: Shaded pins are 5V tolerant.

# 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUs

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

#### 2.1 Basic Connection Requirements

Getting started with the PIC32MX1XX/2XX 28/36/44-pin Family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes (see 2.5 "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.7 "External Oscillator Pins")

The following pins may be required:

VREF+/VREF- pins – used when external voltage reference for the ADC module is implemented

Note:

The AVDD and AVss pins must be connected, regardless of ADC use and the ADC voltage reference source.

#### 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1 µF (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used

- Placement on the printed circuit board: The

decoupling capacitors should be placed as close

to the pins as possible. It is recommended that

the capacitors be placed on the same side of the

board as the device. If space is constricted, the

capacitor can be placed on another layer on the

PCB using a via; however, ensure that the trace

length from the pin to the capacitor is within onequarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01 µF to 0.001 µF. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1 µF in parallel with 0.001 µF.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

TABLE 4-1: SFR MEMORY MAP

|                           | Virtual Ad | ddress          |

|---------------------------|------------|-----------------|

| Peripheral                | Base       | Offset<br>Start |

| Watchdog Timer            |            | 0x0000          |

| RTCC                      |            | 0x0200          |

| Timer1-5                  |            | 0x0600          |

| Input Capture 1-5         |            | 0x2000          |

| Output Compare 1-5        |            | 0x3000          |

| IC1 and IC2               |            | 0x5000          |

| SPI1 and SPI2             |            | 0x5800          |

| UART1 and UART2           |            | 0x6000          |

| PMP                       |            | 0x7000          |

| ADC                       | 0xBF80     | 0x9000          |

| CVREF                     |            | 0x9800          |

| Comparator                |            | 0xA000          |

| CTMU                      |            | 0xA200          |

| Oscillator                |            | 0xF000          |

| Device and Revision ID    |            | 0xF220          |

| Peripheral Module Disable |            | 0xF240          |

| Flash Controller          |            | 0xF400          |

| Reset                     |            | 0xF600          |

| PPS                       |            | 0xFA04          |

| Interrupts                |            | 0x1000          |

| Bus Matrix                |            | 0x2000          |

| DMA                       | 0xBF88     | 0x3000          |

| USB                       |            | 0x5050          |

| PORTA-PORTC               |            | 0x6000          |

| Configuration             | 0xBFC0     | 0x0BF0          |

#### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | 1                 | 1                 | I                 | _                 |                   | 1                 |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | -                 | _                 | _                 | _                 |                   | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | -                 | _                 | MVEC              | _                 |                   | TPC<2:0>         |                  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 **Unimplemented:** Read as '0' bit 15-13 **Unimplemented:** Read as '0'

bit 12 MVEC: Multi Vector Configuration bit

1 = Interrupt controller configured for Multi-vectored mode

0 = Interrupt controller configured for Single-vectored mode

bit 11 **Unimplemented:** Read as '0'

bit 10-8 TPC<2:0>: Interrupt Proximity Timer Control bits

111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer

101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer

100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer

011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer

010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

001 = Interrupts of group priority 1 start the Interrupt Proximity timer

000 = Disables Interrupt Proximity timer

bit 7-5 **Unimplemented:** Read as '0'

bit 4 **INT4EP:** External Interrupt 4 Edge Polarity Control bit

1 = Rising edge

0 = Falling edge

bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

1 = Rising edge

0 = Falling edge

bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

1 = Rising edge0 = Falling edge

bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

1 = Rising edge0 = Falling edge

bit 0 **INT0EP:** External Interrupt 0 Edge Polarity Control bit

1 = Rising edge

0 = Falling edge

**FIGURE 10-1:** PIC32MX1XX/2XX 28/36/44-PIN FAMILY FAMILY USB INTERFACE DIAGRAM FRC Oscillator 8 MHz Typical TUN<5:0>(3) Primary Oscillator UFIN(4) (Posc) Div x PLL Div 2 UFRCEN<sup>(2)</sup> osc1 UPLLIDIV<sup>(5)</sup> UPLLEN<sup>(5)</sup> OSC2 **USB Module** USB SRP Charge Voltage Comparators Bus X SRP Discharge 48 MHz USB Clock(6) Full Speed Pull-up D+(1) Registers and Control Interface Host Pull-down SIE Transceiver ow Speed Pull-up D-(1) DMA System ŔAM Host Pull-down ID Pull-up ID<sup>(1)</sup> VBUSON<sup>(1)</sup> VUSB3V3 Transceiver Power 3.3V Pins can be used as digital input/output when USB is not enabled. Note 1: This bit field is contained in the OSCCON register. This bit field is contained in the OSCTRM register. 4: USB PLL UFIN requirements: 4 MHz. This bit field is contained in the DEVCFG2 register. A 48 MHz clock is required for proper USB operation.

#### 11.3 Peripheral Pin Select

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin-count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only option.

The Peripheral Pin Select (PPS) configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The PPS configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.3.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the PPS feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

#### 11.3.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digitalonly peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital-only peripheral modules are never included in the PPS feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin.

Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

# 11.3.3 CONTROLLING PERIPHERAL PIN SELECT

PPS features are controlled through two sets of SFRs: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

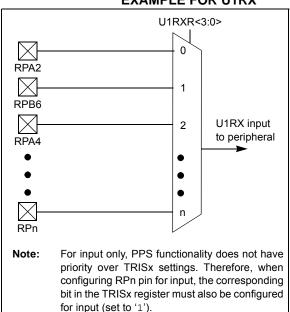

#### 11.3.4 INPUT MAPPING

The inputs of the PPS options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The [pin name]R registers, where [pin name] refers to the peripheral pins listed in Table 11-1, are used to configure peripheral input mapping (see Register 11-1). Each register contains sets of 4 bit fields. Programming these bit fields with an appropriate value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field is shown in Table 11-1.

For example, Figure 11-2 illustrates the remappable pin selection for the U1RX input.

FIGURE 11-2: REMAPPABLE INPUT EXAMPLE FOR U1RX

#### REGISTER 12-1: T1CON: TYPE A TIMER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | _                 | -                 | _                 | -                 | -                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | TWDIS             | TWIP              | _                 | _                | _                |

| 7:0          | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7:0          | TGATE             | _                 | TCKPS             | S<1:0>            | _                 | TSYNC             | TCS              | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Timer On bit<sup>(1)</sup>

1 = Timer is enabled

0 = Timer is disabled

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Discontinue module operation when the device enters Idle mode

0 = Continue module operation when the device enters Idle mode

bit 12 **TWDIS:** Asynchronous Timer Write Disable bit

1 = Writes to Timer1 are ignored until pending write operation completes

0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)

bit 11 **TWIP:** Asynchronous Timer Write in Progress bit

In Asynchronous Timer mode:

1 = Asynchronous write to the Timer1 register in progress

0 = Asynchronous write to Timer1 register is complete

In Synchronous Timer mode:

This bit is read as '0'.

bit 10-8 Unimplemented: Read as '0'

bit 7 TGATE: Timer Gated Time Accumulation Enable bit

$\frac{\text{When TCS} = 1:}{\text{This bit is ignored.}}$

When TCS = 0:

1 = Gated time accumulation is enabled

0 = Gated time accumulation is disabled

bit 6 Unimplemented: Read as '0'

bit 5-4 TCKPS<1:0>: Timer Input Clock Prescale Select bits

11 = 1:256 prescale value

10 = 1:64 prescale value

01 = 1:8 prescale value

00 = 1:1 prescale value

**Note 1:** When using 1:1 PBCmLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

## 13.2 Timer Control Registers

#### TABLE 13-1: TIMER2-TIMER5 REGISTER MAP

| SS                          |                                 |           |       |       |       |       |       |       |      | Ві   | its    |      |          |      |      |      |      |      |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|--------|------|----------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7   | 22/6 | 21/5     | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 0800                        | T2CON                           | 31:16     | _     | -     | _     | _     | _     | -     | _    | _    | _      | _    | _        | _    | _    | _    | _    |      | 0000       |

| 0000                        | 12001                           | 15:0      | ON    | _     | SIDL  | _     | _     | _     | _    | _    | TGATE  | 7    | CKPS<2:0 | >    | T32  | _    | TCS  |      | 0000       |

| 0810                        | TMR2                            | 31:16     | _     | _     | _     | _     | _     | _     | _    |      | _      |      | _        | _    | _    | _    | _    | _    | 0000       |

| 0010                        | TIVITYZ                         | 15:0      |       |       |       |       |       |       |      | TMR2 | <15:0> |      |          |      |      |      |      |      | 0000       |

| 0820                        | PR2                             | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _      | _    | _        | _    | _    | _    | _    | _    | 0000       |

| 0020                        |                                 | 15:0      |       |       |       |       |       |       |      | PR2< | :15:0> |      |          |      |      |      |      |      | FFFF       |

| 0400                        | T3CON                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _      | _    | _        | _    | _    | _    | _    |      | 0000       |

| 0,00                        | 13001                           | 15:0      | ON    |       | SIDL  |       | _     | _     | _    |      | TGATE  | 7    | CKPS<2:0 | >    | _    | _    | TCS  | _    | 0000       |

| 0410                        | TMR3                            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _      | _    | _        | _    | _    | _    | _    | _    | 0000       |

| 0/110                       | TIVITO                          | 15:0      |       |       |       |       |       |       |      | TMR3 | <15:0> |      |          |      |      |      |      |      | 0000       |

| 0A20                        | PR3                             | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _      | _    | _        | _    | _    | _    | _    | _    | 0000       |

| 07120                       |                                 | 15:0      |       |       |       |       |       |       |      | PR3< | :15:0> |      |          |      |      |      |      |      | FFFF       |

| 0000                        | T4CON                           | 31:16     | _     | _     | _     | _     | _     |       | _    | _    | _      | _    | _        | _    | _    | _    | _    |      | 0000       |

| 0000                        |                                 | 15:0      | ON    | _     | SIDL  | _     | _     |       | _    | _    | TGATE  | 7    | CKPS<2:0 | >    | T32  | _    | TCS  |      | 0000       |

| 0C10                        | TMR4                            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _      | _    | _        | _    | _    | _    | _    | _    | 0000       |

| 00.0                        |                                 | 15:0      |       |       |       |       |       |       |      | TMR4 | <15:0> |      |          |      |      | I    | 1    |      | 0000       |

| 0C20                        | PR4                             | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _      | _    | _        | _    | _    | _    | _    | _    | 0000       |

| 0020                        |                                 | 15:0      |       |       | ı     |       | 1     |       |      | PR4< | :15:0> |      | 1        |      | ı    |      | ı    |      | FFFF       |

| 0F00                        | T5CON                           | 31:16     | _     | -     | _     | _     | _     | -     | _    | _    | _      | _    | _        | _    | _    | _    | _    | -    | 0000       |

| 3200                        |                                 | 15:0      | ON    | _     | SIDL  | _     | _     | _     | _    |      | TGATE  |      | CKPS<2:0 | >    | _    | _    | TCS  | _    | 0000       |

| 0E10                        | TMR5                            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _      | _    | _        | _    | _    | _    | _    | _    | 0000       |

| 02.10                       |                                 | 15:0      |       |       |       |       |       |       |      | TMR5 | <15:0> |      |          |      |      | I    | 1    |      | 0000       |

| 0E20                        | PR5                             | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _      | _    | _        | _    | _    | _    | _    | _    | 0000       |

| 3220                        |                                 | 15:0      |       |       |       |       |       |       |      | PR5< | :15:0> |      |          |      |      |      |      |      | FFFF       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### 16.1 Output Compare Control Registers

#### TABLE 16-1: OUTPUT COMPARE 1-OUTPUT COMPARE 5 REGISTER MAP

| ess                         |                                 |               |                |       |           |       |       |       |      | Bi    | ts     |      |           |            |             |      |           |      | 9          |

|-----------------------------|---------------------------------|---------------|----------------|-------|-----------|-------|-------|-------|------|-------|--------|------|-----------|------------|-------------|------|-----------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15          | 30/14 | 29/13     | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7   | 22/6 | 21/5      | 20/4       | 19/3        | 18/2 | 17/1      | 16/0 | All Resets |

|                             | OC1CON                          | 31:16<br>15:0 | ON             |       | —<br>SIDL | _     | _     |       | _    | _     | _      | _    | —<br>OC32 | —<br>OCFLT | —<br>OCTSEL | _    | OCM<2:0>  | _    | 0000       |

| 3010                        | OC1R                            | 31:16<br>15:0 |                |       |           |       |       |       |      | OC1R- | <31:0> |      |           |            |             |      |           |      | xxxx       |

| 3020                        | OC1RS                           | 31:16<br>15:0 |                |       |           |       |       |       |      | OC1RS | <31:0> |      |           |            |             |      |           |      | xxxx       |

| 3200                        | OC2CON                          | 31:16<br>15:0 | —<br>ON        | _     | —<br>SIDL | _     | _     | _     | _    | _     | _      | _    | —<br>OC32 | —<br>OCFLT | OCTSEL      | _    | OCM<2:0>  | _    | 0000       |

| 3210                        | OC2R                            | 31:16<br>15:0 |                |       |           |       |       |       |      | OC2R  | <31:0> |      |           |            |             |      |           |      | xxxx       |

| 3220                        | OC2RS                           | 31:16<br>15:0 | OC2RS<31:0>    |       |           |       |       |       |      |       |        |      |           |            |             | xxxx |           |      |            |

| 3400                        | OC3CON                          | 31:16<br>15:0 | ON             | _     | —<br>SIDL | _     | _     | _     | _    | _     | _      | _    | —<br>OC32 | —<br>OCFLT | OCTSEL      | _    | OCM<2:0>  | _    | 0000       |

| 3410                        | OC3R                            | 31:16<br>15:0 | O.V            |       | OIDE      |       |       |       |      | OC3R  |        |      | 0002      | 00.21      | 001022      |      | 00M 12.01 |      | xxxx       |

| 3420                        | OC3RS                           | 31:16<br>15:0 |                |       |           |       |       |       |      | OC3RS | <31:0> |      |           |            |             |      |           |      | xxxx       |

| 3600                        | OC4CON                          | 31:16<br>15:0 | ON             | _     | —<br>SIDL | _     | _     | _     | _    | _     | _      | _    | —<br>OC32 | —<br>OCFLT | OCTSEL      | _    | OCM<2:0>  | _    | 0000       |

| 3610                        | OC4R                            | 31:16<br>15:0 | 0.1            |       | 0.52      |       |       |       |      | OC4R  | <31:0> |      | 0002      | 00.2.      | 00.022      |      | 20 2.0    |      | xxxx       |

| 3620                        | OC4RS                           | 31:16<br>15:0 | OC4RS<31:0>    |       |           |       |       |       |      |       |        |      |           |            | xxxx        |      |           |      |            |

| 3800                        | OC5CON                          | 31:16<br>15:0 |                |       |           |       |       |       |      |       |        |      |           |            |             | 0000 |           |      |            |

| 3810                        | OC5R                            | 31:16<br>15:0 | OC5R<31:0>     |       |           |       |       |       |      |       |        |      |           |            |             | xxxx |           |      |            |

| 3820                        | OC5RS                           | 31:16<br>15:0 | OC5RS<31:0> xx |       |           |       |       |       |      |       |        |      |           |            | xxxx        |      |           |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### REGISTER 19-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 31:24        |                   | _                 | _                 | -                 | _                 | -                 | _                | ADM_EN           |

| 22.46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | ADDR<             | <7:0>             |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-1              |

| 15:8         | UTXISE            | L<1:0>            | UTXINV            | URXEN             | UTXBRK            | UTXEN             | UTXBF            | TRMT             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R-1               | R-0               | R-0               | R/W-0            | R-0              |

| 7:0          | URXISE            | L<1:0>            | ADDEN             | RIDLE             | PERR              | FERR              | OERR             | URXDA            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-25 Unimplemented: Read as '0'

bit 24 ADM\_EN: Automatic Address Detect Mode Enable bit

1 = Automatic Address Detect mode is enabled

0 = Automatic Address Detect mode is disabled

bit 23-16 ADDR<7:0>: Automatic Address Mask bits

When the ADM\_EN bit is '1', this value defines the address character to use for automatic address detection.

bit 15-14 UTXISEL<1:0>: TX Interrupt Mode Selection bits

11 = Reserved, do not use

10 = Interrupt is generated and asserted while the transmit buffer is empty

01 = Interrupt is generated and asserted when all characters have been transmitted

00 = Interrupt is generated and asserted while the transmit buffer contains at least one empty space

bit 13 UTXINV: Transmit Polarity Inversion bit

If IrDA mode is disabled (i.e., IREN (UxMODE<12>) is '0'):

1 = UxTX Idle state is '0'

0 = UxTX Idle state is '1'

#### If IrDA mode is enabled (i.e., IREN (UxMODE<12>) is '1'):

1 = IrDA encoded UxTX Idle state is '1'

0 = IrDA encoded UxTX Idle state is '0'

bit 12 URXEN: Receiver Enable bit

1 = UARTx receiver is enabled. UxRX pin is controlled by UARTx (if ON = 1)

0 = UARTx receiver is disabled. UxRX pin is ignored by the UARTx module. UxRX pin is controlled by port.

bit 11 UTXBRK: Transmit Break bit

1 = Send Break on next transmission. Start bit followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

0 = Break transmission is disabled or completed

bit 10 UTXEN: Transmit Enable bit

1 = UARTx transmitter is enabled. UxTX pin is controlled by UARTx (if ON = 1).

0 = UARTx transmitter is disabled. Any pending transmission is aborted and buffer is reset. UxTX pin is controlled by port.

bit 9 UTXBF: Transmit Buffer Full Status bit (read-only)

1 = Transmit buffer is full

0 = Transmit buffer is not full, at least one more character can be written

bit 8 **TRMT:** Transmit Shift Register is Empty bit (read-only)

1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed)

0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer

# DS60001168J-page 211

### **ADC Control Registers**

#### TABLE 22-1: ADC REGISTER MAP

| ess                         |                        | 4             | Bits                               |                                    |        |        |        |           |          |                     |           |                 |       |         |        |       |        |       |            |

|-----------------------------|------------------------|---------------|------------------------------------|------------------------------------|--------|--------|--------|-----------|----------|---------------------|-----------|-----------------|-------|---------|--------|-------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range     | 31/15                              | 30/14                              | 29/13  | 28/12  | 27/11  | 26/10     | 25/9     | 24/8                | 23/7      | 22/6            | 21/5  | 20/4    | 19/3   | 18/2  | 17/1   | 16/0  | All Resets |

|                             | AD1CON1 <sup>(1)</sup> | 31:16         | _                                  | _                                  | _      | _      | _      | _         | _        | _                   | _         | _               | _     | _       | _      | _     | _      | _     | 0000       |

| 9000                        | ADTCONTO,              | 15:0          | ON                                 | _                                  | SIDL   | _      | _      |           | FORM<2:0 | >                   | ;         | SSRC<2:0>       | >     | CLRASAM | _      | ASAM  | SAMP   | DONE  | 0000       |

| 9010                        | AD1CON2 <sup>(1)</sup> | 31:16         | _                                  | _                                  | _      | _      | _      | _         | _        | _                   | _         | -               | _     | _       | _      | _     | _      | _     | 0000       |

| 3010                        | ADTOONZ                | 15:0          | ,                                  | VCFG<2:0>                          | '      | OFFCAL | _      | CSCNA     | _        | _                   | BUFS      | _               |       | SMPI    | <3:0>  |       | BUFM   | ALTS  | 0000       |

| 9020                        | AD1CON3 <sup>(1)</sup> | 31:16         | _                                  | _                                  | _      | _      | _      | _         | _        | _                   | _         | _               | _     | _       | _      | _     | _      | _     | 0000       |

| 0020                        | , 15 100110            | 15:0          | ADRC                               | _                                  | _      |        |        | SAMC<4:0> |          |                     |           |                 |       | ADCS    | S<7:0> |       |        |       | 0000       |

| 9040                        | AD1CHS <sup>(1)</sup>  | 31:16         | CH0NB                              | _                                  |        | _      |        | CH0SI     | 3<3:0>   | ı                   | CH0NA     | _               | _     | _       |        | CH0S/ | A<3:0> |       | 0000       |

|                             |                        | 15:0          |                                    | _                                  | _      | _      |        |           |          | _                   | _         |                 | _     | _       | _      |       |        | _     | 0000       |

| 9050                        | AD1CSSL <sup>(1)</sup> | 31:16         |                                    | _                                  | _      | _      |        | _         | _        | _                   | _         | _               |       | _       | _      | _     | _      | _     | 0000       |

|                             |                        | 15:0          | CSSL15                             | CSSL14                             | CSSL13 | CSSL12 | CSSL11 | CSSL10    | CSSL9    | CSSL8               | CSSL7     | CSSL6           | CSSL5 | CSSL4   | CSSL3  | CSSL2 | CSSL1  | CSSL0 | 0000       |

| 9070                        | ADC1BUF0               | 31:16         |                                    |                                    |        |        |        |           | ADC Res  | sult Word 0         | (ADC1BUF  | 0<31:0>)        |       |         |        |       |        |       | 0000       |

|                             |                        | 15:0          |                                    |                                    |        |        |        |           |          |                     |           |                 |       |         |        |       |        |       | 0000       |

| 9080                        | ADC1BUF1               | 31:16<br>15:0 |                                    | ADC Result Word 1 (ADC1BUF1<31:0>) |        |        |        |           |          |                     |           |                 |       |         |        |       |        | 0000  |            |

|                             |                        | 31:16         |                                    | ` ´ ´                              |        |        |        |           |          |                     |           |                 |       |         |        |       |        | 0000  |            |

| 9090                        | ADC1BUF2               | 15:0          |                                    |                                    |        |        |        |           | ADC Res  | sult Word 2         | (ADC1BUF  | 2<31:0>)        |       |         |        |       |        |       | 0000       |

|                             |                        | 31:16         |                                    |                                    |        |        |        |           |          |                     |           |                 |       |         |        |       |        |       | 0000       |

| 90A0                        | ADC1BUF3               | 15:0          |                                    |                                    |        |        |        |           | ADC Res  | sult Word 3         | (ADC1BUF  | 3<31:0>)        |       |         |        |       |        |       | 0000       |

|                             |                        | 31:16         |                                    |                                    |        |        |        |           |          |                     |           |                 |       |         |        |       |        |       | 0000       |

| 90B0                        | ADC1BUF4               | 15:0          |                                    |                                    |        |        |        |           | ADC Res  | sult Word 4         | (ADC1BUF  | 4<31:0>)        |       |         |        |       |        |       | 0000       |

|                             |                        | 31:16         |                                    |                                    |        |        |        |           |          |                     |           |                 |       |         |        |       |        |       | 0000       |

| 90C0                        | ADC1BUF5               | 15:0          |                                    |                                    |        |        |        |           | ADC Res  | sult Word 5         | (ADC1BUF  | 5<31:0>)        |       |         |        |       |        |       | 0000       |

| 0000                        | ADO4DUEC               | 31:16         |                                    |                                    |        |        |        |           | 4 D.C. D |                     | (ADC4DUE  | 0 -104 -05 \    |       |         |        |       |        |       | 0000       |

| 9000                        | ADC1BUF6               | 15:0          |                                    |                                    |        |        |        |           | ADC Res  | sult Word 6         | (ADC1BUF  | 6<31:0>)        |       |         |        |       |        |       | 0000       |

| 00E0                        | ADC1BUF7               | 31:16         |                                    |                                    |        |        |        |           | ADC Box  | sult Word 7         | (ADC1DLIE | 7/21:0>\        |       |         |        |       |        |       | 0000       |

| 9000                        | ADC IBUF1              | 15:0          |                                    |                                    |        |        |        |           | ADC RE   | suit vvoiu <i>i</i> | (ADC IBUF | /<31.02)        |       |         |        |       |        |       | 0000       |

| 90E0                        | ADC1BUF8               | 31:16         |                                    |                                    |        |        |        |           | ADC Per  | sult Word 8         | (ADC1BLIE | 8<31:0>1        |       |         |        |       |        |       | 0000       |

| 901.0                       | ADC IDOF0              | 15:0          |                                    |                                    |        |        |        |           | ADC RE   | ouit VVOIU O        |           | 0 - 0 1 . 0 ~ ) |       |         |        |       |        |       | 0000       |

| 9100                        | ADC1BUF9               | 31:16         | ADC Result Word 9 (ADC1BUF9<31:0>) |                                    |        |        |        |           |          |                     |           |                 |       |         |        |       |        |       |            |

| 3100                        | , .50 1501 9           | 15:0          |                                    | 0000                               |        |        |        |           |          |                     |           |                 |       |         |        |       |        |       |            |

| 9110                        | ADC1BUFA               | 31:16         |                                    | ADC Result Word A (ADC1BUFA<31:0>) |        |        |        |           |          |                     |           |                 |       |         |        |       |        |       |            |

|                             |                        | 15:0          |                                    |                                    |        |        |        |           | 0        |                     | ,         | ,               |       |         |        |       |        |       | 0000       |

**PIC32MX1XX/2XX 28/36/44-PIN FAMILY**

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

This register has corresponding CLR, SET and INV registers at its virtual address, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for details. Note 1:

TABLE 22-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                  | ө        |       |                                     |       |       |       |       |         | Ві          | ts        |          |      |      |      |      |      |      | v         |

|-----------------------------|------------------|----------|-------|-------------------------------------|-------|-------|-------|-------|---------|-------------|-----------|----------|------|------|------|------|------|------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Rang | 31/15 | 30/14                               | 29/13 | 28/12 | 27/11 | 26/10 | 25/9    | 24/8        | 23/7      | 22/6     | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Reset |

| 9120                        | ADC1BUFB         | 31:16    |       |                                     |       |       |       |       | ADC Res | ult Word B  | (ADC1BUE  | B<31·0>) |      |      |      |      |      |      | 0000      |

| 0120                        | 715015015        | 15:0     |       | 000                                 |       |       |       |       |         |             |           |          |      |      |      |      |      | 0000 |           |

| 0130                        | ADC1BUFC         | 31:16    |       | ADC Result Word C (ADC1BUFC<31:0>)  |       |       |       |       |         |             |           |          |      |      |      |      |      | 0000 |           |

| 9130                        | ADCIBULC         | 15:0     |       | ADC Result Word C (ADC1BUFC<31:0>)  |       |       |       |       |         |             |           |          |      |      |      |      |      | 0000 |           |

| 0140                        | ADC1BUFD         | 31:16    |       |                                     |       |       |       |       | ADC Boo | ult Word D  | (ADC1BUF  | D-21:0>) |      |      |      |      |      |      | 0000      |

| 9140                        | ADCIBULD         | 15:0     |       |                                     |       |       |       |       | ADC Res | uit vvoiu D | (ADC IBUF | D<31.02) |      |      |      |      |      |      | 0000      |

| 0150                        | ADC1BUFE         | 31:16    |       |                                     |       |       |       |       | ADC Pos | ult Word E  | (ADC1BLIE | E_31:0\) |      |      |      |      |      |      | 0000      |

| 9130                        | ADCIBULE         | 15:0     |       | ADC Result Word E (ADC1BUFE<31:0>)  |       |       |       |       |         |             |           |          |      |      |      |      |      | 0000 |           |

| 0160                        | ADC1BUFF         | 31:16    |       | ADC Pocult Word E (ADC1BLIEE-21:05) |       |       |       |       |         |             |           |          |      |      |      |      |      |      |           |

| 9100                        | ADCIBUFF         | 15:0     |       | ADC Result Word F (ADC1BUFF<31:0>)  |       |       |       |       |         |             |           |          |      |      |      |      | 0000 |      |           |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for details.

#### REGISTER 22-1: AD1CON1: ADC CONTROL REGISTER 1

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1    | Bit<br>24/16/8/0    |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|

| 31:24        | U-0                 | U-0                 |

|              | _                 | _                 | _                 | _                 | _                 |                   | _                   | _                   |

| 23:16        | U-0                 | U-0                 |

|              | _                 | _                 | _                 | _                 | _                 |                   | _                   | _                   |

| 15:8         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0               | R/W-0               |

|              | ON <sup>(1)</sup> | _                 | SIDL              | _                 | _                 | FORM<2:0>         |                     |                     |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0, HSC          | R/C-0, HSC          |

|              | SSRC<2:0>         |                   |                   | CLRASAM           | _                 | ASAM              | SAMP <sup>(2)</sup> | DONE <sup>(3)</sup> |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** ADC Operating Mode bit<sup>(1)</sup>

1 = ADC module is operating

0 = ADC module is not operating

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation when the device enters Idle mode

bit 12-11 **Unimplemented:** Read as '0'

bit 10-8 **FORM<2:0>:** Data Output Format bits

111 = Signed Fractional 32-bit (DOUT = sddd dddd dd00 0000 0000 0000 0000)

101 = Signed Integer 32-bit (DOUT = ssss ssss ssss ssss ssss sssd dddd dddd)

100 = Integer 32-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

011 = Signed Fractional 16-bit (DOUT = 0000 0000 0000 0000 sddd dddd dd00 0000)

010 = Fractional 16-bit (DOUT = 0000 0000 0000 0000 dddd dddd dd00 0000)

000 =Integer 16-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

bit 7-5 SSRC<2:0>: Conversion Trigger Source Select bits

111 = Internal counter ends sampling and starts conversion (auto convert)

110 = Reserved

101 = Reserved

100 = Reserved

011 = CTMU ends sampling and starts conversion

010 = Timer 3 period match ends sampling and starts conversion

001 = Active transition on INTO pin ends sampling and starts conversion

000 = Clearing SAMP bit ends sampling and starts conversion

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC = 0, software can write a '0' to end sampling and start conversion. If SSRC ≠ '0', this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

The processor will exit, or 'wake-up', from Sleep on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep. The interrupt priority must be greater than the current CPU priority.

- · On any form of device Reset

- · On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the PBCLK will start running and the device will enter into Idle mode.

#### 26.3.2 IDLE MODE

In Idle mode, the CPU is Halted but the System Clock (SYSCLK) source is still enabled. This allows peripherals to continue operation when the CPU is Halted. Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit. Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

- Note 1: Changing the PBCLK divider ratio requires recalculation of peripheral timing. For example, assume the UART is configured for 9600 baud with a PB clock ratio of 1:1 and a Posc of 8 MHz. When the PB clock divisor of 1:2 is used, the input frequency to the baud clock is cut in half; therefore, the baud rate is reduced to 1/2 its former value. Due to numeric truncation in calculations (such as the baud rate divisor), the actual baud rate may be a tiny percentage different than expected. For this reason, any timing calculation required for a peripheral should be performed with the new PB clock frequency instead of scaling the previous value based on a change in the PB divisor

- 2: Oscillator start-up and PLL lock delays are applied when switching to a clock source that was disabled and that uses a crystal and/or the PLL. For example, assume the clock source is switched from Posc to LPRC just prior to entering Sleep in order to save power. No oscillator start-up delay would be applied when exiting Idle. However, when switching back to Posc, the appropriate PLL and/or oscillator start-up/lock delays would be applied.

The device enters Idle mode when the SLPEN (OSCCON<4>) bit is clear and a WAIT instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU. If the priority of the interrupt event is lower than or equal to current priority of the CPU, the CPU will remain Halted and the device will remain in Idle mode.

- · On any form of device Reset

- On a WDT time-out interrupt

# 26.3.3 PERIPHERAL BUS SCALING METHOD

Most of the peripherals on the device are clocked using the PBCLK. The Peripheral Bus can be scaled relative to the SYSCLK to minimize the dynamic power consumed by the peripherals. The PBCLK divisor is controlled by PBDIV<1:0> (OSCCON<20:19>), allowing SYSCLK to PBCLK ratios of 1:1, 1:2, 1:4 and 1:8. All peripherals using PBCLK are affected when the divisor is changed. Peripherals such as the USB, Interrupt Controller, DMA, and the bus matrix are clocked directly from SYSCLK. As a result, they are not affected by PBCLK divisor changes.

Changing the PBCLK divisor affects:

- The CPU to peripheral access latency. The CPU has to wait for next PBCLK edge for a read to complete. In 1:8 mode, this results in a latency of one to seven SYSCLKs.

- The power consumption of the peripherals. Power consumption is directly proportional to the frequency at which the peripherals are clocked. The greater the divisor, the lower the power consumed by the peripherals.

To minimize dynamic power, the PB divisor should be chosen to run the peripherals at the lowest frequency that provides acceptable system performance. When selecting a PBCLK divider, peripheral clock requirements, such as baud rate accuracy, should be taken into account. For example, the UART peripheral may not be able to achieve all baud rate values at some PBCLK divider depending on the SYSCLK value.

#### 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB® X IDE Software

- · Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>TM</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- · In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- · Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- · Third-party development tools

# 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users

#### Feature-Rich Editor:

- · Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

Project-Based Workspaces:

- · Multiple projects

- · Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- · Built-in support for Bugzilla issue tracker

#### TABLE 30-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACTERISTICS                    |                        | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |       |            |                                                 |  |  |

|---------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|-------------------------------------------------|--|--|

| Param.<br>No.                         | Typical <sup>(2)</sup> | Max.                                                                                                                                                                                                                                            | Units | Conditions |                                                 |  |  |

| Power-Down Current (IPD) (Notes 1, 5) |                        |                                                                                                                                                                                                                                                 |       |            |                                                 |  |  |

| DC40k                                 | 44                     | 70                                                                                                                                                                                                                                              | μА    | -40°C      |                                                 |  |  |

| DC40I                                 | 44                     | 70                                                                                                                                                                                                                                              | μА    | +25°C      | Base Power-Down Current                         |  |  |

| DC40n                                 | 168                    | 259                                                                                                                                                                                                                                             | μА    | +85°C      | Base Power-Down Current                         |  |  |

| DC40m                                 | 335                    | 536                                                                                                                                                                                                                                             | μA    | +105°C     |                                                 |  |  |

| Module                                | Differential           | Current                                                                                                                                                                                                                                         |       |            | •                                               |  |  |

| DC41e                                 | 5                      | 20                                                                                                                                                                                                                                              | μА    | 3.6V       | Watchdog Timer Current: ΔIWDT (Note 3)          |  |  |