Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx170f256dt-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

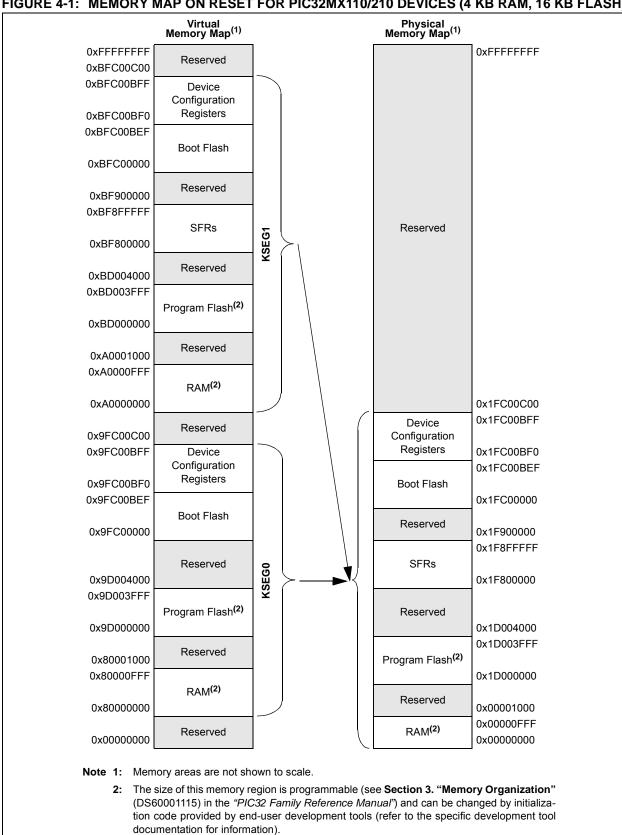

## FIGURE 4-1: MEMORY MAP ON RESET FOR PIC32MX110/210 DEVICES (4 KB RAM, 16 KB FLASH)

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 |                   | _                 | _                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 |                   | _                 | _                 | _                 | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | _                 | —                 | MVEC              | _                 |                   | TPC<2:0>         |                  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |

## REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

# Legend:

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-13 Unimplemented: Read as '0'

- bit 12 MVEC: Multi Vector Configuration bit

- 1 = Interrupt controller configured for Multi-vectored mode

- 0 = Interrupt controller configured for Single-vectored mode

- bit 11 Unimplemented: Read as '0'

- bit 10-8 **TPC<2:0>:** Interrupt Proximity Timer Control bits

- 111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer

- 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer

- 101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer

- 100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer

- 011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer

- 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

- 001 = Interrupts of group priority 1 start the Interrupt Proximity timer

- 000 = Disables Interrupt Proximity timer

#### bit 7-5 Unimplemented: Read as '0'

- bit 4 INT4EP: External Interrupt 4 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2    | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0              | U-0              |

|              |                   | _                 |                   | —                 | _                 |                      | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                    | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                | R/W-0            | R/W-0            |

| 15:8         |                   | _                 |                   | _                 | _                 | S                    | RIPL<2:0>(1)     |                  |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 |                   |                   | VEC               | <5:0> <sup>(1)</sup> |                  |                  |

#### REGISTER 7-2: INTSTAT: INTERRUPT STATUS REGISTER

# Legend:

| Legena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-11 Unimplemented: Read as '0'

- bit 10-8 SRIPL<2:0>: Requested Priority Level bits<sup>(1)</sup>

- 111-000 = The priority level of the latest interrupt presented to the CPU

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 VEC<5:0>: Interrupt Vector bits<sup>(1)</sup> 11111-00000 = The interrupt vector that is presented to the CPU

- Note 1: This value should only be used when the interrupt controller is configured for Single Vector mode.

| D:/          | Dit               | Dit               | D:                | Dit               | D'i               | D''               | Dir              | Dit              |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   | IPTMR<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23.10        | IPTMR<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 10.0         |                   |                   |                   | IPTM              | R<15:8>           |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7.0          |                   |                   |                   | IPTM              | R<7:0>            |                   |                  |                  |  |  |  |

#### REGISTER 7-3: IPTMR: INTERRUPT PROXIMITY TIMER REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 31-0 **IPTMR<31:0>:** Interrupt Proximity Timer Reload bits Used by the Interrupt Proximity Timer as a reload value when the Interrupt Proximity timer is triggered by an interrupt event.

|              |                   |                      | OULEAIO                 |                   |                   |                       |                  |                  |

|--------------|-------------------|----------------------|-------------------------|-------------------|-------------------|-----------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0                  | R/W-y                   | R/W-y             | R/W-y             | R/W-0                 | R/W-0            | R/W-1            |

| 31:24        | —                 | —                    | PLLODIV<2:0> FRCDIV<2:0 |                   | RCDIV<2:0>        | >                     |                  |                  |

| 00.40        | U-0               | R-0                  | R-1                     | R/W-y             | R/W-y             | R/W-y                 | R/W-y            | R/W-y            |

| 23:16        | —                 | SOSCRDY              | PBDIVRDY                | PBDI              | /<1:0>            | Р                     | LLMULT<2:0>      | •                |

| 45.0         | U-0               | R-0                  | R-0                     | R-0               | U-0               | R/W-y                 | R/W-y            | R/W-y            |

| 15:8         | —                 |                      | COSC<2:0>               |                   | —                 |                       | NOSC<2:0>        |                  |

| 7:0          | R/W-0             | R-0                  | R-0                     | R/W-0             | R/W-0             | R/W-0                 | R/W-y            | R/W-0            |

| 7:0          | CLKLOCK           | ULOCK <sup>(1)</sup> | SLOCK                   | SLPEN             | CF                | UFRCEN <sup>(1)</sup> | SOSCEN           | OSWEN            |

#### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| Legend:     y = Value set from Configuration bits on POR |                  |                                                          |  |  |  |  |

|----------------------------------------------------------|------------------|----------------------------------------------------------|--|--|--|--|

| R = Readable bit                                         | W = Writable bit | able bit U = Unimplemented bit, read as '0'              |  |  |  |  |

| -n = Value at POR                                        | '1' = Bit is set | '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |  |  |  |  |

#### bit 31-30 **Unimplemented:** Read as '0'

#### bit 29-27 **PLLODIV<2:0>:** Output Divider for PLL

- 111 = PLL output divided by 256

- 110 = PLL output divided by 64

- 101 = PLL output divided by 32

- 100 = PLL output divided by 16

- 011 = PLL output divided by 8

- 010 = PLL output divided by 4

- 001 = PLL output divided by 2

- 000 = PLL output divided by 1

#### bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2 (default setting)

- 000 = FRC divided by 1

- bit 23 Unimplemented: Read as '0'

- bit 22 SOSCRDY: Secondary Oscillator (Sosc) Ready Indicator bit

- 1 = The Secondary Oscillator is running and is stable

- 0 = The Secondary Oscillator is still warming up or is turned off

- bit 21 **PBDIVRDY:** Peripheral Bus Clock (PBCLK) Divisor Ready bit

- 1 = PBDIV<1:0> bits can be written

- 0 = PBDIV<1:0> bits cannot be written

- bit 20-19 **PBDIV<1:0>:** Peripheral Bus Clock (PBCLK) Divisor bits

- 11 = PBCLK is SYSCLK divided by 8 (default)

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

Note 1: This bit is only available on PIC32MX2XX devices.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

# REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- bit 3-0 ROSEL<3:0>: Reference Clock Source Select bits<sup>(1)</sup>

- 1111 = Reserved; do not use

- 1001 = Reserved; do not use 1000 = REFCLKI 0111 = System PLL output 0110 = USB PLL output 0101 = Sosc 0100 = LPRC 0011 = FRC 0010 = POSC 0001 = PBCLK 0000 = SYSCLK

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- 2: This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| REGIOTE      |                   |                   |                   |                   |                   |                   |                  |                  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 | _                 | _                 | —                 | _                 | —                | —                |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        |                   | _                 |                   | _                 | _                 |                   | _                | —                |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         |                   |                   |                   | CHSSIZ            | <15:8>            |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | CHSSIZ            | <7:0>             |                   |                  |                  |  |

# REGISTER 9-12: DCHxSSIZ: DMA CHANNEL 'x' SOURCE SIZE REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

## bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

1111111111111111 = 65,535 byte source size

# **REGISTER 9-13: DCHxDSIZ: DMA CHANNEL 'x' DESTINATION SIZE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

|              | —                 | _                 | —                 | _                 | _                 | —                 | _                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | —                 | _                 | —                 | _                | —                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         |                   | CHDSIZ<15:8>      |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | CHDSIZ            | <7:0>             |                   |                  |                  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

# 16.1 Output Compare Control Registers

# TABLE 16-1: OUTPUT COMPARE 1-OUTPUT COMPARE 5 REGISTER MAP

| ess                         |                                 |                   | Bits  |       |       |       |       |       |      |       |          |      |      |       |        |      |          |      |              |

|-----------------------------|---------------------------------|-------------------|-------|-------|-------|-------|-------|-------|------|-------|----------|------|------|-------|--------|------|----------|------|--------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range         | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7     | 22/6 | 21/5 | 20/4  | 19/3   | 18/2 | 17/1     | 16/0 | All Resets   |

|                             | OC1CON                          | 31:16             | —     | —     | —     | —     | —     | —     | —    | _     | —        | —    | —    | —     | —      |      | —        | -    | 0000         |

| 0000                        | 001001                          | 15:0              | ON    | —     | SIDL  | —     | —     | —     |      | —     | —        | —    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3010                        | OC1R                            | 31:16<br>15:0     |       |       |       |       |       |       |      | OC1R  | <31:0>   |      |      |       |        |      |          |      | xxxx         |

| 3020                        | OC1RS                           | 31:16<br>15:0     |       |       |       |       |       |       |      | OC1RS | \$<31:0> |      |      |       |        |      |          |      | xxxx         |

| 0000                        | 00000                           | 31:16             | —     | _     | _     | _     | _     | _     |      | _     | —        | —    | _    | —     | _      | _    | —        | —    | 0000         |

| 3200                        | OC2CON                          | 15:0              | ON    | _     | SIDL  | _     | _     | _     | _    | _     | _        | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3210                        | OC2R                            | 31:16             |       |       |       |       |       |       |      | OC2R  | ~21.0>   |      |      |       |        |      |          |      | xxxx         |

| 3210                        | UCZR                            | 15:0              |       |       |       |       |       |       |      | UCZR  | <31.0>   |      |      |       |        |      |          |      | xxxx         |

| 3220                        | OC2RS                           | 31:16             |       |       |       |       |       |       |      | OC2RS | 2-31-05  |      |      |       |        |      |          |      | XXXX         |

| 3220                        | 00283                           | 15:0              |       |       |       |       |       |       |      | UCZRO | 5<31.02  |      |      |       |        |      |          |      | XXXX         |

| 3400                        | OC3CON                          | 31:16             | _     | _     | _     | _     | _     | _     | _    | _     | _        | _    | _    | _     | _      |      | —        |      | 0000         |

| 3400                        | 003001                          | 15:0              | ON    | _     | SIDL  | _     | _     | _     | _    | _     | -        | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3410                        | OC3R                            | 31:16<br>15:0     |       |       |       |       |       |       |      | OC3R  | <31:0>   |      |      |       |        |      |          |      | XXXX<br>XXXX |

| 3420                        | OC3RS                           | 31:16             |       |       |       |       |       |       |      | OC3R8 | 221.05   |      |      |       |        |      |          |      | XXXX         |

| 3420                        | 00383                           | 15:0              |       |       |       |       |       |       |      | UCSRC | 5-51.0-  |      |      |       |        |      |          |      | XXXX         |

| 3600                        | OC4CON                          | 31:16             | —     | _     | _     | _     | _     | _     | _    | _     | —        | _    | _    | —     | —      | _    | —        | _    | 0000         |

| 3000                        | 004001                          | 15:0              | ON    | _     | SIDL  | _     | _     | _     | _    | _     | -        | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3610                        | OC4R                            | 31:16             |       |       |       |       |       |       |      | OC4R  | <31.0>   |      |      |       |        |      |          |      | XXXX         |

| 3010                        | 0041                            | 15:0              |       |       |       |       |       |       |      | 0041  | -01.02   |      |      |       |        |      |          |      | xxxx         |

| 3620                        | OC4RS                           | 31:16             |       |       |       |       |       |       |      | OC4RS | 221.05   |      |      |       |        |      |          |      | xxxx         |

| 3020                        | 00410                           | 15:0              |       |       |       |       |       |       |      | 00400 | 0-01.0-  |      |      |       |        |      |          |      | xxxx         |

| 3800                        | OC5CON                          | 31:16             | -     | _     | —     | _     | _     | _     | _    | _     | -        | _    | —    | —     | —      |      | —        |      | 0000         |

| 3000                        | 000001                          | 15:0              | ON    | —     | SIDL  | —     | —     | —     | —    | —     | —        | —    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3810                        | OC5R                            | 31:16             |       |       |       |       |       |       |      | OC5R  | <31.0>   |      |      |       |        |      |          |      | XXXX         |

| 3010                        | 0000                            | 15:0              |       |       |       |       |       |       |      | OUJK  | -01.02   |      |      |       |        |      |          |      | xxxx         |

| 3820                        | OC5RS                           | 31:16             |       |       |       |       |       |       |      | OC5RS |          |      |      |       |        |      |          |      | xxxx         |

| 3020                        | 00010                           | 15 <sup>.</sup> 0 |       |       |       |       |       |       |      | 00000 | -01.02   |      |      |       |        |      |          |      | xxxx         |

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

# 27.2 Configuration Registers

# TABLE 27-1: DEVCFG: DEVICE CONFIGURATION WORD SUMMARY

| ess (                       |                  |           |                       |          |         |          |       |          |            | Bits                |        |        |           |       |        |           |             |        | ú         |

|-----------------------------|------------------|-----------|-----------------------|----------|---------|----------|-------|----------|------------|---------------------|--------|--------|-----------|-------|--------|-----------|-------------|--------|-----------|

| Virtual Address<br>(BFC0_#) | Register<br>Name | Bit Range | 31/15                 | 30/14    | 29/13   | 28/12    | 27/11 | 26/10    | 25/9       | 24/8                | 23/7   | 22/6   | 21/5      | 20/4  | 19/3   | 18/2      | 17/1        | 16/0   | All Reset |

|                             | DEVCFG3          | 31:16     | FVBUSONIO             | FUSBIDIO | IOL1WAY | PMDL1WAY | -     | —        | _          | —                   | -      | —      | —         | —     | —      | —         | —           | _      | xxxx      |

| UDFU                        | DEVCEGS          | 15:0      |                       |          |         |          |       |          |            | USERID<1            | 15:0>  |        |           |       |        |           |             |        | xxxx      |

|                             | DEVCFG2          | 31:16     | _                     | —        | _       | —        | —     | —        | _          |                     | —      | _      | —         | _     | _      | FP        | LLODIV<2:   | 0>     | xxxx      |

| 0014                        |                  | 15:0      | UPLLEN <sup>(1)</sup> |          |         | —        | _     | UPL      | LIDIV<2:0> | <sub>&gt;</sub> (1) | _      | FI     | PLLMUL<2: | 0>    | _      | FF        | PLLIDIV<2:0 | )>     | xxxx      |

|                             | DEVCFG1          | 31:16     |                       |          |         | —        | _     | _        | FWDTWI     | NSZ<1:0>            | FWDTEN | WINDIS | _         |       | ١      | WDTPS<4:0 | >           |        | xxxx      |

|                             |                  | 15:0      | FCKSM                 | <1:0>    | FPBD    | IV<1:0>  | _     | OSCIOFNC | POSCM      | OD<1:0>             | IESO   | _      | FSOSCEN   |       | _      | F         | NOSC<2:0>   | >      | xxxx      |

|                             | DEVCFG0          | 31:16     | _                     | —        | _       | CP       | —     | —        | _          | BWP                 | —      | _      | _         | _     | _      | F         | WP<8:6>(2)  | )      | xxxx      |

| UBFC                        |                  | 15:0      |                       |          | PWP<    | <5:0>    |       |          |            |                     | _      | _      | _         | ICESE | L<1:0> | JTAGEN    | DEBUG       | G<1:0> | xxxx      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This bit is only available on PIC32MX2XX devices.

2: PWP<8:7> are only available on devices with 256 KB of Flash.

# TABLE 27-2: DEVICE ID, REVISION, AND CONFIGURATION SUMMARY

| ess                         | Bits                  |           |       |       |        |         |       |       |      |       | (1)     |       |         |      |        |      |      |       |                     |

|-----------------------------|-----------------------|-----------|-------|-------|--------|---------|-------|-------|------|-------|---------|-------|---------|------|--------|------|------|-------|---------------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15 | 30/14 | 29/13  | 28/12   | 27/11 | 26/10 | 25/9 | 24/8  | 23/7    | 22/6  | 21/5    | 20/4 | 19/3   | 18/2 | 17/1 | 16/0  | All Resets          |

| F220                        | DEVID                 | 31:16     |       | VER   | <3:0>  |         |       |       |      |       |         | DEVID | <27:16> |      |        |      |      |       | xxxx <sup>(1)</sup> |

| F220                        | DEVID                 | 15:0      |       |       |        |         |       |       |      | DEVID | <15:0>  |       |         |      |        |      |      |       | xxxx <sup>(1)</sup> |

| F000                        |                       | 31:16     | -     | _     | _      | _       | _     | _     | _    | _     | _       | _     | _       | _    | _      | _    | _    | _     | 0000                |

|                             | CFGCON                | 15:0      |       | —     | IOLOCK | PMDLOCK | _     | _     | _    | _     | —       | _     | _       | _    | JTAGEN | _    | _    | TDOEN | 000B                |

| F220                        | SYSKEY <sup>(3)</sup> | 31:16     |       |       |        |         |       |       |      | SYSKE | /~31.05 |       |         |      |        |      |      |       | 0000                |

| F230                        | STORET                | 15:0      |       |       |        |         |       |       |      | SISKE | 1~51.02 |       |         |      |        |      |      |       | 0000                |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset values are dependent on the device variant.

# REGISTER 27-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

bit 18-10 **PWP<8:0>:** Program Flash Write-Protect bits<sup>(3)</sup>

| DIT 18-10 | PWP<8:0>: Program Flash Write-Protect bits <sup>30</sup>                                                       |

|-----------|----------------------------------------------------------------------------------------------------------------|

|           | Prevents selected program Flash memory pages from being modified during code execution.<br>11111111 = Disabled |

|           | 111111110 = Memory below 0x0400 address is write-protected                                                     |

|           | 111111101 = Memory below 0x0400 address is write-protected                                                     |

|           | 111111100 = Memory below 0x0000 address is write-protected                                                     |

|           | 111111001 = Memory below 0x0000 address is write-protected                                                     |

|           | 111111010 = Memory below 0x1000 (44) address is write-protected                                                |

|           | 111111001 = Memory below 0x1400 address is write-protected                                                     |

|           | 111111000 = Memory below 0x1000 address is write-protected                                                     |

|           | 111110111 = Memory below 0x2000 (8K) address is write-protected                                                |

|           | 111110110 = Memory below 0x2400 address is write-protected                                                     |

|           | 111110101 = Memory below 0x2800 address is write-protected                                                     |

|           | 111110100 = Memory below 0x2C00 address is write-protected                                                     |

|           | 111110011 = Memory below 0x3000 address is write-protected                                                     |

|           | 111110010 = Memory below 0x3400 address is write-protected                                                     |

|           | 111110001 = Memory below 0x3800 address is write-protected                                                     |

|           | 111110000 = Memory below 0x3C00 address is write-protected                                                     |

|           | 111101111 = Memory below 0x4000 (16K) address is write-protected                                               |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | •<br>110111111 = Memory below 0x10000 (64K) address is write-protected                                         |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | 101111111 = Memory below 0x20000 (128K) address is write-protected                                             |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | 011111111 = Memory below 0x40000 (256K) address is write-protected                                             |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | 00000000 = All possible memory is write-protected                                                              |

|           |                                                                                                                |

| bit 9-5   | Reserved: Write '1'                                                                                            |

| bit 4-3   | ICESEL<1:0>: In-Circuit Emulator/Debugger Communication Channel Select bits <sup>(2)</sup>                     |

|           | 11 = PGEC1/PGED1 pair is used                                                                                  |

|           | 10 = PGEC2/PGED2 pair is used                                                                                  |

|           | 01 = PGEC3/PGED3 pair is used                                                                                  |

|           | 00 = PGEC4/PGED4 pair is used <sup>(2)</sup>                                                                   |

| bit 2     | JTAGEN: JTAG Enable bit <sup>(1)</sup>                                                                         |

| bit 2     | 1 = JTAG is enabled                                                                                            |

|           | 0 = JTAG is disabled                                                                                           |

| bit 1-0   | <b>DEBUG&lt;1:0&gt;:</b> Background Debugger Enable bits (forced to '11' if code-protect is enabled)           |

|           |                                                                                                                |

|           | 1x = Debugger is disabled                                                                                      |

|           | 0x = Debugger is enabled                                                                                       |

| Note 1:   | This bit sets the value for the JTAGEN bit in the CFGCON register.                                             |

|           | -                                                                                                              |

| 2:        | The PGEC4/PGED4 pin pair is not available on all devices. Refer to the " <b>Pin Diagrams</b> " section for     |

|           | availability.                                                                                                  |

| -         |                                                                                                                |

3: The PWP<8:7> bits are only available on devices with 256 KB Flash.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.04        | R/P               | R/P               | R/P               | R/P               | r-1               | r-1               | r-1              | r-1              |  |  |  |  |  |

| 31:24        | FVBUSONIO         | FUSBIDIO          | IOL1WAY           | PMDL1WAY          | _                 |                   | _                | _                |  |  |  |  |  |

| 23:16        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |  |  |  |  |  |

| 23.10        | —                 | —                 | _                 | —                 | _                 |                   | -                | —                |  |  |  |  |  |

| 15.0         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |  |  |  |

| 15:8         |                   |                   |                   | USERID<1          | 5:8>              |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |  |  |  |

| 7:0          |                   | USERID<7:0>       |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

## REGISTER 27-4: DEVCFG3: DEVICE CONFIGURATION WORD 3

| Legend:           | r = Reserved bit | P = Programmable bi  | t                  |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31 FVBUSONIO: USB VBUSON Selection bit

- 1 = VBUSON pin is controlled by the USB module 0 = VBUSON pin is controlled by the port function

- bit 30 **FUSBIDIO:** USB USBID Selection bit 1 = USBID pin is controlled by the USB module 0 = USBID pin is controlled by the port function

- bit 29 IOL1WAY: Peripheral Pin Select Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 28 PMDI1WAY: Peripheral Module Disable Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 27-16 Reserved: Write '1'

- bit 15-0 USERID<15:0>: User ID bits

This is a 16-bit value that is user-defined and is readable via ICSP™ and JTAG.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5     | Bit<br>28/20/12/4      | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-----------------------|------------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | —                 | _                     | —                      | _                 |                   | _                | —                |  |  |  |  |

| 22:16        | U-0               | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | —                 | —                 | -                     | —                      | _                 | _                 | -                | —                |  |  |  |  |

| 45.0         | U-0               | U-0               | R/W-0                 | R/W-0                  | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15:8         | —                 | —                 | IOLOCK <sup>(1)</sup> | PMDLOCK <sup>(1)</sup> |                   |                   |                  | —                |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0                   | U-0                    | R/W-1             | U-0               | U-1              | R/W-1            |  |  |  |  |

| 7:0          | _                 |                   |                       | _                      | JTAGEN            |                   | _                | TDOEN            |  |  |  |  |

## **REGISTER 27-5: CFGCON: CONFIGURATION CONTROL REGISTER**

# Legend:

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-14 Unimplemented: Read as '0'

- bit 13 IOLOCK: Peripheral Pin Select Lock bit<sup>(1)</sup>

- 1 = Peripheral Pin Select is locked. Writes to PPS registers is not allowed.

- 0 = Peripheral Pin Select is not locked. Writes to PPS registers is allowed.

- bit 12 PMDLOCK: Peripheral Module Disable bit<sup>(1)</sup>

- 1 = Peripheral module is locked. Writes to PMD registers is not allowed.

- 0 = Peripheral module is not locked. Writes to PMD registers is allowed.

#### bit 11-4 Unimplemented: Read as '0'

- bit 3 JTAGEN: JTAG Port Enable bit

- 1 = Enable the JTAG port

- 0 = Disable the JTAG port

- bit 2-1 Unimplemented: Read as '1'

- bit 0 **TDOEN:** TDO Enable for 2-Wire JTAG bit

- 1 = 2-wire JTAG protocol uses TDO

- 0 = 2-wire JTAG protocol does not use TDO

- Note 1: To change this bit, the unlock sequence must be performed. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

NOTES:

| TABLE 30-0.      |                        |               |                                                                                                                                                                                                                                                                                        |                     |                 |  |  |  |  |  |

|------------------|------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|--|--|--|--|--|

| DC CHARACT       | ERISTICS               |               | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                     |                 |  |  |  |  |  |

| Parameter<br>No. | Typical <sup>(2)</sup> | Max.          | Units                                                                                                                                                                                                                                                                                  |                     | Conditions      |  |  |  |  |  |

| Idle Current (I  | DLE): Core Of          | f, Clock on E | Base Current                                                                                                                                                                                                                                                                           | (Notes 1, 4)        |                 |  |  |  |  |  |

| DC30a            | 1                      | 1.5           | mA                                                                                                                                                                                                                                                                                     |                     | 4 MHz (Note 3)  |  |  |  |  |  |

| DC31a            | 2                      | 3             | mA                                                                                                                                                                                                                                                                                     |                     | 10 MHz          |  |  |  |  |  |

| DC32a            | 4                      | 6             | mA                                                                                                                                                                                                                                                                                     |                     | 20 MHz (Note 3) |  |  |  |  |  |

| DC33a            | 5.5                    | 8             | mA                                                                                                                                                                                                                                                                                     |                     | 30 MHz (Note 3) |  |  |  |  |  |

| DC34a            | 7.5                    | 11            | mA                                                                                                                                                                                                                                                                                     |                     | 40 MHz          |  |  |  |  |  |

| DC37a            | 100                    | _             | μA                                                                                                                                                                                                                                                                                     | -40°C LPRC (31 kHz) |                 |  |  |  |  |  |

| DC37b            | 250                    | _             | μA                                                                                                                                                                                                                                                                                     | +25°C 3.3V (Note 3) |                 |  |  |  |  |  |

| DC37c            | 380                    |               | μA                                                                                                                                                                                                                                                                                     | JA +85°C            |                 |  |  |  |  |  |

## TABLE 30-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

**Note 1:** The test conditions for IIDLE current measurements are as follows:

Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

OSC2/CLKO is configured as an I/O input pin

- UCD DLL as sillator is dischard if the LLCD readule is implemented

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Idle mode (CPU core Halted), and SRAM data memory Wait states = 1  $\,$

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- 4: IIDLE electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

|               |         |                                                         | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) |                        |            |       |                                                   |  |  |  |  |

|---------------|---------|---------------------------------------------------------|-----------------------------------------------------------------------|------------------------|------------|-------|---------------------------------------------------|--|--|--|--|

|               | ARACTER |                                                         | Operating tempe                                                       |                        |            |       | C for Industrial<br>C for V-temp                  |  |  |  |  |

| Param.<br>No. | Symbol  | Characteristics                                         | Min.                                                                  | Typical <sup>(1)</sup> | Max.       | Units | Conditions                                        |  |  |  |  |

|               | VIL     | Input Low Voltage                                       |                                                                       |                        |            |       |                                                   |  |  |  |  |

| DI10          |         | I/O Pins with PMP                                       | Vss                                                                   | —                      | 0.15 Vdd   | V     |                                                   |  |  |  |  |

|               |         | I/O Pins                                                | Vss                                                                   | —                      | 0.2 Vdd    | V     |                                                   |  |  |  |  |

| DI18          |         | SDAx, SCLx                                              | Vss                                                                   | _                      | 0.3 Vdd    | V     | SMBus disabled<br>(Note 4)                        |  |  |  |  |

| DI19          |         | SDAx, SCLx                                              | Vss                                                                   | —                      | 0.8        | V     | SMBus enabled<br>(Note 4)                         |  |  |  |  |

|               | VIH     | Input High Voltage                                      |                                                                       |                        |            |       |                                                   |  |  |  |  |

| DI20          |         | I/O Pins not 5V-tolerant <sup>(5)</sup>                 | 0.65 VDD                                                              | —                      | Vdd        | V     | (Note 4,6)                                        |  |  |  |  |

|               |         | I/O Pins 5V-tolerant with<br>PMP <sup>(5)</sup>         | 0.25 VDD + 0.8V                                                       | —                      | 5.5        | V     | (Note 4,6)                                        |  |  |  |  |

|               |         | I/O Pins 5V-tolerant <sup>(5)</sup>                     | 0.65 VDD                                                              | —                      | 5.5        | V     |                                                   |  |  |  |  |

| DI28          |         | SDAx, SCLx                                              | 0.65 VDD                                                              | _                      | 5.5        | V     | SMBus disabled<br>(Note 4,6)                      |  |  |  |  |

| DI29          |         | SDAx, SCLx                                              | 2.1                                                                   | _                      | 5.5        | V     | SMBus enabled,<br>2.3V ≤ VPIN ≤ 5.5<br>(Note 4,6) |  |  |  |  |

| DI30          | ICNPU   | Change Notification<br>Pull-up Current                  | _                                                                     | —                      | -50        | μA    | VDD = 3.3V, VPIN = VSS<br>(Note 3,6)              |  |  |  |  |

| DI31          | ICNPD   | Change Notification<br>Pull-down Current <sup>(4)</sup> | _                                                                     | —                      | -50        | μA    | VDD = 3.3V, VPIN = VDD                            |  |  |  |  |

|               | lı∟     | Input Leakage Current<br>(Note 3)                       |                                                                       |                        |            |       |                                                   |  |  |  |  |

| DI50          |         | I/O Ports                                               | _                                                                     | _                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD$ ,<br>Pin at high-impedance |  |  |  |  |

| DI51          |         | Analog Input Pins                                       | _                                                                     | _                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance  |  |  |  |  |

| DI55          |         | MCLR <sup>(2)</sup>                                     | —                                                                     | _                      | <u>+</u> 1 | μA    | $Vss \leq V PIN \leq V DD$                        |  |  |  |  |

| DI56          |         | OSC1                                                    | _                                                                     | _                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD,$<br>XT and HS modes        |  |  |  |  |

# TABLE 30-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Pin Diagrams" section for the 5V-tolerant pins.

- 6: The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

# TABLE 30-14: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| DC CHA        |         | STICS                                                       | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |                    |       |                                                                 |  |  |  |  |

|---------------|---------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|-------|-----------------------------------------------------------------|--|--|--|--|

| Param.<br>No. | Symbol  | Characteristics                                             | Min.                                                                                                                                                                                                                                                                                   | Тур. | Max.               | Units | Comments                                                        |  |  |  |  |

| D312          | TSET    | Internal 4-bit DAC<br>Comparator Reference<br>Settling time | _                                                                                                                                                                                                                                                                                      | _    | 10                 | μs    | See Note 1                                                      |  |  |  |  |

| D313          | DACREFH | CVREF Input Voltage                                         | AVss                                                                                                                                                                                                                                                                                   | _    | AVDD               | V     | CVRSRC with CVRSS = 0                                           |  |  |  |  |

|               |         | Reference Range                                             | VREF-                                                                                                                                                                                                                                                                                  | _    | VREF+              | V     | CVRSRC with CVRSS = 1                                           |  |  |  |  |

| D314          | DVREF   | CVREF Programmable<br>Output Range                          | 0                                                                                                                                                                                                                                                                                      | _    | 0.625 x<br>DACREFH | V     | 0 to 0.625 DACREFH with<br>DACREFH/24 step size                 |  |  |  |  |

|               |         |                                                             | 0.25 x<br>DACREFH                                                                                                                                                                                                                                                                      | _    | 0.719 x<br>DACREFH | V     | 0.25 x DACREFH to 0.719<br>DACREFH with<br>DACREFH/32 step size |  |  |  |  |

| D315          | DACRES  | Resolution                                                  | —                                                                                                                                                                                                                                                                                      | _    | DACREFH/24         |       | CVRCON <cvrr> = 1</cvrr>                                        |  |  |  |  |

|               |         |                                                             | _                                                                                                                                                                                                                                                                                      | —    | DACREFH/32         | _     | CVRCON <cvrr> = 0</cvrr>                                        |  |  |  |  |

| D316          | DACACC  | Absolute Accuracy <sup>(2)</sup>                            |                                                                                                                                                                                                                                                                                        | _    | 1/4                | LSB   | DACREFH/24,<br>CVRCON <cvrr> = 1</cvrr>                         |  |  |  |  |

|               |         |                                                             |                                                                                                                                                                                                                                                                                        | _    | 1/2                | LSB   | DACREFH/32,<br>CVRCON <cvrr> = 0</cvrr>                         |  |  |  |  |

**Note 1:** Settling time was measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but is not tested in manufacturing.

**2:** These parameters are characterized but not tested.

#### TABLE 30-15: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHA        | RACTERIS                                  | STICS | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |         |      |       |                                                                                                    |  |  |  |

|---------------|-------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|----------------------------------------------------------------------------------------------------|--|--|--|

| Param.<br>No. | Symbol Characteristics                    |       |                                                                                                                                                                                                                                                                                       | Typical | Max. | Units | Comments                                                                                           |  |  |  |

| D321          | D321 CEFC External Filter Capacitor Value |       | 8                                                                                                                                                                                                                                                                                     | 10      |      | μF    | Capacitor must be low series<br>resistance (1 ohm). Typical<br>voltage on the VCAP pin is<br>1.8V. |  |  |  |

## TABLE 30-41: CTMU CURRENT SOURCE SPECIFICATIONS

| DC CHARACTERISTICS  |        |                                                    | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |       |      |       |                                  |  |

|---------------------|--------|----------------------------------------------------|------------------------------------------------------|-------|------|-------|----------------------------------|--|

| Param<br>No.        | Symbol | Characteristic                                     | Min.                                                 | Тур.  | Max. | Units | Conditions                       |  |

| CTMU CURRENT SOURCE |        |                                                    |                                                      |       |      |       |                                  |  |

| CTMUI1              | Ιουτ1  | Base Range <sup>(1)</sup>                          | _                                                    | 0.55  | _    | μA    | CTMUCON<9:8> = 01                |  |

| CTMUI2              | Ιουτ2  | 10x Range <sup>(1)</sup>                           | _                                                    | 5.5   |      | μA    | CTMUCON<9:8> = 10                |  |

| CTMUI3              | Ιουτ3  | 100x Range <sup>(1)</sup>                          | _                                                    | 55    |      | μA    | CTMUCON<9:8> = 11                |  |

| CTMUI4              | IOUT4  | 1000x Range <sup>(1)</sup>                         | _                                                    | 550   |      | μA    | CTMUCON<9:8> = 00                |  |

| CTMUFV1             | VF     | Temperature Diode Forward Voltage <sup>(1,2)</sup> | —                                                    | 0.598 | _    | V     | TA = +25°C,<br>CTMUCON<9:8> = 01 |  |

|                     |        |                                                    | _                                                    | 0.658 | _    | V     | TA = +25°C,<br>CTMUCON<9:8> = 10 |  |

|                     |        |                                                    | —                                                    | 0.721 |      | V     | TA = +25°C,<br>CTMUCON<9:8> = 11 |  |

| CTMUFV2             | VFVR   | Temperature Diode Rate of Change <sup>(1,2)</sup>  | —                                                    | -1.92 |      | mV/ºC | CTMUCON<9:8> = 01                |  |

|                     |        |                                                    | _                                                    | -1.74 |      | mV/ºC | CTMUCON<9:8> = 10                |  |

|                     |        |                                                    | _                                                    | -1.56 |      | mV/ºC | CTMUCON<9:8> = 11                |  |

**Note 1:** Nominal value at center point of current trim range (CTMUCON<15:10> = 000000).

**2:** Parameters are characterized but not tested in manufacturing. Measurements taken with the following conditions:

- VREF+ = AVDD = 3.3V

- ADC module configured for conversion speed of 500 ksps

- All PMD bits are cleared (PMDx = 0)

- Executing a while(1) statement

- Device operating from the FRC with no PLL

- **3:** The CTMU module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

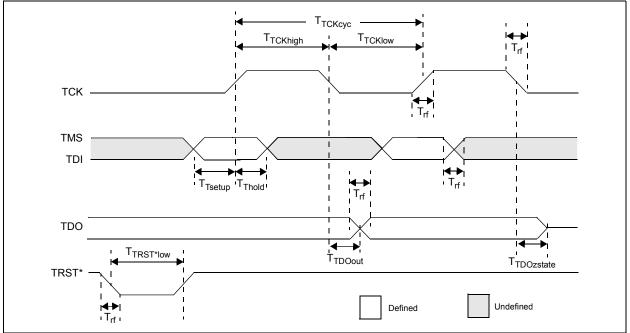

# FIGURE 30-23: EJTAG TIMING CHARACTERISTICS

## TABLE 30-42: EJTAG TIMING REQUIREMENTS

| AC CHARACTERISTICS |            |                                                  | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |            |  |

|--------------------|------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|

| Param.<br>No.      | Symbol     | Description <sup>(1)</sup>                       | Min.                                                                                                                                                                                                                                                                                | Max. | Units | Conditions |  |

| EJ1                | Ттсксус    | TCK Cycle Time                                   | 25                                                                                                                                                                                                                                                                                  |      | ns    | _          |  |

| EJ2                | Ттскнідн   | TCK High Time                                    | 10                                                                                                                                                                                                                                                                                  | _    | ns    | —          |  |

| EJ3                | TTCKLOW    | TCK Low Time                                     | 10                                                                                                                                                                                                                                                                                  | _    | ns    | _          |  |

| EJ4                | TTSETUP    | TAP Signals Setup Time Before<br>Rising TCK      | 5                                                                                                                                                                                                                                                                                   | _    | ns    | _          |  |

| EJ5                | TTHOLD     | TAP Signals Hold Time After<br>Rising TCK        | 3                                                                                                                                                                                                                                                                                   | -    | ns    | —          |  |

| EJ6                | Ττροουτ    | TDO Output Delay Time from<br>Falling TCK        | -                                                                                                                                                                                                                                                                                   | 5    | ns    | —          |  |

| EJ7                | TTDOZSTATE | TDO 3-State Delay Time from<br>Falling TCK       | _                                                                                                                                                                                                                                                                                   | 5    | ns    | _          |  |