Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 256КВ (256К х 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx170f256dt-v-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 5: PIN NAMES FOR 28-PIN GENERAL PURPOSE DEVICES

### 28-PIN QFN (TOP VIEW)<sup>(1,2,3.4)</sup>

PIC32MX110F016B PIC32MX120F032B PIC32MX130F064B PIC32MX130F256B PIC32MX150F128B PIC32MX170F256B

28

1

| Pin # | Full Pin Name                         | Pin # | Full Pin Name                                  |

|-------|---------------------------------------|-------|------------------------------------------------|

| 1     | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0  | 15    | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 2     | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1 | 16    | Vss                                            |

| 3     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2  | 17    | VCAP                                           |

| 4     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3    | 18    | PGED2/RPB10/CTED11/PMD2/RB10                   |

| 5     | Vss                                   | 19    | PGEC2/TMS/RPB11/PMD1/RB11                      |

| 6     | OSC1/CLKI/RPA2/RA2                    | 20    | AN12/PMD0/RB12                                 |

| 7     | OSC2/CLKO/RPA3/PMA0/RA3               | 21    | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 8     | SOSCI/RPB4/RB4                        | 22    | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 9     | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4        | 23    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 10    | Vdd                                   | 24    | AVss                                           |

| 11    | PGED3/RPB5/PMD7/RB5                   | 25    | AVDD                                           |

| 12    | PGEC3/RPB6/PMD6/RB6                   | 26    | MCLR                                           |

| 13    | TDI/RPB7/CTED3/PMD5/INT0/RB7          | 27    | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          |

| 14    | TCK/RPB8/SCL1/CTED10/PMD4/RB8         | 28    | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                |

1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: Shaded pins are 5V tolerant.

#### TABLE 6: PIN NAMES FOR 28-PIN USB DEVICES

## 28-PIN QFN (TOP VIEW)<sup>(1,2,3,4)</sup>

PIC32MX210F016B PIC32MX220F032B PIC32MX230F064B PIC32MX230F256B PIC32MX250F128B PIC32MX250F128B

28

1

| Pin # | Full Pin Name                              | Pin # | Full Pin Name                                    |

|-------|--------------------------------------------|-------|--------------------------------------------------|

| 1     | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0  | 15    | TDO/RPB9/SDA1/CTED4/PMD3/RB9                     |

| 2     | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1 | 16    | Vss                                              |

| 3     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2  | 17    | VCAP                                             |

| 4     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3    | 18    | PGED2/RPB10/D+/CTED11/RB10                       |

| 5     | Vss                                        | 19    | PGEC2/RPB11/D-/RB11                              |

| 6     | OSC1/CLKI/RPA2/RA2                         | 20    | VUSB3V3                                          |

| 7     | OSC2/CLKO/RPA3/PMA0/RA3                    | 21    | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 8     | SOSCI/RPB4/RB4                             | 22    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 9     | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4             | 23    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 10    | Vdd                                        | 24    | AVss                                             |

| 11    | TMS/RPB5/USBID/RB5                         | 25    | AVDD                                             |

| 12    | VBUS                                       | 26    | MCLR                                             |

| 13    | TDI/RPB7/CTED3/PMD5/INT0/RB7               | 27    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 14    | TCK/RPB8/SCL1/CTED10/PMD4/RB8              | 28    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: Shaded pins are 5V tolerant.

## TABLE 7: PIN NAMES FOR 36-PIN GENERAL PURPOSE DEVICES

## 36-PIN VTLA (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX110F016C PIC32MX120F032C PIC32MX130F064C PIC32MX150F128C

36

| Pin # | Full Pin Name                        | Pi | in # | Full Pin Name                                  |

|-------|--------------------------------------|----|------|------------------------------------------------|

| 1     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 | 1  | 19   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 2     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3   | 2  | 20   | RPC9/CTED7/RC9                                 |

| 3     | PGED4 <sup>(4)</sup> /AN6/RPC0/RC0   | 2  | 21   | Vss                                            |

| 4     | PGEC4 <sup>(4)</sup> /AN7/RPC1/RC1   | 2  | 22   | VCAP                                           |

| 5     | Vdd                                  | 2  | 23   | Vdd                                            |

| 6     | Vss                                  | 2  | 24   | PGED2/RPB10/CTED11/PMD2/RB10                   |

| 7     | OSC1/CLKI/RPA2/RA2                   | 2  | 25   | PGEC2/TMS/RPB11/PMD1/RB11                      |

| 8     | OSC2/CLKO/RPA3/PMA0/RA3              | 2  | 26   | AN12/PMD0/RB12                                 |

| 9     | SOSCI/RPB4/RB4                       | 2  | 27   | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 10    | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4       | 2  | 28   | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 11    | RPC3/RC3                             | 2  | 29   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 12    | Vss                                  | 3  | 30   | AVss                                           |

| 13    | Vdd                                  | 3  | 31   | AVdd                                           |

| 14    | Vdd                                  | 3  | 32   | MCLR                                           |

| 15    | PGED3/RPB5/PMD7/RB5                  | 3  | 33   | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          |

| 16    | PGEC3/RPB6/PMD6/RB6                  | 3  | 34   | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                |

| 17    | TDI/RPB7/CTED3/PMD5/INT0/RB7         | 3  | 35   | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0           |

| 18    | TCK/RPB8/SCL1/CTED10/PMD4/RB8        | 3  | 36   | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1          |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016C and PIC32MX120F032C devices.

5: Shaded pins are 5V tolerant.

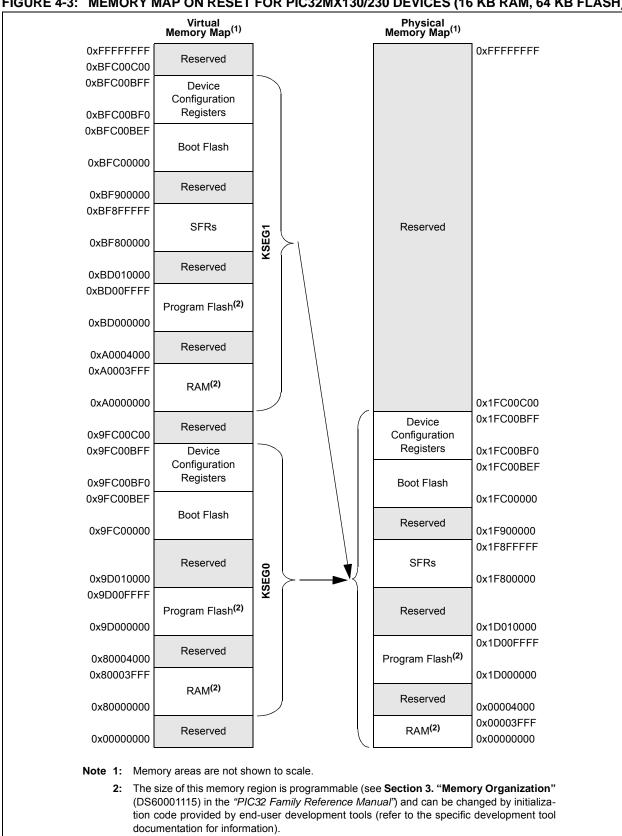

#### FIGURE 4-3: MEMORY MAP ON RESET FOR PIC32MX130/230 DEVICES (16 KB RAM, 64 KB FLASH)

## 9.1 DMA Control Registers

#### TABLE 9-1: DMA GLOBAL REGISTER MAP

| ess                         |                                 | Ô         |       |               |       |         |         |       |      | Bi   | ts   |      |      |      |      |      |           |      | s         |

|-----------------------------|---------------------------------|-----------|-------|---------------|-------|---------|---------|-------|------|------|------|------|------|------|------|------|-----------|------|-----------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14         | 29/13 | 28/12   | 27/11   | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1      | 16/0 | All Reset |

| 2000                        | DMACON                          | 31:16     | _     | _             | -     | —       | —       | _     | —    | —    | —    | -    | -    | _    | -    | -    | —         | _    | 0000      |

| 3000                        | DIVIACON                        | 15:0      | ON    | —             | _     | SUSPEND | DMABUSY | —     | _    | —    | _    | —    | —    | —    | —    | —    | —         | _    | 0000      |

| 2010                        | DMASTAT                         | 31:16     | -     | _             | —     | —       | —       | —     | —    | —    | _    | _    | _    | _    | _    | —    | —         | _    | 0000      |

| 3010                        | DIVIASTAT                       | 15:0      | -     | _             | —     | —       | —       | —     | —    | —    | _    | _    | _    | _    | RDWR | DI   | MACH<2:0> | .(2) | 0000      |

| 3020                        | DMAADDR                         | 31:16     |       | DMAADDR<31:0> |       |         |         |       |      |      |      |      |      |      |      |      |           |      |           |

| 3020                        | DIVIAADDR                       | 15:0      |       | 0000          |       |         |         |       |      |      |      |      |      |      |      |      |           |      |           |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### TABLE 9-2: DMA CRC REGISTER MAP

| ess                         |                                 | â         |       |               | -     |       |       |           |      | В      | ts       |        | -      |      |      |      |           |      |            |

|-----------------------------|---------------------------------|-----------|-------|---------------|-------|-------|-------|-----------|------|--------|----------|--------|--------|------|------|------|-----------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14         | 29/13 | 28/12 | 27/11 | 26/10     | 25/9 | 24/8   | 23/7     | 22/6   | 21/5   | 20/4 | 19/3 | 18/2 | 17/1      | 16/0 | All Resets |

| 2020                        | DCRCCON                         | 31:16     | —     | _             | BYTO  | <1:0> | WBO   | —         | —    | BITO   | _        | —      | —      | _    | _    | _    | —         | _    | 0000       |

| 3030                        | DURUUUN                         | 15:0      | —     | _             | —     |       |       | PLEN<4:0> |      |        | CRCEN    | CRCAPP | CRCTYP | —    | —    | C    | CRCCH<2:0 | >    | 0000       |

| 2040                        | DCRCDATA                        | 31:16     |       |               |       |       |       |           |      |        | TA<31:0> |        |        |      |      |      |           |      | 0000       |

| 3040                        | DURUDAIA                        | 15:0      |       |               |       |       |       |           |      | DURUDA | IA~51.02 |        |        |      |      |      |           |      | 0000       |

| 3050                        | DCRCXOR                         | 31:16     |       | 0000          |       |       |       |           |      |        |          |        |        |      |      |      |           |      |            |

| 3050                        | DUNUAUR                         | 15:0      |       | DCRCXOR<31:0> |       |       |       |           |      |        |          |        |        |      |      |      |           |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | _                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | -                 | —                 | _                 | _                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | —                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          | _                 | _                 |                   | _                 | RDWR              | Γ                 | DMACH<2:0>       | >                |

#### REGISTER 9-2: DMASTAT: DMA STATUS REGISTER

### Legend:

| 0                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-4 Unimplemented: Read as '0'

- bit 3 RDWR: Read/Write Status bit

- 1 = Last DMA bus access was a read

- 0 = Last DMA bus access was a write

- bit 2-0 **DMACH<2:0>:** DMA Channel bits These bits contain the value of the most recent active DMA channel.

### REGISTER 9-3: DMAADDR: DMA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 31:24        |                   |                   |                   | DMAADDF           | ?<31:24>          |                   |                  |                  |  |  |  |  |

| 00.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 23:16        |                   |                   |                   | DMAADDF           | ?<23:16>          |                   |                  |                  |  |  |  |  |

| 15.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8         |                   |                   |                   | DMAADD            | R<15:8>           |                   |                  |                  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          |                   |                   |                   | DMAADD            | R<7:0>            |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 DMAADDR<31:0>: DMA Module Address bits

These bits contain the address of the most recent DMA access.

#### TABLE 11-5: PORTC REGISTER MAP

| ess                         | -                                 |           |       |       |       |       |       |       |          |                       |                         | Bits                  |                       |                         |          |                       |          |          | <i>"</i>   |

|-----------------------------|-----------------------------------|-----------|-------|-------|-------|-------|-------|-------|----------|-----------------------|-------------------------|-----------------------|-----------------------|-------------------------|----------|-----------------------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1,2)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9     | 24/8                  | 23/7                    | 22/6                  | 21/5                  | 20/4                    | 19/3     | 18/2                  | 17/1     | 16/0     | All Resets |

| 6200                        | ANSELC                            | 31:16     |       | _     |       |       | —     | —     | _        |                       | _                       |                       | _                     | _                       | —        | _                     | —        |          | 0000       |

| 0200                        | ,                                 | 15:0      | —     | —     | —     | —     | —     | —     |          |                       | —                       |                       |                       | _                       | ANSC3(4) | ANSC2 <sup>(3)</sup>  | ANSC1    | ANSC0    | 000F       |

| 6210                        | TRISC                             | 31:16     | _     | _     | —     | —     | —     | —     | —        | —                     | —                       | —                     | —                     | —                       | —        | —                     | —        |          | 0000       |

| 0210                        | 11100                             | 15:0      | _     | _     | —     | —     | —     | —     | TRISC9   | TRISC8 <sup>(3)</sup> | TRISC7 <sup>(3)</sup>   | TRISC6 <sup>(3)</sup> | TRISC5 <sup>(3)</sup> | TRISC4 <sup>(3)</sup>   | TRISC3   | TRISC2 <sup>(3)</sup> | TRISC1   | TRISC0   | 03FF       |

| 6220                        | PORTC                             | 31:16     | —     | —     | —     | —     | —     | —     | _        |                       | _                       |                       | _                     |                         |          |                       |          |          | 0000       |

| 0220                        |                                   | 15:0      | _     | _     | —     | —     | —     | —     | RC9      | RC8 <sup>(3)</sup>    | RC7 <sup>(3)</sup>      | RC6 <sup>(3)</sup>    | RC5 <sup>(3)</sup>    | RC4 <sup>(3)</sup>      | RC3      | RC2 <sup>(3)</sup>    | RC1      | RC0      | xxxx       |

| 6230                        | LATC                              | 31:16     | _     | _     | —     | —     | —     | —     | _        |                       | _                       |                       |                       | _                       | —        |                       | —        | —        | 0000       |

| 0230                        | LAIC                              | 15:0      |       |       | _     | _     | _     | _     | LATC9    | LATC8 <sup>(3)</sup>  | LATC7 <sup>(3)</sup>    | LATC6 <sup>(3)</sup>  | LATC5 <sup>(3)</sup>  | LATC4 <sup>(3)</sup>    | LATC3    | LATC2 <sup>(3)</sup>  | LATC1    | LATC0    | xxxx       |

| 6240                        | ODCC                              | 31:16     |       |       | _     | _     | _     | _     | _        |                       |                         |                       |                       |                         | _        |                       | _        | _        | 0000       |

| 6240                        | ODCC                              | 15:0      |       |       | _     | _     | _     | _     | ODCC9    | ODCC8 <sup>(3)</sup>  | ODCC7 <sup>(3)</sup>    | ODCC6 <sup>(3)</sup>  | ODCC5 <sup>(3)</sup>  | ODCC4 <sup>(3)</sup>    | ODCC3    | ODCC2 <sup>(3)</sup>  | ODCC1    | ODCC0    | 0000       |

| 0050                        |                                   | 31:16     |       |       | —     | —     | —     | -     | —        | -                     | _                       | -                     | —                     | —                       | —        | —                     | —        | —        | 0000       |

| 6250                        | CNPUC                             | 15:0      | _     | _     | _     | _     | —     | —     | CNPUC9   | CNPUC8 <sup>(3)</sup> | CNPUC7 <sup>(3)</sup>   | CNPUC6 <sup>(3)</sup> | CNPUC5 <sup>(3)</sup> | CNPUC4 <sup>(3)</sup>   | CNPUC3   | CNPUC2 <sup>(3)</sup> | CNPUC1   | CNPUC0   | 0000       |

| 0000                        |                                   | 31:16     | _     | _     | _     | _     | _     | _     | —        | _                     | _                       | _                     | _                     | —                       | _        | —                     | _        | _        | 0000       |

| 6260                        | CNPDC                             | 15:0      | _     | _     | —     | —     | —     | —     | CNPDC9   | CNPDC8 <sup>(3)</sup> | CNPDC7 <sup>(3)</sup>   | CNPDC6 <sup>(3)</sup> | CNPDC5 <sup>(3)</sup> | CNPDC4 <sup>(3)</sup>   | CNPDC3   | CNPDC2 <sup>(3)</sup> | CNPDC1   | CNPDC0   | 0000       |

| 0070                        | anaana                            | 31:16     | _     | _     | —     | —     | —     | —     | _        | _                     | _                       | _                     | —                     | —                       | —        | _                     | —        | —        | 0000       |

| 6270                        | CNCONC                            | 15:0      | ON    | _     | SIDL  | —     | —     | —     | _        | _                     | _                       | _                     | _                     | —                       | —        | _                     | —        | —        | 0000       |

|                             |                                   | 31:16     | _     | _     | _     |       | —     | _     |          |                       | _                       |                       | _                     | _                       | _        | _                     | —        | —        | 0000       |

| 6280                        | CNENC                             | 15:0      | _     | _     | _     |       | —     | _     | CNIEC9   | CNIEC8(3)             | CNIEC7 <sup>(3)</sup>   | CNIEC6(3)             | CNIEC5 <sup>(3)</sup> | CNIEC4 <sup>(3)</sup>   | CNIEC3   | CNIEC2 <sup>(3)</sup> | CNIEC1   | CNIEC0   | 0000       |

|                             |                                   | 31:16     | _     | _     | _     | _     | _     | _     | _        |                       | _                       |                       | _                     | _                       | —        |                       | —        | —        | 0000       |

| 6290                        | CNSTATC                           | 15:0      | _     | _     | _     | _     | _     | _     | CNSTATC9 | CNSTATC8(3)           | CNSTATC7 <sup>(3)</sup> | CNSTATC6(3)           | CNSTATC5(3)           | CNSTATC4 <sup>(3)</sup> | CNSTATC3 | CNSTATC2(3)           | CNSTATC1 | CNSTATC0 | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: PORTC is not available on 28-pin devices.

3: This bit is only available on 44-pin devices.

4: This bit is only available on USB-enabled devices with 36 or 44 pins.

## REGISTER 12-1: T1CON: TYPE A TIMER CONTROL REGISTER (CONTINUED)

- bit 3 Unimplemented: Read as '0'

bit 2 TSYNC: Timer External Clock Input Synchronization Selection bit When TCS = 1: 1 = External clock input is synchronized 0 = External clock input is not synchronized When TCS = 0: This bit is ignored.

bit 1 TCS: Timer Clock Source Select bit 1 = External clock from TxCKI pin

- 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCmLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

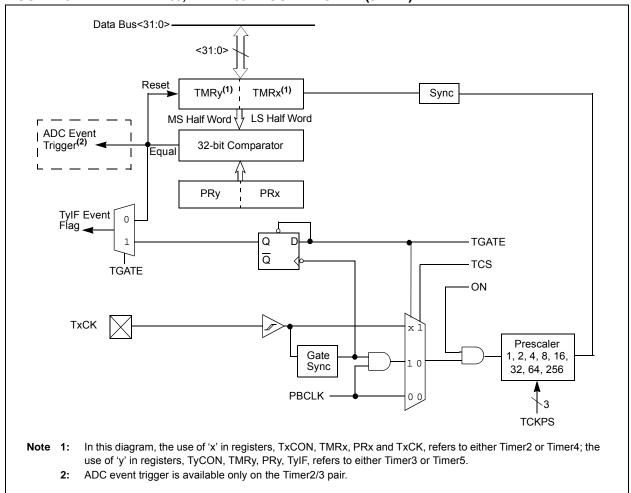

## FIGURE 13-2: TIMER2/3, TIMER4/5 BLOCK DIAGRAM (32-BIT)

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### REGISTER 17-2: SPIxCON2: SPI CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0        |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|-------------------------|

| 31:24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 31.24        | —                    | —                 | —                 | —                 | —                        | —                 | _                | —                       |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 23.10        | —                    | —                 | —                 | —                 | —                        | —                 | _                | —                       |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                   |

| 10.0         | SPISGNEXT            | —                 | —                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                  |

| 7:0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                   |

| 7:0          | AUDEN <sup>(1)</sup> | _                 | —                 | —                 | AUDMONO <sup>(1,2)</sup> | —                 | AUDMOD           | )<1:0> <sup>(1,2)</sup> |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

- 1 = Data from RX FIFO is sign extended

- 0 = Data from RX FIFO is not sign extended

- bit 14-13 Unimplemented: Read as '0'

- bit 12 **FRMERREN:** Enable Interrupt Events via FRMERR bit

- 1 = Frame Error overflow generates error events

- 0 = Frame Error does not generate error events

- bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit

- 1 = Receive overflow generates error events

- 0 = Receive overflow does not generate error events

- bit 10 SPITUREN: Enable Interrupt Events via SPITUR bit

- 1 = Transmit underrun generates error events

- 0 = Transmit underrun does not generate error events

- bit 9 IGNROV: Ignore Receive Overflow bit (for Audio Data Transmissions)

- 1 = A ROV is not a critical error; during ROV data in the FIFO is not overwritten by receive data

0 = A ROV is a critical error that stops SPI operation

- bit 8 **IGNTUR:** Ignore Transmit Underrun bit (for Audio Data Transmissions)

- 1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty

- 0 = A TUR is a critical error that stops SPI operation

- bit 7 AUDEN: Enable Audio CODEC Support bit<sup>(1)</sup>

- 1 = Audio protocol enabled

- 0 = Audio protocol disabled

- bit 6-5 Unimplemented: Read as '0'

- bit 3 AUDMONO: Transmit Audio Data Format bit<sup>(1,2)</sup>

- 1 = Audio data is mono (Each data word is transmitted on both left and right channels)

- 0 = Audio data is stereo

- bit 2 Unimplemented: Read as '0'

- bit 1-0 AUDMOD<1:0>: Audio Protocol Mode bit<sup>(1,2)</sup>

- 11 = PCM/DSP mode

- 10 = Right-Justified mode

- 01 = Left-Justified mode

- $00 = I^2S \mod$

- **Note 1:** This bit can only be written when the ON bit = 0.

- **2:** This bit is only valid for AUDEN = 1.

## 20.1 PMP Control Registers

## TABLE 20-1: PARALLEL MASTER PORT REGISTER MAP

| ess                         |                                 | 0             |       |                     |       |       |         |                                                  |        | Bi     | ts      |       |           |      |      |      |      |      |            |

|-----------------------------|---------------------------------|---------------|-------|---------------------|-------|-------|---------|--------------------------------------------------|--------|--------|---------|-------|-----------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14               | 29/13 | 28/12 | 27/11   | 26/10                                            | 25/9   | 24/8   | 23/7    | 22/6  | 21/5      | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 7000                        | PMCON                           | 31:16         | —     | _                   |       | _     | —       | —                                                | —      | —      | _       | —     | —         | -    |      | —    | _    | _    | 0000       |

| 7000                        | FINCON                          | 15:0          | ON    | _                   | SIDL  | ADRML | IX<1:0> | PMPTTL                                           | PTWREN | PTRDEN | CSF∢    | <1:0> | ALP       | -    | CS1P | —    | WRSP | RDSP | 0000       |

| 7010                        | PMMODE                          | 31:16         | _     | _                   |       |       |         |                                                  |        |        |         |       |           |      |      |      |      |      |            |

| 7010                        | FININODL                        | 15:0          | BUSY  | IRQM                | <1:0> | INCM  | <1:0>   | > _ MODE<1:0> WAITB<1:0> WAITM<3:0> WAITE<1:0> 0 |        |        |         |       | 0000      |      |      |      |      |      |            |

|                             |                                 | 31:16         | _     | _                   |       | _     | _       | _                                                | _      | _      | _       | _     | _         |      |      | _    | _    |      | 0000       |

| 7020                        | PMADDR                          | 15:0          | -     | CS1<br>ADDR14       | _     | _     | _       |                                                  |        |        |         | ŀ     | ADDR<10:0 | >    |      |      |      |      | 0000       |

| 7030                        | PMDOUT                          | 31:16<br>15:0 |       |                     |       |       |         |                                                  |        | DATAOU | T<31:0> |       |           |      |      |      |      |      | 0000       |

| 7040                        | PMDIN                           | 31:16<br>15:0 |       | DATAIN<31:0>        |       |       |         |                                                  |        |        |         |       |           |      |      |      |      |      |            |

| 7050                        |                                 | 31:16         | _     | _                   |       | _     | —       | _                                                | _      | —      | _       | —     | _         | -    | -    | _    | _    | _    | 0000       |

| 7050                        | PMAEN                           | 15:0          | —     | - PTEN14 PTEN<10:0> |       |       |         |                                                  |        | 0000   |         |       |           |      |      |      |      |      |            |

| 7060                        | PMSTAT                          | 31:16         |       | —                   |       |       | —       | —                                                | —      | —      | _       | —     | —         | —    | _    | _    | _    |      | 0000       |

| 1000                        | FINISTAT                        | 15:0          | IBF   | IBOV                | _     | _     | IB3F    | IB2F                                             | IB1F   | IB0F   | OBE     | OBUF  | —         | _    | OB3E | OB2E | OB1E | OB0E | 008F       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | _                 | —                 | _                 | _                 | —                 | _                 | _                | —                |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | —                 | —                 | _                 | _                 | —                 | _                 | _                | —                |  |  |  |  |  |

| 45.0         | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         | —                 | PTEN14            | _                 | _                 | —                 |                   | PTEN<10:8>       |                  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   |                   |                   | PTEN              | <7:0>             |                   |                  |                  |  |  |  |  |  |

## REGISTER 20-4: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-15 Unimplemented: Read as '0'

- bit 15-14 **PTEN14:** PMCS1 Address Port Enable bits

- 1 = PMA14 functions as either PMA14 or PMCS1<sup>(1)</sup>

- 0 = PMA14 functions as port I/O

- bit 13-11 Unimplemented: Read as '0'

- bit 10-2 PTEN<10:2>: PMP Address Port Enable bits

- 1 = PMA<10:2> function as PMP address lines

- 0 = PMA<10:2> function as port I/O

#### bit 1-0 PTEN<1:0>: PMALH/PMALL Address Port Enable bits

- 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL<sup>(2)</sup>

- 0 = PMA1 and PMA0 pads functions as port I/O

- Note 1: The use of this pin as PMA14 or CS1 is selected by the CSF<1:0> bits in the PMCON register.

- 2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by bits ADRMUX<1:0> in the PMCON register.

#### REGISTER 21-1: RTCCON: RTC CONTROL REGISTER (CONTINUED)

- bit 5-4 **Unimplemented:** Read as '0'

- bit 3 RTCWREN: RTC Value Registers Write Enable bit<sup>(4)</sup>

- 1 = RTC Value registers can be written to by the user

- 0 = RTC Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: RTCC Value Registers Read Synchronization bit

- 1 = RTC Value registers can change while reading, due to a rollover ripple that results in an invalid data read

If the register is read twice and results in the same data, the data can be assumed to be valid

- 0 = RTC Value registers can be read without concern about a rollover ripple

- bit 1 HALFSEC: Half-Second Status bit<sup>(5)</sup>

- 1 = Second half period of a second

- 0 = First half period of a second

- bit 0 **RTCOE:** RTCC Output Enable bit

- 1 = RTCC clock output enabled clock presented onto an I/O

- 0 = RTCC clock output disabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **3:** Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- 4: The RTCWREN bit can be set only when the write sequence is enabled.

- 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

Note: This register is reset only on a Power-on Reset (POR).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 |                     | _                 | _                 |                   | —                | _                |

| 00.40        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                   | _                 | _                 |                   | —                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 15:8         | ON <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | _                 | —                 | —                 | —                | COUT             |

| 7.0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7:0          | EVPOL             | _<1:0>            | _                   | CREF              | —                 | —                 | CCH              | <1:0>            |

#### REGISTER 23-1: CMXCON: COMPARATOR CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

- bit 14 **COE:** Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

- bit 12-9 Unimplemented: Read as '0'

- bit 8 **COUT:** Comparator Output bit

- 1 = Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 **EVPOL<1:0>:** Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

- bit 4 CREF: Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CXINA pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the CxIND pin

- 01 = Comparator inverting input is connected to the CxINC pin

- 00 = Comparator inverting input is connected to the CxINB pin

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

## 26.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to enabled or disabled peripherals:

- Control register lock sequence

- · Configuration bit select lock

#### 26.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the Configuration bit, PMDLOCK (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes.

To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 6.** "**Oscillator**" (DS60001112) in the "*PIC32 Family Reference Manual*" for details.

#### 26.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The Configuration bit, PMDL1WAY (DEVCFG3<28>), blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

#### TABLE 26-2: PERIPHERAL MODULE DISABLE REGISTER MAP

| ess                         |                                 |           |       |       |       |       |       |       |        |        | Bits |      |      |       |       |        |        |        | 6          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|--------|--------|------|------|------|-------|-------|--------|--------|--------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8   | 23/7 | 22/6 | 21/5 | 20/4  | 19/3  | 18/2   | 17/1   | 16/0   | All Resets |

| 5040                        | PMD1                            | 31:16     | —     | —     | _     | —     | _     |       | —      | —      | —    | —    | —    | —     |       | —      | —      | —      | 0000       |

| F240                        | FIVIDI                          | 15:0      | -     |       |       | CVRMD | Ι     |       | —      | CTMUMD | —    | -    |      | -     |       |        | —      | AD1MD  | 0000       |

| 5250                        | PMD2                            | 31:16     | —     | —     |       | —     | _     | _     |        | —      | —    | —    | —    | —     | -     | —      | —      | —      | 0000       |

| F250                        | FIVIDZ                          | 15:0      | —     | _     | _     | —     | _     | _     | —      | —      | _    | _    | _    | _     | _     | CMP3MD | CMP2MD | CMP1MD | 0000       |

| F260                        | PMD3                            | 31:16     | _     |       |       | _     | -     |       | _      | _      | _    |      | _    | OC5MD | OC4MD | OC3MD  | OC2MD  | OC1MD  | 0000       |

| F200                        | FIVIDS                          | 15:0      | _     |       |       | _     | -     |       | _      | _      | _    |      | _    | IC5MD | IC4MD | IC3MD  | IC2MD  | IC1MD  | 0000       |

| F270                        | PMD4                            | 31:16     | _     |       |       | _     | -     |       | _      | _      | _    |      | _    | -     |       | _      | —      | _      | 0000       |

| F270                        | F IVID4                         | 15:0      | _     |       |       | _     | -     |       | _      | _      | _    |      | _    | T5MD  | T4MD  | T3MD   | T2MD   | T1MD   | 0000       |

| F280                        | PMD5                            | 31:16     | _     |       |       | _     | -     |       | _      | USB1MD | _    |      | _    | -     |       | _      | I2C1MD | I2C1MD | 0000       |

| F200                        | FIVIDS                          | 15:0      | _     |       |       | _     | -     |       | SPI2MD | SPI1MD | _    |      | _    | -     |       | _      | U2MD   | U1MD   | 0000       |

| F200                        | PMD6                            | 31:16     | _     | —     |       | —     | _     | _     | _      | —      | —    | _    | —    | _     | _     | —      | —      | PMPMD  | 0000       |

| F290                        |                                 | 15:0      | —     | _     |       |       | _     |       | —      | _      | —    |      | —    | _     |       | —      | REFOMD | RTCCMD | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| DC CHA                                | RACTERIS               | TICS    | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                                      |                                        |  |  |  |  |  |  |

|---------------------------------------|------------------------|---------|------------------------------------------------------|------------------------------------------------------|----------------------------------------|--|--|--|--|--|--|

| Param.<br>No.                         | Typical <sup>(2)</sup> | Max.    | Units                                                | Conditions                                           |                                        |  |  |  |  |  |  |

| Power-Down Current (IPD) (Notes 1, 5) |                        |         |                                                      |                                                      |                                        |  |  |  |  |  |  |

| DC40k                                 | 44                     | 70      | μA                                                   | -40°C                                                |                                        |  |  |  |  |  |  |

| DC40I                                 | 44                     | 70      | μA                                                   | +25°C                                                | Base Power-Down Current                |  |  |  |  |  |  |

| DC40n                                 | 168                    | 259     | μA                                                   | +85°C                                                |                                        |  |  |  |  |  |  |

| DC40m                                 | 335                    | 536     | μA                                                   | +105°C                                               |                                        |  |  |  |  |  |  |

| Module                                | Differential           | Current |                                                      |                                                      |                                        |  |  |  |  |  |  |

| DC41e                                 | 5                      | 20      | μA                                                   | 3.6V                                                 | Watchdog Timer Current: AIWDT (Note 3) |  |  |  |  |  |  |

| DC42e                                 | 23                     | 50      | μA                                                   | 3.6V RTCC + Timer1 w/32 kHz Crystal: △IRTCC (Note 3) |                                        |  |  |  |  |  |  |

| DC43d                                 | 1000                   | 1100    | μA                                                   | 3.6V                                                 | ADC: ΔIADC (Notes 3,4)                 |  |  |  |  |  |  |

## TABLE 30-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** The test conditions for IPD current measurements are as follows:

Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

OSC2/CLKO is configured as an I/O input pin

• USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

• CPU is in Sleep mode, and SRAM data memory Wait states = 1

• No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set

• WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

• All I/O pins are configured as inputs and pulled to Vss

• MCLR = VDD

• RTCC and JTAG are disabled

2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

- 5: IPD electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

#### TABLE 30-33: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE) (CONTINUED)

| AC CHA        | RACTERIS | STICS             |                               | Standard Op<br>(unless othe<br>Operating te | rwise st | <b>ated)</b><br>re -40° | ons: 2.3V to 3.6V<br>$^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |

|---------------|----------|-------------------|-------------------------------|---------------------------------------------|----------|-------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No. | Symbol   | Charact           | eristics                      | Min.                                        | Max.     | Units                   | Conditions                                                                                                                 |

| IS34          | THD:STO  | Stop Condition    | 100 kHz mode                  | 4000                                        | _        | ns                      | —                                                                                                                          |

|               |          | Hold Time         | 400 kHz mode                  | 600                                         | —        | ns                      |                                                                                                                            |

|               |          |                   | 1 MHz mode<br>(Note 1)        | 250                                         |          | ns                      |                                                                                                                            |

| IS40          | TAA:SCL  | Output Valid from | 100 kHz mode                  | 0                                           | 3500     | ns                      | —                                                                                                                          |

|               |          | Clock             | 400 kHz mode                  | 0                                           | 1000     | ns                      |                                                                                                                            |

|               |          |                   | 1 MHz mode<br><b>(Note 1)</b> | 0                                           | 350      | ns                      |                                                                                                                            |

| IS45          | TBF:SDA  | Bus Free Time     | 100 kHz mode                  | 4.7                                         | —        | μs                      | The amount of time the bus                                                                                                 |

|               |          |                   | 400 kHz mode                  | 1.3                                         |          | μS                      | must be free before a new                                                                                                  |

|               |          |                   | 1 MHz mode<br>(Note 1)        | 0.5                                         | -        | μS                      | transmission can start                                                                                                     |

| IS50          | Св       | Bus Capacitive Lo | ading                         | _                                           | 400      | pF                      | —                                                                                                                          |

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

#### TABLE 30-37: PARALLEL SLAVE PORT REQUIREMENTS

| AC CH         | ARACTE       | RISTICS                                                                          | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |      |       |            |  |  |

|---------------|--------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|--|--|

| Para<br>m.No. | Symbol       | Characteristics <sup>(1)</sup>                                                   | Min.                                                                                                                                                                                                                                                                                | Тур. | Max. | Units | Conditions |  |  |

| PS1           | TdtV2wr<br>H | Data In Valid before $\overline{WR}$ or $\overline{CS}$<br>Inactive (setup time) | 20                                                                                                                                                                                                                                                                                  |      |      | ns    | _          |  |  |

| PS2           | TwrH2dt<br>I | WR or CS Inactive to Data-In Invalid (hold time)                                 | 40                                                                                                                                                                                                                                                                                  | —    | —    | ns    | _          |  |  |

| PS3           | TrdL2dt<br>V | RD and CS Active to Data-Out Valid                                               | _                                                                                                                                                                                                                                                                                   | —    | 60   | ns    | _          |  |  |

| PS4           | TrdH2dtl     | RD Active or CS Inactive to Data-Out Invalid                                     | 0                                                                                                                                                                                                                                                                                   | —    | 10   | ns    | _          |  |  |

| PS5           | Tcs          | CS Active Time                                                                   | Трв + 40                                                                                                                                                                                                                                                                            | _    | _    | ns    | —          |  |  |

| PS6           | Twr          | WR Active Time                                                                   | Трв + 25                                                                                                                                                                                                                                                                            | _    | _    | ns    | —          |  |  |

| PS7           | Trd          | RD Active Time                                                                   | Трв + 25                                                                                                                                                                                                                                                                            | _    | —    | ns    | —          |  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

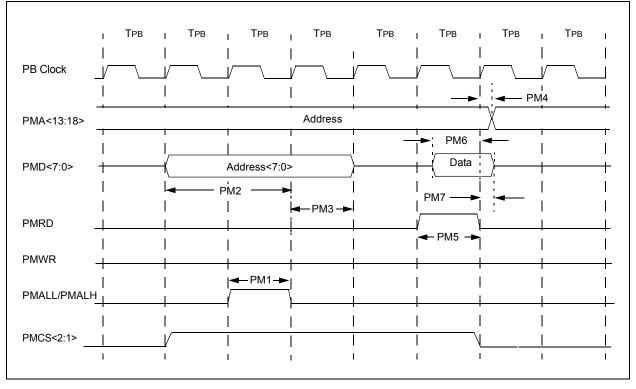

## FIGURE 30-21: PARALLEL MASTER PORT READ TIMING DIAGRAM

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

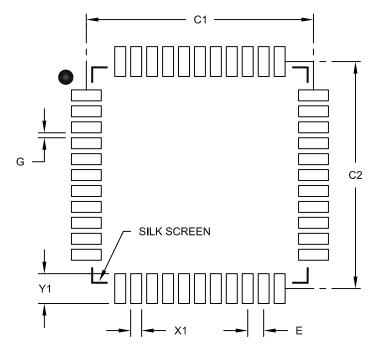

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | Units  |      |          |      |  |  |  |

|--------------------------|--------|------|----------|------|--|--|--|

| Dimension                | Limits | MIN  | NOM      | MAX  |  |  |  |

| Contact Pitch            | E      |      | 0.80 BSC |      |  |  |  |

| Contact Pad Spacing      | C1     |      | 11.40    |      |  |  |  |

| Contact Pad Spacing      | C2     |      | 11.40    |      |  |  |  |

| Contact Pad Width (X44)  | X1     |      |          | 0.55 |  |  |  |

| Contact Pad Length (X44) | Y1     |      |          | 1.50 |  |  |  |

| Distance Between Pads    | G      | 0.25 |          |      |  |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B