#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 010.00                   |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 19                                                                             |

| Program Memory Size        | 16KB (16K × 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx210f016b-i-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|              |                        | Pin Nu                                      | mber <sup>(1)</sup> |                                 |             | -                   |                                                            |

|--------------|------------------------|---------------------------------------------|---------------------|---------------------------------|-------------|---------------------|------------------------------------------------------------|

| Pin Name     | 28-pin<br>QFN          | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC           | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type      | Description                                                |

| RC0          | —                      | —                                           | 3                   | 25                              | I/O         | ST                  | PORTC is a bidirectional I/O port                          |

| RC1          | —                      | —                                           | 4                   | 26                              | I/O         | ST                  |                                                            |

| RC2          | —                      | —                                           | _                   | 27                              | I/O         | ST                  |                                                            |

| RC3          | —                      | —                                           | 11                  | 36                              | I/O         | ST                  | _                                                          |

| RC4          | —                      | —                                           | _                   | 37                              | I/O         | ST                  | _                                                          |

| RC5          | —                      |                                             |                     | 38                              | I/O         | ST                  | _                                                          |

| RC6          |                        | —                                           | _                   | 2                               | I/O         | ST                  | _                                                          |

| RC7          | —                      |                                             | —                   | 3                               | I/O         | ST                  | 4                                                          |

| RC8          | —                      | —                                           | —                   | 4                               | I/O         | ST                  | _                                                          |

| RC9          |                        | - 40                                        | 20                  | 5                               | I/O         | ST                  | Time and an element all all in must                        |

| T1CK<br>T2CK | 9<br>PPS               | 12                                          | 10                  | 34                              |             | ST                  | Timer1 external clock input                                |

| T3CK         | PPS<br>PPS             | PPS<br>PPS                                  | PPS<br>PPS          | PPS<br>PPS                      |             | ST<br>ST            | Timer2 external clock input<br>Timer3 external clock input |

| T4CK         | PPS                    | PPS                                         | PPS                 | PPS                             | 1           | ST                  | Timer4 external clock input                                |

| T5CK         | PPS                    | PPS                                         | PPS                 | PPS                             |             | ST                  | Timer5 external clock input                                |

|              | PPS                    | PPS                                         | PPS                 | PPS                             |             | ST                  | UART1 clear to send                                        |

| U1RTS        | PPS                    | PPS                                         | PPS                 | PPS                             |             | 51                  |                                                            |

| U1RX         | PPS<br>PPS             | PPS<br>PPS                                  | PPS<br>PPS          | PPS<br>PPS                      | 0           | ST                  | UART1 ready to send<br>UART1 receive                       |

| U1TX         | PPS                    | PPS                                         | PPS                 | PPS                             | -           |                     |                                                            |

|              |                        |                                             |                     |                                 | 0           |                     | UART1 transmit                                             |

| U2CTS        | PPS                    | PPS                                         | PPS                 | PPS                             | I           | ST                  | UART2 clear to send                                        |

| U2RTS        | PPS                    | PPS                                         | PPS                 | PPS                             | 0           |                     | UART2 ready to send                                        |

| U2RX         | PPS                    | PPS                                         | PPS                 | PPS                             | I           | ST                  | UART2 receive                                              |

| U2TX         | PPS                    | PPS                                         | PPS                 | PPS                             | 0           |                     | UART2 transmit                                             |

| SCK1         | 22                     | 25                                          | 28                  | 14                              | I/O         | ST                  | Synchronous serial clock input/output for SPI1             |

| SDI1         | PPS                    | PPS                                         | PPS                 | PPS                             | I           | ST                  | SPI1 data in                                               |

| SDO1         | PPS                    | PPS                                         | PPS                 | PPS                             | 0           | _                   | SPI1 data out                                              |

| SS1          | PPS                    | PPS                                         | PPS                 | PPS                             | I/O         | ST                  | SPI1 slave synchronization or frame pulse I/O              |

| SCK2         | 23                     | 26                                          | 29                  | 15                              | I/O         | ST                  | Synchronous serial clock input/output for SPI2             |

| SDI2         | PPS                    | PPS                                         | PPS                 | PPS                             |             | ST                  | SPI2 data in                                               |

| SDO2         | PPS                    | PPS                                         | PPS                 | PPS                             | 0           | _                   | SPI2 data out                                              |

| SS2          | PPS                    | PPS                                         | PPS                 | PPS                             | I/O         | ST                  | SPI2 slave synchronization or frame pulse I/O              |

| SCL1         | 14                     | 17                                          | 18                  | 44                              | I/O         | ST                  | Synchronous serial clock input/output for<br>I2C1          |

|              | ST = Schm<br>TTL = TTL | MOS compa<br>itt Trigger in<br>input buffer | put with CN         | MOS levels                      |             | O = Outp<br>PPS = P | Analog input P = Power                                     |

####

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

|                 |                             | OUT I/O D<br>Pin Nui                        |                                       |                                 |             | Í                    |                                                                                                 |

|-----------------|-----------------------------|---------------------------------------------|---------------------------------------|---------------------------------|-------------|----------------------|-------------------------------------------------------------------------------------------------|

| Pin Name        | 28-pin<br>QFN               | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC           | 36-pin<br>VTLA                        | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type       | Description                                                                                     |

| PMA0            | 7                           | 10                                          | 8                                     | 3                               | I/O         | TTL/ST               | Parallel Master Port Address bit 0 input<br>(Buffered Slave modes) and output<br>(Master modes) |

| PMA1            | 9                           | 12                                          | 10                                    | 2                               | I/O         | TTL/ST               | Parallel Master Port Address bit 1 input<br>(Buffered Slave modes) and output<br>(Master modes) |

| PMA2            |                             | _                                           |                                       | 27                              | 0           | —                    | Parallel Master Port address                                                                    |

| PMA3            |                             | _                                           | _                                     | 38                              | 0           | _                    | (Demultiplexed Master modes)                                                                    |

| PMA4            |                             | _                                           | _                                     | 37                              | 0           | _                    | 7                                                                                               |

| PMA5            |                             | _                                           | _                                     | 4                               | 0           | _                    |                                                                                                 |

| PMA6            |                             | _                                           | _                                     | 5                               | 0           | _                    | -                                                                                               |

| PMA7            |                             | _                                           | _                                     | 13                              | 0           | _                    | -                                                                                               |

| PMA8            |                             | _                                           | _                                     | 32                              | 0           | _                    | -                                                                                               |

| PMA9            |                             | _                                           | _                                     | 35                              | 0           | _                    | -                                                                                               |

| PMA10           |                             |                                             | _                                     | 12                              | 0           |                      | -                                                                                               |

| PMCS1           | 23                          | 26                                          | 29                                    | 15                              | 0           |                      | Parallel Master Port Chip Select 1 strob                                                        |

|                 | 20 <sup>(2)</sup>           | 23 <sup>(2)</sup>                           | 26 <sup>(2)</sup>                     | 10 <sup>(2)</sup>               | -           |                      | Parallel Master Port data (Demultiplexed                                                        |

| PMD0            | 1 <sup>(3)</sup>            | <br>4 <sup>(3)</sup>                        | 35 <sup>(3)</sup>                     | 21 <sup>(3)</sup>               | I/O         | TTL/ST               | Master mode) or address/data                                                                    |

|                 | 19(2)                       | 22(2)                                       | 25(2)                                 | <u>9</u> (2)                    |             |                      | (Multiplexed Master modes)                                                                      |

| PMD1            | 2(3)                        | 5 <sup>(3)</sup>                            | 36 <sup>(3)</sup>                     | 22 <sup>(3)</sup>               | I/O         | TTL/ST               |                                                                                                 |

|                 | 18(2)                       | 21 <sup>(2)</sup>                           | 24 <sup>(2)</sup>                     | 8 <sup>(2)</sup>                |             |                      | -                                                                                               |

| PMD2            | <u></u>                     | 6 <sup>(3)</sup>                            | 1 <sup>(3)</sup>                      | 23(3)                           | I/O         | TTL/ST               |                                                                                                 |

| PMD3            | 15                          | 18                                          | 19                                    | 1                               | I/O         | TTL/ST               | -                                                                                               |

| PMD4            | 10                          | 10                                          | 18                                    | 44                              | 1/O         | TTL/ST               | -                                                                                               |

| PMD5            | 13                          | 16                                          | 17                                    | 43                              | I/O         | TTL/ST               | -                                                                                               |

| PMD5<br>PMD6    | 13<br>12 <sup>(2)</sup>     | 15 <sup>(2)</sup>                           | 16 <sup>(2)</sup>                     | 43<br>42 <sup>(2)</sup>         | 1/0         | 111/31               | -                                                                                               |

| FIVIDO          | 28(3)                       | 3( <b>3</b> )                               | 34 <b>(3)</b>                         | 20(3)                           | I/O         | TTL/ST               |                                                                                                 |

| PMD7            | <u>11(2)</u>                | 14(2)                                       | 15 <sup>(2)</sup>                     | 41 <sup>(2)</sup>               |             |                      | -                                                                                               |

| PINDI           | 27 <sup>(3)</sup>           | 2 <sup>(3)</sup>                            | 33( <b>3</b> )                        | 19 <sup>(3)</sup>               | I/O         | TTL/ST               |                                                                                                 |

| PMRD            | 2/07                        | 24                                          | 27                                    | 19(1)                           | 0           |                      | Derellel Meeter Pert read stroke                                                                |

| PINIRD          | 21<br>22 <sup>(2)</sup>     | 24<br>25 <sup>(2)</sup>                     | 27<br>28 <sup>(2)</sup>               | 14 <sup>(2)</sup>               | 0           |                      | Parallel Master Port read strobe                                                                |

| PMWR            | <u></u><br>4 <sup>(3)</sup> | 25 <sup>(2)</sup><br>7 <sup>(3)</sup>       | 28 <sup>(-)</sup><br>2 <sup>(3)</sup> | 24 <sup>(3)</sup>               | 0           | —                    | Parallel Master Port write strobe                                                               |

| VBUS            | 12(3)                       | 15 <sup>(3)</sup>                           | 16 <sup>(3)</sup>                     | 42(3)                           |             | Analog               | USB bus power monitor                                                                           |

| VBUS<br>VUSB3V3 | 20 <sup>(3)</sup>           | 23(3)                                       | 26 <sup>(3)</sup>                     | 10 <sup>(3)</sup>               | P           | Analog               | USB internal transceiver supply. This pin                                                       |

| VUSBSVS         | 20.7                        | 23.7                                        | 20.7                                  | 10.7                            | Г           | _                    | must be connected to VDD.                                                                       |

| VBUSON          | 22 <sup>(3)</sup>           | 25 <sup>(3)</sup>                           | 28 <sup>(3)</sup>                     | 14 <sup>(3)</sup>               | 0           | _                    | USB Host and OTG bus power control output                                                       |

| D+              | 18 <sup>(3)</sup>           | 21 <sup>(3)</sup>                           | 24 <sup>(3)</sup>                     | 8 <sup>(3)</sup>                | I/O         | Analog               | USB D+                                                                                          |

| –<br>D-         | 19(3)                       | 22 <sup>(3)</sup>                           | 25 <sup>(3)</sup>                     | 9 <sup>(3)</sup>                | I/O         | Analog               | USB D-                                                                                          |

| Legend: C       | CMOS = CI<br>ST = Schm      | MOS compa<br>itt Trigger in<br>input buffer | atible input                          | or output                       |             | Analog =<br>O = Outp | Analog input P = Power                                                                          |

####

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

NOTES:

## 4.2 Bus Matrix Control Registers

### TABLE 4-2: BUS MATRIX REGISTER MAP

| ess (                       |                         | a         |       |                     |       |       |       |       |      |      |      | Bits         |      |           |           |           |            |          |               |

|-----------------------------|-------------------------|-----------|-------|---------------------|-------|-------|-------|-------|------|------|------|--------------|------|-----------|-----------|-----------|------------|----------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name        | Bit Range | 31/15 | 30/14               | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6         | 21/5 | 20/4      | 19/3      | 18/2      | 17/1       | 16/0     | All<br>Resets |

| 2000                        | BMXCON <sup>(1)</sup>   | 31:16     | —     | _                   | _     | _     | -     | _     | _    | _    |      | —            | _    | BMXERRIXI | BMXERRICD | BMXERRDMA | BMXERRDS   | BMXERRIS | 001F          |

| 2000                        | BINIXCON                | 15:0      |       |                     | _     | _     |       | -     |      | _    |      | BMXWSDRM     | _    | _         | -         | В         | MXARB<2:0> |          | 0041          |

| 2010                        | BMXDKPBA <sup>(1)</sup> | 31:16     | —     | _                   | _     | _     | -     | _     | _    | _    |      | —            | _    | —         | _         | _         | _          | —        | 0000          |

| 2010                        | DIVIAUNEDA              | 15:0      |       |                     |       |       |       |       |      |      | BN   | IXDKPBA<15:0 | >    |           |           |           |            |          | 0000          |

| 2020                        | BMXDUDBA <sup>(1)</sup> | 31:16     | _     | _                   | _     |       | _     | —     | _    | _    | _    | —            | _    | —         | _         | _         | _          | _        | 0000          |

|                             |                         | 15:0      |       |                     |       |       |       |       |      |      | BN   | XDUDBA<15:0  | >    |           |           |           |            |          | 0000          |

| 2030                        | BMXDUPBA <sup>(1)</sup> | 31:16     | —     | —                   | —     |       | —     | —     | —    | —    | —    | —            | —    | —         | —         | —         | —          | —        | 0000          |

| 2000                        |                         | 15:0      |       |                     |       |       |       |       |      |      | BN   | IXDUPBA<15:0 | >    |           |           |           |            |          | 0000          |

| 2040                        | BMXDRMSZ                | 31:16     |       |                     |       |       |       |       |      |      | BM   | XDRMSZ<31:0  | >    |           |           |           |            |          | xxxx          |

|                             |                         | 15:0      |       |                     |       | 1     |       |       |      | 1    |      |              |      | 1         |           |           |            |          | xxxx          |

| 2050                        | BMXPUPBA <sup>(1)</sup> | 31:16     | —     | —                   | —     |       | —     | -     | —    | _    | _    | _            | —    | —         |           | BMXPUPBA  | <19:16>    |          | 0000          |

|                             |                         | 15:0      |       | BMXPUPBA<15:0> 0000 |       |       |       |       |      | 0000 |      |              |      |           |           |           |            |          |               |

| 2060                        | BMXPFMSZ                | 31:16     |       | BMXPFMSZ<31:0>      |       |       |       |       |      | xxxx |      |              |      |           |           |           |            |          |               |

| 2000                        | 2                       | 15:0      |       |                     |       |       |       |       |      |      | xxxx |              |      |           |           |           |            |          |               |

| 2070                        | BMXBOOTSZ               | 31:16     |       | BMXBOOTSZ<31:0>     |       |       |       |       |      |      | 0000 |              |      |           |           |           |            |          |               |

|                             | # (20010E               | 15:0      |       |                     |       |       |       |       |      |      |      |              |      |           |           |           |            |          | 0C00          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

## 5.1 Flash Controller Control Registers

## TABLE 5-1: FLASH CONTROLLER REGISTER MAP

| ess                         |                        | 0         |       |                  |       |        |         |       |      | Bit       | s         |      |      |      |      |      |        |      | 6          |

|-----------------------------|------------------------|-----------|-------|------------------|-------|--------|---------|-------|------|-----------|-----------|------|------|------|------|------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range | 31/15 | 30/14            | 29/13 | 28/12  | 27/11   | 26/10 | 25/9 | 24/8      | 23/7      | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| F400                        | NVMCON <sup>(1)</sup>  | 31:16     | —     | —                | -     | —      | —       | —     | _    | -         | —         | _    | —    | _    | —    | —    | -      | -    | 0000       |

| F400                        | INVIVICOIN**           | 15:0      | WR    | WREN             | WRERR | LVDERR | LVDSTAT | _     |      | —         |           | _    | —    | _    |      | NVMO | P<3:0> |      | 0000       |

| F410                        | NVMKEY                 | 31:16     |       |                  |       |        |         |       |      | NVMKEY    | <31·0>    |      |      |      |      |      |        |      | 0000       |

| 1410                        |                        | 15:0      |       |                  |       |        |         |       |      |           | ~51.02    |      |      |      |      |      |        |      | 0000       |

| F420                        | NVMADDR <sup>(1)</sup> | 31:16     |       |                  |       |        |         |       |      | NVMADD    | ₽<31·0>   |      |      |      |      |      |        |      | 0000       |

| 1 420                       | NVINADDR               | 15:0      |       |                  |       |        |         |       |      | NVINADD   | N~51.02   |      |      |      |      |      |        |      | 0000       |

| F430                        | NVMDATA                | 31:16     |       | NV/MD ATA <24.0> |       |        |         |       |      |           |           | 0000 |      |      |      |      |        |      |            |

| 1 430                       |                        | 15:0      |       | NVMDATA<31:0>    |       |        |         |       |      |           |           | 0000 |      |      |      |      |        |      |            |

| E440                        | NVMSRCADDR             | 31:16     |       |                  |       |        |         |       |      |           |           |      | 0000 |      |      |      |        |      |            |

| 1 440                       | NVINGRCADDR            | 15:0      |       |                  |       |        |         |       | IN   | VIVIGRUAL | 011-01.02 |      |      |      |      |      |        |      | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 31:24        | —                 | —                 | _                 | —                 | _                 | —                 | -                | —                    |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 23:16        | —                 | —                 | _                 | —                 | _                 | —                 | -                | —                    |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 10.0         | _                 | —                 | _                 | —                 | _                 | —                 | _                | —                    |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |

| 7:0          | —                 | —                 | —                 | —                 | _                 | —                 | —                | SWRST <sup>(1)</sup> |

## REGISTER 6-2: RSWRST: SOFTWARE RESET REGISTER

| Legend:           | HC = Cleared by hardwa | ire                       |                    |

|-------------------|------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit       | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set       | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-1 Unimplemented: Read as '0'

- bit 0 SWRST: Software Reset Trigger bit<sup>(1)</sup> 1 = Enable Software Reset event

- 0 = No effect

- Note 1: The system unlock sequence must be performed before the SWRST bit is written. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

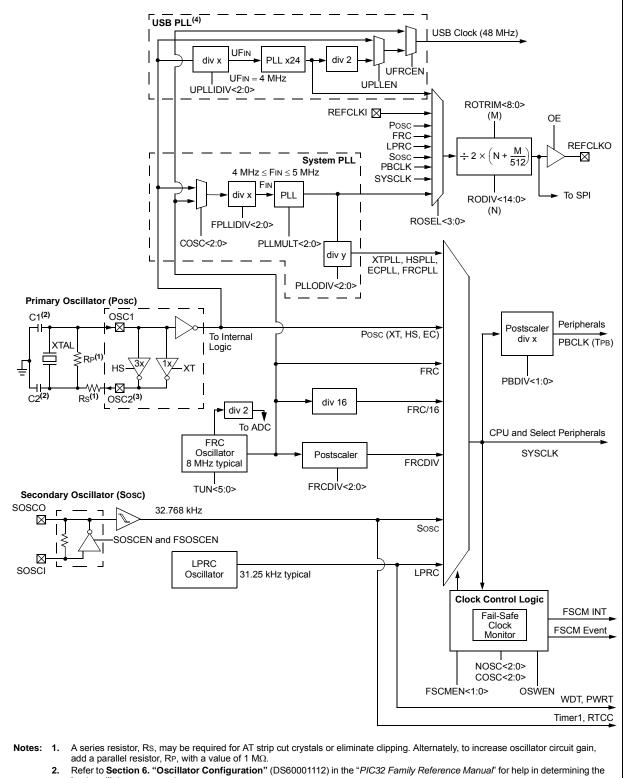

## FIGURE 8-1: OSCILLATOR DIAGRAM

Refer to Section 6. "Oscillator Configuration" (DS60001112) in the "PIC32 Family Reference Manual" for help in determinin best oscillator components.

3. The PBCLK out is only available on the OSC2 pin in certain clock modes.

4. The USB PLL is only available on PIC32MX2XX devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | _                 | —                 | —                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | —                 | —                 | —                 | _                | —                |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | —                 | _                 | SUSPEND           | DMABUSY           | _                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

### REGISTER 9-1: DMACON: DMA CONTROLLER CONTROL REGISTER

#### Legend:

| 0                 |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | nd as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: DMA On bit<sup>(1)</sup>

- 1 = DMA module is enabled

- 0 = DMA module is disabled

- bit 14-13 **Unimplemented:** Read as '0'

- bit 12 SUSPEND: DMA Suspend bit

- 1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

- 0 = DMA operates normally

### bit 11 DMABUSY: DMA Module Busy bit

- 1 = DMA module is active

- 0 = DMA module is disabled and not actively transferring data

- bit 10-0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| INE OIOT     | LK 10-J.          |                   |                   |                   |                        |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | -                 | —                 | _                      | _                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | -                 | —                 | _                      | _                 | —                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 |                   | —                 | _                      | _                 | —                | —                |

| 7:0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0                  | U-0               | R/W-0            | R/W-0            |

| 7:0          | UACTPND           |                   |                   | USLPGRD           | USBBUSY <sup>(1)</sup> | _                 | USUSPEND         | USBPWR           |

### REGISTER 10-5: U1PWRC: USB POWER CONTROL REGISTER

## Legend:

| zogonai           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB bus activity has been detected; however, an interrupt is pending, which has yet to be generated

0 = An interrupt is not pending

- bit 6-5 Unimplemented: Read as '0'

- bit 4 USLPGRD: USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

- bit 3 USBBUSY: USB Module Busy bit<sup>(1)</sup>

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- bit 2 Unimplemented: Read as '0'

- bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

- bit 0 USBPWR: USB Operation Enable bit

- 1 = USB module is turned on

- 0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

## **Note 1:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

### TABLE 11-1: INPUT PIN SELECTION

| Peripheral Pin | [pin name]R SFR | [pin name]R bits | [ <i>pin name</i> ]R Value to<br>RPn Pin Selection                                     |

|----------------|-----------------|------------------|----------------------------------------------------------------------------------------|

| INT4           | INT4R           | INT4R<3:0>       | 0000 = RPA0<br>0001 = RPB3                                                             |

| T2CK           | T2CKR           | T2CKR<3:0>       | 0010 = RPB4<br>0011 = RPB15<br>0100 = RPB7                                             |

| IC4            | IC4R            | IC4R<3:0>        | 0101 = RPC7 <sup>(2)</sup><br>0110 = RPC0 <sup>(1)</sup><br>0111 = RPC5 <sup>(2)</sup> |

| SS1            | SS1R            | SS1R<3:0>        | 1000 = Reserved                                                                        |

| REFCLKI        | REFCLKIR        | REFCLKIR<3:0>    | :<br>1111 = Reserved                                                                   |

| INT3           | INT3R           | INT3R<3:0>       | 0000 = RPA1<br>0001 = RPB5                                                             |

| ТЗСК           | T3CKR           | T3CKR<3:0>       | 0010 = RPB1<br>0011 = RPB11                                                            |

| IC3            | IC3R            | IC3R<3:0>        | 0100 = RPB8<br>0101 = RPA8 <sup>(2)</sup>                                              |

| U1CTS          | U1CTSR          | U1CTSR<3:0>      | 0110 = RPC8 <sup>(2)</sup><br>0111 = RPA9 <sup>(2)</sup>                               |

| U2RX           | U2RXR           | U2RXR<3:0>       | 1000 = Reserved                                                                        |

| SDI1           | SDI1R           | SDI1R<3:0>       | •<br>1111 = Reserved                                                                   |

| INT2           | INT2R           | INT2R<3:0>       | 0000 = RPA2                                                                            |

| T4CK           | T4CKR           | T4CKR<3:0>       |                                                                                        |

| IC1            | IC1R            | IC1R<3:0>        | 0011 = RPB13<br>0100 = RPB2                                                            |

| IC5            | IC5R            | IC5R<3:0>        | 0101 = RPC6 <sup>(2)</sup>                                                             |

| U1RX           | U1RXR           | U1RXR<3:0>       | 0110 = RPC1 <sup>(1)</sup><br>0111 = RPC3 <sup>(1)</sup>                               |

| U2CTS          | U2CTSR          | U2CTSR<3:0>      | 1000 = Reserved                                                                        |

| SDI2           | SDI2R           | SDI2R<3:0>       | •                                                                                      |

| OCFB           | OCFBR           | OCFBR<3:0>       | •<br>1111 = Reserved                                                                   |

| INT1           | INT1R           | INT1R<3:0>       | 0000 = RPA3<br>0001 = RPB14                                                            |

| T5CK           | T5CKR           | T5CKR<3:0>       | 0010 = RPB0<br>0011 = RPB10<br>0100 = RPB9                                             |

| IC2            | IC2R            | IC2R<3:0>        | 0101 = RPC9 <sup>(1)</sup><br>0110 = RPC2 <sup>(2)</sup><br>0111 = RPC4 <sup>(2)</sup> |

| SS2            | SS2R            | SS2R<3:0>        | 1000 = Reserved                                                                        |

| OCFA           | OCFAR           | OCFAR<3:0>       | •<br>•<br>1111 = Reserved                                                              |

Note 1: This pin is not available on 28-pin devices.

2: This pin is only available on 44-pin devices.

## TABLE 11-2: OUTPUT PIN SELECTION

| RPn Port Pin | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection       |

|--------------|----------|-------------|---------------------------------------------|

| RPA0         | RPA0R    | RPA0R<3:0>  | 0000 = No Connect                           |

| RPB3         | RPB3R    | RPB3R<3:0>  | 0001 = <u>U1TX</u><br>0010 = <u>U2RTS</u>   |

| RPB4         | RPB4R    | RPB4R<3:0>  | 0011 = SS1                                  |

| RPB15        | RPB15R   | RPB15R<3:0> |                                             |

| RPB7         | RPB7R    | RPB7R<3:0>  | 0110 = Reserved<br>0111 = C2OUT             |

| RPC7         | RPC7R    | RPC7R<3:0>  | 1000 = Reserved                             |

| RPC0         | RPC0R    | RPC0R<3:0>  | •                                           |

| RPC5         | RPC5R    | RPC5R<3:0>  | •<br>1111 = Reserved                        |

| RPA1         | RPA1R    | RPA1R<3:0>  | 0000 = No Connect                           |

| RPB5         | RPB5R    | RPB5R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPB1         | RPB1R    | RPB1R<3:0>  | 0011 = SDO1                                 |

| RPB11        | RPB11R   | RPB11R<3:0> | 0100 = SDO2<br>0101 = OC2                   |

| RPB8         | RPB8R    | RPB8R<3:0>  | 0110 = Reserved                             |

| RPA8         | RPA8R    | RPA8R<3:0>  |                                             |

| RPC8         | RPC8R    | RPC8R<3:0>  | •                                           |

| RPA9         | RPA9R    | RPA9R<3:0>  | 1111 = Reserved                             |

| RPA2         | RPA2R    | RPA2R<3:0>  | 0000 = No Connect                           |

| RPB6         | RPB6R    | RPB6R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPA4         | RPA4R    | RPA4R<3:0>  | 0011 = SDO1<br>0100 = SDO2                  |

| RPB13        | RPB13R   | RPB13R<3:0> | 0101 <b>= OC4</b>                           |

| RPB2         | RPB2R    | RPB2R<3:0>  | 0110 = OC5<br>0111 = REFCLKO                |

| RPC6         | RPC6R    | RPC6R<3:0>  | 1000 = Reserved                             |

| RPC1         | RPC1R    | RPC1R<3:0>  |                                             |

| RPC3         | RPC3R    | RPC3R<3:0>  | 1111 = Reserved                             |

| RPA3         | RPA3R    | RPA3R<3:0>  | 0000 = No Connect                           |

| RPB14        | RPB14R   | RPB14R<3:0> |                                             |

| RPB0         | RPB0R    | RPB0R<3:0>  | 0011 = <u>Reserved</u><br>0100 = <u>SS2</u> |

| RPB10        | RPB10R   | RPB10R<3:0> | 0101 <b>= OC3</b>                           |

| RPB9         | RPB9R    | RPB9R<3:0>  |                                             |

| RPC9         | RPC9R    | RPC9R<3:0>  | 1000 = Reserved                             |

| RPC2         | RPC2R    | RPC2R<3:0>  |                                             |

| RPC4         | RPC4R    | RPC4R<3:0>  | 1111 = Reserved                             |

## TABLE 11-6: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| SS                          |                  |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |       |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| FA04                        | INT1R            | 31:16     |       | —     | —     | —     | —     | -     | —    | -    | —    | —    | —    | —    | —    | —     | _      | —    | 0000       |

| FA04                        | INTIK            | 15:0      | _     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | INT1F | R<3:0> |      | 0000       |

| FA08                        | INT2R            | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    | —    | —    | —    | —    | —    | —     | —      | -    | 0000       |

| 1 400                       | INTZR            | 15:0      | _     | —     | —     | —     | —     | —     | —    | _    | —    | —    | —    | —    |      | INT2F | R<3:0> |      | 0000       |

| FA0C                        | INT3R            | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    | —    | —    | —    | —    | —    | —     | —      | -    | 0000       |

| TAUC                        | INTOR            | 15:0      | _     | —     | —     | —     | —     | —     | —    | _    | —    | —    | —    | —    |      | INT3F | R<3:0> |      | 0000       |

| FA10                        | INT4R            | 31:16     |       |       | —     |       |       | _     |      | _    |      | —    | —    |      | _    | —     | —      | _    | 0000       |

| IAIU                        |                  | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | INT4F | R<3:0> |      | 0000       |

| FA18                        | T2CKR            | 31:16     |       |       | _     |       |       | _     |      | _    |      | —    | _    |      | _    | —     | —      | _    | 0000       |

| 17(10                       | 120101           | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | T2CKI | R<3:0> |      | 0000       |

| FA1C                        | T3CKR            | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —      |      | 0000       |

| TAIC                        | IJORK            | 15:0      |       |       | _     |       |       | _     |      | _    |      | —    | _    |      |      | T3CKI | R<3:0> |      | 0000       |

| FA20                        | T4CKR            | 31:16     |       |       | _     |       |       | _     |      | _    |      | —    | _    |      | _    | —     | —      | _    | 0000       |

| 1 A20                       | THORK            | 15:0      |       |       | _     |       |       | _     |      | _    |      | —    | _    |      |      | T4CKI | R<3:0> |      | 0000       |

| FA24                        | T5CKR            | 31:16     | _     | —     | —     | —     | —     | _     | —    |      | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1 724                       | IJORK            | 15:0      |       |       | _     |       |       | _     |      | _    |      | —    | _    |      |      | T5CKI | R<3:0> |      | 0000       |

| FA28                        | IC1R             | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    | —    | —    | —    | —    | —    | —     | —      | -    | 0000       |

| FA20                        | ICIK             | 15:0      | _     | —     | —     | —     | —     | —     | —    | _    | —    | —    | —    | —    |      | IC1R  | <3:0>  |      | 0000       |

| FA2C                        | IC2R             | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    | —    | —    | —    | —    | —    | —     | —      | -    | 0000       |

| FA2C                        | ICZR             | 15:0      | _     | —     | —     | —     | —     | —     | —    | _    | —    | —    | —    | —    |      | IC2R  | <3:0>  |      | 0000       |

| FA30                        | IC3R             | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    | —    | —    | —    | —    | —    | —     | —      | -    | 0000       |

| FA30                        | ICSR             | 15:0      | _     | —     | —     | —     | —     | —     | —    | _    | —    | —    | —    | —    |      | IC3R  | <3:0>  |      | 0000       |

| FA34                        | IC4R             | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    | —    | —    | —    | —    | —    | —     | —      | -    | 0000       |

| 1 7.34                      | 1041             | 15:0      |       |       | —     |       |       | _     |      | _    |      | —    | —    |      |      | IC4R  | <3:0>  |      | 0000       |

| FA38                        | IC5R             | 31:16     |       |       | —     |       |       | _     |      | _    |      | —    | —    |      | _    | —     | —      | _    | 0000       |

| 1 7.30                      | 10.5K            | 15:0      |       |       | —     |       |       | _     |      | _    |      | —    | —    |      |      | IC5R  | <3:0>  |      | 0000       |

| FA48                        | OCFAR            | 31:16     | _     | —     | —     | —     | —     | _     | —    | _    | —    | —    | _    | —    | —    | —     | —      | _    | 0000       |

| 1 7440                      | UULAK            | 15:0      |       | _     | _     | _     | _     | _     | _    | _    | —    | _    | _    | _    |      | OCFA  | R<3:0> |      | 0000       |

| FA4C                        | OCFBR            | 31:16     |       | —     | —     | -     | —     | _     | _    | _    | _    | —    | —    | —    | _    | -     | _      | _    | 0000       |

| FA4U                        | UCFBR            | 15:0      |       | _     | —     | —     | —     | _     | —    | _    | _    | _    | —    | —    |      | OCFB  | R<3:0> |      | 0000       |

| EAEO                        |                  | 31:16     |       | —     | —     | —     | —     | _     | —    | _    | _    | _    | —    | —    | —    | —     | _      | _    | 0000       |

| FA50                        | U1RXR            | 15:0      |       | —     | _     | —     | _     | _     | —    | _    | _    | —    | _    | _    |      | U1RX  | R<3:0> |      | 0000       |

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

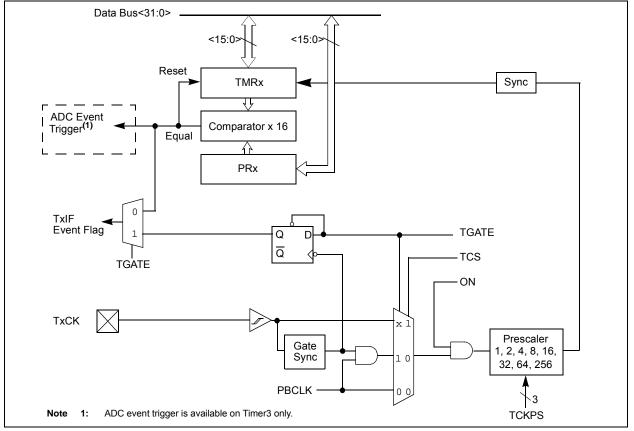

## 13.0 TIMER2/3, TIMER4/5

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features four synchronous 16-bit timers (default) that can operate as a freerunning interval timer for various timing applications and counting external events. The following modes are supported:

- Synchronous internal 16-bit timer

- Synchronous internal 16-bit gated timer

- · Synchronous external 16-bit timer

Two 32-bit synchronous timers are available by combining Timer2 with Timer3 and Timer4 with Timer5. The 32-bit timers can operate in three modes:

- Synchronous internal 32-bit timer

- · Synchronous internal 32-bit gated timer

- Synchronous external 32-bit timer

| Note: | In this chapter, references to registers, |

|-------|-------------------------------------------|

|       | TxCON, TMRx and PRx, use 'x' to           |

|       | represent Timer2 through Timer5 in 16-bit |

|       | modes. In 32-bit modes, 'x' represents    |

|       | Timer2 or Timer4 and 'y' represents       |

|       | Timer3 or Timer5.                         |

## **13.1 Additional Supported Features**

- · Selectable clock prescaler

- Timers operational during CPU idle

- Time base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

- ADC event trigger (Timer3 in 16-bit mode, Timer2/3 in 32-bit mode)

- Fast bit manipulation using CLR, SET and INV registers

Figure 13-1 and Figure 13-2 illustrate block diagrams of Timer2/3 and Timer4/5.

### FIGURE 13-1: TIMER2-TIMER5 BLOCK DIAGRAM (16-BIT)

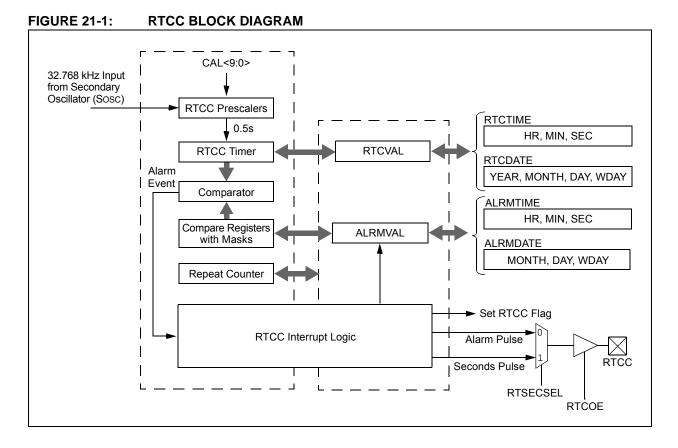

## 21.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32 RTCC module is intended for applications in which accurate time must be maintained for extended periods of time with minimal or no CPU intervention. Low-power optimization provides extended battery lifetime while keeping track of time. Following are some of the key features of this module:

- · Time: hours, minutes and seconds

- 24-hour format (military time)

- · Visibility of one-half second period

- · Provides calendar: day, date, month and year

- Alarm intervals are configurable for half of a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month and one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat: Chime

- Year range: 2000 to 2099

- Leap vear correction

- · BCD format for smaller firmware overhead

- Optimized for long-term battery operation

- Fractional second synchronization

- User calibration of the clock crystal frequency with auto-adjust

- Calibration range: ±0.66 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- Requirements: External 32.768 kHz clock crystal

- Alarm pulse or seconds clock output on RTCC pin

## 26.0 POWER-SAVING FEATURES

This section describes power-saving features for the PIC32MX1XX/2XX 28/36/44-pin Family. The PIC32 devices offer a total of nine methods and modes, organized into two categories, that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

## 26.1 Power Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the PBCLK and by individually disabling modules. These methods are grouped into the following categories:

- FRC Run mode: the CPU is clocked from the FRC clock source with or without postscalers

- LPRC Run mode: the CPU is clocked from the LPRC clock source

- Sosc Run mode: the CPU is clocked from the Sosc clock source

In addition, the Peripheral Bus Scaling mode is available where peripherals are clocked at the programmable fraction of the CPU clock (SYSCLK).

## 26.2 CPU Halted Methods

The device supports two power-saving modes, Sleep and Idle, both of which Halt the clock to the CPU. These modes operate with all clock sources, as follows:

- Posc Idle mode: the system clock is derived from the Posc. The system clock source continues to operate. Peripherals continue to operate, but can optionally be individually disabled.

- FRC Idle mode: the system clock is derived from the FRC with or without postscalers. Peripherals continue to operate, but can optionally be individually disabled.

- Sosc Idle mode: the system clock is derived from the Sosc. Peripherals continue to operate, but can optionally be individually disabled.

- LPRC Idle mode: the system clock is derived from the LPRC. Peripherals continue to operate, but can optionally be individually disabled. This is the lowest power mode for the device with a clock running.

- Sleep mode: the CPU, the system clock source and any peripherals that operate from the system clock source are Halted. Some peripherals can operate in Sleep using specific clock sources. This is the lowest power mode for the device.

## 26.3 Power-Saving Operation

Peripherals and the CPU can be Halted or disabled to further reduce power consumption.

## 26.3.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are Halted. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- The CPU is halted

- The system clock source is typically shutdown. See Section 26.3.3 "Peripheral Bus Scaling Method" for specific information.

- There can be a wake-up delay based on the oscillator selection

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode

- The BOR circuit remains operative during Sleep mode

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep

- The USB module can override the disabling of the Posc or FRC. Refer to the USB section for specific details.

- Modules can be individually disabled by software prior to entering Sleep in order to further reduce consumption

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | r-1                   | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |  |  |

| 31:24        | —                     |                   |                   | -                 | _                 |                   | _                | -                |  |  |

| 00.40        | r-1                   | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |  |  |

| 23:16        | —                     | _                 | —                 | -                 | —                 | FI                | PLLODIV<2:(      | LLODIV<2:0>      |  |  |

| 45.0         | R/P                   | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |  |  |

| 15:8         | UPLLEN <sup>(1)</sup> |                   | —                 | _                 | _                 | UF                | .(1)             |                  |  |  |

| 7.0          | r-1                   | R/P-1             | R/P               | R/P-1             | r-1               | R/P               | R/P              | R/P              |  |  |

| 7:0          | —                     | F                 | PLLMUL<2:0>       |                   | _                 | FPLLIDIV<2:0>     |                  |                  |  |  |

#### **DEVCFG2: DEVICE CONFIGURATION WORD 2 REGISTER 27-3:**

| Legend:           | r = Reserved bit | P = Programmable bit                    |  |  |  |  |

|-------------------|------------------|-----------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |  |  |  |  |

### bit 31-19 Reserved: Write '1'

bit 15

bit 7

bit 18-16 FPLLODIV<2:0>: Default PLL Output Divisor bits

- 111 = PLL output divided by 256 110 = PLL output divided by 64 101 = PLL output divided by 32 100 = PLL output divided by 16 011 = PLL output divided by 8 010 = PLL output divided by 4 001 = PLL output divided by 2 000 = PLL output divided by 1 UPLLEN: USB PLL Enable bit<sup>(1)</sup> 1 = Disable and bypass USB PLL 0 = Enable USB PLL bit 14-11 Reserved: Write '1' bit 10-8 UPLLIDIV<2:0>: USB PLL Input Divider bits<sup>(1)</sup> 111 = 12x divider 110 = 10x divider 101 = 6x divider100 = 5x divider 011 = 4x divider 010 = 3x divider 010 = 3x divider 001 = 2x divider000 = 1x divider Reserved: Write '1'

- bit 6-4 FPLLMUL<2:0>: PLL Multiplier bits

- 111 = 24x multiplier 110 = 21x multiplier

- 101 = 20x multiplier

- 100 = 19x multiplier

- 011 = 18x multiplier

- 010 = 17x multiplier

- 001 = 16x multiplier

- 000 = 15x multiplier

- bit 3 Reserved: Write '1'

Note 1: This bit is only available on PIC32MX2XX devices.

## 28.0 INSTRUCTION SET

The PIC32MX1XX/2XX family instruction set complies with the MIPS32<sup>®</sup> Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- · Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

**Note:** Refer to *"MIPS32<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set"* at www.imgtec.com for more information.

## TABLE 30-14: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| DC CHARACTERISTICS |         |                                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |                    |       |                                                                 |  |  |  |

|--------------------|---------|-------------------------------------------------------------|-------------------------------------------------------|------|--------------------|-------|-----------------------------------------------------------------|--|--|--|

| Param.<br>No.      | Symbol  | Characteristics                                             | Min.                                                  | Тур. | Max.               | Units | Comments                                                        |  |  |  |

| D312               | TSET    | Internal 4-bit DAC<br>Comparator Reference<br>Settling time | _                                                     | _    | 10                 | μs    | See Note 1                                                      |  |  |  |

| D313               | DACREFH | CVREF Input Voltage                                         | AVss                                                  | _    | AVDD               | V     | CVRSRC with CVRSS = 0                                           |  |  |  |

|                    |         | Reference Range                                             | VREF-                                                 | _    | VREF+              | V     | CVRSRC with CVRSS = 1                                           |  |  |  |

| D314               | DVREF   | CVREF Programmable<br>Output Range                          | 0                                                     | _    | 0.625 x<br>DACREFH | V     | 0 to 0.625 DACREFH with<br>DACREFH/24 step size                 |  |  |  |

|                    |         |                                                             | 0.25 x<br>DACREFH                                     | _    | 0.719 x<br>DACREFH | V     | 0.25 x DACREFH to 0.719<br>DACREFH with<br>DACREFH/32 step size |  |  |  |

| D315               | DACRES  | Resolution                                                  | —                                                     | _    | DACREFH/24         |       | CVRCON <cvrr> = 1</cvrr>                                        |  |  |  |

|                    |         |                                                             | _                                                     | —    | DACREFH/32         | _     | CVRCON <cvrr> = 0</cvrr>                                        |  |  |  |

| D316               | DACACC  | Absolute Accuracy <sup>(2)</sup>                            |                                                       | _    | 1/4                | LSB   | DACREFH/24,<br>CVRCON <cvrr> = 1</cvrr>                         |  |  |  |

|                    |         |                                                             |                                                       | _    | 1/2                | LSB   | DACREFH/32,<br>CVRCON <cvrr> = 0</cvrr>                         |  |  |  |

**Note 1:** Settling time was measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but is not tested in manufacturing.

**2:** These parameters are characterized but not tested.

### TABLE 30-15: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHARACTERISTICS |        |                                 | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |         |      |       |                                                                                                    |  |

|--------------------|--------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|----------------------------------------------------------------------------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics                 | Min.                                                                                                                                                                                                                                                                                | Typical | Max. | Units | Comments                                                                                           |  |

| D321               | Cefc   | External Filter Capacitor Value | 8                                                                                                                                                                                                                                                                                   | 10      |      | μF    | Capacitor must be low series<br>resistance (1 ohm). Typical<br>voltage on the VCAP pin is<br>1.8V. |  |

## TABLE 30-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS (CONTINUED)

| AC CHARACTERISTICS |                      |                                                    |              | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature } -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |            |  |  |  |

|--------------------|----------------------|----------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|--|

| Param.<br>No.      | Symbol               | Characteristics <sup>(1)</sup>                     | Min.         | Typical <sup>(2)</sup>                                                                                                                                                                                                                                                             | Max. | Units | Conditions |  |  |  |

| SP51               | TssH2doZ             | SSx ↑ to SDOx Output<br>High-Impedance<br>(Note 4) | 5            | _                                                                                                                                                                                                                                                                                  | 25   | ns    | _          |  |  |  |

| SP52               | TscH2ssH<br>TscL2ssH | SSx ↑ after SCKx Edge                              | Тѕск +<br>20 | —                                                                                                                                                                                                                                                                                  | _    | ns    | —          |  |  |  |

| SP60               | TssL2doV             | SDOx Data Output Valid after<br>SSx Edge           | —            | —                                                                                                                                                                                                                                                                                  | 25   | ns    |            |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 50 ns.

**4:** Assumes 50 pF load on all SPIx pins.

| AC CHARAG                         | S <sup>(2)</sup> | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 3): 2.5V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |         |                 |                            |  |

|-----------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------|----------------------------|--|

| ADC Speed                         | TAD Min.         | Sampling<br>Time Min.                                                                                                                                                                                                                                                                              | Rs Max. | Vdd             | ADC Channels Configuration |  |

| 1 Msps to 400 ksps <sup>(1)</sup> | 65 ns            | 132 ns                                                                                                                                                                                                                                                                                             | 500Ω    | 3.0V to<br>3.6V | ANX CHX ADC                |  |

| Up to 400 ksps                    | 200 ns           | 200 ns                                                                                                                                                                                                                                                                                             | 5.0 kΩ  | 2.5V to<br>3.6V | ANX CHX<br>ANX OF VREF-    |  |

### TABLE 30-35:10-BIT CONVERSION RATE PARAMETERS