Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 19                                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx210f016b-v-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                     |      |                                    |                  | Rem             | appab                                  | le Pe | riphe                | erals                              |                    |                     |                  |     | (                                        |      | ls)                          |      |          |      |                                 |

|---------------------|------|------------------------------------|------------------|-----------------|----------------------------------------|-------|----------------------|------------------------------------|--------------------|---------------------|------------------|-----|------------------------------------------|------|------------------------------|------|----------|------|---------------------------------|

| Device              | Pins | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins | Timers <sup>(2)</sup> /Capture/Compare | UART  | SPI/I <sup>2</sup> S | External Interrupts <sup>(3)</sup> | Analog Comparators | USB On-The-Go (OTG) | I <sup>2</sup> C | dMq | DMA Channels<br>(Programmable/Dedicated) | CTMU | 10-bit 1 Msps ADC (Channels) | RTCC | I/O Pins | JTAG | Packages                        |

| PIC32MX210F016B     | 28   | 16+3                               | 4                | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX210F016C     | 36   | 16+3                               | 4                | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 25       | Y    | VTLA                            |

| PIC32MX210F016D     | 44   | 16+3                               | 4                | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX220F032B     | 28   | 32+3                               | 8                | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX220F032C     | 36   | 32+3                               | 8                | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA                            |

| PIC32MX220F032D     | 44   | 32+3                               | 8                | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX230F064B     | 28   | 64+3                               | 16               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX230F064C     | 36   | 64+3                               | 16               | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA                            |

| PIC32MX230F064D     | 44   | 64+3                               | 16               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX250F128B     | 28   | 128+3                              | 32               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX250F128C     | 36   | 128+3                              | 32               | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA<br>VTLA,                   |

| PIC32MX250F128D     | 44   | 128+3                              | 32               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | TQFP,<br>QFN                    |

| PIC32MX230F256B     | 28   | 256+3                              | 16               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX230F256D     | 44   | 256+3                              | 16               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX270F256B     | 28   | 256+3                              | 64               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX270F256D     | 44   | 256+3                              | 64               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX270F256DB(4) | 44   | 256+3                              | 64               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

#### TABLE 2: PIC32MX2XX 28/36/44-PIN USB FAMILY FEATURES

Note 1: This device features 3 KB of boot Flash memory.

**2:** Four out of five timers are remappable.

3: Four out of five external interrupts are remappable.

4: This PIC32 device is targeted to specific audio software packages that are tracked for licensing royalty purposes. All peripherals and electrical characteristics are identical to their corresponding base part numbers.

#### TABLE 10: PIN NAMES FOR 44-PIN USB DEVICES

### 44-PIN QFN (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX210F016D PIC32MX220F032D PIC32MX230F064D PIC32MX230F256D PIC32MX250F128D PIC32MX270F256D

|       |                                                  |       | 44 1                                      |

|-------|--------------------------------------------------|-------|-------------------------------------------|

| Pin # | Full Pin Name                                    | Pin # | Full Pin Name                             |

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                         | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 2     | RPC6/PMA1/RC6                                    | 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 3     | RPC7/PMA0/RC7                                    | 25    | AN6/RPC0/RC0                              |

| 4     | RPC8/PMA5/RC8                                    | 26    | AN7/RPC1/RC1                              |

| 5     | RPC9/CTED7/PMA6/RC9                              | 27    | AN8/RPC2/PMA2/RC2                         |

| 6     | Vss                                              | 28    | Vdd                                       |

| 7     | VCAP                                             | 29    | Vss                                       |

| 8     | PGED2/RPB10/D+/CTED11/RB10                       | 30    | OSC1/CLKI/RPA2/RA2                        |

| 9     | PGEC2/RPB11/D-/RB11                              | 31    | OSC2/CLKO/RPA3/RA3                        |

| 10    | VUSB3V3                                          | 32    | TDO/RPA8/PMA8/RA8                         |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                       | 33    | SOSCI/RPB4/RB4                            |

| 12    | PGED4/TMS/PMA10/RA10                             | 34    | SOSCO/RPA4/T1CK/CTED9/RA4                 |

| 13    | PGEC4/TCK/CTED8/PMA7/RA7                         | 35    | TDI/RPA9/PMA9/RA9                         |

| 14    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 | 36    | AN12/RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            | 37    | RPC4/PMA4/RC4                             |

| 16    | AVss                                             | 38    | RPC5/PMA3/RC5                             |

| 17    | AVDD                                             | 39    | Vss                                       |

| 18    | MCLR                                             | 40    | Vdd                                       |

| 19    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 | 41    | RPB5/USBID/RB5                            |

| 20    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       | 42    | VBUS                                      |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        | 43    | RPB7/CTED3/PMD5/INT0/RB7                  |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       | 44    | RPB8/SCL1/CTED10/PMD4/RB8                 |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

5: Shaded pins are 5V tolerant.

NOTES:

## 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source.For detailed information, refer to **Section 3.** "Memory Organization" (DS60001115), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family microcontrollers provide 4 GB unified virtual memory address space. All memory regions, including program, data memory, Special Function Registers (SFRs), and Configuration registers, reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, the data memory can be made executable, allowing PIC32MX1XX/2XX 28/36/44-pin Family devices to execute from data memory.

Key features include:

- 32-bit native data width

- Separate User (KUSEG) and Kernel (KSEG0/KSEG1) mode address space

- · Flexible program Flash memory partitioning

- Flexible data RAM partitioning for data and program space

- Separate boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Simple memory mapping with Fixed Mapping Translation (FMT) unit

- Cacheable (KSEG0) and non-cacheable (KSEG1) address regions

## 4.1 PIC32MX1XX/2XX 28/36/44-pin Family Memory Layout

PIC32MX1XX/2XX 28/36/44-pin Family microcontrollers implement two address schemes: virtual and physical. All hardware resources, such as program memory, data memory and peripherals, are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by bus master peripherals, such as DMA and the Flash controller, that access memory independently of the CPU.

The memory maps for the PIC32MX1XX/2XX 28/36/44-pin Family devices are illustrated in Figure 4-1 through Figure 4-6.

Table 4-1 provides SFR memory map details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |  |  |

| 31:24        | —                 | —                 | _                 | —                 | _                 | —                 | -                | —                    |  |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |  |  |

| 23:16        | —                 | —                 | _                 | —                 | _                 | —                 | -                | —                    |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |  |  |

| 10.0         | _                 | —                 | _                 | —                 | _                 | —                 | _                | —                    |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |  |  |  |

| 7:0          | —                 | —                 | _                 | —                 | _                 | —                 | —                | SWRST <sup>(1)</sup> |  |  |  |

## REGISTER 6-2: RSWRST: SOFTWARE RESET REGISTER

| Legend:           | HC = Cleared by hardwa | ire                       |                    |

|-------------------|------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit       | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set       | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-1 Unimplemented: Read as '0'

- bit 0 SWRST: Software Reset Trigger bit<sup>(1)</sup> 1 = Enable Software Reset event

- 0 = No effect

- Note 1: The system unlock sequence must be performed before the SWRST bit is written. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

## 8.0 OSCILLATOR CONFIGURATION

| Note: | This data sheet summarizes the features<br>of the PIC32MX1XX/2XX 28/36/44-pin<br>Family of devices. It is not intended to be<br>a comprehensive reference source. To<br>complement the information in this data |  |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|       | sheet, refer to Section 6. "Oscillator                                                                                                                                                                          |  |  |  |  |  |  |

|       | Configuration" (DS60001112), which is                                                                                                                                                                           |  |  |  |  |  |  |

|       | available from the Documentation >                                                                                                                                                                              |  |  |  |  |  |  |

|       | Reference Manual section of the                                                                                                                                                                                 |  |  |  |  |  |  |

|       | Microchip PIC32 web site                                                                                                                                                                                        |  |  |  |  |  |  |

|       | (www.microchip.com/pic32).                                                                                                                                                                                      |  |  |  |  |  |  |

The PIC32MX1XX/2XX 28/36/44-pin Family oscillator system has the following modules and features:

- Four external and internal oscillator options as clock sources

- On-Chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-Chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Dedicated On-Chip PLL for USB peripheral

A block diagram of the oscillator system is provided in Figure 8-1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        |                   | DCRCDATA<31:24>   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.10        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | DCRCDATA<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | DCRCDATA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

|              |                   |                   |                   | DCRCDA            | TA<7:0>           |                   |                  |                  |  |  |  |  |

### REGISTER 9-5: DCRCDATA: DMA CRC DATA REGISTER

# Legend:

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (i.e., current IP header checksum value).

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

### REGISTER 9-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | DCRCXOR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | DCRCXOR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | DCRCXOR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

|              |                   |                   |                   | DCRCXO            | R<7:0>            |                   |                  |                  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): This register is unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = Enable the XOR input to the Shift register

- 0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

| INE OIOT     |                   |                   |                   |                   |                        |                   |                  |                  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |  |  |

| 31.24        | —                 | —                 | -                 | —                 | _                      | _                 | —                | _                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |  |  |

| 23.10        | —                 | —                 | -                 | —                 | _                      | _                 | —                | _                |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |  |  |

| 15.0         | —                 | —                 |                   | —                 | _                      | _                 | —                | —                |  |  |

| 7.0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0                  | U-0               | R/W-0            | R/W-0            |  |  |

| 7:0          | UACTPND           |                   |                   | USLPGRD           | USBBUSY <sup>(1)</sup> | _                 | USUSPEND         | USBPWR           |  |  |

### REGISTER 10-5: U1PWRC: USB POWER CONTROL REGISTER

## Legend:

| zogonai           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB bus activity has been detected; however, an interrupt is pending, which has yet to be generated

0 = An interrupt is not pending

- bit 6-5 Unimplemented: Read as '0'

- bit 4 USLPGRD: USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

- bit 3 USBBUSY: USB Module Busy bit<sup>(1)</sup>

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- bit 2 Unimplemented: Read as '0'

- bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

- bit 0 USBPWR: USB Operation Enable bit

- 1 = USB module is turned on

- 0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

# **Note 1:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|----------------------|----------------------|-------------------|-------------------|------------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |  |

| 31.24        | —                 | -                 | —                    | -                    | —                 | —                 | _                      | -                |  |  |

| 23:16        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |  |

| 23.10        | —                 | —                 | —                    | —                    | —                 | —                 | —                      | —                |  |  |

| 15:8         | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |  |

| 15.0         | —                 | -                 | —                    | -                    | —                 | —                 | -                      | -                |  |  |

|              | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS           | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS             | R/WC-0, HS       |  |  |

| 7:0          | BTSEF             | BTSEF BMXEF       |                      | BTOEF <sup>(2)</sup> | DFN8EF            | CRC16EF           | CRC5EF <sup>(4)</sup>  | PIDEF            |  |  |

|              | DISEF             | DIVIALE           | DMAEF <sup>(1)</sup> | DIVERY               | DINOLF            | GIVE IDEF         | EOFEF <sup>(3,5)</sup> |                  |  |  |

### REGISTER 10-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable bit         |                    |  |  |  |

|-------------------|-------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

- bit 31-8 Unimplemented: Read as '0'

- bit 7 BTSEF: Bit Stuff Error Flag bit

- 1 = Packet rejected due to bit stuff error

- 0 = Packet accepted

- bit 6 BMXEF: Bus Matrix Error Flag bit

- 1 = The base address, of the Buffer Descriptor Table, or the address of an individual buffer pointed to by a Buffer Descriptor Table entry, is invalid.

- 0 = No address error

- bit 5 DMAEF: DMA Error Flag bit<sup>(1)</sup>

- 1 = USB DMA error condition detected

- 0 = No DMA error

- bit 4 BTOEF: Bus Turnaround Time-Out Error Flag bit<sup>(2)</sup>

- 1 = Bus turnaround time-out has occurred

- 0 = No bus turnaround time-out

- bit 3 **DFN8EF:** Data Field Size Error Flag bit

- 1 = Data field received is not an integral number of bytes

- 0 = Data field received is an integral number of bytes

- bit 2 CRC16EF: CRC16 Failure Flag bit

- 1 = Data packet rejected due to CRC16 error

- 0 = Data packet accepted

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- **2:** This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

## 13.2 Timer Control Registers

## TABLE 13-1: TIMER2-TIMER5 REGISTER MAP

|                             | - 15                            |           |                |       |       |       |       |       |      |      |        |      |            |      |      |      |          |      |            |

|-----------------------------|---------------------------------|-----------|----------------|-------|-------|-------|-------|-------|------|------|--------|------|------------|------|------|------|----------|------|------------|

| ess                         |                                 |           |                |       |       |       |       |       |      | Bi   | its    |      |            |      |      |      |          |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15          | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7   | 22/6 | 21/5       | 20/4 | 19/3 | 18/2 | 17/1     | 16/0 | All Resets |

| 0800                        | T2CON                           | 31:16     | _              | _     | —     | _     | —     | —     | —    | —    | —      | _    | —          | _    | —    | _    | —        | -    | 0000       |

| 0000                        | 12001                           | 15:0      | ON             |       | SIDL  | —     | —     | —     | _    | _    | TGATE  | -    | TCKPS<2:0> | >    | T32  | _    | TCS      |      | 0000       |

| 0810                        | TMR2                            | 31:16     | —              | —     | —     | —     | —     | —     | _    | —    | —      | —    | —          | —    |      | —    | —        | _    | 0000       |

| 0010                        | T WIT VZ                        | 15:0      |                |       |       |       |       |       |      | TMR2 | <15:0> |      |            |      |      |      |          |      | 0000       |

| 0820                        | PR2                             | 31:16     | —              | —     | —     | —     | —     | —     | —    | —    | —      | —    | —          | —    | —    | —    | —        | —    | 0000       |

| 0020                        |                                 | 15:0      |                |       |       |       |       |       |      | PR2< | 15:0>  |      |            |      |      |      |          |      | FFFF       |

| 0040                        | T3CON                           | 31:16     | —              | —     | —     | _     | —     | —     | —    | —    | —      | —    | —          | —    | —    | —    | —        | —    | 0000       |

| 0/100                       | 10001                           | 15:0      | ON             | —     | SIDL  | _     | —     | —     | —    | —    | TGATE  | -    | TCKPS<2:0> | >    | —    | —    | TCS      | —    | 0000       |

| 0A10                        | TMR3                            | 31:16     |                | _     | _     | —     | _     | —     |      | —    |        | _    | —          | _    | —    | _    | _        | _    | 0000       |

| 0,110                       | -                               | 15:0      |                |       |       |       |       |       |      | TMR3 | <15:0> |      |            |      |      |      |          |      | 0000       |

| 0A20                        | PR3                             | 31:16     | —              | —     | —     | —     | —     | —     | _    | —    | —      | _    | —          | —    |      | _    | —        |      | 0000       |

|                             | _                               | 15:0      |                |       |       |       |       |       |      | PR3< | 15:0>  |      |            |      |      |      |          |      | FFFF       |

| 0C00                        | T4CON                           | 31:16     | _              | _     | —     | —     | —     | —     | —    | _    | —      | —    | _          | —    | —    |      | —        |      | 0000       |

|                             |                                 | 15:0      | ON             | —     | SIDL  | —     | —     |       | _    | —    | TGATE  |      | TCKPS<2:0> | >    | T32  | —    | TCS      | —    | 0000       |

| 0C10                        | TMR4                            | 31:16     | _              | —     | —     | —     | —     | —     | _    | —    | —      | —    | _          | —    | —    | —    | —        | _    | 0000       |

|                             |                                 | 15:0      |                |       |       |       |       |       |      | TMR4 |        |      |            |      |      |      |          |      | 0000       |

| 0C20                        | PR4                             | 31:16     | _              | —     | —     | —     | —     | —     | _    | -    | -      | _    | —          | _    | —    | —    | —        | _    | 0000       |

|                             |                                 | 15:0      |                |       |       |       |       |       |      |      | 15:0>  |      |            |      |      |      |          |      | FFFF       |

| 0E00                        | T5CON                           | 31:16     | -              | _     | -     | _     |       | —     |      | _    |        |      |            |      |      |      | —<br>T00 |      | 0000       |

|                             |                                 | 15:0      | ON             |       | SIDL  | _     |       |       | _    | _    | TGATE  |      | TCKPS<2:0> |      | _    | _    | TCS      |      | 0000       |

| 0E10                        | TMR5                            | 31:16     | _              | —     | —     | —     | —     | —     | _    | -    |        | —    | —          | —    |      | —    | —        |      | 0000       |

|                             |                                 | 15:0      |                |       |       |       |       |       |      | TMR5 | <15:0> |      |            |      |      |      |          |      | 0000       |

| 0E20                        | PR5                             | 31:16     |                | —     | —     | —     | —     | —     | _    |      |        | —    | —          | —    | —    | —    | _        | _    | 0000       |

|                             |                                 | 15:0      | PR5<15:0> FFFF |       |       |       |       |       |      |      |        |      |            |      |      |      |          |      |            |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

### REGISTER 15-1: ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER (CONTINUED)

ICM<2:0>: Input Capture Mode Select bits

bit 2-0

- 111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

- 110 = Simple Capture Event mode every edge, specified edge first and every edge thereafter

- 101 = Prescaled Capture Event mode every sixteenth rising edge

- 100 = Prescaled Capture Event mode every fourth rising edge

- 011 = Simple Capture Event mode every rising edge

- 010 = Simple Capture Event mode every falling edge

- 001 = Edge Detect mode every edge (rising and falling)

- 000 = Input Capture module is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

NOTES:

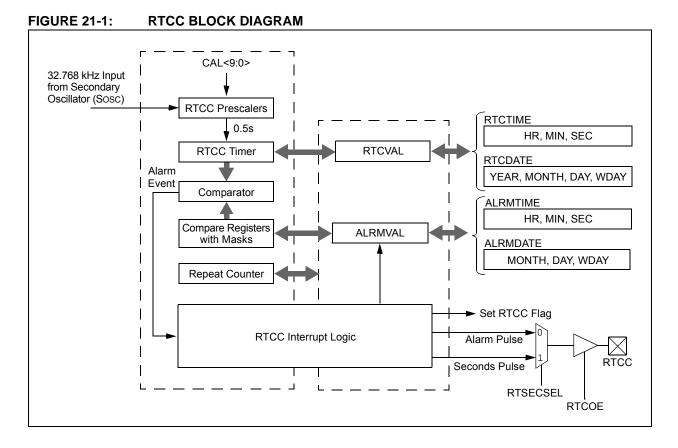

## 21.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32 RTCC module is intended for applications in which accurate time must be maintained for extended periods of time with minimal or no CPU intervention. Low-power optimization provides extended battery lifetime while keeping track of time. Following are some of the key features of this module:

- · Time: hours, minutes and seconds

- 24-hour format (military time)

- · Visibility of one-half second period

- · Provides calendar: day, date, month and year

- Alarm intervals are configurable for half of a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month and one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat: Chime

- Year range: 2000 to 2099

- Leap vear correction

- · BCD format for smaller firmware overhead

- Optimized for long-term battery operation

- Fractional second synchronization

- User calibration of the clock crystal frequency with auto-adjust

- Calibration range: ±0.66 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- Requirements: External 32.768 kHz clock crystal

- Alarm pulse or seconds clock output on RTCC pin

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2       | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|----------------------|-------------------------|------------------|------------------|--|

| 24.04        | r-0               | r-1               | r-1               | R/P               | r-1                  | r-1                     | r-1              | R/P              |  |

| 31:24        |                   | _                 |                   | CP                | —                    | _                       | _                | BWP              |  |

| 00.40        | r-1               | r-1               | r-1               | r-1               | r-1                  | R/P                     | R/P              | R/P              |  |

| 23:16        |                   | _                 |                   |                   |                      | PWP<8:6> <sup>(3)</sup> |                  |                  |  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | R/P                  | R/P                     | r-1              | r-1              |  |

| 15:8         |                   |                   | PWP<              | :5:0>             |                      |                         | —                | —                |  |

| 7.0          | r-1               | r-1               | r-1               | R/P               | R/P                  | R/P                     | R/P              | R/P              |  |

| 7:0          |                   |                   |                   | ICESEL            | <1:0> <sup>(2)</sup> | JTAGEN <sup>(1)</sup>   | DEBUG<1:0>       |                  |  |

### REGISTER 27-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

| Legend:           | r = Reserved bit | P = Programmable bit               |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 31 Reserved: Write '0'

bit 30-29 Reserved: Write '1'

- bit 28 **CP:** Code-Protect bit

- Prevents boot and program Flash memory from being read or modified by an external programming device. 1 = Protection is disabled

0 = Protection is enabled

bit 27-25 Reserved: Write '1'

bit 24 **BWP:** Boot Flash Write-Protect bit

Prevents boot Flash memory from being modified during code execution.

1 = Boot Flash is writable

0 = Boot Flash is not writable

- bit 23-19 Reserved: Write '1'

- **Note 1:** This bit sets the value for the JTAGEN bit in the CFGCON register.

- 2: The PGEC4/PGED4 pin pair is not available on all devices. Refer to the "**Pin Diagrams**" section for availability.

- 3: The PWP<8:7> bits are only available on devices with 256 KB Flash.

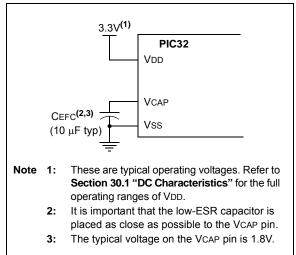

## 27.3 On-Chip Voltage Regulator

All PIC32MX1XX/2XX 28/36/44-pin Family devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX1XX/2XX 28/36/44-pin Family family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 30.1 "DC Characteristics"**.

| Note: | It is important that the low-ESR capacitor |

|-------|--------------------------------------------|

|       | is placed as close as possible to the VCAP |

|       | pin.                                       |

## 27.3.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

## 27.3.2 ON-CHIP REGULATOR AND BOR

PIC32MX1XX/2XX 28/36/44-pin Family devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specific in **Section 30.1 "DC Characteristics"**.

#### FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

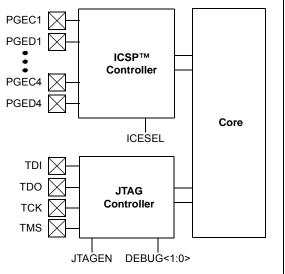

## 27.4 Programming and Diagnostics

PIC32MX1XX/2XX 28/36/44-pin Family devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

Figure 27-2 illustrates a block diagram of the programming, debugging, and trace ports.

NOTES:

# 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

## 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- · Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

### TABLE 30-41: CTMU CURRENT SOURCE SPECIFICATIONS

|              | DC CHAI   | RACTERISTICS                                       | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 3):2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |       |      |       |                                  |  |  |

|--------------|-----------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|----------------------------------|--|--|

| Param<br>No. | Symbol    | Characteristic                                     | Min.                                                                                                                                                                                                                                                                                          | Тур.  | Max. | Units | Conditions                       |  |  |

| CTMU CUR     | RENT SOUR | CE                                                 | •                                                                                                                                                                                                                                                                                             | •     |      |       |                                  |  |  |

| CTMUI1       | Ιουτ1     | Base Range <sup>(1)</sup>                          | _                                                                                                                                                                                                                                                                                             | 0.55  | _    | μA    | CTMUCON<9:8> = 01                |  |  |

| CTMUI2       | Ιουτ2     | 10x Range <sup>(1)</sup>                           | _                                                                                                                                                                                                                                                                                             | 5.5   | _    | μA    | CTMUCON<9:8> = 10                |  |  |

| CTMUI3       | Ιουτ3     | 100x Range <sup>(1)</sup>                          | _                                                                                                                                                                                                                                                                                             | 55    |      | μA    | CTMUCON<9:8> = 11                |  |  |

| CTMUI4       | IOUT4     | 1000x Range <sup>(1)</sup>                         | _                                                                                                                                                                                                                                                                                             | 550   |      | μA    | CTMUCON<9:8> = 00                |  |  |

| CTMUFV1      | VF        | Temperature Diode Forward Voltage <sup>(1,2)</sup> | —                                                                                                                                                                                                                                                                                             | 0.598 | _    | V     | TA = +25°C,<br>CTMUCON<9:8> = 01 |  |  |

|              |           |                                                    | _                                                                                                                                                                                                                                                                                             | 0.658 | _    | V     | TA = +25°C,<br>CTMUCON<9:8> = 10 |  |  |

|              |           |                                                    | —                                                                                                                                                                                                                                                                                             | 0.721 |      | V     | TA = +25°C,<br>CTMUCON<9:8> = 11 |  |  |

| CTMUFV2      | VFVR      |                                                    |                                                                                                                                                                                                                                                                                               | -1.92 | _    | mV/ºC | CTMUCON<9:8> = 01                |  |  |

|              |           | Change <sup>(1,2)</sup>                            | _                                                                                                                                                                                                                                                                                             | -1.74 |      | mV/ºC | CTMUCON<9:8> = 10                |  |  |

|              |           |                                                    | _                                                                                                                                                                                                                                                                                             | -1.56 |      | mV/ºC | CTMUCON<9:8> = 11                |  |  |

**Note 1:** Nominal value at center point of current trim range (CTMUCON<15:10> = 000000).

**2:** Parameters are characterized but not tested in manufacturing. Measurements taken with the following conditions:

- VREF+ = AVDD = 3.3V

- ADC module configured for conversion speed of 500 ksps

- All PMD bits are cleared (PMDx = 0)

- Executing a while(1) statement

- Device operating from the FRC with no PLL

- **3:** The CTMU module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

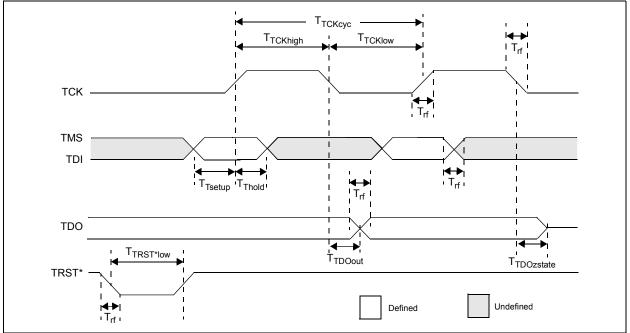

## FIGURE 30-23: EJTAG TIMING CHARACTERISTICS

### TABLE 30-42: EJTAG TIMING REQUIREMENTS

| AC CHA        | RACTERISTI | CS                                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industria} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |            |  |  |  |

|---------------|------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|--|

| Param.<br>No. | Symbol     | Description <sup>(1)</sup>                       | Min.                                                                                                                                                                                                                                                                                 | Max. | Units | Conditions |  |  |  |

| EJ1           | Ттсксус    | TCK Cycle Time                                   | 25                                                                                                                                                                                                                                                                                   |      | ns    | _          |  |  |  |

| EJ2           | Ттскнідн   | TCK High Time                                    | 10                                                                                                                                                                                                                                                                                   | _    | ns    | —          |  |  |  |

| EJ3           | TTCKLOW    | TCK Low Time                                     | 10                                                                                                                                                                                                                                                                                   | _    | ns    | _          |  |  |  |

| EJ4           | TTSETUP    | TAP Signals Setup Time Before<br>Rising TCK      | 5                                                                                                                                                                                                                                                                                    | _    | ns    | _          |  |  |  |

| EJ5           | TTHOLD     | TAP Signals Hold Time After<br>Rising TCK        | 3                                                                                                                                                                                                                                                                                    | -    | ns    | —          |  |  |  |

| EJ6           | Ττροουτ    | TDO Output Delay Time from<br>Falling TCK        | -                                                                                                                                                                                                                                                                                    | 5    | ns    | —          |  |  |  |

| EJ7           | TTDOZSTATE | TDO 3-State Delay Time from<br>Falling TCK       | _                                                                                                                                                                                                                                                                                    | 5    | ns    | _          |  |  |  |

| EJ8           | TTRSTLOW   | TRST Low Time                                    | 25                                                                                                                                                                                                                                                                                   |      | ns    |            |  |  |  |

| EJ9           | Trf        | TAP Signals Rise/Fall Time, All Input and Output | —                                                                                                                                                                                                                                                                                    | _    | ns    | _          |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

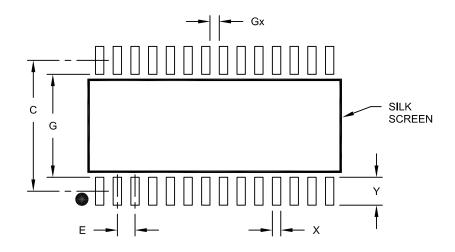

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |          |      |      |  |  |

|--------------------------|-------------|----------|------|------|--|--|

| Dimensio                 | n Limits    | MIN      | NOM  | MAX  |  |  |

| Contact Pitch            | E           | 1.27 BSC |      |      |  |  |

| Contact Pad Spacing      | С           |          | 9.40 |      |  |  |

| Contact Pad Width (X28)  | X           |          |      | 0.60 |  |  |

| Contact Pad Length (X28) | Y           |          |      | 2.00 |  |  |

| Distance Between Pads    | Gx          | 0.67     |      |      |  |  |

| Distance Between Pads    | G           | 7.40     |      |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A