Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

|                            |                                                                                |

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 19                                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx210f016b-v-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 4: PIN NAMES FOR 28-PIN USB DEVICES

28-PIN SOIC, SPDIP, SSOP (TOP VIEW) $^{(1,2,3)}$

1 28 1 28 1 28 SSOP SOIC SPDIP

PIC32MX210F016B PIC32MX220F032B PIC32MX230F064B PIC32MX230F256B PIC32MX250F128B PIC32MX270F256B

| Pin# | Full Pin Name                                    |

|------|--------------------------------------------------|

| 1    | MCLR                                             |

| 2    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 3    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

| 4    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        |

| 5    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       |

| 6    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2        |

| 7    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3          |

| 8    | Vss                                              |

| 9    | OSC1/CLKI/RPA2/RA2                               |

| 10   | OSC2/CLKO/RPA3/PMA0/RA3                          |

| 11   | SOSCI/RPB4/RB4                                   |

| 12   | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4                   |

| 13   | VDD                                              |

| 14   | TMS/RPB5/USBID/RB5                               |

| Pin# | Full Pin Name                                    |

|------|--------------------------------------------------|

| 15   | VBUS                                             |

| 16   | TDI/RPB7/CTED3/PMD5/INT0/RB7                     |

| 17   | TCK/RPB8/SCL1/CTED10/PMD4/RB8                    |

| 18   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                     |

| 19   | Vss                                              |

| 20   | VCAP                                             |

| 21   | PGED2/RPB10/D+/CTED11/RB10                       |

| 22   | PGEC2/RPB11/D-/RB11                              |

| 23   | Vusb3v3                                          |

| 24   | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 25   | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 26   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 27   | AVss                                             |

| 28   | AVDD                                             |

Note 1

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3 "Peripheral Pin Select"** for restrictions.

- 2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information

- 3: Shaded pins are 5V tolerant.

## TABLE 12: PIN NAMES FOR 44-PIN USB DEVICES

44-PIN TQFP (TOP VIEW)(1,2,3,5)

PIC32MX210F016D PIC32MX220F032D PIC32MX230F064D PIC32MX230F256D PIC32MX250F128D PIC32MX270F256D

44

1

| Pin # | Full Pin Name                                    |

|-------|--------------------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                         |

| 2     | RPC6/PMA1/RC6                                    |

| 3     | RPC7/PMA0/RC7                                    |

| 4     | RPC8/PMA5/RC8                                    |

| 5     | RPC9/CTED7/PMA6/RC9                              |

| 6     | Vss                                              |

| 7     | VCAP                                             |

| 8     | PGED2/RPB10/D+/CTED11/RB10                       |

| 9     | PGEC2/RPB11/D-/RB11                              |

| 10    | VUSB3V3                                          |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10             |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7         |

| 14    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 16    | AVss                                             |

| 17    | AVDD                                             |

| 18    | MCLR                                             |

| 19    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 20    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       |

| Pin # | Full Pin Name                             |

|-------|-------------------------------------------|

| 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 25    | AN6/RPC0/RC0                              |

| 26    | AN7/RPC1/RC1                              |

| 27    | AN8/RPC2/PMA2/RC2                         |

| 28    | VDD                                       |

| 29    | Vss                                       |

| 30    | OSC1/CLKI/RPA2/RA2                        |

| 31    | OSC2/CLKO/RPA3/RA3                        |

| 32    | TDO/RPA8/PMA8/RA8                         |

| 33    | SOSCI/RPB4/RB4                            |

| 34    | SOSCO/RPA4/T1CK/CTED9/RA4                 |

| 35    | TDI/RPA9/PMA9/RA9                         |

| 36    | AN12/RPC3/RC3                             |

| 37    | RPC4/PMA4/RC4                             |

| 38    | RPC5/PMA3/RC5                             |

| 39    | Vss                                       |

| 40    | VDD                                       |

| 41    | RPB5/USBID/RB5                            |

| 42    | VBUS                                      |

| 43    | RPB7/CTED3/PMD5/INT0/RB7                  |

| 44    | RPB8/SCL1/CTED10/PMD4/RB8                 |

## Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3 "Peripheral Pin Select"** for restrictions.

- Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: This pin function is not available on PIC32MX210F016D and PIC32MX220F032D devices.

- 5: Shaded pins are 5V tolerant.

#### Referenced Sources

This device data sheet is based on the following individual chapters of the "PIC32 Family Reference Manual". These documents should be considered as the general reference for the operation of a particular module or device feature.

Note: To access the following documents, refer to the *Documentation* > *Reference Manuals* section of the Microchip PIC32 website: http://www.microchip.com/pic32

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

- Section 3. "Memory Organization" (DS60001115)

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer" (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Compare" (DS60001111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116)

- Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167)

NOTES:

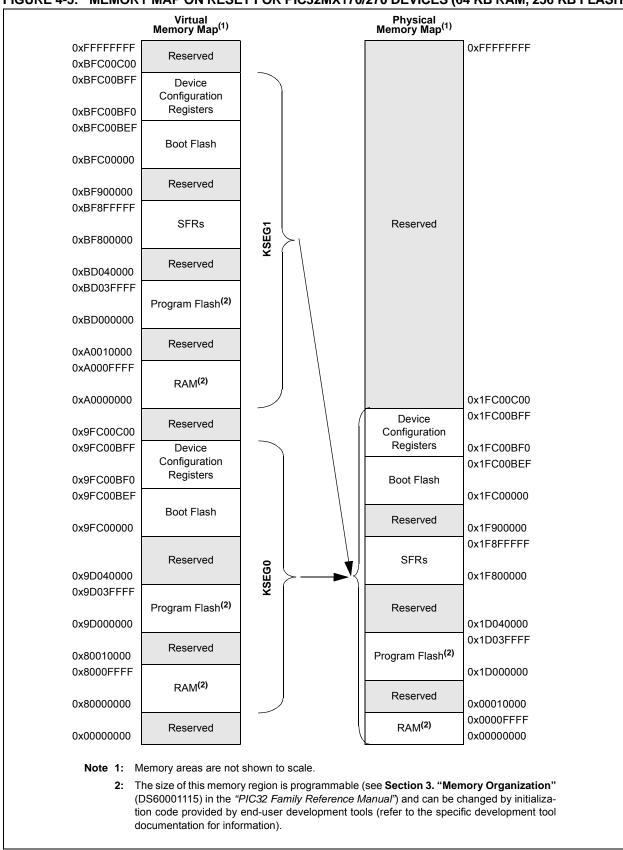

FIGURE 4-5: MEMORY MAP ON RESET FOR PIC32MX170/270 DEVICES (64 KB RAM, 256 KB FLASH)

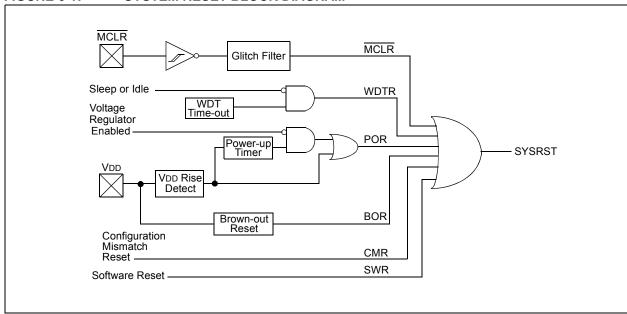

## 6.0 RESETS

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7.** "**Resets**" (DS60001118), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The following is a list of device Reset sources:

- Power-on Reset (POR)

- Master Clear Reset pin (MCLR)

- · Software Reset (SWR)

- Watchdog Timer Reset (WDTR)

- · Brown-out Reset (BOR)

- · Configuration Mismatch Reset (CMR)

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

FIGURE 6-1: SYSTEM RESET BLOCK DIAGRAM

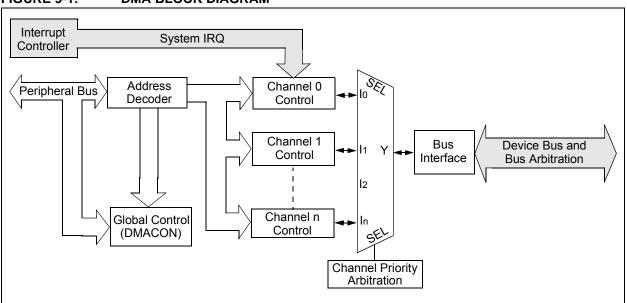

# 9.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32, such as Peripheral Bus devices: SPI, UART, PMP, etc., or memory itself. Figure 9-1 show a block diagram of the DMA Controller module.

The DMA Controller module has the following key features:

- · Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- · Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

- · Fixed priority channel arbitration

- Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt)

DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- · Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- · Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

FIGURE 9-1: DMA BLOCK DIAGRAM

## REGISTER 9-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|

| 24.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 31:24     |                   |                   |                   | CHSSA<            | 31:24>            |                   |                  |                  |  |  |  |  |  |  |  |

| 23:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

|           | CHSSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 15:8      |                   | CHSSA<15:8>       |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 7:0       |                   |                   |                   | CHSSA             | <7:0>             |                   |                  |                  |  |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 CHSSA<31:0> Channel Source Start Address bits

Channel source start address.

**Note:** This must be the physical address of the source.

## REGISTER 9-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | 28/20/12/4 27/19/11/3 |       | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-------|------------------|------------------|--|--|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0 | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 31:24        |                   |                   |                   | CHDSA<            | 31:24>                |       |                  |                  |  |  |  |  |  |  |

| 22:46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0 | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23:16        | CHDSA<23:16>      |                   |                   |                   |                       |       |                  |                  |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0 | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 15:8         | CHDSA<15:8>       |                   |                   |                   |                       |       |                  |                  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0 | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | CHDSA             | <7:0>                 |       |                  |                  |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 CHDSA<31:0>: Channel Destination Start Address bits

Channel destination start address.

**Note:** This must be the physical address of the destination.

## REGISTER 13-1: TXCON: TYPE B TIMER CONTROL REGISTER (CONTINUED)

bit 3 T32: 32-Bit Timer Mode Select bit<sup>(2)</sup>

1 = Odd numbered and even numbered timers form a 32-bit timer

0 = Odd numbered and even numbered timers form a separate 16-bit timer

bit 2 **Unimplemented:** Read as '0'

bit 1 **TCS**: Timer Clock Source Select bit<sup>(3)</sup>

1 = External clock from TxCK pin

0 = Internal peripheral clock

bit 0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3, and Timer5). All timer functions are set through the even numbered timers.

- **4:** While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

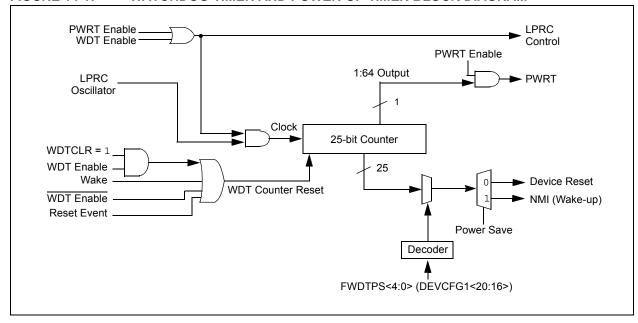

## 14.0 WATCHDOG TIMER (WDT)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 9. "Watchdog, Deadman, and Power-up Timers"** (DS60001114), which are available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The WDT, when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are some of the key features of the WDT module:

- · Configuration or software controlled

- · User-configurable time-out period

- · Can wake the device from Sleep or Idle mode

Figure 14-1 illustrates a block diagram of the WDT and Power-up timer.

FIGURE 14-1: WATCHDOG TIMER AND POWER-UP TIMER BLOCK DIAGRAM

| 1XX/2X | X 28/36 | 5/44-PIN      | HAMII                | _ Y                        |                             |

|--------|---------|---------------|----------------------|----------------------------|-----------------------------|

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        | 1XX/2X  | 1XX/2XX 28/36 | 1XX/2XX 28/36/44-PIN | 1XX/2XX 28/36/44-PIN FAMIL | 1XX/2XX 28/36/44-PIN FAMILY |

## REGISTER 21-4: RTCDATE: RTC DATE VALUE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-x R/W-x R/W-x |                   | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            |                  |  |  |  |

| 31:24        |                   | YEAR1             | 0<3:0>            |                   | YEAR01<3:0>       |                   |                  |                  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        | _                 | _                 | _                 | MONTH10           |                   | MONTH01<3:0>      |                  |                  |  |  |  |

| 45.0         | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         | _                 | _                 | DAY10             | )<1:0>            | DAY01<3:0>        |                   |                  |                  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          |                   | _                 | _                 |                   |                   | V                 | VDAY01<2:0       | >                |  |  |  |

### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10s place digit; contains a value from 0 to 9

bit 27-24 YEAR01<3:0>: Binary-Coded Decimal Value of Years bits, 1s place digit; contains a value from 0 to 9

bit 23-21 Unimplemented: Read as '0'

bit 20 MONTH10: Binary-Coded Decimal Value of Months bits, 10s place digit; contains a value of 0 or 1

bit 19-16 MONTH01<3:0>: Binary-Coded Decimal Value of Months bits, 1s place digit; contains a value from 0 to 9

bit 15-14 Unimplemented: Read as '0'

bit 13-12 DAY10<1:0>: Binary-Coded Decimal Value of Days bits, 10s place digit; contains a value of 0 to 3

bit 11-8 DAY01<3:0>: Binary-Coded Decimal Value of Days bits, 1s place digit; contains a value from 0 to 9

bit 7-3 Unimplemented: Read as '0'

bit 2-0 WDAY01<2:0>: Binary-Coded Decimal Value of Weekdays bits; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

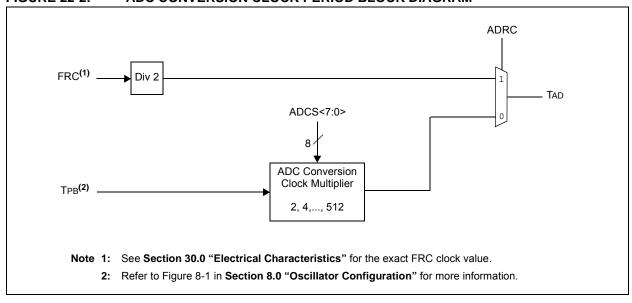

## FIGURE 22-2: ADC CONVERSION CLOCK PERIOD BLOCK DIAGRAM

# DS60001168J-page 211

## **ADC Control Registers**

## TABLE 22-1: ADC REGISTER MAP

| ess                         |                        | 4             |                                    |           |        |        |        |           |           | В                   | its                                     |                 |       |         |        |       |        |       |            |

|-----------------------------|------------------------|---------------|------------------------------------|-----------|--------|--------|--------|-----------|-----------|---------------------|-----------------------------------------|-----------------|-------|---------|--------|-------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range     | 31/15                              | 30/14     | 29/13  | 28/12  | 27/11  | 26/10     | 25/9      | 24/8                | 23/7                                    | 22/6            | 21/5  | 20/4    | 19/3   | 18/2  | 17/1   | 16/0  | All Resets |

|                             | AD1CON1 <sup>(1)</sup> | 31:16         | _                                  | _         | _      | _      | _      | _         | _         | _                   | _                                       | _               | _     | _       | _      | _     | _      | _     | 0000       |

| 9000                        | ADTCONTO,              | 15:0          | ON                                 | _         | SIDL   | _      | _      |           | FORM<2:0  | >                   | ;                                       | SSRC<2:0>       | >     | CLRASAM | _      | ASAM  | SAMP   | DONE  | 0000       |

| 9010                        | AD1CON2 <sup>(1)</sup> | 31:16         | _                                  | _         | _      | _      | _      | _         | _         | _                   | _                                       | -               | _     | _       | _      | _     | _      | _     | 0000       |

| 3010                        | ADTOONZ                | 15:0          | ,                                  | VCFG<2:0> | '      | OFFCAL | _      | CSCNA     | _         | _                   | BUFS                                    | _               |       | SMPI    | <3:0>  |       | BUFM   | ALTS  | 0000       |

| 9020                        | AD1CON3 <sup>(1)</sup> | 31:16         | _                                  | _         | _      | _      | _      | _         | _         | _                   | _                                       | _               | _     |         |        |       | _      | 0000  |            |

| 0020                        | , 15 100110            | 15:0          | ADRC                               | _         | _      |        |        | SAMC<4:0> |           |                     |                                         |                 |       | ADCS    | S<7:0> |       |        |       | 0000       |

| 9040                        | AD1CHS <sup>(1)</sup>  | 31:16         | CH0NB                              | _         |        | _      |        | CH0SI     | 3<3:0>    | ı                   | CH0NA                                   | _               | _     | _       |        | CH0S/ | A<3:0> |       | 0000       |

|                             |                        | 15:0          |                                    | _         | _      | _      |        |           |           | _                   | _                                       |                 | _     | _       | _      |       |        | _     | 0000       |

| 9050                        | AD1CSSL <sup>(1)</sup> | 31:16         |                                    | _         | _      | _      |        | _         | _         | _                   | _                                       | _               |       | _       | _      | _     | _      | _     | 0000       |

|                             |                        | 15:0          | CSSL15                             | CSSL14    | CSSL13 | CSSL12 | CSSL11 | CSSL10    | CSSL9     | CSSL8               | CSSL7                                   | CSSL6           | CSSL5 | CSSL4   | CSSL3  | CSSL2 | CSSL1  | CSSL0 | 0000       |

| 9070                        | ADC1BUF0               | 31:16         | ADC Result Word 0 (ADC1BUF0<31:0>) |           |        |        |        |           |           |                     |                                         |                 |       |         |        | 0000  |        |       |            |

|                             |                        | 15:0          |                                    |           |        |        |        |           |           |                     |                                         |                 |       |         |        | 0000  |        |       |            |

| 9080                        | ADC1BUF1               | 31:16<br>15:0 | ADC Result Word 1 (ADC1BUF1<31:0>) |           |        |        |        |           |           |                     |                                         |                 |       |         |        | 0000  |        |       |            |

|                             |                        | 31:16         |                                    |           |        |        |        |           |           |                     |                                         |                 |       |         | 0000   |       |        |       |            |

| 9090                        | ADC1BUF2               | 15:0          |                                    |           |        |        |        |           | ADC Res   | sult Word 2         | (ADC1BUF                                | 2<31:0>)        |       |         |        |       |        |       | 0000       |

|                             |                        | 31:16         |                                    |           |        |        |        |           |           |                     |                                         |                 |       |         |        |       |        |       | 0000       |

| 90A0                        | ADC1BUF3               | 15:0          |                                    |           |        |        |        |           | ADC Res   | sult Word 3         | (ADC1BUF                                | 3<31:0>)        |       |         |        |       |        |       | 0000       |

|                             |                        | 31:16         |                                    |           |        |        |        |           |           |                     |                                         |                 |       |         |        |       |        |       | 0000       |

| 90B0                        | ADC1BUF4               | 15:0          |                                    |           |        |        |        |           | ADC Res   | sult Word 4         | (ADC1BUF                                | 4<31:0>)        |       |         |        |       |        |       | 0000       |

|                             |                        | 31:16         |                                    |           |        |        |        |           |           |                     |                                         |                 |       |         |        |       |        |       | 0000       |

| 90C0                        | ADC1BUF5               | 15:0          |                                    |           |        |        |        |           | ADC Res   | sult Word 5         | (ADC1BUF                                | 5<31:0>)        |       |         |        |       |        |       | 0000       |

| 0000                        | ADO4DUEC               | 31:16         |                                    |           |        |        |        |           | 4 D.C. D  |                     | (ADC4DUE                                | 0 -104 -05 \    |       |         |        |       |        |       | 0000       |

| 9000                        | ADC1BUF6               | 15:0          |                                    |           |        |        |        |           | ADC Res   | sult Word 6         | (ADC1BUF                                | 6<31:0>)        |       |         |        |       |        |       | 0000       |

| 00E0                        | ADC1BUF7               | 31:16         |                                    |           |        |        |        |           | ADC Box   | sult Word 7         | (ADC1DLIE                               | 7/21:0>\        |       |         |        |       |        |       | 0000       |

| 9000                        | ADC IBUF1              | 15:0          |                                    |           |        |        |        |           | ADC RE    | suit vvoiu <i>i</i> | (ADC IBUF                               | /<31.02)        |       |         |        |       |        |       | 0000       |

| 90E0                        | ADC1BUF8               | 31:16         |                                    |           |        |        |        |           | ADC Per   | sult Word 8         | (ADC1BLIE                               | 8<31:0>1        |       |         |        |       |        |       | 0000       |

| 901.0                       | ADC IDOF0              | 15:0          |                                    |           |        |        |        |           | ADC RE    | ouit VVOIU O        |                                         | 0 - 0 1 . 0 ~ ) |       |         |        |       |        |       | 0000       |

| 9100                        | ADC1BUF9               | 31:16         |                                    |           |        |        | ·      |           | ADC Res   | sult Word 9         | (ADC1BLIE                               | 9<31:0>1        |       |         |        |       |        |       | 0000       |

| 3100                        | , .50 1501 9           | 15:0          |                                    |           |        |        |        |           | / IDO NO. | Jan Word 9          | (, ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 0 :01:0-)       |       |         |        |       |        |       | 0000       |

| 9110                        | ADC1BUFA               | 31:16         |                                    |           |        |        |        |           | ADC Res   | sult Word A         | (ADC1BUF                                | A<31:0>)        |       |         |        |       |        |       | 0000       |

|                             |                        | 15:0          |                                    |           |        |        |        |           | 0         |                     | ,                                       | ,               |       |         |        |       |        |       | 0000       |

**PIC32MX1XX/2XX 28/36/44-PIN FAMILY**

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

This register has corresponding CLR, SET and INV registers at its virtual address, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for details. Note 1:

## REGISTER 23-2: CMSTAT: COMPARATOR STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                                        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|----------------------------------------------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                                                      | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 | -                 | _                 | 1                                                        | -                 | _                | _                |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0                                                      | U-0               | U-0              | U-0              |

| 23:16        | -                 | _                 | _                 | _                 |                                                          |                   | _                | _                |

| 15:8         | U-0               | U-0               | R/W-0             | U-0               | U-0                                                      | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | SIDL              | _                 | 4 27/19/11/3 26/1  U-0  U-0  U-0  U-0  U-0  U-0  U-0  U- | _                 | _                | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0                                                      | R-0               | R-0              | R-0              |

| 7.0          | _                 | _                 | _                 | _                 |                                                          | C3OUT             | C2OUT            | C1OUT            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Control bit

1 = All Comparator modules are disabled when the device enters Idle mode

0 = All Comparator modules continue to operate when the device enters Idle mode

bit 12-3 Unimplemented: Read as '0'

bit 2 C3OUT: Comparator Output bit

1 = Output of Comparator 3 is a '1'

0 = Output of Comparator 3 is a '0'

bit 1 C2OUT: Comparator Output bit

1 = Output of Comparator 2 is a '1'

0 = Output of Comparator 2 is a '0'

bit 0 C10UT: Comparator Output bit

1 = Output of Comparator 1 is a '1'

0 = Output of Comparator 1 is a '0'

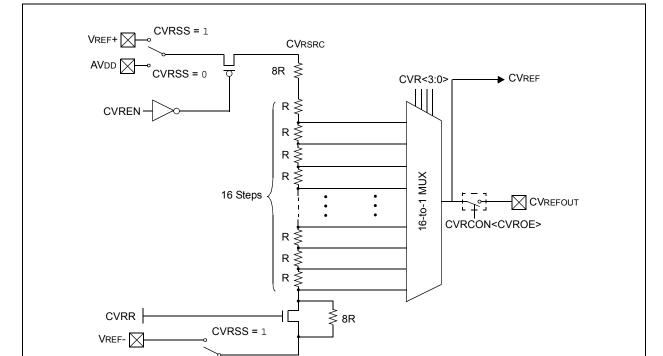

# 24.0 COMPARATOR VOLTAGE REFERENCE (CVREF)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 20.** "Comparator Voltage Reference (CVREF)" (DS60001109), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The CVREF module is a 16-tap, resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it also may be used independently of them.

The resistor ladder is segmented to provide two ranges of voltage reference values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/Vss or an external voltage reference. The CVREF output is available for the comparators and typically available for pin output.

The comparator voltage reference has the following features:

- · High and low range selection

- · Sixteen output levels available for each range

- Internally connected to comparators to conserve device pins

- · Output can be connected to a pin

A block diagram of the module is shown in Figure 24-1.

FIGURE 24-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

CVRSS = 0

AVss X

## 24.1 Comparator Voltage Reference Control Register

## TABLE 24-1: COMPARATOR VOLTAGE REFERENCE REGISTER MAP

| s e                         |                                 | ø.        | Bits  |       |       |       |       |       |      |      |      |       |      |       |      |      |      |      |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|-------|------|-------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6  | 21/5 | 20/4  | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 0000                        | O) (DOON                        | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _     | _    | _     | _    | _    | _    | _    | 0000       |

| 9800                        | CVRCON                          | 15:0      | ON    | _     | _     | _     |       | _     | _    | _    | _    | CVROE | CVRR | CVRSS |      | CVR< | 3:0> |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| I I C J Z I WI X I Z | 20/30/ | 7-7-1 II <b>V</b> |  |  |

|----------------------|--------|-------------------|--|--|

| NOTES:               |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

## APPENDIX A: REVISION HISTORY

## Revision A (May 2011)

This is the initial released version of this document.

## **Revision B (October 2011)**

The following two global changes are included in this revision:

- All packaging references to VLAP have been changed to VTLA throughout the document

- · All references to VCORE have been removed

- All occurrences of the ASCL1, ASCL2, ASDA1, and ASDA2 pins have been removed

- V-temp temperature range (-40°C to +105°C) was added to all electrical specification tables

This revision includes the addition of the following devices:

- PIC32MX130F064B

- PIC32MX230F064B

- PIC32MX130F064C

- PIC32MX230F064C

- PIC32MX130F064D

- PIC32MX230F064D

- PIC32MX150F128B

- PIC32MX250F128B

- PIC32MX150F128C

- PIC32MX250F128C

- PIC32MX150F128D

- PIC32MX250F128D

Text and formatting changes were incorporated throughout the document.

All other major changes are referenced by their respective section in Table A-1.

## TABLE A-1: MAJOR SECTION UPDATES

| Section                                                                                                                             | Update Description                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to 128 KE<br>Flash and 32 KB SRAM) with Audio<br>and Graphics Interfaces, USB, and<br>Advanced Analog" | Split the existing Features table into two: PIC32MX1XX General Purpose Family Features (Table 1) and PIC32MX2XX USB Family Features (Table 2).                            |

|                                                                                                                                     | Added the SPDIP package reference (see Table 1, Table 2, and "Pin Diagrams").                                                                                             |

|                                                                                                                                     | Added the new devices to the applicable pin diagrams.                                                                                                                     |

|                                                                                                                                     | Changed PGED2 to PGED1 on pin 35 of the 36-pin VTLA diagram for PIC32MX220F032C, PIC32MX220F016C, PIC32MX230F064C, and PIC32MX250F128C devices.                           |

| 1.0 "Device Overview"                                                                                                               | Added the SPDIP package reference and updated the pin number for AN12 for 44-pin QFN devices in the Pinout I/O Descriptions (see Table 1-1).                              |

|                                                                                                                                     | Added the PGEC4/PGED4 pin pair and updated the C1INA-C1IND and C2INA-C2IND pin numbers for 28-pin SSOP/SPDIP/SOIC devices in the Pinout I/O Descriptions (see Table 1-1). |

| 2.0 "Guidelines for Getting Started with 32-bit Microcontrollers"                                                                   | Updated the Recommended Minimum Connection diagram (see Figure 2-1).                                                                                                      |

TABLE A-1: MAJOR SECTION UPDATES (CONTINUED)

| Section                           | Update Description                                                                                                                                    |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29.0 "Electrical Characteristics" | Updated the Absolute Maximum Ratings (removed Voltage on VCORE with respect to Vss).                                                                  |

|                                   | Added the SPDIP specification to the Thermal Packaging Characteristics (see Table 29-2).                                                              |

|                                   | Updated the Typical values for parameters DC20-DC24 in the Operating Current (IDD) specification (see Table 29-5).                                    |

|                                   | Updated the Typical values for parameters DC30a-DC34a in the Idle Current (IIDLE) specification (see Table 29-6).                                     |

|                                   | Updated the Typical values for parameters DC40i and DC40n and removed parameter DC40m in the Power-down Current (IPD) specification (see Table 29-7). |

|                                   | Removed parameter D320 (VCORE) from the Internal Voltage Regulator Specifications and updated the Comments (see Table 29-13).                         |

|                                   | Updated the Minimum, Typical, and Maximum values for parameter F20b in the Internal FRC Accuracy specification (see Table 29-17).                     |

|                                   | Removed parameter SY01 (TPWRT) and removed all Conditions from Resets Timing (see Table 29-20).                                                       |

|                                   | Updated all parameters in the CTMU Specifications (see Table 29-39).                                                                                  |

| 31.0 "Packaging Information"      | Added the 28-lead SPDIP package diagram information (see <b>31.1 "Package Marking Information"</b> and <b>31.2 "Package Details"</b> ).               |

| "Product Identification System"   | Added the SPDIP (SP) package definition.                                                                                                              |

## **Revision C (November 2011)**

All major changes are referenced by their respective section in Table A-2.

TABLE A-2: MAJOR SECTION UPDATES

| Section                                                                                                                    | Update Description                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to 128 KB Flash and 32 KB SRAM) with Audio and Graphics Interfaces, USB, and Advanced Analog" | Revised the source/sink on I/O pins (see "Input/Output" on page 1).  Added the SPDIP package to the PIC32MX220F032B device in the PIC32MX2XX USB Family Features (see Table 2). |

| 4.0 "Memory Organization"                                                                                                  | Removed ANSB6 from the ANSELB register and added the ODCB6, ODCB10, and ODCB11 bits in the PORTB Register Map (see Table 4-20).                                                 |

| 29.0 "Electrical Characteristics"                                                                                          | Updated the minimum value for parameter OS50 in the PLL Clock Timing Specifications (see Table 29-16).                                                                          |