Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 25                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 12x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 36-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 36-VTLA (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx210f016ct-i-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 10: PIN NAMES FOR 44-PIN USB DEVICES

# 44-PIN QFN (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX210F016D PIC32MX220F032D PIC32MX230F064D PIC32MX230F256D PIC32MX250F128D PIC32MX270F256D

|       |                                                  |       | 44 1                                      |

|-------|--------------------------------------------------|-------|-------------------------------------------|

| Pin # | Full Pin Name                                    | Pin # | Full Pin Name                             |

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                         | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 2     | RPC6/PMA1/RC6                                    | 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 3     | RPC7/PMA0/RC7                                    | 25    | AN6/RPC0/RC0                              |

| 4     | RPC8/PMA5/RC8                                    | 26    | AN7/RPC1/RC1                              |

| 5     | RPC9/CTED7/PMA6/RC9                              | 27    | AN8/RPC2/PMA2/RC2                         |

| 6     | Vss                                              | 28    | Vdd                                       |

| 7     | VCAP                                             | 29    | Vss                                       |

| 8     | PGED2/RPB10/D+/CTED11/RB10                       | 30    | OSC1/CLKI/RPA2/RA2                        |

| 9     | PGEC2/RPB11/D-/RB11                              | 31    | OSC2/CLKO/RPA3/RA3                        |

| 10    | VUSB3V3                                          | 32    | TDO/RPA8/PMA8/RA8                         |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                       | 33    | SOSCI/RPB4/RB4                            |

| 12    | PGED4/TMS/PMA10/RA10                             | 34    | SOSCO/RPA4/T1CK/CTED9/RA4                 |

| 13    | PGEC4/TCK/CTED8/PMA7/RA7                         | 35    | TDI/RPA9/PMA9/RA9                         |

| 14    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 | 36    | AN12/RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            | 37    | RPC4/PMA4/RC4                             |

| 16    | AVss                                             | 38    | RPC5/PMA3/RC5                             |

| 17    | AVDD                                             | 39    | Vss                                       |

| 18    | MCLR                                             | 40    | Vdd                                       |

| 19    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 | 41    | RPB5/USBID/RB5                            |

| 20    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       | 42    | VBUS                                      |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        | 43    | RPB7/CTED3/PMD5/INT0/RB7                  |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       | 44    | RPB8/SCL1/CTED10/PMD4/RB8                 |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

5: Shaded pins are 5V tolerant.

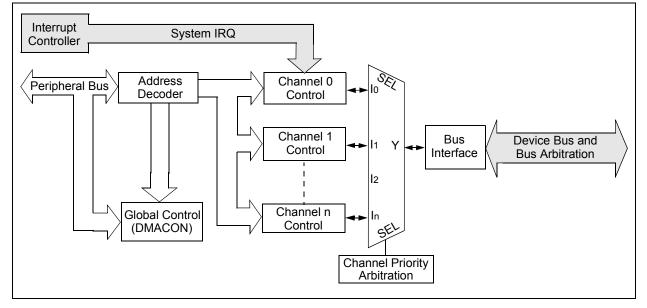

# 9.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32, such as Peripheral Bus devices: SPI, UART, PMP, etc., or memory itself. Figure 9-1 show a block diagram of the DMA Controller module.

The DMA Controller module has the following key features:

- Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

### FIGURE 9-1: DMA BLOCK DIAGRAM

- Fixed priority channel arbitration

- · Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- · Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- · Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

# TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       | - /   |       |      |      | Bit  | s    |      |          |        |        |         |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 5390                        | U1EP9                           | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |      | _    | —    | —        | —      | _      | —       | —      | 0000       |

| 5590                        | UIEF9                           | 15:0      |       |       | —     | —     | —     | —     | _    | —    |      |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5040                        | U1EP10                          | 31:16     | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | —        | _      | _      | —       | _      | 0000       |

| 53A0                        | UTEPTU                          | 15:0      |       | _     | _     | -     | _     | _     | _    | _    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                        |                                 | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 53BU                        | U1EP11                          | 15:0      | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                        | U1EP12                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEFIZ                          | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53D0                        | U1EP13                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEF 13                         | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     |       | _     | _     |       | -     | _     | _    | _    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 53E0                        | U1EP14                          | 15:0      | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | —        | _      | _      | _       | _      | 0000       |

| 53F0                        | U1EP15                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | —    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 |                   |                   |                   | —                 |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | —                 |                   |                   | -                 | —                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | -                 | —                 | —                 | -                 | -                 | —                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | R/W-0            |

| 7:0          | IDIE              | T1MSECIE          | LSTATEIE          | ACTVIE            | SESVDIE           | SESENDIE          |                  | VBUSVDIE         |

# REGISTER 10-2: U1OTGIE: USB OTG INTERRUPT ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIE:** ID Interrupt Enable bit

- 1 = ID interrupt is enabled

- 0 = ID interrupt is disabled

#### bit 6 T1MSECIE: 1 Millisecond Timer Interrupt Enable bit

- 1 = 1 millisecond timer interrupt is enabled

- 0 = 1 millisecond timer interrupt is disabled

#### bit 5 LSTATEIE: Line State Interrupt Enable bit

- 1 = Line state interrupt is enabled

- 0 = Line state interrupt is disabled

- bit 4 ACTVIE: Bus Activity Interrupt Enable bit

- 1 = Activity interrupt is enabled

- 0 = Activity interrupt is disabled

- bit 3 SESVDIE: Session Valid Interrupt Enable bit

- 1 = Session valid interrupt is enabled

- 0 = Session valid interrupt is disabled

- bit 2 SESENDIE: B-Device Session End Interrupt Enable bit

- 1 = B-Device session end interrupt is enabled

- 0 = B-Device session end interrupt is disabled

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIE: A-Device VBUS Valid Interrupt Enable bit

- 1 = A-Device VBUS valid interrupt is enabled

- 0 = A-Device VBUS valid interrupt is disabled

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### REGISTER 10-3: U1OTGSTAT: USB OTG STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 51.24        | -                 | —                 | —                 | —                 | _                 | —                 | —                | —                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        | -                 | —                 | —                 | —                 | _                 | —                 | —                | —                |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0         |                   | —                 | —                 | —                 | _                 | —                 |                  | —                |  |  |  |

| 7:0          | R-0               | U-0               | R-0               | U-0               | R-0               | R-0               | U-0              | R-0              |  |  |  |

| 7.0          | ID                |                   | LSTATE            | _                 | SESVD             | SESEND            | _                | VBUSVD           |  |  |  |

### Legend:

| Logona.           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 ID: ID Pin State Indicator bit

- 1 = No cable is attached or a "type B" cable has been inserted into the USB receptacle

- 0 = A "type A" OTG cable has been inserted into the USB receptacle

- bit 6 Unimplemented: Read as '0'

- bit 5 LSTATE: Line State Stable Indicator bit

- 1 = USB line state (SE0 (U1CON<6>) bit and JSTATE (U1CON<7>)) bit has been stable for previous 1 ms 0 = USB line state (SE0 and JSTATE) has not been stable for previous 1 ms

#### bit 4 Unimplemented: Read as '0'

- bit 3 SESVD: Session Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A or B device

- 0 = VBUS voltage is below Session Valid on the A or B device

- bit 2 SESEND: B-Device Session End Indicator bit

- 1 = VBUS voltage is below Session Valid on the B device

- 0 = VBUS voltage is above Session Valid on the B device

#### bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVD: A-Device VBUS Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A device

- 0 = VBUS voltage is below Session Valid on the A device

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |  |  |  |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|--|--|--|

| 24.04        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |  |  |  |

| 31:24        | —                 | —                 | —                        | _                 | —                     | —                     |                  | _                    |  |  |  |

| 22:16        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |  |  |  |

| 23:16        | —                 | —                 | —                        | -                 | —                     | _                     | _                | _                    |  |  |  |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |  |  |  |

| 15.0         | —                 | —                 | —                        | -                 | —                     | _                     | _                | _                    |  |  |  |

|              | R-x               | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |  |  |  |

| 7:0          | JSTATE            | SE0               | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST           | USBEN <sup>(4)</sup> |  |  |  |

|              |                   |                   | TOKBUSY <sup>(1,5)</sup> |                   |                       |                       |                  | SOFEN <sup>(5)</sup> |  |  |  |

# REGISTER 10-11: U1CON: USB CONTROL REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **JSTATE:** Live Differential Receiver JSTATE flag bit 1 = JSTATE was detected on the USB

- 0 = No JSTATE was detected on the

- bit 6 **SE0:** Live Single-Ended Zero flag bit 1 = Single-Ended Zero was detected on the USB

- 0 = No Single-Ended Zero was detected

- bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

- 1 = Token and packet processing is disabled (set upon SETUP token received)

- 0 = Token and packet processing is enabled

- TOKBUSY: Token Busy Indicator bit<sup>(1,5)</sup>

- 1 = Token is being executed by the USB module

- 0 = No token is being executed

### bit 4 USBRST: Module Reset bit<sup>(5)</sup>

- 1 = USB reset generated

- 0 = USB reset terminated

- bit 3 HOSTEN: Host Mode Enable bit<sup>(2)</sup>

- 1 = USB host capability is enabled

- 0 = USB host capability is disabled

- bit 2 RESUME: RESUME Signaling Enable bit<sup>(3)</sup>

- 1 = RESUME signaling is activated

- 0 = RESUME signaling is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0         | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          | —                 | —                 | _                 | —                 | —                 |                   | FRMH<2:0>        |                  |  |  |  |

#### REGISTER 10-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

# Legend:

| 0                 |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-3 Unimplemented: Read as '0'

bit 2-0 **FRMH<2:0>:** The Upper 3 bits of the Frame Numbers bits The register bits are updated with the current frame number whenever a SOF TOKEN is received.

#### Bit Bit Bit Bit Bit Bit Bit Bit Bit 30/22/14/6 27/19/11/3 26/18/10/2 25/17/9/1 24/16/8/0 Range 31/23/15/7 29/21/13/5 28/20/12/4 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 31:24 \_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 23:16 \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 15:8 \_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 7:0 PID < 3:0 > (1)EP<3:0>

# **REGISTER 10-15: U1TOK: USB TOKEN REGISTER**

| Legend:           |                        |                                  |                    |  |

|-------------------|------------------------|----------------------------------|--------------------|--|

| R = Readable bit  | U = Unimplemented bit, | = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set       | '0' = Bit is cleared             | x = Bit is unknown |  |

### bit 31-8 Unimplemented: Read as '0'

bit 7-4 **PID<3:0>:** Token Type Indicator bits<sup>(1)</sup>

1101 = SETUP (TX) token type transaction

- 1001 = IN (RX) token type transaction

- 0001 = OUT (TX) token type transaction

Note: All other values are reserved and must not be used.

bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits The four bit value must specify a valid endpoint.

Note 1: All other values are reserved and must not be used.

# REGISTER 13-1: TXCON: TYPE B TIMER CONTROL REGISTER (CONTINUED)

- bit 3 T32: 32-Bit Timer Mode Select bit<sup>(2)</sup>

- 1 = Odd numbered and even numbered timers form a 32-bit timer

- 0 = Odd numbered and even numbered timers form a separate 16-bit timer

- bit 2 Unimplemented: Read as '0'

- bit 1 **TCS:** Timer Clock Source Select bit<sup>(3)</sup>

- 1 = External clock from TxCK pin

- 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3, and Timer5). All timer functions are set through the even numbered timers.

- 4: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 02:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | —                 | -                 | -                 | _                 | _                 | -                | —                |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8      | 0N <sup>(1)</sup> | —                 | SIDL              | _                 | _                 | _                 | FEDGE            | C32              |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | ICTMR             | ICI<              | 1:0>              | ICOV              | ICBNE             |                   | ICM<2:0>         |                  |

# REGISTER 15-1: ICxCON: INPUT CAPTURE 'x' CONTROL REGISTER

# Legend:

| R = Readable bit                           | W = Writable bit | U = Unimplemented bit |                  |

|--------------------------------------------|------------------|-----------------------|------------------|

| -n = Bit Value at POR: ('0', '1', x = unkn | own)             | P = Programmable bit  | r = Reserved bit |

| bit 31-16 | Unimplemented: Read as '0'                                                                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | <b>ON:</b> Input Capture Module Enable bit <sup>(1)</sup>                                                                                                                                |

|           | 1 = Module is enabled                                                                                                                                                                    |

|           | 0 = Disable and reset module, disable clocks, disable interrupt generation and allow SFR modifications                                                                                   |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 13    | SIDL: Stop in Idle Control bit                                                                                                                                                           |

|           | <ul> <li>1 = Halt in Idle mode</li> <li>0 = Continue to operate in Idle mode</li> </ul>                                                                                                  |

| bit 12-10 | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 9     | FEDGE: First Capture Edge Select bit (only used in mode 6, ICM<2:0> = 110)                                                                                                               |

|           | 1 = Capture rising edge first                                                                                                                                                            |

|           | 0 = Capture falling edge first                                                                                                                                                           |

| bit 8     | C32: 32-bit Capture Select bit                                                                                                                                                           |

|           | 1 = 32-bit timer resource capture                                                                                                                                                        |

|           | 0 = 16-bit timer resource capture                                                                                                                                                        |

| bit 7     | ICTMR: Timer Select bit (Does not affect timer selection when C32 (ICxCON<8>) is '1')                                                                                                    |

|           | 0 = Timer3 is the counter source for capture                                                                                                                                             |

|           | 1 = Timer2 is the counter source for capture                                                                                                                                             |

| bit 6-5   | ICI<1:0>: Interrupt Control bits                                                                                                                                                         |

|           | <ul> <li>11 = Interrupt on every fourth capture event</li> <li>10 = Interrupt on every third capture event</li> </ul>                                                                    |

|           | 01 = Interrupt on every second capture event                                                                                                                                             |

|           | 00 = Interrupt on every capture event                                                                                                                                                    |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                                                 |

|           | 1 = Input capture overflow has occurred                                                                                                                                                  |

|           | 0 = No input capture overflow has occurred                                                                                                                                               |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                                                             |

|           | <ul> <li>1 = Input capture buffer is not empty; at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>                                        |

| Note 1:   | When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. |

|           | STOCEN Gyole infinediately following the instruction that deals the module's ON bit.                                                                                                     |

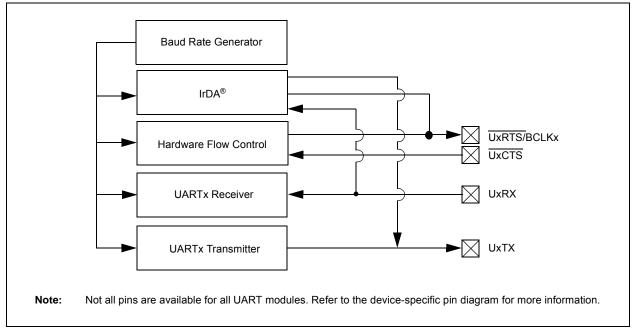

# 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The UART module is one of the serial I/O modules available in PIC32MX1XX/2XX 28/36/44-pin Family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN, and IrDA<sup>®</sup>. The UART module also supports the hardware flow control option, with UXCTS and UXRTS pins, and also includes an IrDA encoder and decoder.

Key features of the UART module include:

- Full-duplex, 8-bit or 9-bit data transmission

- Even, Odd or No Parity options (for 8-bit data)

- · One or two Stop bits

- Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 38 bps to 12.5 Mbps at 50 MHz

- 8-level deep First In First Out (FIFO) transmit data buffer

- 8-level deep FIFO receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (9th bit = 1)

- · Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- · LIN protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 19-1 illustrates a simplified block diagram of the UART module.

### FIGURE 19-1: UART SIMPLIFIED BLOCK DIAGRAM

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 | —                 | _                 | —                 | —                 | —                | -                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | _                 | —                 | _                 | _                 | _                 | —                 | —                | -                |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | CSSL15            | CSSL14            | CSSL13            | CSSL12            | CSSL11            | CSSL10            | CSSL9            | CSSL8            |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              | CSSL7             | CSSL6             | CSSL5             | CSSL4             | CSSL3             | CSSL2             | CSSL1            | CSSL0            |  |

# REGISTER 22-5: AD1CSSL: ADC INPUT SCAN SELECT REGISTER

# Legend:

| Logona.           |                                 |                      |                                    |  |  |  |

|-------------------|---------------------------------|----------------------|------------------------------------|--|--|--|

| R = Readable bit  | = Readable bit W = Writable bit |                      | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set                | '0' = Bit is cleared | x = Bit is unknown                 |  |  |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CSSL<15:0>: ADC Input Pin Scan Selection bits<sup>(1,2)</sup>

1 = Select ANx for input scan

0 = Skip ANx for input scan

- **Note 1:** CSSL = ANx, where 'x' = 0-12; CSSL13 selects CTMU input for scan; CSSL14 selects IVREF for scan; CSSL15 selects Vss for scan.

- 2: On devices with less than 13 analog inputs, all CSSLx bits can be selected; however, inputs selected for scan without a corresponding input on the device will convert to VREFL.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 | _                 | —                 | _                 |                   | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | CVROE             | CVRR              | CVRSS             |                   | CVR<              | <3:0>            |                  |

# **REGISTER 24-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER**

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator Voltage Reference On bit<sup>(1)</sup>

- 1 = Module is enabled

- Setting this bit does not affect other bits in the register.

- 0 = Module is disabled and does not consume current.

- Clearing this bit does not affect the other bits in the register.

- bit 14-7 Unimplemented: Read as '0'

- bit 6 **CVROE:** CVREFOUT Enable bit

- 1 = Voltage level is output on CVREFOUT pin

- 0 = Voltage level is disconnected from CVREFOUT pin

- bit 5 CVRR: CVREF Range Selection bit

- 1 = 0 to 0.67 CVRSRC, with CVRSRC/24 step size

- 0 = 0.25 CVRSRC to 0.75 CVRSRC, with CVRSRC/32 step size

- bit 4 **CVRSS:** CVREF Source Selection bit

- 1 = Comparator voltage reference source, CVRSRC = (VREF+) (VREF-)

- 0 = Comparator voltage reference source, CVRSRC = AVDD AVSS

- bit 3-0 **CVR<3:0>:** CVREF Value Selection  $0 \le CVR<3:0> \le 15$  bits

<u>When CVRR = 1:</u> CVREF = (CVR<3:0>/24) • (CVRSRC) <u>When CVRR = 0:</u> CVREF = 1/4 • (CVRSRC) + (CVR<3:0>/32) • (CVRSRC)

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| DC CHARACTERISTICS |        |                                                           | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |         |      |       |                                                                                         |

|--------------------|--------|-----------------------------------------------------------|-------------------------------------------------------|---------|------|-------|-----------------------------------------------------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics                                           | Min.                                                  | Typical | Max. | Units | Comments                                                                                |

| D300               | VIOFF  | Input Offset Voltage                                      | -                                                     | ±7.5    | ±25  | mV    | AVDD = VDD,<br>AVSS = VSS                                                               |

| D301               | VICM   | Input Common Mode Voltage                                 | 0                                                     | -       | Vdd  | V     | AVDD = VDD,<br>AVss = Vss<br>(Note 2)                                                   |

| D302               | CMRR   | Common Mode Rejection Ratio                               | 55                                                    | —       | _    | dB    | Max VICM = (VDD - 1)V<br>(Note 2)                                                       |

| D303A              | Tresp  | Large Signal Response Time                                | _                                                     | 150     | 400  | ns    | AVDD = VDD, AVSS = VSS<br>(Note 1,2)                                                    |

| D303B              | TSRESP | Small Signal Response Time                                | -                                                     | 1       | _    | μS    | This is defined as an input<br>step of 50 mV with 15 mV<br>of overdrive <b>(Note 2)</b> |

| D304               | ON2ov  | Comparator Enabled to Output<br>Valid                     | _                                                     | _       | 10   | μs    | Comparator module is<br>configured before setting<br>the comparator ON bit<br>(Note 2)  |

| D305               | IVREF  | Internal Voltage Reference                                | 1.14                                                  | 1.2     | 1.26 | V     | _                                                                                       |

| D312               | TSET   | Internal Comparator Voltage<br>DRC Reference Setting time | _                                                     | —       | 10   | μs    | (Note 3)                                                                                |

# TABLE 30-13: COMPARATOR SPECIFICATIONS

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

**2:** These parameters are characterized but not tested.

**3:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

**4:** The Comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

| AC CHARAG                                | S <sup>(2)</sup> | (unless of | Operating<br>herwise state<br>temperature |                 |                            |

|------------------------------------------|------------------|------------|-------------------------------------------|-----------------|----------------------------|

| ADC Speed TAD Min. Sampling<br>Time Min. |                  |            | Rs Max.                                   | Vdd             | ADC Channels Configuration |

| 1 Msps to 400 ksps <sup>(1)</sup>        | 65 ns            | 132 ns     | 500Ω                                      | 3.0V to<br>3.6V | ANX CHX ADC                |

| Up to 400 ksps                           | 200 ns           | 200 ns     | 5.0 kΩ                                    | 2.5V to<br>3.6V | ANX CHX<br>ANX OF VREF-    |

### TABLE 30-35:10-BIT CONVERSION RATE PARAMETERS

**Note 1:** External VREF- and VREF+ pins must be used for correct operation.

2: These parameters are characterized, but not tested in manufacturing.

**3:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

# 33.2 Package Details

This section provides the technical details of the packages.

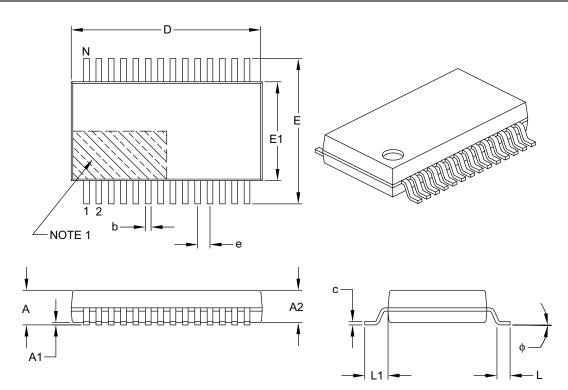

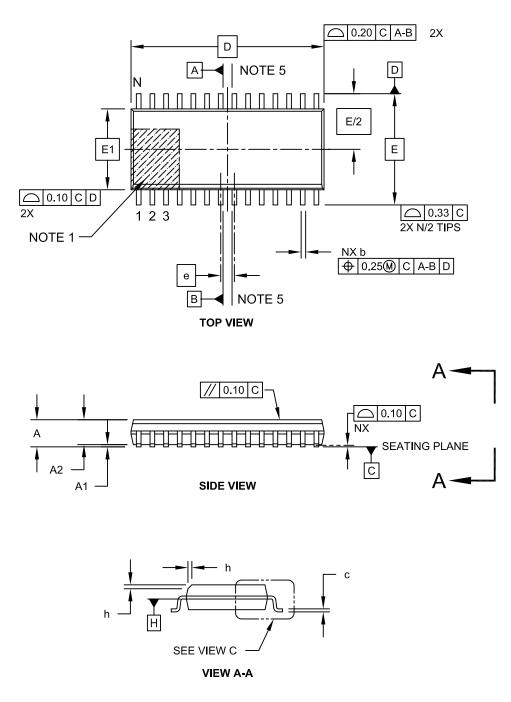

# 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |          |       |  |

|--------------------------|------------------|-------------|----------|-------|--|

|                          | Dimension Limits | MIN         | NOM      | MAX   |  |

| Number of Pins           | N                |             | 28       |       |  |

| Pitch                    | e                |             | 0.65 BSC |       |  |

| Overall Height           | A                | -           | -        | 2.00  |  |

| Molded Package Thickness | A2               | 1.65        | 1.75     | 1.85  |  |

| Standoff                 | A1               | 0.05        | -        | -     |  |

| Overall Width            | E                | 7.40        | 7.80     | 8.20  |  |

| Molded Package Width     | E1               | 5.00        | 5.30     | 5.60  |  |

| Overall Length           | D                | 9.90        | 10.20    | 10.50 |  |

| Foot Length              | L                | 0.55        | 0.75     | 0.95  |  |

| Footprint                | L1               |             | 1.25 REF |       |  |

| Lead Thickness           | С                | 0.09        | -        | 0.25  |  |

| Foot Angle               | φ                | 0°          | 4°       | 8°    |  |

| Lead Width               | b                | 0.22        | -        | 0.38  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

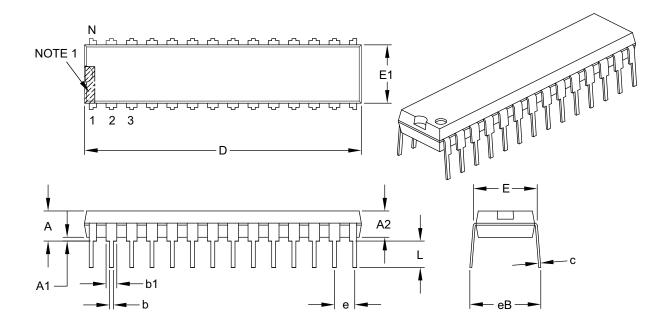

# 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |       | INCHES   |       |

|----------------------------|----------|-------|----------|-------|

| Dimension                  | n Limits | MIN   | NOM      | MAX   |

| Number of Pins             | Ν        |       | 28       |       |

| Pitch                      | е        |       | .100 BSC |       |

| Top to Seating Plane       | Α        | -     | -        | .200  |

| Molded Package Thickness   | A2       | .120  | .135     | .150  |

| Base to Seating Plane      | A1       | .015  | -        | -     |

| Shoulder to Shoulder Width | Е        | .290  | .310     | .335  |

| Molded Package Width       | E1       | .240  | .285     | .295  |

| Overall Length             | D        | 1.345 | 1.365    | 1.400 |

| Tip to Seating Plane       | L        | .110  | .130     | .150  |

| Lead Thickness             | С        | .008  | .010     | .015  |

| Upper Lead Width           | b1       | .040  | .050     | .070  |

| Lower Lead Width           | b        | .014  | .018     | .022  |

| Overall Row Spacing §      | eВ       | -     | -        | .430  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

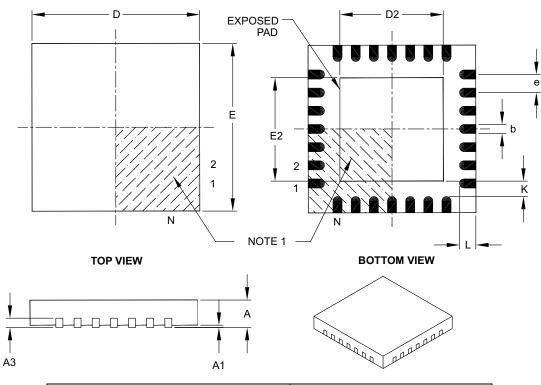

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units       | MILLIMETERS |          |      |  |

|------------------------|-------------|-------------|----------|------|--|

| Dimens                 | sion Limits | MIN         | NOM      | MAX  |  |

| Number of Pins         | Ν           |             | 28       |      |  |

| Pitch                  | е           |             | 0.65 BSC |      |  |

| Overall Height         | Α           | 0.80        | 0.90     | 1.00 |  |

| Standoff               | A1          | 0.00        | 0.02     | 0.05 |  |

| Contact Thickness      | A3          | 0.20 REF    |          |      |  |

| Overall Width          | Е           | 6.00 BSC    |          |      |  |

| Exposed Pad Width      | E2          | 3.65        | 3.70     | 4.20 |  |

| Overall Length         | D           |             | 6.00 BSC |      |  |

| Exposed Pad Length     | D2          | 3.65        | 3.70     | 4.20 |  |

| Contact Width          | b           | 0.23        | 0.30     | 0.35 |  |

| Contact Length         | L           | 0.50        | 0.55     | 0.70 |  |

| Contact-to-Exposed Pad | К           | 0.20        | -        | -    |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

# Revision G (April 2015)

This revision includes the addition of the following devices:

- PIC32MX130F256B PIC32MX230F256B

- PIC32MX130F256D PIC32MX230F256D

The title of the document was updated to avoid confusion with the PIC32MX1XX/2XX/5XX 64/100-pin Family data sheet.

### TABLE A-6: MAJOR SECTION UPDATES

All peripheral SFR maps have been relocated from the Memory chapter to their respective peripheral chapters.

In addition, this revision includes the following major changes as described in Table A-6, as well as minor updates to text and formatting, which were incorporated throughout the document.

| Section                                                                                                                           | Update Description                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32-bit Microcontrollers (up to 256<br>KB Flash and 64 KB SRAM) with<br>Audio and Graphics Interfaces,<br>USB, and Advanced Analog | Added new devices to the family features (see Table 1 and Table 2).<br>Updated pin diagrams to include new devices (see Pin Diagrams).                                                          |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"                                                                          | Updated these sections: 2.2 "Decoupling Capacitors", 2.3 "Capacitor on<br>Internal Voltage Regulator (VCAP)", 2.4 "Master Clear (MCLR) Pin",<br>2.8.1 "Crystal Oscillator Design Consideration" |

| 4.0 "Memory Organization"                                                                                                         | Added Memory Map for new devices (see Figure 4-6).                                                                                                                                              |

| 14.0 "Watchdog Timer (WDT)"                                                                                                       | New chapter created from content previously located in the Special Features chapter.                                                                                                            |

| 30.0 "Electrical Characteristics"                                                                                                 | Removed parameter D312 (TSET) from the Comparator Specifications (see Table 30-12).                                                                                                             |

|                                                                                                                                   | Added the Comparator Voltage Reference Specifications (see Table 30-13).                                                                                                                        |

|                                                                                                                                   | Updated Table 30-12.                                                                                                                                                                            |

# **Revision H (July 2015)**

This revision includes the following major changes as described in Table A-7, as well as minor updates to text and formatting, which were incorporated throughout the document.

### TABLE A-7: MAJOR SECTION UPDATES

| Section                                                  | Update Description                                                                                    |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs" | Section 2.9 "Sosc Design Recommendation" was removed.                                                 |

| 8.0 "Oscillator Configuration"                           | The Primary Oscillator (Posc) logic in the Oscillator diagram was updated (see Figure 8-1).           |

| 30.0 "Electrical Characteristics"                        | The Power-Down Current (IPD) DC Characteristics parameter DC40k was updated (see Table 30-7).         |

|                                                          | Table 30-9: "DC Characteristics: I/O Pin Input Injection current           Specifications" was added. |

# Revision J (April 2016)

This revision includes the following major changes as described in Table A-8, as well as minor updates to text and formatting, which were incorporated throughout the document.

# TABLE A-8: MAJOR SECTION UPDATES

| Section                                                                                                                                | Update Description                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to<br>256 KB Flash and 64 KB<br>SRAM) with Audio and<br>Graphics Interfaces, USB, and<br>Advanced Analog" | The PIC32MX270FDB device and Note 4 were added to <b>TABLE 2: "PIC32MX2XX</b><br><b>28/36/44-pin USB Family Features"</b> .       |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"                                                                               | EXAMPLE 2-1: "Crystal Load Capacitor Calculation" was updated.                                                                    |

| 30.0 "Electrical<br>Characteristics"                                                                                                   | Parameter DO50a (Csosc) was removed from the Capacitive Loading Requirements on Output Pins AC Characteristics (see Table 30-16). |

| "Product Identification<br>System"                                                                                                     | The device mapping was updated to include type B for Software Targeting.                                                          |