Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 25                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

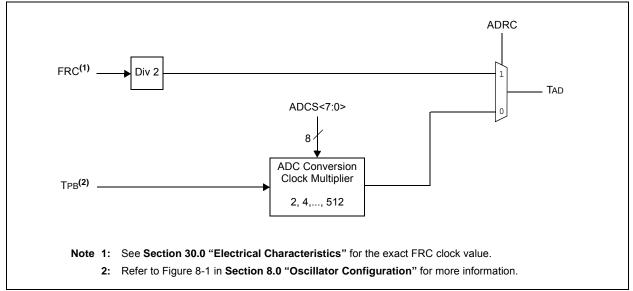

| Data Converters            | A/D 12x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 36-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 36-VTLA (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx210f016ct-v-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 6: PIN NAMES FOR 28-PIN USB DEVICES

#### 28-PIN QFN (TOP VIEW)<sup>(1,2,3,4)</sup>

PIC32MX210F016B PIC32MX220F032B PIC32MX230F064B PIC32MX230F256B PIC32MX250F128B PIC32MX250F128B

28

1

| Pin # | Full Pin Name                              | Pin # | Full Pin Name                                    |

|-------|--------------------------------------------|-------|--------------------------------------------------|

| 1     | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0  | 15    | TDO/RPB9/SDA1/CTED4/PMD3/RB9                     |

| 2     | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1 | 16    | Vss                                              |

| 3     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2  | 17    | VCAP                                             |

| 4     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3    | 18    | PGED2/RPB10/D+/CTED11/RB10                       |

| 5     | Vss                                        | 19    | PGEC2/RPB11/D-/RB11                              |

| 6     | OSC1/CLKI/RPA2/RA2                         | 20    | VUSB3V3                                          |

| 7     | OSC2/CLKO/RPA3/PMA0/RA3                    | 21    | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 8     | SOSCI/RPB4/RB4                             | 22    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 9     | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4             | 23    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 10    | Vdd                                        | 24    | AVss                                             |

| 11    | TMS/RPB5/USBID/RB5                         | 25    | AVDD                                             |

| 12    | VBUS                                       | 26    | MCLR                                             |

| 13    | TDI/RPB7/CTED3/PMD5/INT0/RB7               | 27    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 14    | TCK/RPB8/SCL1/CTED10/PMD4/RB8              | 28    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: Shaded pins are 5V tolerant.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 31:24        | DCRCDATA<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 00.10        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23:16        | DCRCDATA<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 15:8         | DCRCDATA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | DCRCDA            | TA<7:0>           |                   |                  |                  |  |  |  |  |  |  |

#### REGISTER 9-5: DCRCDATA: DMA CRC DATA REGISTER

### Legend:

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (i.e., current IP header checksum value).

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

#### REGISTER 9-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 31:24        | DCRCXOR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23:16        | DCRCXOR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 15:8         | DCRCXOR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | DCRCXO            | R<7:0>            |                   |                  |                  |  |  |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): This register is unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = Enable the XOR input to the Shift register

- 0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit Bit<br>4/6 29/21/13/5 28/20/12/4 |                      | Bit Bit<br>27/19/11/3 26/18/10/2 |            | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|--------------------------------------|----------------------|----------------------------------|------------|------------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0                                  | U-0                  | U-0                              | U-0        | U-0                    | U-0              |  |  |  |

| 31.24        | —                 | -                 | —                                    | -                    | —                                | —          | _                      | -                |  |  |  |

| 23:16        | U-0 U-0           |                   | U-0 U-0                              |                      | U-0 U-0                          |            | U-0                    | U-0              |  |  |  |

| 23.10        | —                 | —                 | —                                    | —                    | —                                | —          | —                      | —                |  |  |  |

| 15:8         | U-0               | U-0               | U-0 U-0                              |                      | U-0 U-0                          |            | U-0                    | U-0              |  |  |  |

| 15.0         | —                 | -                 | —                                    | -                    | —                                | —          | —                      | -                |  |  |  |

|              | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS                           | R/WC-0, HS           | R/WC-0, HS                       | R/WC-0, HS | R/WC-0, HS             | R/WC-0, HS       |  |  |  |

| 7:0          | BTSEF             | BTSEF BMXEF       |                                      | BTOEF <sup>(2)</sup> | DFN8EF                           | CRC16EF    | CRC5EF <sup>(4)</sup>  |                  |  |  |  |

|              | DISEF             | DIVIALE           | DMAEF <sup>(1)</sup>                 | BIOLE                | DINOLF                           | GIVE IDEF  | EOFEF <sup>(3,5)</sup> | PIDEF            |  |  |  |

#### REGISTER 10-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable b           | pit                |  |  |

|-------------------|-------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared               | x = Bit is unknown |  |  |

- bit 31-8 Unimplemented: Read as '0'

- bit 7 BTSEF: Bit Stuff Error Flag bit

- 1 = Packet rejected due to bit stuff error

- 0 = Packet accepted

- bit 6 BMXEF: Bus Matrix Error Flag bit

- 1 = The base address, of the Buffer Descriptor Table, or the address of an individual buffer pointed to by a Buffer Descriptor Table entry, is invalid.

- 0 = No address error

- bit 5 DMAEF: DMA Error Flag bit<sup>(1)</sup>

- 1 = USB DMA error condition detected

- 0 = No DMA error

- bit 4 BTOEF: Bus Turnaround Time-Out Error Flag bit<sup>(2)</sup>

- 1 = Bus turnaround time-out has occurred

- 0 = No bus turnaround time-out

- bit 3 **DFN8EF:** Data Field Size Error Flag bit

- 1 = Data field received is not an integral number of bytes

- 0 = Data field received is an integral number of bytes

- bit 2 CRC16EF: CRC16 Failure Flag bit

- 1 = Data packet rejected due to CRC16 error

- 0 = Data packet accepted

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- **2:** This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                              | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------------------|------------------|

| 31:24        | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0               | U-0                                           | U-0              |

|              |                   | _                 | —                 | —                 | _                 | —                 | _                                             | _                |

| 00:16        | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0               | U-0                                           | U-0              |

| 23:16        |                   | _                 | —                 | —                 |                   |                   | _                                             |                  |

| 15:0         | U-0                                           | U-0              |

| 15:8         |                   | —                 | —                 | —                 | —                 | -                 | —                                             | —                |

|              | R/W-0                                         | R/W-0            |

| 7:0          | BTSEE             | BMXEE             | DMAEE             | BTOEE             | DFN8EE            | CRC16EE           | CRC5EE <sup>(1)</sup><br>EOFEE <sup>(2)</sup> | PIDEE            |

#### REGISTER 10-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

#### Legend:

| 0                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

|       | •                                                         |

|-------|-----------------------------------------------------------|

| bit 7 | BTSEE: Bit Stuff Error Interrupt Enable bit               |

|       | 1 = BTSEF interrupt is enabled                            |

|       | 0 = BTSEF interrupt is disabled                           |

| bit 6 | BMXEE: Bus Matrix Error Interrupt Enable bit              |

|       | 1 = BMXEF interrupt is enabled                            |

|       | 0 = BMXEF interrupt is disabled                           |

| bit 5 | DMAEE: DMA Error Interrupt Enable bit                     |

|       | 1 = DMAEF interrupt is enabled                            |

|       | 0 = DMAEF interrupt is disabled                           |

| bit 4 | BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit |

|       | 1 = BTOEF interrupt is enabled                            |

|       | 0 = BTOEF interrupt is disabled                           |

| bit 3 | DFN8EE: Data Field Size Error Interrupt Enable bit        |

|       | 1 = DFN8EF interrupt is enabled                           |

|       | 0 = DFN8EF interrupt is disabled                          |

- bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

- 1 = CRC16EF interrupt is enabled

- 0 = CRC16EF interrupt is disabled

- bit 1 CRC5EE: CRC5 Host Error Interrupt Enable bit<sup>(1)</sup>

- 1 = CRC5EF interrupt is enabled

- 0 = CRC5EF interrupt is disabled

- EOFEE: EOF Error Interrupt Enable bit<sup>(2)</sup>

- 1 = EOF interrupt is enabled

- 0 = EOF interrupt is disabled

- bit 0 PIDEE: PID Check Failure Interrupt Enable bit

- 1 = PIDEF interrupt is enabled

- 0 = PIDEF interrupt is disabled

- Note 1: Device mode.

- 2: Host mode.

Note: For an interrupt to propagate the USBIF register, the UERRIE (U1IE<1>) bit must be set.

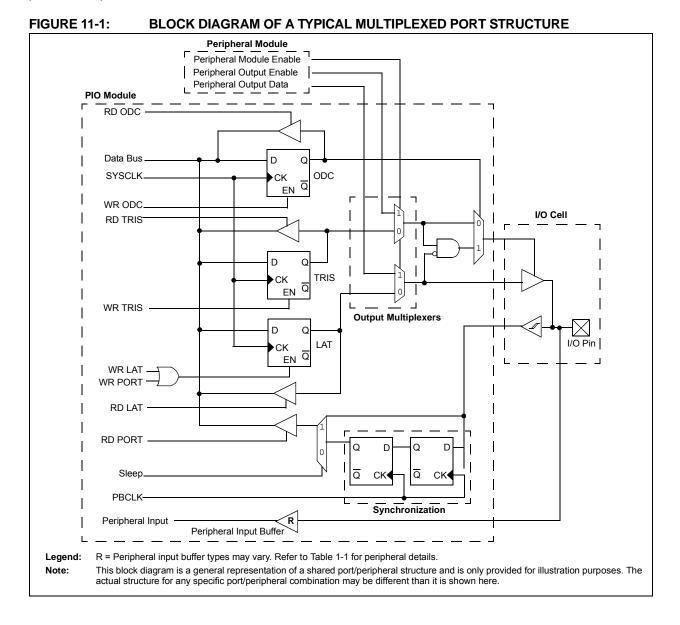

#### 11.0 I/O PORTS

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS60001120), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

General purpose I/O pins are the simplest of peripherals. They allow the PIC<sup>®</sup> MCU to monitor and control other devices. To add flexibility and functionality, some pins are multiplexed with alternate functions. These functions depend on which peripheral features are on the device. In general, when a peripheral is functioning, that pin may not be used as a general purpose I/O pin.

Key features of this module include:

- · Individual output pin open-drain enable/disable

- · Individual input pin weak pull-up and pull-down

- Monitor selective inputs and generate interrupt when change in pin state is detected

- · Operation during Sleep and Idle modes

- Fast bit manipulation using CLR, SET, and INV registers

Figure 11-1 illustrates a block diagram of a typical multiplexed I/O port.

#### TABLE 11-4: PORTB REGISTER MAP

| ess                                             |           |        |               |               |                       |                              |               |               |              | Bits         |              |                             |              |              |              |              |              |              |      |

|-------------------------------------------------|-----------|--------|---------------|---------------|-----------------------|------------------------------|---------------|---------------|--------------|--------------|--------------|-----------------------------|--------------|--------------|--------------|--------------|--------------|--------------|------|

| Virtual Address<br>(BF88_#)<br>Register<br>Name | Bit Range | 31/15  | 30/14         | 29/13         | 28/12                 | 27/11                        | 26/10         | 25/9          | 24/8         | 23/7         | 22/6         | 21/5                        | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All Resets   |      |

|                                                 |           | 31:16  | _             |               | —                     |                              | _             | —             | —            | —            | _            | —                           | _            |              | —            | _            | —            | —            | 0000 |

| 6100 ANSELB                                     | 15:0      | ANSB15 | ANSB14        | ANSB13        | ANSB12 <sup>(2)</sup> | —                            | —             | —             | —            | _            | _            | _                           | _            | ANSB3        | ANSB2        | ANSB1        | ANSB0        | EOOF         |      |

| 6110                                            | TRISB     | 31:16  | -             | _             | _                     | 1                            | _             | —             | —            | —            | -            | —                           | -            | -            | —            | -            | _            | _            | 0000 |

| 0110                                            | IIKIOD    | 15:0   | TRISB15       | TRISB14       | TRISB13               | TRISB12 <sup>(2)</sup>       | TRISB11       | TRISB10       | TRISB9       | TRISB8       | TRISB7       | TRISB6 <sup>(2)</sup>       | TRISB5       | TRISB4       | TRISB3       | TRISB2       | TRISB1       | TRISB0       | FFFF |

| 6120                                            | PORTB     | 31:16  | _             | _             | _                     |                              | _             | _             | _            | _            |              | _                           | -            |              |              |              |              |              | 0000 |

| 0120                                            | FORTB     | 15:0   | RB15          | RB14          | RB13                  | RB12 <sup>(2)</sup>          | RB11          | RB10          | RB9          | RB8          | RB7          | RC6 <sup>(2)</sup>          | RB5          | RB4          | RB3          | RB2          | RB1          | RB0          | xxxx |

| 6130                                            | LATB      | 31:16  | -             | _             | _                     |                              | -             | _             | _            | _            |              | _                           |              |              | _            |              | _            | _            | 0000 |

| 0150                                            | LAID      | 15:0   | LATB15        | LATB14        | LATB13                | LATB12 <sup>(2)</sup>        | LATB11        | LATB10        | LATB9        | LATB8        | LATB7        | LATB6 <sup>(2)</sup>        | LATB5        | LATB4        | LATB3        | LATB2        | LATB1        | LATB0        | xxxx |

| C1 4 0                                          | 0000      | 31:16  |               | _             | _                     | —                            | _             | _             | _            | —            | _            | _                           |              | —            | _            | —            | _            | —            | 0000 |

| 6140                                            | ODCB      | 15:0   | ODCB15        | ODCB14        | ODCB13                | ODCB12 <sup>(2)</sup>        | ODCB11        | ODCB10        | ODCB9        | ODCB8        | ODCB7        | ODCB6                       | ODCB5        | ODCB4        | ODCB3        | ODCB2        | ODCB1        | ODCB0        | 0000 |

| 6150                                            |           | 31:16  | -             | —             | —                     | -                            | _             | _             | _            | —            | -            | _                           | _            | _            | _            | -            | _            | —            | 0000 |

| 6150                                            | CNPUB     | 15:0   | CNPUB15       | CNPUB14       | CNPUB13               | CNPUB12 <sup>(2)</sup>       | CNPUB11       | CNPUB10       | CNPUB9       | CNPUB8       | CNPUB7       | CNPUB6 <sup>(2)</sup>       | CNPUB5       | CNPUB4       | CNPUB3       | CNPUB2       | CNPUB1       | CNPUB0       | 0000 |

| 6160                                            | CNPDB     | 31:16  | -             | _             | _                     |                              | -             | _             | _            | _            |              | _                           |              |              | _            |              | _            | _            | 0000 |

| 0100                                            | CNPDB     | 15:0   | CNPDB15       | CNPDB14       | CNPDB13               | CNPDB12 <sup>(2)</sup>       | CNPDB11       | CNPDB10       | CNPDB9       | CNPDB8       | CNPDB7       | CNPDB6 <sup>(2)</sup>       | CNPDB5       | CNPDB4       | CNPDB3       | CNPDB2       | CNPDB1       | CNPDB0       | 0000 |

| 6170                                            | CNCONB    | 31:16  | -             | _             | _                     |                              | -             | _             | _            | _            |              | _                           |              |              | _            |              | _            | _            | 0000 |

| 0170                                            | CINCOINE  | 15:0   | ON            | _             | SIDL                  |                              | -             | _             | _            | _            |              | _                           |              |              | _            |              | _            | _            | 0000 |

| C400                                            |           | 31:16  |               | —             | —                     | -                            | —             | —             | —            | _            |              | —                           | Ι            | -            | —            | -            | —            | _            | 0000 |

| 6180                                            | CNENB     | 15:0   | CNIEB15       | CNIEB14       | CNIEB13               | CNIEB11 <sup>(2)</sup>       | CNIEB11       | CNIEB10       | CNIEB9       | CNIEB8       | CNIEB7       | CNIEB6(2)                   | CNIEB5       | CNIEB4       | CNIEB3       | CNIEB2       | CNIEB1       | CNIEB0       | 0000 |

|                                                 |           | 31:16  | —             |               | —                     |                              | _             | —             | —            | —            | _            | —                           | _            | _            | —            | _            | _            | —            | 0000 |

| 6190                                            | CNSTATB   | 15:0   | CN<br>STATB15 | CN<br>STATB14 | CN<br>STATB13         | CN<br>STATB12 <sup>(2)</sup> | CN<br>STATB11 | CN<br>STATB10 | CN<br>STATB9 | CN<br>STATB8 | CN<br>STATB7 | CN<br>STATB6 <sup>(2)</sup> | CN<br>STATB5 | CN<br>STATB4 | CN<br>STATB3 | CN<br>STATB2 | CN<br>STATB1 | CN<br>STATB0 | 0000 |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This bit is not available on PIC32MX2XX devices. The reset value for the TRISB register when this bit is not available is 0x0000EFBF.

| TABL                        | .E 11-6:         | PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED) |       |       |       |       |       |       |      |      |      |      |      |      |      |       |          |      |            |

|-----------------------------|------------------|------------------------------------------------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|----------|------|------------|

| sse                         |                  |                                                      |       |       |       |       |       |       |      | В    | its  |      |      |      |      |       |          |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range                                            | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1     | 16/0 | All Resets |

| 5454                        |                  | 31:16                                                | _     | —     | —     | —     | —     | —     | -    | —    | —    | —    | -    | -    | -    | -     | —        | —    | 0000       |

| FA54                        | U1CTSR           | 15:0                                                 | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U1CTS | R<3:0>   |      | 0000       |

| 5450                        |                  | 31:16                                                | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _        | _    | 0000       |

| FA58                        | U2RXR            | 15:0                                                 | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U2RXI | R<3:0>   |      | 0000       |

| FAFO                        |                  | 31:16                                                | _     | —     | —     |       | _     | _     | —    | _    |      | —    | -    | —    | —    | —     |          |      | 0000       |

| FA5C                        | U2CTSR           | 15:0                                                 | —     | —     | —     |       | —     | —     | —    | _    |      | —    |      | —    |      | U2CTS | R<3:0>   |      | 0000       |

| FA84                        | SDI1R            | 31:16                                                | —     | _     | —     |       | _     | —     | —    | _    |      | _    |      | _    | _    | _     |          |      | 0000       |

| FA04                        | SDIR             | 15:0                                                 | —     | _     | —     |       | _     | —     | —    | _    |      | _    |      | _    |      | SDI1F | R<3:0>   |      | 0000       |

| FA88                        | SS1R             | 31:16                                                | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —        | -    | 0000       |

| FA00                        | 331K             | 15:0                                                 | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | SS1R  | <3:0>    |      | 0000       |

| FA90                        | SDI2R            | 31:16                                                | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —        | -    | 0000       |

| FA90                        | SDIZK            | 15:0                                                 | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | SDI2F | R<3:0>   |      | 0000       |

| FA94                        | SS2R             | 31:16                                                | _     | —     | —     | _     | —     | —     | —    | —    | _    | —    | -    | _    | —    | —     | —        | —    | 0000       |

| 1 A94                       | 332R             | 15:0                                                 | _     | —     | —     | _     | —     | —     | —    | —    | _    | —    | -    | _    |      | SS2R  | <3:0>    |      | 0000       |

| EVBS                        | REFCLKIR         | 31:16                                                | _     | —     | —     | _     | —     | —     | —    | —    | _    | —    | -    | _    | —    | —     | —        | —    | 0000       |

| I ADO                       |                  | 15:0                                                 | —     | —     | -     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | REFCL | (IR<3:0> |      | 0000       |

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

|              |                   |                   |                   |                   |                   |                   |                  | ., _, _,         |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04-04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | _                 |                   |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | -                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 | SIDL              | _                 | _                 |                   |                  | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          |                   | _                 |                   |                   |                   |                   | _                | _                |

#### **REGISTER 11-3:** CNCONX: CHANGE NOTICE CONTROL FOR PORTX REGISTER (X = A, B, C)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Change Notice (CN) Control ON bit

- 1 = CN is enabled

- 0 = CN is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Control bit

- 1 = Idle mode halts CN operation

- 0 = Idle does not affect CN operation

- bit 12-0 Unimplemented: Read as '0'

#### REGISTER 17-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)

- bit 5 **MSTEN:** Master Mode Enable bit

- 1 = Master mode

- 0 = Slave mode

- bit 4 DISSDI: Disable SDI bit

- 1 = SDI pin is not used by the SPI module (pin is controlled by PORT function)

- 0 = SDI pin is controlled by the SPI module

- bit 3-2 STXISEL<1:0>: SPI Transmit Buffer Empty Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)

- 10 = Interrupt is generated when the buffer is empty by one-half or more

- 01 = Interrupt is generated when the buffer is completely empty

- 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are complete

- bit 1-0 SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is full

- 10 = Interrupt is generated when the buffer is full by one-half or more

- 01 = Interrupt is generated when the buffer is not empty

- 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit can only be written when the ON bit = 0.

- 3: This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- 4: When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

#### 20.1 PMP Control Registers

#### TABLE 20-1: PARALLEL MASTER PORT REGISTER MAP

| ess                         |                                 | 6             |       | Bits          |                                                                                  |       |         |        |        |        |         |       |           |      |      |      |      |      |            |

|-----------------------------|---------------------------------|---------------|-------|---------------|----------------------------------------------------------------------------------|-------|---------|--------|--------|--------|---------|-------|-----------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14         | 29/13                                                                            | 28/12 | 27/11   | 26/10  | 25/9   | 24/8   | 23/7    | 22/6  | 21/5      | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 7000                        | PMCON                           | 31:16         | —     | _             |                                                                                  | _     | —       | —      | —      | —      | _       | —     | —         | -    |      | —    | _    | _    | 0000       |

| 7000                        | FINCON                          | 15:0          | ON    | _             | SIDL                                                                             | ADRML | IX<1:0> | PMPTTL | PTWREN | PTRDEN | CSF∢    | <1:0> | ALP       | _    | CS1P | —    | WRSP | RDSP | 0000       |

| 7010                        | PMMODE                          | 31:16         | _     | _             |                                                                                  | _     | _       | _      | _      | _      | _       | _     | _         |      |      | _    | _    |      | 0000       |

| 7010                        | FININODL                        | 15:0          | BUSY  | IRQM          | IRQM<1:0> INCM<1:0> — MODE<1:0> WAITB<1:0> WAITB<1:0> WAITM<3:0> WAITE<1:0> 0000 |       |         |        |        |        |         |       |           |      |      |      |      |      |            |

|                             |                                 | 31:16         | _     | _             |                                                                                  | _     | _       | _      | _      | _      | _       | _     | _         |      |      | _    | _    |      | 0000       |

| 7020                        | PMADDR                          | 15:0          | _     | CS1<br>ADDR14 | _                                                                                | _     | _       |        |        |        |         | ŀ     | ADDR<10:0 | >    |      |      |      |      | 0000       |

| 7030                        | PMDOUT                          | 31:16<br>15:0 |       |               |                                                                                  |       |         |        |        | DATAOU | T<31:0> |       |           |      |      |      |      |      | 0000       |

| 7040                        | PMDIN                           | 31:16<br>15:0 |       | DATAIN<31:0>  |                                                                                  |       |         |        |        |        |         |       |           |      |      |      |      |      |            |

| 7050                        |                                 | 31:16         | _     | _             |                                                                                  | _     | —       | —      | _      | _      | _       | —     | _         | -    | -    | _    | _    | _    | 0000       |

| 7050                        | PMAEN                           | 15:0          | —     | PTEN14        | PTEN14 0000                                                                      |       |         |        |        |        |         |       |           |      |      |      |      |      |            |

| 7060                        | PMSTAT                          | 31:16         |       | —             |                                                                                  |       | —       | —      | —      | —      | _       | —     | —         | —    | _    | _    | _    |      | 0000       |

| 1000                        | FINISTAT                        | 15:0          | IBF   | IBOV          | _                                                                                | _     | IB3F    | IB2F   | IB1F   | IB0F   | OBE     | OBUF  | —         | _    | OB3E | OB2E | OB1E | OB0E | 008F       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| <b>NEGISTE</b>                                                             | -1\ 21-4. 1\      | ICDAIL. R         | IC DAIL W         |                   |                   |                   |                  |                  |  |  |  |

|----------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range                                                               | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 04.04                                                                      | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24                                                                      |                   | YEAR1             | 0<3:0>            |                   | YEAR01<3:0>       |                   |                  |                  |  |  |  |

| 23:16 U-0 U-0 U-0 R/W-x R/W-x R/W-x R/W-x R/W-x                            |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 23:16                                                                      |                   | —                 | _                 | MONTH10           |                   | MONTH             | 01<3:0>          |                  |  |  |  |

| 45.0                                                                       | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8                                                                       |                   |                   | DAY10             | )<1:0>            | DAY01<3:0>        |                   |                  |                  |  |  |  |

| 7.0                                                                        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0                                                                        | —                 | —                 | —                 | _                 | —                 | WDAY01<2:0>       |                  |                  |  |  |  |

|                                                                            |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:                                                                    | ∟egend:           |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| R = Read                                                                   | able bit          |                   | W = Writable      | e bit             | U = Unimple       | emented bit, re   | ead as '0'       |                  |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 21-4: RTCDATE: RTC DATE VALUE REGISTER

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10s place digit; contains a value from 0 to 9

bit 27-24 **YEAR01<3:0>:** Binary-Coded Decimal Value of Years bits, 1s place digit; contains a value from 0 to 9 bit 23-21 **Unimplemented:** Read as '0'

bit 20 **MONTH10:** Binary-Coded Decimal Value of Months bits, 10s place digit; contains a value of 0 or 1

bit 19-16 **MONTH01<3:0>:** Binary-Coded Decimal Value of Months bits, 1s place digit; contains a value from 0 to 9 bit 15-14 **Unimplemented:** Read as '0'

bit 13-12 DAY10<1:0>: Binary-Coded Decimal Value of Days bits, 10s place digit; contains a value of 0 to 3

bit 11-8 DAY01<3:0>: Binary-Coded Decimal Value of Days bits, 1s place digit; contains a value from 0 to 9

bit 7-3 **Unimplemented:** Read as '0'

bit 2-0 WDAY01<2:0>: Binary-Coded Decimal Value of Weekdays bits; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### 25.1 CTMU Control Registers

#### TABLE 25-1: CTMU REGISTER MAP

| ess                        |                                 | 6         |         |         |          |       |          |          |          | Bits     |         |         |        |       |          |      |      |       | ú          |

|----------------------------|---------------------------------|-----------|---------|---------|----------|-------|----------|----------|----------|----------|---------|---------|--------|-------|----------|------|------|-------|------------|

| Virtual Addres<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13    | 28/12 | 27/11    | 26/10    | 25/9     | 24/8     | 23/7    | 22/6    | 21/5   | 20/4  | 19/3     | 18/2 | 17/1 | 16/0  | All Reset: |

| 1000                       | CTMUCON                         | 31:16     | EDG1MOD | EDG1POL |          | EDG1S | SEL<3:0> |          | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL |        | EDG2S | SEL<3:0> |      | —    | -     | 0000       |

| A200                       | CINUCON                         | 15:0      | ON      | _       | CTMUSIDL | TGEN  | EDGEN    | EDGSEQEN | IDISSEN  | CTTRIG   |         |         | ITRIM< | <5:0> |          |      | IRNG | <1:0> | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### 29.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 29.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 29.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 29.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

#### 29.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

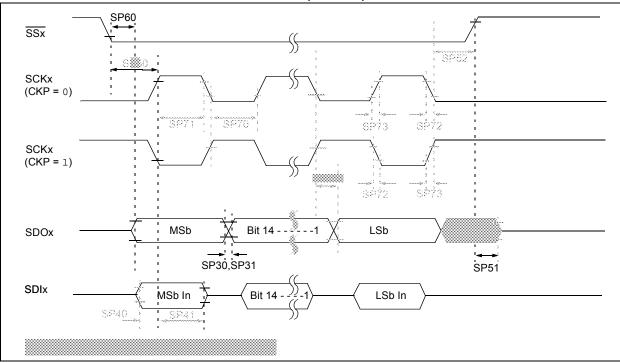

#### FIGURE 30-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

#### TABLE 30-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        | RACTERIS              | TICS                                                                      | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                        |      |       |                    |  |  |  |  |

|---------------|-----------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|--|--|--|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                                            | Min.                                                                                                                                                                                                      | Typical <sup>(2)</sup> | Max. | Units | Conditions         |  |  |  |  |

| SP70          | TscL                  | SCKx Input Low Time (Note 3)                                              | Tsck/2                                                                                                                                                                                                    | _                      | _    | ns    | —                  |  |  |  |  |

| SP71          | TscH                  | SCKx Input High Time (Note 3)                                             | Tsck/2                                                                                                                                                                                                    | —                      | _    | ns    | —                  |  |  |  |  |

| SP72          | TscF                  | SCKx Input Fall Time                                                      | _                                                                                                                                                                                                         | 5                      | 10   | ns    | —                  |  |  |  |  |

| SP73          | TscR                  | SCKx Input Rise Time                                                      | —                                                                                                                                                                                                         | 5                      | 10   | ns    | —                  |  |  |  |  |

| SP30          | TDOF                  | SDOx Data Output Fall Time (Note 4)                                       | —                                                                                                                                                                                                         | —                      | _    | ns    | See parameter DO32 |  |  |  |  |

| SP31          | TDOR                  | SDOx Data Output Rise Time (Note 4)                                       | —                                                                                                                                                                                                         | —                      | _    | ns    | See parameter DO31 |  |  |  |  |

| SP35          | TscH2doV,             | SDOx Data Output Valid after                                              |                                                                                                                                                                                                           | _                      | 20   | ns    | VDD > 2.7V         |  |  |  |  |

|               | TscL2DoV              | SCKx Edge                                                                 | _                                                                                                                                                                                                         | —                      | 30   | ns    | VDD < 2.7V         |  |  |  |  |

| SP40          | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge                                | 10                                                                                                                                                                                                        | —                      | _    | ns    | —                  |  |  |  |  |

| SP41          | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                 | 10                                                                                                                                                                                                        | —                      |      | ns    | —                  |  |  |  |  |

| SP50          | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ Input | 175                                                                                                                                                                                                       | —                      |      | ns    | _                  |  |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 50 ns.

- **4:** Assumes 50 pF load on all SPIx pins.

#### TABLE 31-8:SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| АС СНА        | ARACTERIS | TICS                                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature } -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |      |      |       |            |  |  |  |  |

|---------------|-----------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|--|--|--|--|

| Param.<br>No. | Symbol    | Characteristics                                        | Min.                                                                                                                                                                                                                                                                           | Тур. | Max. | Units | Conditions |  |  |  |  |

| MSP70         | TscL      | SCKx Input Low Time (Note 1,2)                         | Tsck/2                                                                                                                                                                                                                                                                         |      | _    | ns    | _          |  |  |  |  |

| MSP71         | TscH      | SCKx Input High Time (Note 1,2)                        | Tsck/2                                                                                                                                                                                                                                                                         | —    |      | ns    | —          |  |  |  |  |

| MSP51         | TssH2doZ  | SSx ↑ to SDOx Output<br>High-Impedance <b>(Note 2)</b> | 5                                                                                                                                                                                                                                                                              |      | 25   | ns    | —          |  |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns.

#### TABLE 31-9: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        | RACTERIS | TICS                            | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |         |      |       |            |  |  |  |

|---------------|----------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|--|--|

| Param.<br>No. | Symbol   | Characteristics                 | Min.                                                                                                                                                 | Typical | Max. | Units | Conditions |  |  |  |

| SP70          | TscL     | SCKx Input Low Time (Note 1,2)  | Tsck/2                                                                                                                                               |         |      | ns    |            |  |  |  |

| SP71          | TscH     | SCKx Input High Time (Note 1,2) | Tsck/2                                                                                                                                               | _       | _    | ns    | —          |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns.

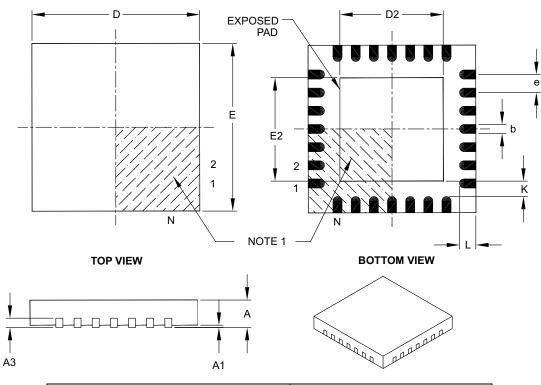

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units       | MILLIMETERS |          |      |  |  |

|------------------------|-------------|-------------|----------|------|--|--|

| Dimens                 | sion Limits | MIN         | NOM      | MAX  |  |  |

| Number of Pins         | Ν           |             | 28       |      |  |  |

| Pitch                  | е           |             | 0.65 BSC |      |  |  |

| Overall Height         | Α           | 0.80        | 0.90     | 1.00 |  |  |

| Standoff               | A1          | 0.00        | 0.02     | 0.05 |  |  |

| Contact Thickness      | A3          |             | 0.20 REF |      |  |  |

| Overall Width          | Е           |             | 6.00 BSC |      |  |  |

| Exposed Pad Width      | E2          | 3.65        | 3.70     | 4.20 |  |  |

| Overall Length         | D           |             | 6.00 BSC |      |  |  |

| Exposed Pad Length     | D2          | 3.65        | 3.70     | 4.20 |  |  |

| Contact Width          | b           | 0.23        | 0.30     | 0.35 |  |  |

| Contact Length         | L           | 0.50        | 0.55     | 0.70 |  |  |

| Contact-to-Exposed Pad | К           | 0.20        | -        | -    |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

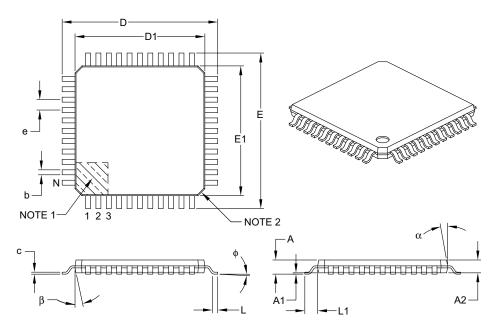

#### 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units        | MILLIMETERS |           |      |  |  |  |

|--------------------------|--------------|-------------|-----------|------|--|--|--|

| Dime                     | nsion Limits | MIN         | NOM       | MAX  |  |  |  |

| Number of Leads          | N            |             | 44        |      |  |  |  |

| Lead Pitch               | е            |             | 0.80 BSC  |      |  |  |  |

| Overall Height           | А            | _           | -         | 1.20 |  |  |  |

| Molded Package Thickness | A2           | 0.95        | 1.00      | 1.05 |  |  |  |

| Standoff                 | A1           | 0.05        | -         | 0.15 |  |  |  |

| Foot Length              | L            | 0.45        | 0.60      | 0.75 |  |  |  |

| Footprint                | L1           |             | 1.00 REF  |      |  |  |  |

| Foot Angle               | φ            | 0°          | 3.5°      | 7°   |  |  |  |

| Overall Width            | E            |             | 12.00 BSC |      |  |  |  |

| Overall Length           | D            |             | 12.00 BSC |      |  |  |  |

| Molded Package Width     | E1           |             | 10.00 BSC |      |  |  |  |

| Molded Package Length    | D1           |             | 10.00 BSC |      |  |  |  |

| Lead Thickness           | С            | 0.09        | -         | 0.20 |  |  |  |

| Lead Width               | b            | 0.30        | 0.37      | 0.45 |  |  |  |

| Mold Draft Angle Top     | α            | 11°         | 12°       | 13°  |  |  |  |

| Mold Draft Angle Bottom  | β            | 11°         | 12°       | 13°  |  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

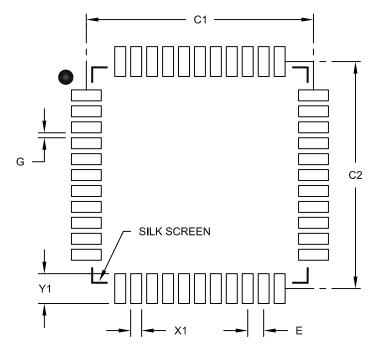

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                          | Units  |      |          |      |  |

|--------------------------|--------|------|----------|------|--|

| Dimension                | Limits | MIN  | NOM      | MAX  |  |

| Contact Pitch            | E      |      | 0.80 BSC |      |  |

| Contact Pad Spacing      | C1     |      | 11.40    |      |  |

| Contact Pad Spacing      | C2     |      | 11.40    |      |  |

| Contact Pad Width (X44)  | X1     |      |          | 0.55 |  |

| Contact Pad Length (X44) | Y1     |      |          | 1.50 |  |

| Distance Between Pads    | G      | 0.25 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2011-2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN:978-1-5224-0471-2