#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 33                                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx210f016d-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to documents listed in the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

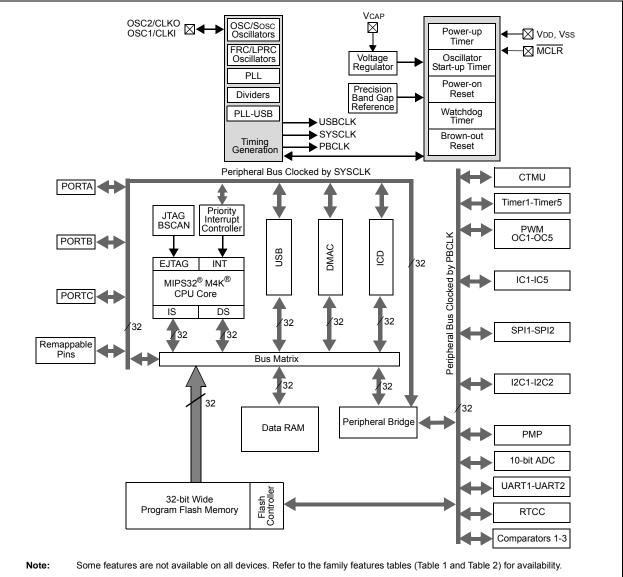

**BLOCK DIAGRAM**

This document contains device-specific information for PIC32MX1XX/2XX 28/36/44-pin Family devices.

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX1XX/2XX 28/36/44-pin Family of devices.

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

FIGURE 1-1:

|          |                        | Pin Nu                            | mber <sup>(1)</sup> | -                               |             |                |                                           |

|----------|------------------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------|-------------------------------------------|

| Pin Name | 28-pin<br>QFN          | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                               |

| OC1      | PPS                    | PPS                               | PPS                 | PPS                             | 0           |                | Output Compare Output 1                   |

| OC2      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 2                   |

| OC3      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | —              | Output Compare Output 3                   |

| OC4      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 4                   |

| OC5      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 5                   |

| OCFA     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | Output Compare Fault A Input              |

| OCFB     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | Output Compare Fault B Input              |

| INT0     | 13                     | 16                                | 17                  | 43                              | I           | ST             | External Interrupt 0                      |

| INT1     | PPS                    | PPS                               | PPS                 | PPS                             | 1           | ST             | External Interrupt 1                      |

| INT2     | PPS                    | PPS                               | PPS                 | PPS                             | 1           | ST             | External Interrupt 2                      |

| INT3     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | External Interrupt 3                      |

| INT4     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | External Interrupt 4                      |

| RA0      | 27                     | 2                                 | 33                  | 19                              | I/O         | ST             | PORTA is a bidirectional I/O port         |

| RA1      | 28                     | 3                                 | 34                  | 20                              | I/O         | ST             | -                                         |

| RA2      | 6                      | 9                                 | 7                   | 30                              | I/O         | ST             | -                                         |

| RA3      | 7                      | 10                                | 8                   | 31                              | I/O         | ST             | -                                         |

| RA4      | 9                      | 12                                | 10                  | 34                              | I/O         | ST             | -                                         |

| RA7      | _                      |                                   |                     | 13                              | I/O         | ST             | -                                         |

| RA8      |                        |                                   |                     | 32                              | I/O         | ST             | -                                         |

| RA9      | <u> </u>               |                                   | _                   | 35                              | I/O         | ST             | -                                         |

| RA10     |                        |                                   |                     | 12                              | I/O         | ST             | -                                         |

| RB0      | 1                      | 4                                 | 35                  | 21                              | I/O         | ST             | PORTB is a bidirectional I/O port         |

| RB1      | 2                      | 5                                 | 36                  | 22                              | I/O         | ST             |                                           |

| RB2      | 3                      | 6                                 | 1                   | 23                              | I/O         | ST             | -                                         |

| RB3      | 4                      | 7                                 | 2                   | 24                              | I/O         | ST             | -                                         |

| RB4      | 8                      | 11                                | 9                   | 33                              | I/O         | ST             | -                                         |

| RB5      | 11                     | 14                                | 15                  | 41                              | I/O         | ST             | -                                         |

| RB6      | 12 <sup>(2)</sup>      | 15 <sup>(2)</sup>                 | 16 <sup>(2)</sup>   | 42(2)                           | I/O         | ST             | 1                                         |

| RB7      | 13                     | 16                                | 17                  | 43                              | I/O         | ST             | 4                                         |

| RB8      | 18                     | 10                                | 18                  | 44                              | I/O         | ST             | 4                                         |

| RB9      | 15                     | 18                                | 19                  | 1                               | I/O         | ST             | 4                                         |

| RB10     | 18                     | 21                                | 24                  | 8                               | I/O         | ST             | 4                                         |

| RB11     | 10                     | 22                                | 25                  | 9                               | I/O         | ST             | 4                                         |

| RB12     | 20(2)                  | 23(2)                             | 26 <sup>(2)</sup>   | 10 <sup>(2)</sup>               | I/O         | ST             | 4                                         |

| RB13     | 21                     | 24                                | 27                  | 11                              | I/O         | ST             | 4                                         |

| RB14     | 21                     | 25                                | 28                  | 14                              | I/O         | ST             | 4                                         |

| RB15     | 23                     | 26                                | 29                  | 15                              | 1/O         | ST             | 4                                         |

|          | CMOS = C               | -                                 |                     |                                 |             |                | Analog input P = Power                    |

| Leyena.  | ST = Schm<br>TTL = TTL | itt Trigger in                    |                     |                                 |             | O = Outp       |                                           |

| Note 1:  |                        | -                                 | led for refe        | rence onlv.                     | See the     |                | grams" section for device pin availabilit |

#### DINOUT I/O DESCRIPTIONS (CONTINUED)

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

|                 |                             | OUT I/O D<br>Pin Nui                        |                                       |                                 |             | Í                    |                                                                                                 |

|-----------------|-----------------------------|---------------------------------------------|---------------------------------------|---------------------------------|-------------|----------------------|-------------------------------------------------------------------------------------------------|

| Pin Name        | 28-pin<br>QFN               | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC           | 36-pin<br>VTLA                        | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type       | Description                                                                                     |

| PMA0            | 7                           | 10                                          | 8                                     | 3                               | I/O         | TTL/ST               | Parallel Master Port Address bit 0 input<br>(Buffered Slave modes) and output<br>(Master modes) |

| PMA1            | 9                           | 12                                          | 10                                    | 2                               | I/O         | TTL/ST               | Parallel Master Port Address bit 1 input<br>(Buffered Slave modes) and output<br>(Master modes) |

| PMA2            |                             | _                                           |                                       | 27                              | 0           | —                    | Parallel Master Port address                                                                    |

| PMA3            |                             | _                                           | _                                     | 38                              | 0           | _                    | (Demultiplexed Master modes)                                                                    |

| PMA4            |                             | _                                           | _                                     | 37                              | 0           | _                    | 7                                                                                               |

| PMA5            |                             | _                                           | _                                     | 4                               | 0           | _                    |                                                                                                 |

| PMA6            |                             | _                                           | _                                     | 5                               | 0           | _                    | -                                                                                               |

| PMA7            |                             | _                                           | _                                     | 13                              | 0           | _                    | -                                                                                               |

| PMA8            |                             | _                                           | _                                     | 32                              | 0           | _                    | -                                                                                               |

| PMA9            |                             | _                                           | _                                     | 35                              | 0           | _                    | -                                                                                               |

| PMA10           |                             |                                             | _                                     | 12                              | 0           |                      | -                                                                                               |

| PMCS1           | 23                          | 26                                          | 29                                    | 15                              | 0           |                      | Parallel Master Port Chip Select 1 strob                                                        |

|                 | 20 <sup>(2)</sup>           | 23 <sup>(2)</sup>                           | 26 <sup>(2)</sup>                     | 10 <sup>(2)</sup>               | -           |                      | Parallel Master Port data (Demultiplexed                                                        |

| PMD0            | 1 <sup>(3)</sup>            | <br>4 <sup>(3)</sup>                        | 35 <sup>(3)</sup>                     | 21 <sup>(3)</sup>               | I/O         | TTL/ST               | Master mode) or address/data                                                                    |

|                 | 19(2)                       | 22(2)                                       | 25(2)                                 | <u>9</u> (2)                    |             |                      | (Multiplexed Master modes)                                                                      |

| PMD1            | 2(3)                        | 5 <sup>(3)</sup>                            | 36 <sup>(3)</sup>                     | 22 <sup>(3)</sup>               | I/O         | TTL/ST               |                                                                                                 |

|                 | 18(2)                       | 21 <sup>(2)</sup>                           | 24 <sup>(2)</sup>                     | 8 <sup>(2)</sup>                |             |                      | -                                                                                               |

| PMD2            | <u></u>                     | 6 <sup>(3)</sup>                            | 1 <sup>(3)</sup>                      | 23(3)                           | I/O         | TTL/ST               |                                                                                                 |

| PMD3            | 15                          | 18                                          | 19                                    | 1                               | I/O         | TTL/ST               | -                                                                                               |

| PMD4            | 10                          | 10                                          | 18                                    | 44                              | 1/O         | TTL/ST               | -                                                                                               |

| PMD5            | 13                          | 16                                          | 17                                    | 43                              | I/O         | TTL/ST               | -                                                                                               |

| PMD5<br>PMD6    | 13<br>12 <sup>(2)</sup>     | 15 <sup>(2)</sup>                           | 16 <sup>(2)</sup>                     | 43<br>42 <sup>(2)</sup>         | 1/0         | 111/31               | -                                                                                               |

| FIVIDO          | 28(3)                       | 3( <b>3</b> )                               | 34 <b>(3)</b>                         | 20(3)                           | I/O         | TTL/ST               |                                                                                                 |

| PMD7            | <u>11(2)</u>                | 14(2)                                       | 15 <sup>(2)</sup>                     | 41 <sup>(2)</sup>               |             |                      | -                                                                                               |

| PINDI           | 27 <sup>(3)</sup>           | 2 <sup>(3)</sup>                            | 33( <b>3</b> )                        | 19 <sup>(3)</sup>               | I/O         | TTL/ST               |                                                                                                 |

| PMRD            | 2/07                        | 24                                          | 27                                    | 19(1)                           | 0           |                      | Derellel Meeter Pert read stroke                                                                |

| PINIRD          | 21<br>22 <sup>(2)</sup>     | 24<br>25 <sup>(2)</sup>                     | 27<br>28 <sup>(2)</sup>               | 14 <sup>(2)</sup>               | 0           |                      | Parallel Master Port read strobe                                                                |

| PMWR            | <u></u><br>4 <sup>(3)</sup> | 25 <sup>(2)</sup><br>7 <sup>(3)</sup>       | 28 <sup>(-)</sup><br>2 <sup>(3)</sup> | 24 <sup>(3)</sup>               | 0           | —                    | Parallel Master Port write strobe                                                               |

| VBUS            | 12(3)                       | 15 <sup>(3)</sup>                           | 16 <sup>(3)</sup>                     | 42(3)                           |             | Analog               | USB bus power monitor                                                                           |

| VBUS<br>VUSB3V3 | 20(3)                       | 23 <sup>(3)</sup>                           | 26 <sup>(3)</sup>                     | 10 <sup>(3)</sup>               | P           | Analog               | USB internal transceiver supply. This pin                                                       |

| VUSBSVS         | 20.7                        | 23.7                                        | 20.7                                  | 10.7                            | Г           | _                    | must be connected to VDD.                                                                       |

| VBUSON          | 22 <sup>(3)</sup>           | 25 <sup>(3)</sup>                           | 28 <sup>(3)</sup>                     | 14 <sup>(3)</sup>               | 0           | _                    | USB Host and OTG bus power control output                                                       |

| D+              | 18 <sup>(3)</sup>           | 21 <sup>(3)</sup>                           | 24 <sup>(3)</sup>                     | 8 <sup>(3)</sup>                | I/O         | Analog               | USB D+                                                                                          |

| –<br>D-         | 19(3)                       | 22 <sup>(3)</sup>                           | 25 <sup>(3)</sup>                     | 9 <sup>(3)</sup>                | I/O         | Analog               | USB D-                                                                                          |

| Legend: C       | CMOS = CI<br>ST = Schm      | MOS compa<br>itt Trigger in<br>input buffer | atible input                          | or output                       |             | Analog =<br>O = Outp | Analog input P = Power                                                                          |

####

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site:

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- *"MPLAB<sup>®</sup> ICD 3 Design Advisory"* (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

### 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

### 2.7 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

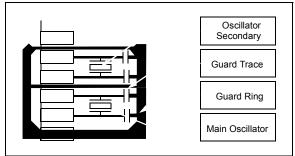

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

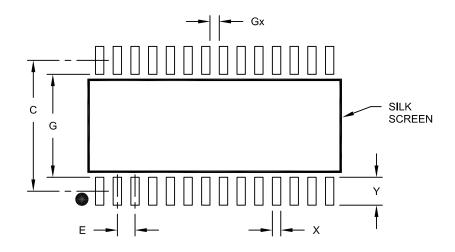

#### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

### 2.8 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

#### 3.2 Architecture Overview

The MIPS32 M4K processor core contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- Dual Internal Bus interfaces

- Power Management

- MIPS16e<sup>®</sup> Support

- · Enhanced JTAG (EJTAG) Controller

#### 3.2.1 EXECUTION UNIT

The MIPS32 M4K processor core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- · 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

- Shifter and store aligner

#### 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The MIPS32 M4K processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32 core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16-bit wide *rs*, 15 iterations are skipped and for a 24-bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32 core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

# TABLE 3-1:MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE HIGH-PERFORMANCE INTEGERMULTIPLY/DIVIDE UNIT LATENCIES AND REPEAT RATES

| Opcode                  | Operand Size (mul <i>rt</i> ) (div <i>rs</i> ) | Latency | Repeat Rate |

|-------------------------|------------------------------------------------|---------|-------------|

| MULT/MULTU, MADD/MADDU, | 16 bits                                        | 1       | 1           |

| MSUB/MSUBU              | 32 bits                                        | 2       | 2           |

| MUL                     | 16 bits                                        | 2       | 1           |

|                         | 32 bits                                        | 3       | 2           |

| DIV/DIVU                | 8 bits                                         | 12      | 11          |

|                         | 16 bits                                        | 19      | 18          |

|                         | 24 bits                                        | 26      | 25          |

|                         | 32 bits                                        | 33      | 32          |

NOTES:

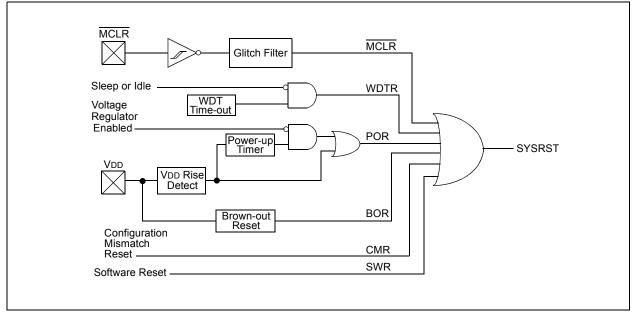

#### 6.0 RESETS

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7.** "**Resets**" (DS60001118), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The following is a list of device Reset sources:

- Power-on Reset (POR)

- Master Clear Reset pin (MCLR)

- · Software Reset (SWR)

- Watchdog Timer Reset (WDTR)

- Brown-out Reset (BOR)

- Configuration Mismatch Reset (CMR)

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

#### FIGURE 6-1: SYSTEM RESET BLOCK DIAGRAM

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 21.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24     | CHSSA<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00:40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16     | CHSSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8      | CHSSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0       |                   |                   |                   | CHSSA             | <7:0>             |                   |                  |                  |  |  |  |  |

#### **REGISTER 9-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER**

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0

CHSSA<31:0> Channel Source Start Address bits

Channel source start address.

Note: This must be the physical address of the source.

#### **REGISTER 9-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | CHDSA<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | CHDSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | CHDSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | CHDSA             | <7:0>             |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                                              |                    |  |  |  |  |

|-------------------|------------------|----------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | table bit U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                         | x = Bit is unknown |  |  |  |  |

bit 31-0 **CHDSA<31:0>:** Channel Destination Start Address bits Channel destination start address.

$\ensuremath{\textbf{Note:}}$  This must be the physical address of the destination.

#### TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       | - /   |       |      |      | Bit  | s    |      |          |        |        |         |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 5390                        | U1EP9                           | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |      | _    | —    | —        | —      | _      | —       | —      | 0000       |

| 5590                        | UIEF9                           | 15:0      |       |       | —     | —     | _     | —     | _    | —    |      |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5240                        | U1EP10                          | 31:16     | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | —        | _      | _      | —       | _      | 0000       |

| 53A0                        | UIEPIU                          | 15:0      |       | _     | _     | -     | _     | _     | _    | _    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                        | U1EP11                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 53BU                        | UIEPII                          | 15:0      | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                        | U1EP12                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEFIZ                          | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53D0                        | U1EP13                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEF 13                         | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     |       | _     | _     |       | -     | _     | _    | _    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 53E0                        | U1EP14                          | 15:0      | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | —        | _      | _      | _       | _      | 0000       |

| 53F0                        | U1EP15                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | —    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

| Bit<br>Range |        |       | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|--------|-------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0    | U-0   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |        | —     |                   | —                 |                   |                   |                  | —                |

| 23:16        | U-0    | U-0   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |        | —     |                   | —                 | -                 |                   |                  | —                |

| 15:8         | U-0    | U-0   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | -      | —     | -                 | —                 | _                 | -                 | —                | —                |

| 7:0          | R/W-0  | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | LSPDEN |       |                   | D                 | EVADDR<6:0        | >                 |                  |                  |

#### REGISTER 10-12: U1ADDR: USB ADDRESS REGISTER

#### Legend:

| U                 |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | ead as '0'           |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7 LSPDEN: Low-Speed Enable Indicator bit

1 = Next token command to be executed at Low-Speed

0 = Next token command to be executed at Full-Speed

bit 6-0 **DEVADDR<6:0>:** 7-bit USB Device Address bits

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | —                 | —                 | _                 | —                 | _                 | —                |                  |  |  |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | —                 | —                 | —                 | _                 | —                 | _                 | —                |                  |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15.0         | —                 | —                 | —                 | -                 | —                 | _                 | —                | -                |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          |                   |                   |                   | FRML              | <7:0>             |                   |                  |                  |  |  |  |  |

#### REGISTER 10-13: U1FRML: USB FRAME NUMBER LOW REGISTER

| Legend:           |                  |                                                 |                    |  |  |  |

|-------------------|------------------|-------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | /ritable bit U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                            | x = Bit is unknown |  |  |  |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **FRML<7:0>:** The 11-bit Frame Number Lower bits

The register bits are updated with the current frame number whenever a SOF TOKEN is received.

#### TABLE 11-2: OUTPUT PIN SELECTION

| RPn Port Pin | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection       |

|--------------|----------|-------------|---------------------------------------------|

| RPA0         | RPA0R    | RPA0R<3:0>  | 0000 = No Connect                           |

| RPB3         | RPB3R    | RPB3R<3:0>  | 0001 = <u>U1TX</u><br>0010 = <u>U2RTS</u>   |

| RPB4         | RPB4R    | RPB4R<3:0>  | 0011 = SS1                                  |

| RPB15        | RPB15R   | RPB15R<3:0> |                                             |

| RPB7         | RPB7R    | RPB7R<3:0>  | 0110 = Reserved<br>0111 = C2OUT             |

| RPC7         | RPC7R    | RPC7R<3:0>  | 1000 = Reserved                             |

| RPC0         | RPC0R    | RPC0R<3:0>  | •                                           |

| RPC5         | RPC5R    | RPC5R<3:0>  | •<br>1111 = Reserved                        |

| RPA1         | RPA1R    | RPA1R<3:0>  | 0000 = No Connect                           |

| RPB5         | RPB5R    | RPB5R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPB1         | RPB1R    | RPB1R<3:0>  | 0011 = SDO1                                 |

| RPB11        | RPB11R   | RPB11R<3:0> | 0100 = SDO2<br>0101 = OC2                   |

| RPB8         | RPB8R    | RPB8R<3:0>  | 0110 = Reserved                             |

| RPA8         | RPA8R    | RPA8R<3:0>  |                                             |

| RPC8         | RPC8R    | RPC8R<3:0>  | •                                           |

| RPA9         | RPA9R    | RPA9R<3:0>  | 1111 = Reserved                             |

| RPA2         | RPA2R    | RPA2R<3:0>  | 0000 = No Connect                           |

| RPB6         | RPB6R    | RPB6R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPA4         | RPA4R    | RPA4R<3:0>  | 0011 = SDO1<br>0100 = SDO2                  |

| RPB13        | RPB13R   | RPB13R<3:0> | 0101 <b>= OC4</b>                           |

| RPB2         | RPB2R    | RPB2R<3:0>  | 0110 = OC5<br>0111 = REFCLKO                |

| RPC6         | RPC6R    | RPC6R<3:0>  | 1000 = Reserved                             |

| RPC1         | RPC1R    | RPC1R<3:0>  |                                             |

| RPC3         | RPC3R    | RPC3R<3:0>  | 1111 = Reserved                             |

| RPA3         | RPA3R    | RPA3R<3:0>  | 0000 = No Connect                           |

| RPB14        | RPB14R   | RPB14R<3:0> |                                             |

| RPB0         | RPB0R    | RPB0R<3:0>  | 0011 = <u>Reserved</u><br>0100 = <u>SS2</u> |

| RPB10        | RPB10R   | RPB10R<3:0> | 0101 <b>= OC3</b>                           |

| RPB9         | RPB9R    | RPB9R<3:0>  |                                             |

| RPC9         | RPC9R    | RPC9R<3:0>  | 1000 = Reserved                             |

| RPC2         | RPC2R    | RPC2R<3:0>  |                                             |

| RPC4         | RPC4R    | RPC4R<3:0>  | 1111 = Reserved                             |

#### 12.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features one synchronous/asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can also be used with the Low-Power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications.

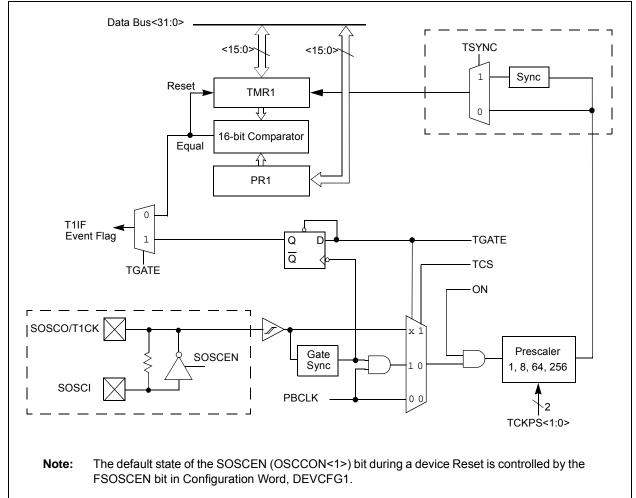

FIGURE 12-1: TIMER1 BLOCK DIAGRAM

The following modes are supported:

- · Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

#### 12.1 Additional Supported Features

- · Selectable clock prescaler

- Timer operation during CPU Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

Figure 12-1 illustrates a general block diagram of Timer1.

| REGIST    | ER 17-1: SPIXCON: SPI CONTROL REGISTER (CONTINUED)                                                                                                                                              |  |  |  |  |  |  |  |  |  |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| bit 17    | SPIFE: Frame Sync Pulse Edge Select bit (Framed SPI mode only)                                                                                                                                  |  |  |  |  |  |  |  |  |  |  |

|           | 1 = Frame synchronization pulse coincides with the first bit clock                                                                                                                              |  |  |  |  |  |  |  |  |  |  |

|           | 0 = Frame synchronization pulse precedes the first bit clock                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

| bit 16    | ENHBUF: Enhanced Buffer Enable bit <sup>(2)</sup>                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |

|           | 1 = Enhanced Buffer mode is enabled                                                                                                                                                             |  |  |  |  |  |  |  |  |  |  |

|           | 0 = Enhanced Buffer mode is disabled                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |

| bit 15    | ON: SPI Peripheral On bit <sup>(1)</sup>                                                                                                                                                        |  |  |  |  |  |  |  |  |  |  |

|           | 1 = SPI Peripheral is enabled                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |

|           | 0 = SPI Peripheral is disabled                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |  |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |

| bit 13    | SIDL: Stop in Idle Mode bit                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |

|           | 1 = Discontinue module operation when the device enters Idle mode                                                                                                                               |  |  |  |  |  |  |  |  |  |  |

|           | 0 = Continue module operation when the device enters Idle mode                                                                                                                                  |  |  |  |  |  |  |  |  |  |  |

| bit 12    | DISSDO: Disable SDOx pin bit                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

|           | 1 = SDOx pin is not used by the module. Pin is controlled by associated PORT register                                                                                                           |  |  |  |  |  |  |  |  |  |  |

|           | 0 = SDOx pin is controlled by the module                                                                                                                                                        |  |  |  |  |  |  |  |  |  |  |

| bit 11-10 | MODE<32,16>: 32/16-Bit Communication Select bits                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |

|           | When AUDEN = 1:                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |

|           | MODE32 MODE16 Communication                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |

|           | 1 1 24-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |

|           | 1 0 32-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |

|           | 0116-bit Data, 16-bit FIFO, 32-bit Channel/64-bit Frame0016-bit Data, 16-bit FIFO, 16-bit Channel/32-bit Frame                                                                                  |  |  |  |  |  |  |  |  |  |  |

|           |                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |

|           | When AUDEN = 0:                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |

|           | MODE32 MODE16 Communication                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |

|           | $1 \times 32$ -bit                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |  |

|           | 0 1 <b>16-bit</b>                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |

|           | 0 0 <b>8-bit</b>                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |

| bit 9     | SMP: SPI Data Input Sample Phase bit                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |

|           | Master mode (MSTEN = 1):                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |  |

|           | 1 = Input data sampled at end of data output time                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |

|           | 0 = Input data sampled at middle of data output time                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |

|           | <u>Slave mode (MSTEN = 0):</u><br>SMP value is ignored when SPI is used in Slave mode. The module always uses SMP = 0.                                                                          |  |  |  |  |  |  |  |  |  |  |

|           | -                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |

| hit 0     | To write a '1' to this bit, the MSTEN value = 1 must first be written.<br><b>CKE:</b> SPI Clock Edge Select bit <sup>(3)</sup>                                                                  |  |  |  |  |  |  |  |  |  |  |

| bit 8     | 1 = Serial output data changes on transition from active clock state to Idle clock state (see the CKP bit)                                                                                      |  |  |  |  |  |  |  |  |  |  |

|           | 0 = Serial output data changes on transition from Idle clock state to active clock state (see the CKP bit)                                                                                      |  |  |  |  |  |  |  |  |  |  |

| bit 7     | SSEN: Slave Select Enable (Slave mode) bit                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |

|           | 1 = SSx pin used for Slave mode                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |

|           | $0 = \overline{SSx}$ pin not used for Slave mode, pin controlled by port function.                                                                                                              |  |  |  |  |  |  |  |  |  |  |

| bit 6     | CKP: Clock Polarity Select bit <sup>(4)</sup>                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |

|           | 1 = Idle state for clock is a high level; active state is a low level                                                                                                                           |  |  |  |  |  |  |  |  |  |  |

|           | 0 = Idle state for clock is a low level; active state is a high level                                                                                                                           |  |  |  |  |  |  |  |  |  |  |

|           |                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |

| Note 1:   | When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. |  |  |  |  |  |  |  |  |  |  |

| 2:        | This bit can only be written when the ON bit = $0$ .                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |

| 3:        | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI                                                                                         |  |  |  |  |  |  |  |  |  |  |

| 5.        | mode (FRMEN = 1).                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |

| 4:        | When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value                                                                                      |  |  |  |  |  |  |  |  |  |  |

|           | of CKP.                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |

|           |                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |

2

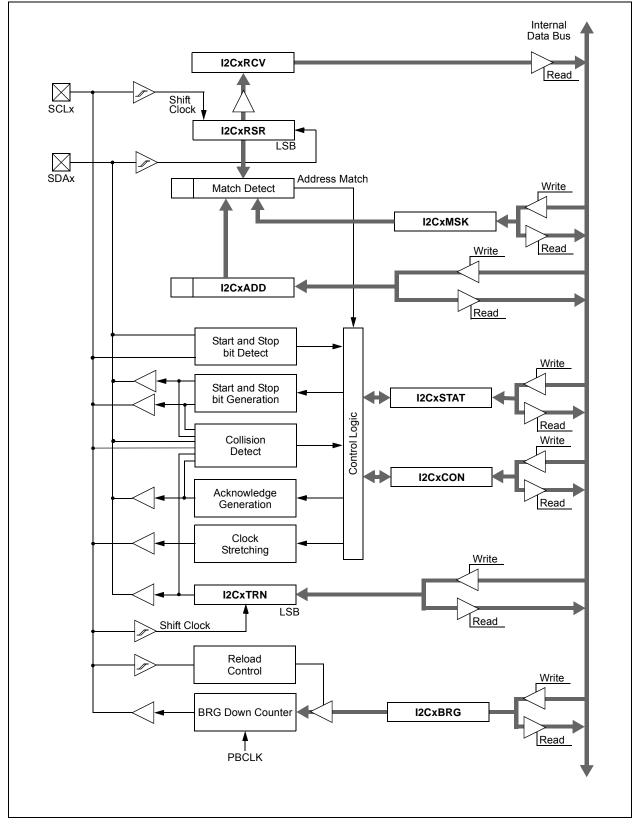

#### FIGURE 18-1: I<sup>2</sup>C BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | —                 | _                 | _                 | —                 | _                 | _                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | _                 | _                 | —                 | _                 | _                | —                |  |  |  |

| 45.0         | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | _                 | PTEN14            | _                 | _                 | —                 |                   | PTEN<10:8>       |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | PTEN<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

### REGISTER 20-4: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-15 Unimplemented: Read as '0'

- bit 15-14 **PTEN14:** PMCS1 Address Port Enable bits

- 1 = PMA14 functions as either PMA14 or PMCS1<sup>(1)</sup>

- 0 = PMA14 functions as port I/O

- bit 13-11 Unimplemented: Read as '0'

- bit 10-2 PTEN<10:2>: PMP Address Port Enable bits

- 1 = PMA<10:2> function as PMP address lines

- 0 = PMA<10:2> function as port I/O

#### bit 1-0 PTEN<1:0>: PMALH/PMALL Address Port Enable bits

- 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL<sup>(2)</sup>

- 0 = PMA1 and PMA0 pads functions as port I/O

- Note 1: The use of this pin as PMA14 or CS1 is selected by the CSF<1:0> bits in the PMCON register.

- 2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by bits ADRMUX<1:0> in the PMCON register.

### 21.1 RTCC Control Registers

#### TABLE 21-1: RTCC REGISTER MAP

| ess                         |                                 | ē         |        |       |          |          |                 | Bits       |        |      |          |                            |           | ŝ       |         |         |            |       |            |

|-----------------------------|---------------------------------|-----------|--------|-------|----------|----------|-----------------|------------|--------|------|----------|----------------------------|-----------|---------|---------|---------|------------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15  | 30/14 | 29/13    | 28/12    | 27/11           | 26/10      | 25/9   | 24/8 | 23/7     | 22/6                       | 21/5      | 20/4    | 19/3    | 18/2    | 17/1       | 16/0  | All Resets |

| 0200                        | RTCCON                          | 31:16     | —      | _     | _        | -        | — — CAL<9:0> 00 |            |        |      |          |                            |           | 0000    |         |         |            |       |            |

| 0200                        | RICCON                          | 15:0      | ON     | _     | SIDL     | —        | —               | -          | —      | _    | RTSECSEL | RTCCLKON                   | —         | _       | RTCWREN | RTCSYNC | HALFSEC    | RTCOE | 0000       |

| 0210                        | RTCALRM                         | 31:16     | _      |       | _        | _        | —               |            | _      |      | _        | -                          | —         | _       | _       | _       | _          | —     | 0000       |

| 0210                        | IN OALIN                        | 15:0      | ALRMEN | CHIME | PIV      | ALRMSYNC |                 | AMASI      | K<3:0> |      |          | ARPT<7:0>                  |           |         |         |         |            | 0000  |            |

| 0220                        | RTCTIME                         | 31:16     | —      | _     | HR1      | 0<1:0>   |                 | HR01       | <3:0>  |      | —        | MIN10<2:0> MIN01<3:0>      |           |         |         | xxxx    |            |       |            |

| 0220                        | INTO THME                       | 15:0      | —      |       | SEC10<2: | 0>       |                 | SEC07      | 1<3:0> |      | —        | —                          | —         | —       | —       | —       | —          | _     | xx00       |

| 0230                        | RTCDATE                         | 31:16     |        | YEAR  | 10<3:0>  |          |                 | YEAR0      | 1<3:0> |      | —        | – – – MONTH10 MONTH01<3:0> |           |         |         | xxxx    |            |       |            |

| 0230                        | RICDAIL                         | 15:0      | —      | _     | DAY      | 10<1:0>  |                 | DAY01      | 1<3:0> |      | —        | _                          | —         | _       | —       | W       | /DAY01<2:0 | >     | xx00       |

| 0240                        | ALRMTIME                        | 31:16     | _      |       | HR1      | 0<1:0>   |                 | HR01<3:0>  |        |      | _        | М                          | IN10<2:0> | ,       |         | MIN01   | <3:0>      |       | xxxx       |

| 0240                        |                                 | 15:0      | —      |       | SEC10<2: | 0>       |                 | SEC01<3:0> |        | _    |          | —                          | _         | —       | —       | _       | —          | xx00  |            |

| 0250                        | ALRMDATE                        | 31:16     | —      | _     | _        | _        | _               | _          | _      |      | _        | -                          | —         | MONTH10 |         | MONTH   | 01<3:0>    |       | 00xx       |

| 0250                        |                                 | 15:0      |        | DAY1  | 0<3:0>   |          |                 | DAY01      | 1<3:0> |      | _        | _                          | _         | _       | _       | W       | /DAY01<2:0 | >     | xx0x       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| REGISTER 21-4. RTCDATE. RTC DATE VALUE REGISTER |                   |                   |                   |                   |                   |                   |                  |                  |  |

|-------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range                                    | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 04.04                                           | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 31:24                                           |                   | YEAR1             | 0<3:0>            |                   |                   | YEAR0             | 1<3:0>           |                  |  |

| 00.40                                           | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 23:16                                           |                   | —                 | _                 | MONTH10           | MONTH01<3:0>      |                   |                  |                  |  |

| 45.0                                            | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8                                            |                   |                   | DAY10             | )<1:0>            | DAY01<3:0>        |                   |                  |                  |  |

| 7.0                                             | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x            | R/W-x            |  |

| 7:0                                             | —                 | _                 | _                 | _                 | — WDAY01<2:0>     |                   |                  | >                |  |

|                                                 |                   |                   |                   |                   |                   |                   |                  |                  |  |

| Legend:                                         |                   |                   |                   |                   |                   |                   |                  |                  |  |

| R = Read                                        | able bit          |                   | W = Writable      | e bit             | U = Unimple       | emented bit, re   | ead as '0'       |                  |  |

| -n = Value                                      | e at POR          |                   | '1' = Bit is se   | t                 | '0' = Bit is cl   | eared             | x = Bit is un    | known            |  |

#### REGISTER 21-4: RTCDATE: RTC DATE VALUE REGISTER

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10s place digit; contains a value from 0 to 9

bit 27-24 **YEAR01<3:0>:** Binary-Coded Decimal Value of Years bits, 1s place digit; contains a value from 0 to 9 bit 23-21 **Unimplemented:** Read as '0'

bit 20 **MONTH10:** Binary-Coded Decimal Value of Months bits, 10s place digit; contains a value of 0 or 1

bit 19-16 **MONTH01<3:0>:** Binary-Coded Decimal Value of Months bits, 1s place digit; contains a value from 0 to 9 bit 15-14 **Unimplemented:** Read as '0'

bit 13-12 DAY10<1:0>: Binary-Coded Decimal Value of Days bits, 10s place digit; contains a value of 0 to 3

bit 11-8 DAY01<3:0>: Binary-Coded Decimal Value of Days bits, 1s place digit; contains a value from 0 to 9

bit 7-3 **Unimplemented:** Read as '0'

bit 2-0 WDAY01<2:0>: Binary-Coded Decimal Value of Weekdays bits; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

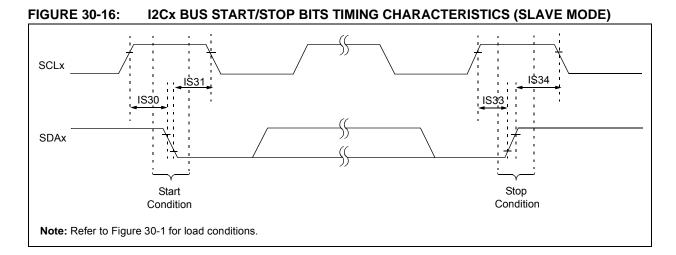

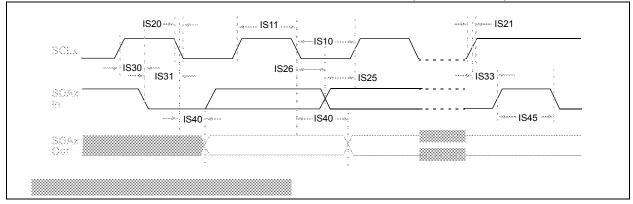

#### TABLE 30-33: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE) (CONTINUED)

| AC CHA        | RACTERIS | STICS                      |                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |                           |                            |  |  |