Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Betans                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 33                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

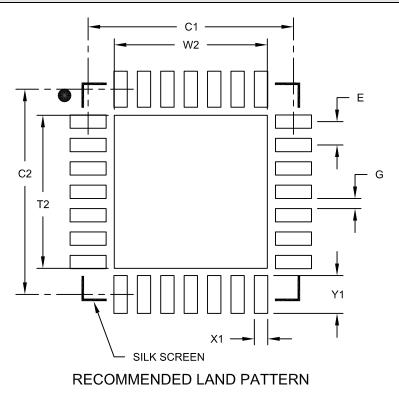

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 44-VTLA (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx210f016dt-i-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

| Exception | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                               |

| DSS       | EJTAG debug single step.                                                                                                                |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                                |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                            |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                         |

| AdEL      | Fetch address alignment error.<br>Fetch reference to protected address.                                                                 |

| IBE       | Instruction fetch bus error.                                                                                                            |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                                      |

| Sys       | Execution of SYSCALL instruction.                                                                                                       |

| Вр        | Execution of BREAK instruction.                                                                                                         |

| RI        | Execution of a reserved instruction.                                                                                                    |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                           |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled.                                                                     |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                                 |

| Tr        | Execution of a trap (when trap condition is true).                                                                                      |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                           |

| AdEL      | Load address alignment error.<br>Load reference to protected address.                                                                   |

| AdES      | Store address alignment error.<br>Store to protected address.                                                                           |

| DBE       | Load or store bus error.                                                                                                                |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                            |

# TABLE 3-3: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE EXCEPTION TYPES

# 3.3 Power Management

The MIPS M4K processor core offers many power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or Halting the clocks, which reduces system power consumption during Idle periods.

## 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see Section 26.0 "Power-Saving Features".

# 3.4 EJTAG Debug Support

The MIPS M4K processor core provides an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the M4K core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used.

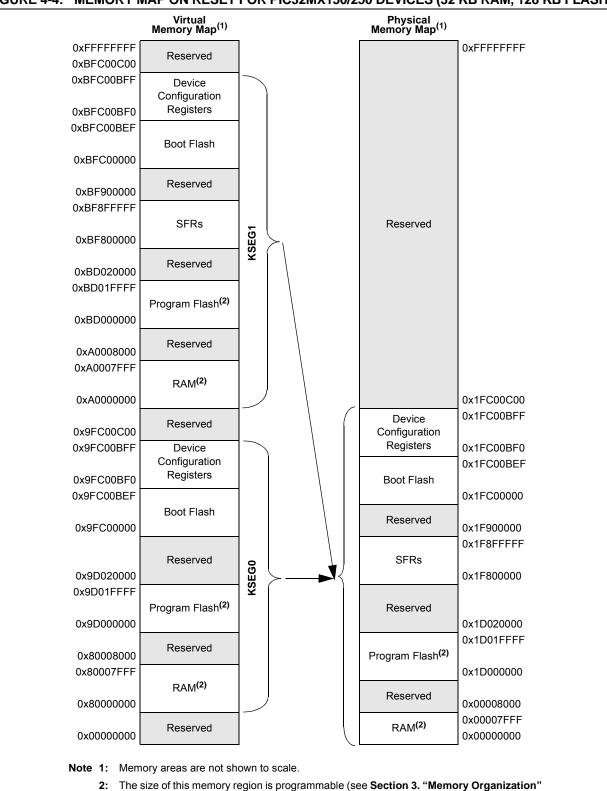

# FIGURE 4-4: MEMORY MAP ON RESET FOR PIC32MX150/250 DEVICES (32 KB RAM, 128 KB FLASH)

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS60001115) in the "*PIC32 Family Reference Manual*") and can be changed by initialization code provided by end-user development tools (refer to the specific development tool documentation for information).

# 6.1 Reset Control Registers

# TABLE 6-1: RESET CONTROL REGISTER MAP

| ess                         |                                 | 0         | Bits  |       |       |       |       |       |      |       |      |      |      | s    |       |      |      |       |           |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|-------|------|------|------|------|-------|------|------|-------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7 | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1 | 16/0  | All Reset |

| F600                        | RCON                            | 31:16     | _     | _     | _     |       | —     | _     |      | —     | _    | _    |      | _    |       | -    | -    | _     | 0000      |

| 1 000                       | ROOM                            | 15:0      | _     |       | -     |       | _     | -     | CMR  | VREGS | EXTR | SWR  |      | WDTO | SLEEP | IDLE | BOR  | POR   | xxxx(2)   |

| E610                        | RSWRST                          | 31:16     |       | —     | -     | —     | —     | —     | —    | —     |      | —    | —    | _    | —     | _    | —    | —     | 0000      |

| 1010                        | N31/K31                         | 15:0      | _     | _     | _     | -     | _     | _     |      | —     | _    | _    | -    | _    | _     | _    | -    | SWRST | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | _                 | _                 |                   | _                 | _                 | —                 | —                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                 | _                 |                   | _                 | _                 | _                 | —                | —                |  |  |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | —                 | _                 | —                 | MVEC              | _                 | TPC<2:0>          |                  |                  |  |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | _                 | _                 | _                 | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |  |  |

### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

# Legend:

| Logona.           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31-16 Unimplemented: Read as '0'

### bit 15-13 Unimplemented: Read as '0'

- bit 12 MVEC: Multi Vector Configuration bit

- 1 = Interrupt controller configured for Multi-vectored mode

- 0 = Interrupt controller configured for Single-vectored mode

- bit 11 Unimplemented: Read as '0'

- bit 10-8 **TPC<2:0>:** Interrupt Proximity Timer Control bits

- 111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer

- 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer

- 101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer

- 100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer

- 011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer

- 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

- 001 = Interrupts of group priority 1 start the Interrupt Proximity timer

- 000 = Disables Interrupt Proximity timer

### bit 7-5 Unimplemented: Read as '0'

- bit 4 INT4EP: External Interrupt 4 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04-04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | ROTRIM<8:1>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0             | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | ROTRIM<0>         | _                 | _                 | _                 | —                 | _                 | —                | —                |  |  |  |  |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15:8         | —                 | _                 | _                 | _                 | —                 | _                 | —                | —                |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 7:0          | _                 | _                 | _                 | _                 | —                 | _                 | _                | —                |  |  |  |  |

### REGISTER 8-4: REFOTRIM: REFERENCE OSCILLATOR TRIM REGISTER

### Legend:

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

Note: While the ON (REFOCON<15>) bit is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | —                 | _                 | —                 | —                 | _                 | _                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | _                 | —                 | —                 | —                 | _                | —                |  |  |  |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |  |  |

| 15:8         | ON <sup>(1)</sup> | —                 | _                 | SUSPEND           | DMABUSY           | _                 | _                | —                |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

# REGISTER 9-1: DMACON: DMA CONTROLLER CONTROL REGISTER

### Legend:

| 0                 |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: DMA On bit<sup>(1)</sup>

- 1 = DMA module is enabled

- 0 = DMA module is disabled

- bit 14-13 **Unimplemented:** Read as '0'

- bit 12 SUSPEND: DMA Suspend bit

- 1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

- 0 = DMA operates normally

### bit 11 DMABUSY: DMA Module Busy bit

- 1 = DMA module is active

- 0 = DMA module is disabled and not actively transferring data

- bit 10-0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | —                 |                   |                   |                   | _                | —                |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | —                 |                   |                   | -                 | _                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | -                 | —                 | —                 | —                 | —                 | -                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | DPPULUP           | DMPULUP           | DPPULDWN          | DMPULDWN          | VBUSON            | OTGEN             | VBUSCHG          | VBUSDIS          |

## REGISTER 10-4: U1OTGCON: USB OTG CONTROL REGISTER

## Legend:

| Logona            |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31-8 Unimplemented: Read as '0'

| bit 7 | DPPUL | UP: D | )+ Pull-U | p Enable | bit |  |

|-------|-------|-------|-----------|----------|-----|--|

|       |       |       |           |          |     |  |

1 = D+ data line pull-up resistor is enabled

0 = D+ data line pull-up resistor is disabled

# bit 6 **DMPULUP:** D- Pull-Up Enable bit

- It 6 DIVIPOLOP: D- Pull-Op Enable bit

- 1 = D- data line pull-up resistor is enabled

0 = D- data line pull-up resistor is disabled

- bit 5 **DPPULDWN:** D+ Pull-Down Enable bit

- 1 = D + data line pull-down resistor is enabled

- 0 = D + data line pull-down resistor is disabled

- bit 4 **DMPULDWN:** D- Pull-Down Enable bit

- 1 = D- data line pull-down resistor is enabled

- 0 = D- data line pull-down resistor is disabled

- bit 3 VBUSON: VBUS Power-on bit

- 1 = VBUS line is powered

- 0 = VBUS line is not powered

- bit 2 OTGEN: OTG Functionality Enable bit

- 1 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under software control

- 0 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under USB hardware control

- bit 1 VBUSCHG: VBUS Charge Enable bit

- 1 = VBUS line is charged through a pull-up resistor

- 0 = VBUS line is not charged through a resistor

- bit 0 VBUSDIS: VBUS Discharge Enable bit

- 1 = VBUS line is discharged through a pull-down resistor

- 0 = VBUS line is not discharged through a resistor

| TABL                        | E 11-7:                  | PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED) |       |       |       |       |       |       |      |      |      |      |      |      |      |      |        |      |            |

|-----------------------------|--------------------------|-------------------------------------------------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|--------|------|------------|

| SS                          |                          |                                                       |       |       |       |       |       |       |      | В    | its  |      |      |      |      |      |        |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name         | Bit Range                                             | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| FB4C                        | RPB8R                    | 31:16                                                 | _     | -     | —     | -     | _     | -     | _    | _    | -    | —    | _    | —    | _    | _    | _      | —    | 0000       |

| 1040                        | IN DOIX                  | 15:0                                                  | _     |       | —     |       | —     |       | _    | —    |      |      | —    | —    |      | RPB8 | <3:0>  |      | 0000       |

| FB50                        | RPB9R                    | 31:16                                                 | —     | —     | —     | —     | —     | —     | _    | —    | —    | —    | —    | —    | _    | —    | —      | —    | 0000       |

| 1 830                       | KF D9K                   | 15:0                                                  | —     | _     | —     | _     | —     | —     | -    |      | —    | —    | —    | —    |      | RPB9 | <3:0>  |      | 0000       |

| FB54                        | RPB10R                   | 31:16                                                 | —     | _     | —     | _     | —     | —     | -    |      | —    | —    | —    | —    | -    | _    | —      | —    | 0000       |

| FB34                        | REDIUR                   | 15:0                                                  | —     | —     | _     | —     | —     | _     |      |      | —    | —    | —    | —    |      | RPB1 | 0<3:0> |      | 0000       |

| FB58                        | RPB11R                   | 31:16                                                 | —     | —     | _     | —     | —     | _     |      |      | —    | —    | —    | —    |      |      | _      | —    | 0000       |

| FB30                        | RPBIIR                   | 15:0                                                  | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    |      | RPB1 | 1<3:0> |      | 0000       |

| FB60                        | RPB13R                   | 31:16                                                 | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB00                        | RPBISR                   | 15:0                                                  | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    |      | RPB1 | 3<3:0> |      | 0000       |

| FB64                        | RPB14R                   | 31:16                                                 | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB04                        |                          | 15:0                                                  | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    |      | RPB1 | 4<3:0> |      | 0000       |

| FB68                        | RPB15R                   | 31:16                                                 | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB00                        | RPBIOR                   | 15:0                                                  | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    |      | RPB1 | 5<3:0> |      | 0000       |

| FB6C                        | RPC0R <sup>(3)</sup>     | 31:16                                                 | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FBOC                        | RECOR                    | 15:0                                                  | —     | —     | —     | —     | —     | —     | -    |      | —    | —    | -    | —    |      | RPCC | <3:0>  |      | 0000       |

| FB70                        | RPC1R <sup>(3)</sup>     | 31:16                                                 | —     | —     | _     | —     | —     | _     |      |      | —    | —    | —    | —    |      |      | _      | —    | 0000       |

| FB/U                        | RPUIK                    | 15:0                                                  | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    |      | RPC1 | <3:0>  |      | 0000       |

| FB74                        | RPC2R <sup>(1)</sup>     | 31:16                                                 | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB/4                        | RP62R <sup>V</sup>       | 15:0                                                  | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    |      | RPC2 | <3:0>  |      | 0000       |

| FB78                        | RPC3R <sup>(3)</sup>     | 31:16                                                 | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB/0                        | RPGSR                    | 15:0                                                  | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    |      | RPC3 | <3:0>  |      | 0000       |

| FB7C                        | RPC4R <sup>(1)</sup>     | 31:16                                                 | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB/C                        | RPC4R <sup>V</sup>       | 15:0                                                  | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    |      | RPC4 | <3:0>  |      | 0000       |

| FB80                        | RPC5R <sup>(1)</sup>     | 31:16                                                 |       | —     | —     | —     | —     | —     | _    |      | —    | _    | —    | —    | _    | _    | —      | _    | 0000       |

| FB80                        | RPUSK"                   | 15:0                                                  |       |       |       |       | —     | _     | _    | _    | _    |      | —    | —    |      | RPC5 | i<3:0> |      | 0000       |

| FB84                        | RPC6R <sup>(1)</sup>     | 31:16                                                 |       |       |       |       | —     | _     | _    | _    | _    |      | —    | —    | _    | —    |        | —    | 0000       |

| FB04                        | RPU0K"                   | 15:0                                                  |       |       |       |       | —     | _     | _    | _    | _    |      | —    | —    |      | RPC  | <3:0>  |      | 0000       |

| ED00                        |                          | 31:16                                                 |       | —     |       | —     | —     | —     | _    |      | —    |      | —    | —    | _    | _    | —      |      | 0000       |

| F B 08                      | B88 RPC7R <sup>(1)</sup> | 15:0                                                  | _     | _     | —     | _     | _     | —     | —    | _    | —    |      | _    | _    |      | RPC7 | <3:0>  |      | 0000       |

#### OT AUTOUT DEALATED MAD

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register is only available on 44-pin devices. Note 1:

2: 3:

This register is only available on PIC32MX1XX devices. This register is only available on 36-pin and 44-pin devices.

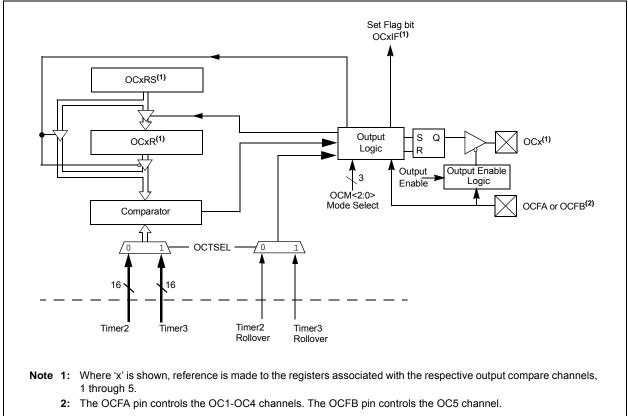

# 16.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 16. "Output Compare" (DS60001111), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Output Compare module is used to generate a single pulse or a train of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation. The following are some of the key features:

- · Multiple Output Compare Modules in a device

- Programmable interrupt generation on compare event

- Single and Dual Compare modes

- Single and continuous output pulse generation

- Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

# REGISTER 17-3: SPIxSTAT: SPI STATUS REGISTER

bit 3 SPITBE: SPI Transmit Buffer Empty Status bit 1 = Transmit buffer, SPIxTXB is empty 0 = Transmit buffer, SPIxTXB is not empty Automatically set in hardware when SPI transfers data from SPIxTXB to SPIxSR. Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB. bit 2 Unimplemented: Read as '0' bit 1 SPITBF: SPI Transmit Buffer Full Status bit 1 = Transmit not yet started, SPITXB is full 0 = Transmit buffer is not full Standard Buffer Mode: Automatically set in hardware when the core writes to the SPIBUF location, loading SPITXB. Automatically cleared in hardware when the SPI module transfers data from SPITXB to SPISR. Enhanced Buffer Mode: Set when CWPTR + 1 = SRPTR; cleared otherwise bit 0 SPIRBF: SPI Receive Buffer Full Status bit 1 = Receive buffer, SPIxRXB is full

0 = Receive buffer, SPIxRXB is not full

### Standard Buffer Mode:

Automatically set in hardware when the SPI module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

### Enhanced Buffer Mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise

| REGISTE | R 18-1:           | I2CxCON: I <sup>2</sup> C CONTROL REGISTER (CONTINUED)                                                                                                                |

|---------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7   | GCEN: Ge          | eneral Call Enable bit (when operating as I <sup>2</sup> C slave)                                                                                                     |

|         | (module           | interrupt when a general call address is received in the I2CxRSR<br>e is enabled for reception)                                                                       |

|         |                   | al call address is disabled                                                                                                                                           |

| bit 6   | STREN: S          | CLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)                                                                                               |

|         |                   | njunction with SCLREL bit.                                                                                                                                            |

|         |                   | e software or receive clock stretching                                                                                                                                |

| L:1 F   |                   | e software or receive clock stretching                                                                                                                                |

| bit 5   |                   | cknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive) is transmitted when the software initiates an Acknowledge sequence. |

|         |                   | a NACK during an Acknowledge sequence                                                                                                                                 |

|         |                   | an ACK during an Acknowledge sequence                                                                                                                                 |

| bit 4   | ACKEN: A receive) | cknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master                                                                   |

|         | Hardwa            | Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit.<br>are clear at end of master Acknowledge sequence.<br>wledge sequence not in progress        |

| bit 3   | RCEN: Re          | ceive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                          |

|         |                   | es Receive mode for I <sup>2</sup> C. Hardware clear at end of eighth bit of master receive data byte.<br>The sequence not in progress                                |

| bit 2   | PEN: Stop         | Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                      |

|         |                   | Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence. ondition not in progress                                                         |

| bit 1   | RSEN: Re          | peated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                         |

|         |                   | Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of Repeated Start sequence.                                                                     |

|         | 0 = Repeat        | ted Start condition not in progress                                                                                                                                   |

| bit 0   |                   | Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                      |

|         |                   | Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence. ondition not in progress                                                       |

|         |                   |                                                                                                                                                                       |

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

### REGISTER 19-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED) bit 7-6 URXISEL<1:0>: Receive Interrupt Mode Selection bit 11 = Reserved; do not use 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (i.e., has 6 or more data characters) 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (i.e., has 4 or more data characters) 00 = Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character) bit 5 ADDEN: Address Character Detect bit (bit 8 of received data = 1) 1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect. 0 = Address Detect mode is disabled bit 4 **RIDLE:** Receiver Idle bit (read-only) 1 =Receiver is Idle 0 = Data is being received PERR: Parity Error Status bit (read-only) bit 3 1 = Parity error has been detected for the current character 0 = Parity error has not been detected bit 2 FERR: Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character 0 = Framing error has not been detected **OERR:** Receive Buffer Overrun Error Status bit. bit 1 This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and the RSR to an empty state. 1 = Receive buffer has overflowed 0 = Receive buffer has not overflowed bit 0 **URXDA:** Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

# 20.1 PMP Control Registers

# TABLE 20-1: PARALLEL MASTER PORT REGISTER MAP

| ess                         |                                 | 0             |       |                         |       |       |         |        |        | Bi     | ts      |        |           |       |        |      |       |       |            |

|-----------------------------|---------------------------------|---------------|-------|-------------------------|-------|-------|---------|--------|--------|--------|---------|--------|-----------|-------|--------|------|-------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14                   | 29/13 | 28/12 | 27/11   | 26/10  | 25/9   | 24/8   | 23/7    | 22/6   | 21/5      | 20/4  | 19/3   | 18/2 | 17/1  | 16/0  | All Resets |

| 7000                        | PMCON                           | 31:16         | —     | _                       | -     | _     |         |        | -      | _      | —       | —      | —         |       |        | —    | —     | _     | 0000       |

| 7000                        | FINCON                          | 15:0          | ON    | _                       | SIDL  | ADRML | IX<1:0> | PMPTTL | PTWREN | PTRDEN | CSF∙    | <1:0>  | ALP       |       | CS1P   | _    | WRSP  | RDSP  | 0000       |

| 7010                        | PMMODE                          | 31:16         | —     | _                       | -     | _     | _       |        | _      | _      | —       | _      | —         |       | -      | _    | —     | _     | 0000       |

| 7010                        | FININODE                        | 15:0          | BUSY  | IRQM                    | <1:0> | INCM  | <1:0>   | —      | MODE   | <1:0>  | WAITE   | 3<1:0> |           | WAITM | /<3:0> |      | WAITE | <1:0> | 0000       |

|                             |                                 | 31:16         | _     | —                       | _     | _     | —       | —      | —      | _      | _       | _      | _         | —     | —      | _    | _     | —     | 0000       |

| 7020                        | PMADDR                          | 15:0          | _     | CS1<br>ADDR14           | _     | _     | _       |        |        |        |         | /      | ADDR<10:0 | >     |        |      |       |       | 0000       |

| 7030                        | PMDOUT                          | 31:16<br>15:0 |       |                         |       |       |         |        |        | DATAOU | T<31:0> |        |           |       |        |      |       |       | 0000       |

| 7040                        | PMDIN                           | 31:16<br>15:0 |       | DATAIN<31:0>            |       |       |         |        |        |        |         |        |           |       |        |      |       |       |            |

| 7050                        |                                 | 31:16         | _     | _                       |       | _     | -       |        | -      | _      | _       | _      | —         |       |        | _    | _     |       | 0000       |

| 7050                        | PMAEN                           | 15:0          | _     | - PTEN14 PTEN<10:0> 000 |       |       |         |        |        |        | 0000    |        |           |       |        |      |       |       |            |

| 7060                        | PMSTAT                          | 31:16         |       |                         |       | _     |         |        | _      | _      |         |        | —         | _     | _      |      | —     | _     | 0000       |

| 1000                        | FINISTAT                        | 15:0          | IBF   | IBOV                    | _     | _     | IB3F    | IB2F   | IB1F   | IB0F   | OBE     | OBUF   | —         | _     | OB3E   | OB2E | OB1E  | OB0E  | 008F       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

## TABLE 30-18: PLL CLOCK TIMING SPECIFICATIONS

| AC CHA        | RACTERI | STICS                                                          | (unless ot        | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |         |      |                                |                                      |  |  |  |

|---------------|---------|----------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|--------------------------------|--------------------------------------|--|--|--|

| Param.<br>No. | Symbol  | Characteristi                                                  | cs <sup>(1)</sup> | Min.                                                                                                                                                                                               | Typical | Max. | Units                          | Conditions                           |  |  |  |

| OS50          | Fplli   | PLL Voltage Control<br>Oscillator (VCO) Inp<br>Frequency Range |                   | 3.92                                                                                                                                                                                               | _       | 5    | MHz                            | ECPLL, HSPLL, XTPLL,<br>FRCPLL modes |  |  |  |

| OS51          | Fsys    | On-Chip VCO Syste<br>Frequency                                 | m                 | 60                                                                                                                                                                                                 | —       | 120  | MHz                            | _                                    |  |  |  |

| OS52          | TLOCK   | PLL Start-up Time (Lock Time)                                  |                   | _                                                                                                                                                                                                  | _       | 2    | ms                             | —                                    |  |  |  |

| OS53          | DCLK    | CLKO Stability <sup>(2)</sup><br>(Period Jitter or Cum         | -0.25             | —                                                                                                                                                                                                  | +0.25   | %    | Measured over 100 ms<br>period |                                      |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{SYSCLK}{CommunicationClock}}}$$

For example, if SYSCLK = 40 MHz and SPI bit rate = 20 MHz, the effective jitter is as follows:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{40}{20}}} = \frac{D_{CLK}}{1.41}$$

# TABLE 30-19: INTERNAL FRC ACCURACY

| АС СНА        | RACTERISTICS                                    | (unless | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |      |       |            |  |  |  |  |

|---------------|-------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|--|--|

| Param.<br>No. | Characteristics                                 | Min.    | Typical                                                                                                                                                                                            | Max. | Units | Conditions |  |  |  |  |

| Internal      | Internal FRC Accuracy @ 8.00 MHz <sup>(1)</sup> |         |                                                                                                                                                                                                    |      |       |            |  |  |  |  |

| F20b          | FRC                                             | -0.9    |                                                                                                                                                                                                    | +0.9 | %     | _          |  |  |  |  |

Note 1: Frequency calibrated at 25°C and 3.3V. The TUN bits can be used to compensate for temperature drift.

### TABLE 30-20: INTERNAL LPRC ACCURACY

| АС СНА        | RACTERISTICS                    | (unless | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |      |       |            |  |  |  |  |

|---------------|---------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|--|--|

| Param.<br>No. | Characteristics                 | Min.    | Typical                                                                                                                                                                                            | Max. | Units | Conditions |  |  |  |  |

| LPRC @        | LPRC @ 31.25 kHz <sup>(1)</sup> |         |                                                                                                                                                                                                    |      |       |            |  |  |  |  |

| F21           | 21 LPRC                         |         | —                                                                                                                                                                                                  | +15  | %     | _          |  |  |  |  |

**Note 1:** Change of LPRC frequency as VDD changes.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

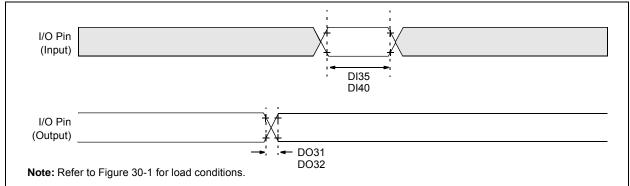

### FIGURE 30-3: I/O TIMING CHARACTERISTICS

### TABLE 30-21: I/O TIMING REQUIREMENTS

| AC CHAP       | RACTERIS | STICS                    | (unless other        | Standard Operating Conditions: 2.3V to 3.6Vunless otherwise stated)Dperating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                        |         |       |            |  |  |  |

|---------------|----------|--------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------|-------|------------|--|--|--|

| Param.<br>No. | Symbol   | Characteris              | stics <sup>(2)</sup> | Min.                                                                                                                                                                                              | Typical <sup>(1)</sup> | Max.    | Units | Conditions |  |  |  |

| DO31          | TIOR     | Port Output Rise Tir     | ne                   |                                                                                                                                                                                                   | 5                      | 15      | ns    | Vdd < 2.5V |  |  |  |

|               |          |                          |                      |                                                                                                                                                                                                   | 5                      | 10      | ns    | Vdd > 2.5V |  |  |  |

| DO32          | TIOF     | Port Output Fall Tim     | е                    | _                                                                                                                                                                                                 | 5                      | 15      | ns    | Vdd < 2.5V |  |  |  |

|               |          |                          |                      |                                                                                                                                                                                                   | 5                      | 10      | ns    | VDD > 2.5V |  |  |  |

| DI35          | Tinp     | NTx Pin High or Low Time |                      | 10                                                                                                                                                                                                | _                      | _       | ns    | _          |  |  |  |

| DI40          | Trbp     | CNx High or Low Tir      | 2                    | _                                                                                                                                                                                                 |                        | TSYSCLK |       |            |  |  |  |

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: This parameter is characterized, but not tested in manufacturing.

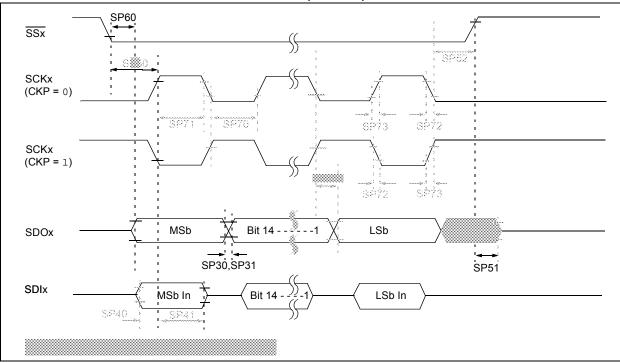

## FIGURE 30-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

## TABLE 30-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        | RACTERIS              | TICS                                                                      | $\begin{array}{c} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature } -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |      |       |                    |  |  |  |

|---------------|-----------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|--|--|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                                            | Min.                                                                                                                                                                                                                                                                               | Typical <sup>(2)</sup> | Max. | Units | Conditions         |  |  |  |

| SP70          | TscL                  | SCKx Input Low Time (Note 3)                                              | Tsck/2                                                                                                                                                                                                                                                                             | _                      | _    | ns    | —                  |  |  |  |

| SP71          | TscH                  | SCKx Input High Time (Note 3)                                             | Tsck/2                                                                                                                                                                                                                                                                             | —                      | _    | ns    | —                  |  |  |  |

| SP72          | TscF                  | SCKx Input Fall Time                                                      | _                                                                                                                                                                                                                                                                                  | 5                      | 10   | ns    | —                  |  |  |  |

| SP73          | TscR                  | SCKx Input Rise Time                                                      | —                                                                                                                                                                                                                                                                                  | 5                      | 10   | ns    | —                  |  |  |  |

| SP30          | TDOF                  | SDOx Data Output Fall Time (Note 4)                                       | —                                                                                                                                                                                                                                                                                  | —                      | _    | ns    | See parameter DO32 |  |  |  |

| SP31          | TDOR                  | SDOx Data Output Rise Time (Note 4)                                       | —                                                                                                                                                                                                                                                                                  | —                      | _    | ns    | See parameter DO31 |  |  |  |

| SP35          | TscH2doV,             | SDOx Data Output Valid after                                              |                                                                                                                                                                                                                                                                                    | _                      | 20   | ns    | VDD > 2.7V         |  |  |  |

|               | TscL2DoV              | SCKx Edge                                                                 | _                                                                                                                                                                                                                                                                                  | —                      | 30   | ns    | VDD < 2.7V         |  |  |  |

| SP40          | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge                                | 10                                                                                                                                                                                                                                                                                 | —                      | _    | ns    | —                  |  |  |  |

| SP41          | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                 | 10                                                                                                                                                                                                                                                                                 | —                      |      | ns    | —                  |  |  |  |

| SP50          | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ Input | 175                                                                                                                                                                                                                                                                                | —                      |      | ns    | _                  |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 50 ns.

- **4:** Assumes 50 pF load on all SPIx pins.

## TABLE 30-32: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHA        |         | ISTICS          |                               | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |      |       |                                |  |  |  |  |

|---------------|---------|-----------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------|--|--|--|--|

| Param.<br>No. | Symbol  | Charact         | eristics                      | Min. <sup>(1)</sup>                                                                                                                                                                                | Max. | Units | Conditions                     |  |  |  |  |

| IM10          | TLO:SCL | Clock Low Time  | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                    | —    | μs    | —                              |  |  |  |  |

|               |         |                 | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                    | _    | μS    | —                              |  |  |  |  |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                    | _    | μs    | _                              |  |  |  |  |

| IM11          | THI:SCL | Clock High Time |                               |                                                                                                                                                                                                    | _    | μS    | —                              |  |  |  |  |

|               |         |                 | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                    | _    | μs    | —                              |  |  |  |  |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                    | —    | μs    | —                              |  |  |  |  |

| IM20          | TF:SCL  | SDAx and SCLx   | 100 kHz mode                  | —                                                                                                                                                                                                  | 300  | ns    | CB is specified to be          |  |  |  |  |

|               |         | Fall Time       | 400 kHz mode                  | 20 + 0.1 Св                                                                                                                                                                                        | 300  | ns    | from 10 to 400 pF              |  |  |  |  |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | _                                                                                                                                                                                                  | 100  | ns    |                                |  |  |  |  |

| IM21          | TR:SCL  | SDAx and SCLx   | 100 kHz mode                  | —                                                                                                                                                                                                  | 1000 | ns    | CB is specified to be          |  |  |  |  |

|               |         | Rise Time       | 400 kHz mode                  | 20 + 0.1 Св                                                                                                                                                                                        | 300  | ns    | from 10 to 400 pF              |  |  |  |  |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | _                                                                                                                                                                                                  | 300  | ns    |                                |  |  |  |  |

| IM25          | TSU:DAT | Data Input      | 100 kHz mode                  | 250                                                                                                                                                                                                | _    | ns    | —                              |  |  |  |  |

|               |         | Setup Time      | 400 kHz mode                  | 100                                                                                                                                                                                                | —    | ns    |                                |  |  |  |  |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | 100                                                                                                                                                                                                | _    | ns    |                                |  |  |  |  |

| IM26          | THD:DAT | Data Input      | 100 kHz mode                  | 0                                                                                                                                                                                                  | _    | μS    | —                              |  |  |  |  |

|               |         | Hold Time       | 400 kHz mode                  | 0                                                                                                                                                                                                  | 0.9  | μs    |                                |  |  |  |  |

|               |         |                 | 1 MHz mode<br>(Note 2)        | 0                                                                                                                                                                                                  | 0.3  | μs    |                                |  |  |  |  |

| IM30          | TSU:STA | Start Condition | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                    | _    | μS    | Only relevant for              |  |  |  |  |

|               |         | Setup Time      | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                    | —    | μS    | Repeated Start condition       |  |  |  |  |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                    | —    | μs    | condition                      |  |  |  |  |

| IM31          | THD:STA | Start Condition | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                    | —    | μS    | After this period, the         |  |  |  |  |

|               |         | Hold Time       | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                    | —    | μs    | first clock pulse is generated |  |  |  |  |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                    | —    | μS    | generaleu                      |  |  |  |  |

| IM33          | Tsu:sto | Stop Condition  | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                    |      | μS    |                                |  |  |  |  |

|               |         | Setup Time      | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                    |      | μs    |                                |  |  |  |  |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                    |      | μs    |                                |  |  |  |  |

| IM34          | THD:STO | Stop Condition  | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                    |      | ns    | —                              |  |  |  |  |

|               |         | Hold Time       | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                    |      | ns    | ]                              |  |  |  |  |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                    | —    | ns    |                                |  |  |  |  |

**Note 1:** BRG is the value of the  $I^2C$  Baud Rate Generator.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** The typical value for this parameter is 104 ns.

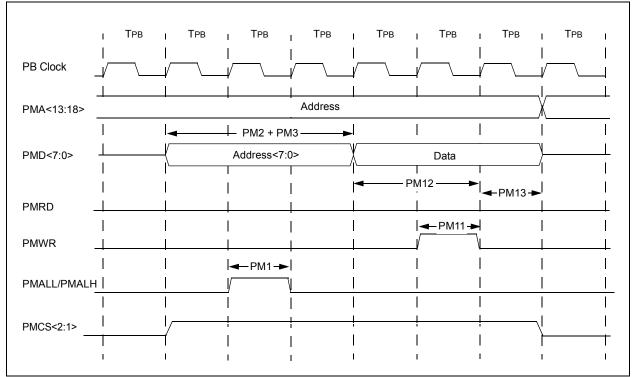

| AC CHA        | ARACTER | ISTICS                                                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |       |      |       |            |  |  |  |

|---------------|---------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------|--|--|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>                                       | Min.                                                                                                                                                                                                                                                                                  | Тур.  | Max. | Units | Conditions |  |  |  |

| PM1           | Tlat    | PMALL/PMALH Pulse Width                                              |                                                                                                                                                                                                                                                                                       | 1 Трв | _    | _     | _          |  |  |  |

| PM2           | TADSU   | Address Out Valid to<br>PMALL/PMALH Invalid (address<br>setup time)  | _                                                                                                                                                                                                                                                                                     | 2 Трв | _    | _     | _          |  |  |  |

| PM3           | Tadhold | PMALL/PMALH Invalid to<br>Address Out Invalid (address<br>hold time) | —                                                                                                                                                                                                                                                                                     | 1 Трв | _    | —     | _          |  |  |  |

| PM4           | TAHOLD  | PMRD Inactive to Address Out<br>Invalid<br>(address hold time)       | 5                                                                                                                                                                                                                                                                                     | _     | _    | ns    | _          |  |  |  |

| PM5           | Trd     | PMRD Pulse Width                                                     | _                                                                                                                                                                                                                                                                                     | 1 Трв | _    | _     | —          |  |  |  |