Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 33                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx210f016dt-v-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | Device Overview                                    | 19  |

|-------|----------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 32-bit MCUs.   |     |

| 3.0   | CPU.                                               |     |

| 4.0   | Memory Organization                                |     |

| 5.0   | Flash Program Memory                               |     |

| 6.0   | Resets                                             |     |

| 7.0   | Interrupt Controller                               |     |

| 8.0   | Oscillator Configuration                           | 73  |

| 9.0   | Direct Memory Access (DMA) Controller              | 83  |

| 10.0  | USB On-The-Go (OTG)                                | 103 |

| 11.0  | I/O Ports                                          | 127 |

| 12.0  | Timer1                                             | 143 |

| 13.0  | Timer2/3, Timer4/5                                 | 147 |

| 14.0  | Watchdog Timer (WDT)                               | 153 |

| 15.0  | Input Capture                                      | 157 |

|       | Output Compare                                     |     |

| 17.0  | Serial Peripheral Interface (SPI)                  | 165 |

| 18.0  | Inter-Integrated Circuit (I <sup>2</sup> C)        |     |

| 19.0  | Universal Asynchronous Receiver Transmitter (UART) | 181 |

|       | Parallel Master Port (PMP)                         |     |

|       | Real-Time Clock and Calendar (RTCC)                |     |

| 22.0  | 10-bit Analog-to-Digital Converter (ADC)           | 209 |

| 23.0  | Comparator                                         |     |

| 24.0  | Comparator Voltage Reference (CVREF)               | 223 |

| 25.0  | Charge Time Measurement Unit (CTMU)                | 227 |

| 26.0  | Power-Saving Features                              | 233 |

| 27.0  | Special Features                                   | 239 |

| 28.0  | Instruction Set                                    |     |

| 29.0  | Development Support                                | 253 |

|       | Electrical Characteristics                         |     |

|       | 50 MHz Electrical Characteristics                  |     |

|       | DC and AC Device Characteristics Graphs            |     |

|       | Packaging Information                              |     |

|       | Aicrochip Web Site                                 |     |

|       | omer Change Notification Service                   |     |

|       | omer Support                                       |     |

| Produ | uct Identification System                          | 342 |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                   | Pin Nu                            | mber <sup>(1)</sup> | •                               |             |                |                                                                         |

|----------|-------------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------|-------------------------------------------------------------------------|

| Pin Name | 28-pin<br>QFN     | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                                             |

| USBID    | 11 <sup>(3)</sup> | 14 <sup>(3)</sup>                 | 15 <sup>(3)</sup>   | 41(3)                           | ı           | ST             | USB OTG ID detect                                                       |

| CTED1    | 27                | 2                                 | 33                  | 19                              | I           | ST             | CTMU External Edge Input                                                |

| CTED2    | 28                | 3                                 | 34                  | 20                              | I           | ST             | 1                                                                       |

| CTED3    | 13                | 16                                | 17                  | 43                              | I           | ST             | 1                                                                       |

| CTED4    | 15                | 18                                | 19                  | 1                               | I           | ST             | 1                                                                       |

| CTED5    | 22                | 25                                | 28                  | 14                              | I           | ST             | 1                                                                       |

| CTED6    | 23                | 26                                | 29                  | 15                              | I           | ST             | 1                                                                       |

| CTED7    | _                 | _                                 | 20                  | 5                               | I           | ST             | 1                                                                       |

| CTED8    | _                 | _                                 | -                   | 13                              | I           | ST             | 1                                                                       |

| CTED9    | 9                 | 12                                | 10                  | 34                              | I           | ST             | 1                                                                       |

| CTED10   | 14                | 17                                | 18                  | 44                              | I           | ST             | 1                                                                       |

| CTED11   | 18                | 21                                | 24                  | 8                               | I           | ST             | 1                                                                       |

| CTED12   | 2                 | 5                                 | 36                  | 22                              | I           | ST             | 1                                                                       |

| CTED13   | 3                 | 6                                 | 1                   | 23                              | I           | ST             | 1                                                                       |

| CTPLS    | 21                | 24                                | 27                  | 11                              | 0           | _              | CTMU Pulse Output                                                       |

| PGED1    | 1                 | 4                                 | 35                  | 21                              | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 1          |

| PGEC1    | 2                 | 5                                 | 36                  | 22                              | I           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 1 |

| PGED2    | 18                | 21                                | 24                  | 8                               | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 2          |

| PGEC2    | 19                | 22                                | 25                  | 9                               | I           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 2 |

| PGED3    | 11 <sup>(2)</sup> | 14 <sup>(2)</sup>                 | 15 <sup>(2)</sup>   | 41 <sup>(2)</sup>               | I/O         | ST             | Data I/O pin for Programming/Debugging                                  |

| PGED3    | 27 <sup>(3)</sup> | 2 <sup>(3)</sup>                  | 33(3)               | 19 <sup>(3)</sup>               | 1/0         | 31             | Communication Channel 3                                                 |

| DCEC2    | 12 <sup>(2)</sup> | 15 <sup>(2)</sup>                 | 16 <sup>(2)</sup>   | 42 <sup>(2)</sup>               |             | ST             | Clock input pin for Programming/                                        |

| PGEC3    | 28 <sup>(3)</sup> | 3(3)                              | 34 <sup>(3)</sup>   | 20 <sup>(3)</sup>               | 1 '         | 31             | Debugging Communication Channel 3                                       |

| PGED4    | _                 | _                                 | 3                   | 12                              | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 4          |

| PGEC4    | _                 | _                                 | 4                   | 13                              | I           | ST             | Clock input pin for Programming/<br>Debugging Communication Channel 4   |

**Legend:** CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

Analog = Analog input O = Output P = Power I = Input

TTL = TTL input buffer

PPS = Peripheral Pin Select

--=N/A

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

**3:** Pin number for PIC32MX2XX devices only.

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32 $^{\circledR}$  architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then

adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

# 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e, is also available by accessing the CP0 registers, listed in Table 3-2.

TABLE 3-2: COPROCESSOR 0 REGISTERS

| Register<br>Number | Register<br>Name        | Function                                                                 |

|--------------------|-------------------------|--------------------------------------------------------------------------|

| 0-6                | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 7                  | HWREna                  | Enables access via the RDHWR instruction to selected hardware registers. |

| 8                  | BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.       |

| 9                  | Count <sup>(1)</sup>    | Processor cycle count.                                                   |

| 10                 | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 11                 | Compare <sup>(1)</sup>  | Timer interrupt control.                                                 |

| 12                 | Status <sup>(1)</sup>   | Processor status and control.                                            |

| 12                 | IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                     |

| 12                 | SRSCtl <sup>(1)</sup>   | Shadow register set status and control.                                  |

| 12                 | SRSMap <sup>(1)</sup>   | Provides mapping from vectored interrupt to a shadow set.                |

| 13                 | Cause <sup>(1)</sup>    | Cause of last general exception.                                         |

| 14                 | EPC <sup>(1)</sup>      | Program counter at last exception.                                       |

| 15                 | PRId                    | Processor identification and revision.                                   |

| 15                 | EBASE                   | Exception vector base register.                                          |

| 16                 | Config                  | Configuration register.                                                  |

| 16                 | Config1                 | Configuration Register 1.                                                |

| 16                 | Config2                 | Configuration Register 2.                                                |

| 16                 | Config3                 | Configuration Register 3.                                                |

| 17-22              | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status.                                      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                 |

| 25-29              | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error.                                           |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                       |

Note 1: Registers used in exception processing.

2: Registers used during debug.

## REGISTER 4-7: BMXPFMSZ: PROGRAM FLASH (PFM) SIZE REGISTER

| Bit<br>Range          | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|-----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.24                 | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 31:24 BMXPFMSZ<31:24> |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 22:16                 | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 23:16                 | BMXPFMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 45.0                  | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 15:8                  |                   |                   |                   | BMXPFN            | MSZ<15:8>         |                   |                  |                  |  |  |  |  |  |  |

| 7.0                   | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 7:0                   |                   | BMXPFMSZ<7:0>     |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 BMXPFMSZ<31:0>: Program Flash Memory (PFM) Size bits

Static value that indicates the size of the PFM in bytes:

0x00004000 = Device has 16 KB Flash

0x00008000 = Device has 32 KB Flash

0x00010000 = Device has 64 KB Flash

0x00020000 = Device has 128 KB Flash

0x00040000 = Device has 256 KB Flash

## REGISTER 4-8: BMXBOOTSZ: BOOT FLASH (IFM) SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 04.04        | R                 | R                 | R R               |                   | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 31:24        | BMXBOOTSZ<31:24>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 22:46        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 23:16        | BMXBOOTSZ<23:16>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 15:8         |                   |                   |                   | BMXBOC            | TSZ<15:8>         |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 7:0          | BMXBOOTSZ<7:0>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

## bit 31-0 BMXBOOTSZ<31:0>: Boot Flash Memory (BFM) Size bits

Static value that indicates the size of the Boot PFM in bytes:

0x00000C00 = Device has 3 KB boot Flash

## 6.0 RESETS

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7.** "**Resets**" (DS60001118), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

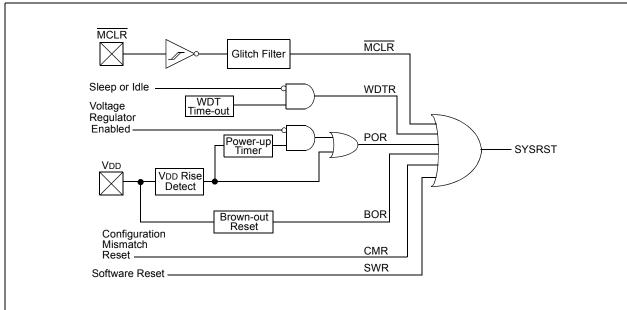

The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The following is a list of device Reset sources:

- Power-on Reset (POR)

- Master Clear Reset pin (MCLR)

- · Software Reset (SWR)

- Watchdog Timer Reset (WDTR)

- · Brown-out Reset (BOR)

- · Configuration Mismatch Reset (CMR)

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

FIGURE 6-1: SYSTEM RESET BLOCK DIAGRAM

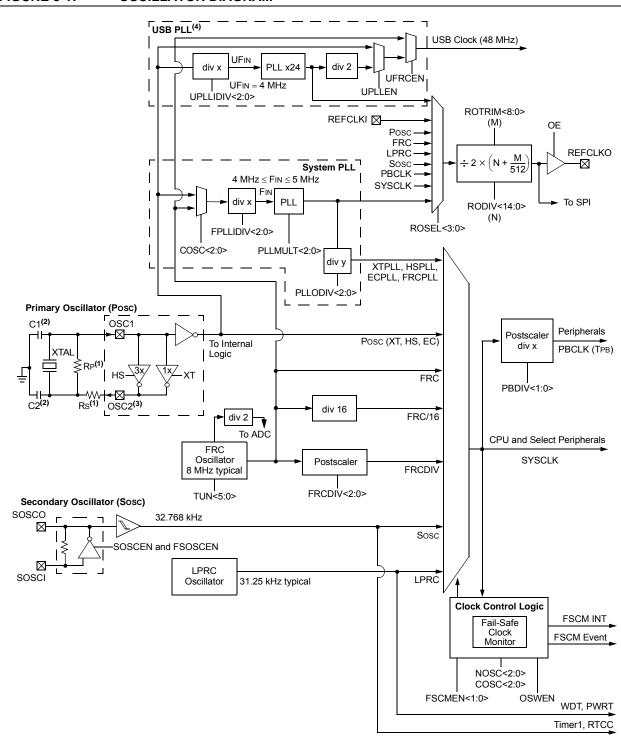

FIGURE 8-1: OSCILLATOR DIAGRAM

- Notes: 1. A series resistor, Rs, may be required for AT strip cut crystals or eliminate clipping. Alternately, to increase oscillator circuit gain, add a parallel resistor, RP, with a value of 1 MΩ.

- Refer to Section 6. "Oscillator Configuration" (DS60001112) in the "PIC32 Family Reference Manual" for help in determining the best oscillator components.

- 3. The PBCLK out is only available on the OSC2 pin in certain clock modes.

- 4. The USB PLL is only available on PIC32MX2XX devices.

### REGISTER 10-4: U10TGCON: USB OTG CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | -                 | _                 | -                 | _                 | _                 | -                | _                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | DPPULUP           | DMPULUP           | DPPULDWN          | DMPULDWN          | VBUSON            | OTGEN             | VBUSCHG          | VBUSDIS          |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 **DPPULUP:** D+ Pull-Up Enable bit

1 = D+ data line pull-up resistor is enabled

0 = D+ data line pull-up resistor is disabled

bit 6 **DMPULUP:** D- Pull-Up Enable bit

1 = D- data line pull-up resistor is enabled

0 = D- data line pull-up resistor is disabled

bit 5 **DPPULDWN:** D+ Pull-Down Enable bit

1 = D+ data line pull-down resistor is enabled

0 = D+ data line pull-down resistor is disabled

bit 4 DMPULDWN: D- Pull-Down Enable bit

1 = D- data line pull-down resistor is enabled

0 = D- data line pull-down resistor is disabled

bit 3 VBUSON: VBUS Power-on bit

1 = VBUS line is powered

0 = VBUS line is not powered

bit 2 OTGEN: OTG Functionality Enable bit

1 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under software control

0 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under USB hardware control

bit 1 VBUSCHG: VBUS Charge Enable bit

1 = VBUS line is charged through a pull-up resistor

0 = VBUS line is not charged through a resistor

bit 0 VBUSDIS: VBUS Discharge Enable bit

1 = VBUS line is discharged through a pull-down resistor

0 = VBUS line is not discharged through a resistor

## REGISTER 10-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 **PPBRST:** Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the EVEN Buffer Descriptor banks

- 0 = Even/Odd buffer pointers are not Reset

- bit 0 USBEN: USB Module Enable bit (4)

- 1 = USB module and supporting circuitry is enabled0 = USB module and supporting circuitry is disabled

- **SOFEN:** SOF Enable bit<sup>(5)</sup>

- 1 = SOF token is sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- **2:** All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

## TABLE 11-7: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| ss                          |                      |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |      |       |      |            |

|-----------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|-------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0 | All Resets |

| ED00                        | RPC8R <sup>(1)</sup> | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _     | _    | 0000       |

| FB8C                        | RPC8R**              | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPC8 | <3:0> |      | 0000       |

| ED00                        | RPC9R <sup>(3)</sup> | 31:16     | _     | _     | _     | -     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _     | _    | 0000       |

| FB90                        | RPC9R <sup>(*)</sup> | 15:0      | _     | _     | _     |       | ı     | 1     | _    | _    | _    | _    | _    | _    |      | RPC9 | <3:0> |      | 0000       |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1:

This register is only available on 44-pin devices. This register is only available on PIC32MX1XX devices. 2:

This register is only available on 36-pin and 44-pin devices.

### REGISTER 14-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                   | _                 | -                 | _                 | _                 | _                 | _                |                  |

| 00:40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                   | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          | _                   |                   | S                 | WDTPS<4:0         | >                 |                   | WDTWINEN         | WDTCLR           |

Legend:y = Values set from Configuration bits on PORR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

1 = Enables the WDT if it is not enabled by the device configuration

0 = Disable the WDT if it was enabled in software

bit 14-7 Unimplemented: Read as '0'

bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> of Configuration bits.

bit 1 WDTWINEN: Watchdog Timer Window Enable bit

1 = Enable windowed Watchdog Timer0 = Disable windowed Watchdog Timer

bit 0 WDTCLR: Watchdog Timer Reset bit

1 = Writing a '1' will clear the WDT

0 = Software cannot force this bit to a '0'

**Note 1:** A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

2: When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

## 16.1 Output Compare Control Registers

## TABLE 16-1: OUTPUT COMPARE 1-OUTPUT COMPARE 5 REGISTER MAP

| ess                         |                                 |               |         |             |           |       |       |       |      | Bi    | ts     |      |           |            |             |      |           |      | 9          |

|-----------------------------|---------------------------------|---------------|---------|-------------|-----------|-------|-------|-------|------|-------|--------|------|-----------|------------|-------------|------|-----------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14       | 29/13     | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7   | 22/6 | 21/5      | 20/4       | 19/3        | 18/2 | 17/1      | 16/0 | All Resets |

|                             | OC1CON                          | 31:16<br>15:0 | ON      |             | —<br>SIDL | _     | _     |       | _    | _     | _      | _    | —<br>OC32 | —<br>OCFLT | —<br>OCTSEL | _    | OCM<2:0>  | _    | 0000       |

| 3010                        | OC1R                            | 31:16<br>15:0 |         |             |           |       |       |       |      | OC1R- | <31:0> |      |           |            |             |      |           |      | xxxx       |

| 3020                        | OC1RS                           | 31:16<br>15:0 |         |             |           |       |       |       |      | OC1RS | <31:0> |      |           |            |             |      |           |      | xxxx       |

| 3200                        | OC2CON                          | 31:16<br>15:0 | —<br>ON | _           | —<br>SIDL | _     | _     | _     | _    | _     | _      | _    | —<br>OC32 | —<br>OCFLT | OCTSEL      | _    | OCM<2:0>  | _    | 0000       |

| 3210                        | OC2R                            | 31:16<br>15:0 |         |             |           |       |       |       |      | OC2R  | <31:0> |      |           |            |             |      |           |      | xxxx       |

| 3220                        | OC2RS                           | 31:16<br>15:0 |         | OC2RS<31:0> |           |       |       |       |      |       |        |      |           |            |             |      |           |      |            |

| 3400                        | OC3CON                          | 31:16<br>15:0 | ON      | _           | —<br>SIDL | _     | _     | _     | _    | _     | _      | _    | —<br>OC32 | —<br>OCFLT | OCTSEL      | _    | OCM<2:0>  | _    | 0000       |

| 3410                        | OC3R                            | 31:16<br>15:0 | O.V     |             | OIDE      |       |       |       |      | OC3R  |        |      | 0002      | 00.21      | 001022      |      | 00M 12.01 |      | xxxx       |

| 3420                        | OC3RS                           | 31:16<br>15:0 |         |             |           |       |       |       |      | OC3RS | <31:0> |      |           |            |             |      |           |      | xxxx       |

| 3600                        | OC4CON                          | 31:16<br>15:0 | ON      | _           | —<br>SIDL | _     | _     | _     | _    | _     | _      | _    | —<br>OC32 | —<br>OCFLT | OCTSEL      | _    | OCM<2:0>  | _    | 0000       |

| 3610                        | OC4R                            | 31:16<br>15:0 | 0.1     |             | 0.52      |       |       |       |      | OC4R  | <31:0> |      | 0002      | 00.2.      | 00.022      |      | 20 2.0    |      | xxxx       |

| 3620                        | OC4RS                           | 31:16<br>15:0 |         |             |           |       |       |       |      | OC4RS | <31:0> |      |           |            |             |      |           |      | xxxx       |

| 3800                        | OC5CON                          | 31:16<br>15:0 | ON      | _           | —<br>SIDL | _     | _     | _     | _    | _     | _      | _    | —<br>OC32 | —<br>OCFLT | OCTSEL      | _    | OCM<2:0>  | _    | 0000       |

| 3810                        | OC5R                            | 31:16<br>15:0 |         |             |           |       |       |       |      | OC5R  | <31:0> |      |           |            | ı           |      |           |      | xxxx       |

| 3820                        | OC5RS                           | 31:16<br>15:0 |         |             |           |       |       |       |      | OC5RS | <31:0> |      |           |            |             |      |           |      | xxxx       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

### REGISTER 16-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                    | _                 | _                 | _                | _                |

| 22.46        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                    | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | _                    | _                 | _                 | _                | _                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            | OCTSEL OCM<       |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Output Compare Peripheral On bit<sup>(1)</sup>

1 = Output Compare peripheral is enabled

0 = Output Compare peripheral is disabled

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Discontinue module operation when the device enters Idle mode

0 = Continue module operation when the device enters Idle mode

bit 12-6 Unimplemented: Read as '0'

bit 5 OC32: 32-bit Compare Mode bit

1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source

0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

bit 4 OCFLT: PWM Fault Condition Status bit<sup>(2)</sup>

1 = PWM Fault condition has occurred (cleared in hardware only)

0 = No PWM Fault condition has occurred

bit 3 OCTSEL: Output Compare Timer Select bit

1 = Timer3 is the clock source for this Output Compare module

0 = Timer2 is the clock source for this Output Compare module

bit 2-0 OCM<2:0>: Output Compare Mode Select bits

111 = PWM mode on OCx; Fault pin enabled

110 = PWM mode on OCx; Fault pin disabled

101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

100 = Initialize OCx pin low; generate single output pulse on OCx pin

011 = Compare event toggles OCx pin

010 = Initialize OCx pin high; compare event forces OCx pin low

001 = Initialize OCx pin low; compare event forces OCx pin high

000 = Output compare peripheral is disabled but continues to draw current

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

2: This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

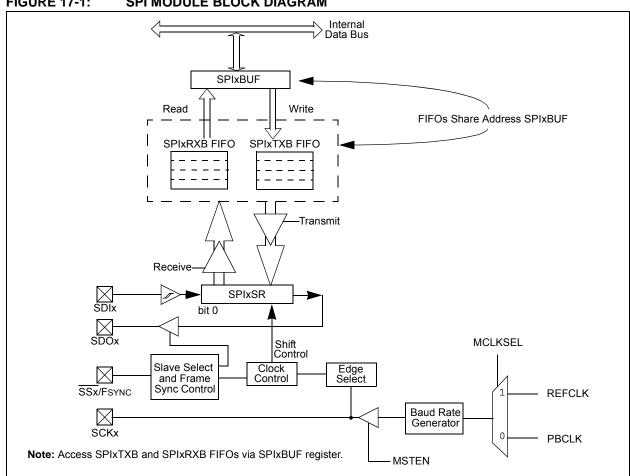

#### SERIAL PERIPHERAL 17.0 **INTERFACE (SPI)**

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial **Peripheral** Interface (SPI)" (DS60001106), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontrollers. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters (ADC), etc. The PIC32 SPI module is compatible with Motorola® SPI and SIOP interfaces.

Some of the key features of the SPI module are:

- Master mode and Slave mode support

- · Four clock formats

- Enhanced Framed SPI protocol support

- · User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

- FIFO buffers act as 4/8/16-level deep FIFOs based on 32/16/8-bit data width

- · Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- · Operation during Sleep and Idle modes

- Audio Codec Support:

- I<sup>2</sup>S protocol

- Left-justified

- Right-justified

- PCM

**FIGURE 17-1:** SPI MODULE BLOCK DIAGRAM

## REGISTER 20-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)

- bit 4 Unimplemented: Read as '0' bit 3 CS1P: Chip Select 0 Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMCS1) 0 = Active-low (PMCS1)

- bit 2 Unimplemented: Read as '0'

- bit 1 WRSP: Write Strobe Polarity bit

For Slave Modes and Master mode 2 (MODE<1:0> = 00,01,10):

- 1 = Write strobe active-high (PMWR)

- $0 = Write strobe active-low (\overline{PMWR})$

For Master mode 1 (MODE<1:0> = 11):

- 1 = Enable strobe active-high (PMENB)

- 0 = Enable strobe active-low (PMENB)

- bit 0 RDSP: Read Strobe Polarity bit

For Slave modes and Master mode 2 (MODE<1:0> = 00,01,10):

- 1 = Read Strobe active-high (PMRD)

- $0 = \text{Read Strobe active-low } (\overline{PMRD})$

For Master mode 1 (MODE<1:0> = 11):

- 1 = Read/write strobe active-high (PMRD/PMWR)

- 0 = Read/write strobe active-low (PMRD/PMWR)

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

2: These bits have no effect when their corresponding pins are used as address lines.

## REGISTER 21-2: RTCALRM: RTC ALARM CONTROL REGISTER (CONTINUED)

bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits<sup>(2)</sup>

11111111 = Alarm will trigger 256 times

•

00000000 = Alarm will trigger one time

The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1.

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

Note: This register is reset only on a Power-on Reset (POR).

# 22.1 ADC Control Registers TABLE 22-1: ADC REGISTER MAP

| ess                         |                        |           |        | Bits y                             |        |        |        |           |           |              |           |           |       |         |        |       |        |       |            |

|-----------------------------|------------------------|-----------|--------|------------------------------------|--------|--------|--------|-----------|-----------|--------------|-----------|-----------|-------|---------|--------|-------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range | 31/15  | 30/14                              | 29/13  | 28/12  | 27/11  | 26/10     | 25/9      | 24/8         | 23/7      | 22/6      | 21/5  | 20/4    | 19/3   | 18/2  | 17/1   | 16/0  | All Resets |

|                             | AD1CON1 <sup>(1)</sup> | 31:16     | _      | _                                  | 1      |        | _      | _         | _         | _            | 1         | 1         | _     | _       | _      | 1     | _      | _     | 0000       |

| 9000                        | AD ICON ICO            | 15:0      | ON     | _                                  | SIDL   |        | _      | I         | FORM<2:0  | >            |           | SSRC<2:0> | >     | CLRASAM | _      | ASAM  | SAMP   | DONE  | 0000       |

| 9010                        | AD1CON2 <sup>(1)</sup> | 31:16     |        | _                                  | _      | _      |        | _         | _         | _            | 1         |           | _     | _       | _      | _     | _      | _     | 0000       |

| 3010                        | 710 100112             | 15:0      | ,      | VCFG<2:0>                          | •      | OFFCAL | _      | CSCNA     | _         | _            | BUFS      | _         |       | SMPI    | <3:0>  |       | BUFM   | ALTS  | 0000       |

| 9020                        | AD1CON3 <sup>(1)</sup> | 31:16     | _      | _                                  | _      | _      | _      | _         | _         | _            | _         | _         | _     | _       | _      | _     | _      | _     | 0000       |

| 0020                        |                        | 15:0      | ADRC   | _                                  |        |        |        | SAMC<4:0> |           |              |           | 1         |       | ADCS    | S<7:0> |       |        |       | 0000       |

| 9040                        | AD1CHS <sup>(1)</sup>  | 31:16     | CH0NB  | _                                  |        | _      |        | CH0SI     | B<3:0>    |              | CH0NA     | _         | _     | _       |        | CH0S/ | A<3:0> |       | 0000       |

| 0010                        | 7.510110               | 15:0      | _      | _                                  | _      | _      | _      | _         | _         | _            | _         | _         | _     | _       | _      | _     | _      | _     | 0000       |

| 9050                        | AD1CSSL <sup>(1)</sup> | 31:16     | _      | _                                  |        | _      | _      | _         | _         | _            | -         | _         | _     | _       | _      | _     | _      | _     | 0000       |

| 0000                        | 710002                 | 15:0      | CSSL15 | CSSL14                             | CSSL13 | CSSL12 | CSSL11 | CSSL10    | CSSL9     | CSSL8        | CSSL7     | CSSL6     | CSSL5 | CSSL4   | CSSL3  | CSSL2 | CSSL1  | CSSL0 | 0000       |

| 9070                        | ADC1BUF0               | 31:16     |        |                                    |        |        |        |           | ADC Res   | sult Word 0  | (ADC1BUE  | 0<31:0>)  |       |         |        |       |        |       | 0000       |

| 0070                        | 7.5015010              | 15:0      |        |                                    |        |        |        |           | 7150 1101 | ouit Troid o | (7.001001 | 0 101.01  |       |         |        |       |        |       | 0000       |

| 9080                        | ADC1BUF1               | 31:16     |        | ADC Result Word 1 (ADC1BUF1<31:0>) |        |        |        |           |           |              |           |           |       |         |        |       |        |       |            |

|                             |                        | 15:0      |        | ADC Result Word 1 (ADC1BUF1<31:0>) |        |        |        |           |           |              |           |           |       |         |        |       |        |       |            |

| 9090                        | ADC1BUF2               | 31:16     |        |                                    |        |        |        |           | ADC Res   | sult Word 2  | (ADC1BUF  | 2<31:0>)  |       |         |        |       |        |       | 0000       |

|                             |                        | 15:0      |        |                                    |        |        |        |           |           |              | (         |           |       |         |        |       |        |       | 0000       |

| 90A0                        | ADC1BUF3               | 31:16     |        |                                    |        |        |        |           | ADC Res   | sult Word 3  | (ADC1BUF  | 3<31:0>)  |       |         |        |       |        |       | 0000       |

|                             |                        | 15:0      |        |                                    |        |        |        |           |           |              | (         | ,         |       |         |        |       |        |       | 0000       |

| 90B0                        | ADC1BUF4               | 31:16     |        |                                    |        |        |        |           | ADC Res   | sult Word 4  | (ADC1BUF  | 4<31:0>)  |       |         |        |       |        |       | 0000       |

|                             |                        | 15:0      |        |                                    |        |        |        |           |           |              |           |           |       |         |        |       |        |       | 0000       |

| 90C0                        | ADC1BUF5               | 31:16     |        |                                    |        |        |        |           | ADC Res   | sult Word 5  | (ADC1BUF  | 5<31:0>)  |       |         |        |       |        |       | 0000       |

|                             |                        | 15:0      |        |                                    |        |        |        |           |           |              | •         | ,         |       |         |        |       |        |       | 0000       |

| 90D0                        | ADC1BUF6               | 31:16     |        |                                    |        |        |        |           | ADC Res   | sult Word 6  | (ADC1BUF  | 6<31:0>)  |       |         |        |       |        |       | 0000       |

|                             |                        | 15:0      |        |                                    |        |        |        |           |           |              | `         |           |       |         |        |       |        |       | 0000       |

| 90E0                        | ADC1BUF7               | 31:16     |        |                                    |        |        |        |           | ADC Res   | sult Word 7  | (ADC1BUF  | 7<31:0>)  |       |         |        |       |        |       | 0000       |

|                             |                        | 15:0      |        |                                    |        |        |        |           |           |              | `         |           |       |         |        |       |        |       | 0000       |

| 90F0                        | ADC1BUF8               | 31:16     |        |                                    |        |        |        |           | ADC Res   | sult Word 8  | (ADC1BUF  | 8<31:0>)  |       |         |        |       |        |       | 0000       |

| -                           |                        | 15:0      |        |                                    |        |        |        |           |           |              | -         | ,         |       |         |        |       |        |       | 0000       |

| 9100                        | ADC1BUF9               | 31:16     |        | ADC Result Word 9 (ADC1BUF9<31:0>) |        |        |        |           |           |              |           |           |       |         |        |       |        |       |            |

|                             |                        | 15:0      |        | 0000                               |        |        |        |           |           |              |           |           |       |         |        |       |        |       |            |

| 9110                        | ADC1BUFA               | 31:16     |        | ADC Result Word A (ADC1BUFA<31:0>) |        |        |        |           |           |              |           |           |       |         |        |       |        |       |            |

|                             |                        | 15:0      |        |                                    |        |        |        |           |           |              |           |           |       |         |        |       |        |       | 0000       |

**PIC32MX1XX/2XX 28/36/44-PIN FAMILY**

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for details.

### REGISTER 22-3: AD1CON3: ADC CONTROL REGISTER 3

| Bit<br>Range | Bit<br>31/23/15/7        | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4        | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|--------------------------|-------------------|-------------------|--------------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0                      | U-0               | U-0               | U-0                      | U-0               | U-0               | U-0              | U-0              |

|              | _                        | _                 | _                 | _                        | _                 | _                 | _                | _                |

| 23:16        | U-0                      | U-0               | U-0               | U-0                      | U-0               | U-0               | U-0              | U-0              |

|              | _                        | _                 | _                 | _                        | _                 | _                 | _                | _                |

| 15:8         | R/W-0                    | U-0               | U-0               | R/W-0                    | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | ADRC                     | _                 | _                 | SAMC<4:0> <sup>(1)</sup> |                   |                   |                  |                  |

| 7:0          | R/W-0                    | R/W-0             | R/W-0             | R/W-0                    | R/W-0             | R/W-0             | R/W              | R/W-0            |

|              | ADCS<7:0> <sup>(2)</sup> |                   |                   |                          |                   |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 ADRC: ADC Conversion Clock Source bit

1 = Clock derived from FRC

0 = Clock derived from Peripheral Bus Clock (PBCLK)

bit 14-13 Unimplemented: Read as '0'

bit 12-8 **SAMC<4:0>:** Auto-Sample Time bits<sup>(1)</sup>

11111 = **31** TAD

00001 = 1 TAD

00000 = 0 TAD (Not allowed)

ADCS<7:0>: ADC Conversion Clock Select bits(2) bit 7-0

11111111 = TPB • 2 • (ADCS<7:0> + 1) = 512 • TPB = TAD

00000001 =TPB • 2 • (ADCS<7:0> + 1) = 4 • TPB = TAD 00000000 =TPB • 2 • (ADCS<7:0> + 1) = 2 • TPB = TAD

**Note 1:** This bit is only used if the SSRC<2:0> bits (AD1CON1<7:5>) = 111.

2: This bit is not used if the ADRC (AD1CON3<15>) bit = 1.

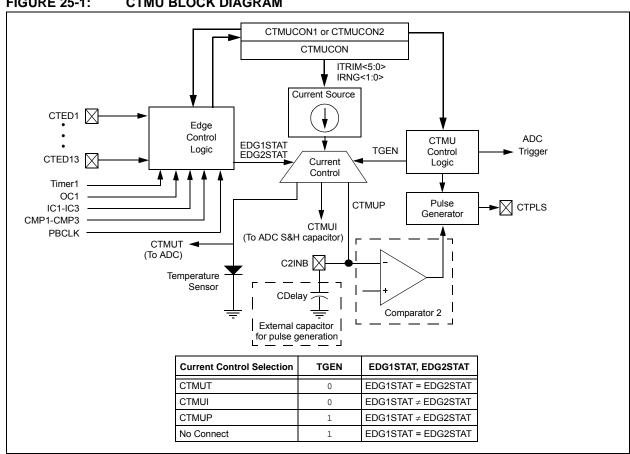

#### **CHARGE TIME** 25.0 **MEASUREMENT UNIT (CTMU)**

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Charge Time Measurement Unit (CTMU) is a flexible analog module that has a configurable current source with a digital configuration circuit built around it. The CTMU can be used for differential time measurement between pulse sources and can be used for generating an asynchronous pulse. By working with other on-chip analog modules, the CTMU can be used for high resolution time measurement, measure capacitance, measure relative changes in capacitance or generate output pulses with a specific time delay. The CTMU is ideal for interfacing with capacitive-based sensors.

The CTMU module includes the following key features:

- · Up to 13 channels available for capacitive or time measurement input

- · On-chip precision current source

- · 16-edge input trigger sources

- · Selection of edge or level-sensitive inputs

- · Polarity control for each edge source

- · Control of edge sequence

- · Control of response to edges

- High precision time measurement

- · Time delay of external or internal signal asynchronous to system clock

- · Integrated temperature sensing diode

- Control of current source during auto-sampling

- · Four current source ranges

- · Time measurement resolution of one nanosecond

A block diagram of the CTMU is shown in Figure 25-1.

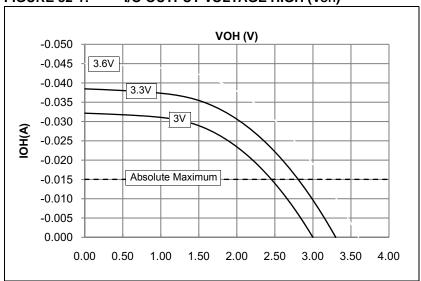

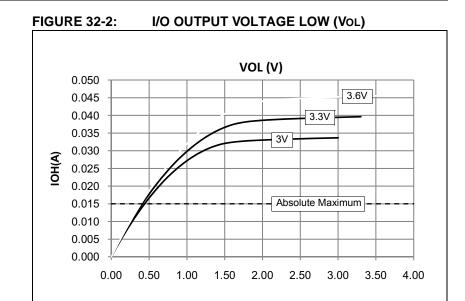

## 32.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

**Note:** The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

FIGURE 32-1: I/O OUTPUT VOLTAGE HIGH (VOH)

TABLE A-1: MAJOR SECTION UPDATES (CONTINUED)

| Section                        | Update Description                                                                                                                                                                                                                   |  |  |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 4.0 "Memory Organization"      | Added Memory Maps for the new devices (see Figure 4-3 and Figure 4-4).                                                                                                                                                               |  |  |  |  |

|                                | Removed the BMXCHEDMA bit from the Bus Matrix Register map (see Table 4-1).                                                                                                                                                          |  |  |  |  |

|                                | Added the REFOTRIM register, added the DIVSWEN bit to the REFOCON registers, added Note 4 to the ULOCK and SOSCEN bits and added the PBDIVRDY bit in the OSCCON register in the in the System Control Register map (see Table 4-16). |  |  |  |  |

|                                | Removed the ALTI2C1 and ALTI2C2 bits from the DEVCFG3 register and added Note 1 to the UPLLEN and UPLLIDIV<2:0> bits of the DEVCFG2 register in the Device Configuration Word Summary (see Table 4-17).                              |  |  |  |  |

|                                | Updated Note 1 in the Device and Revision ID Summary (see Table 4-18).                                                                                                                                                               |  |  |  |  |

|                                | Added Note 2 to the PORTA Register map (see Table 4-19).                                                                                                                                                                             |  |  |  |  |

|                                | Added the ANSB6 and ANSB12 bits to the ANSELB register in the PORTB Register map (see Table 4-20).                                                                                                                                   |  |  |  |  |

|                                | Added Notes 2 and 3 to the PORTC Register map (see Table 4-21).                                                                                                                                                                      |  |  |  |  |

|                                | Updated all register names in the Peripheral Pin Select Register map (see Table 4-23).                                                                                                                                               |  |  |  |  |

|                                | Added values in support of new devices (16 KB RAM and 32 KB RAM) in the Data RAM Size register (see Register 4-5).                                                                                                                   |  |  |  |  |

|                                | Added values in support of new devices (64 KB Flash and 128 KB Flash) in the Data RAM Size register (see Register 4-5).                                                                                                              |  |  |  |  |

| 8.0 "Oscillator Configuration" | Added Note 5 to the PIC32MX1XX/2XX Family Clock Diagram (see Figure 8-1).                                                                                                                                                            |  |  |  |  |

|                                | Added the PBDIVRDY bit and Note 2 to the Oscillator Control register (see Register 8-1).                                                                                                                                             |  |  |  |  |

|                                | Added the DIVSWEN bit and Note 3 to the Reference Oscillator Control register (see Register 8-3).                                                                                                                                    |  |  |  |  |

|                                | Added the REFOTRIM register (see Register 8-4).                                                                                                                                                                                      |  |  |  |  |

| 21.0 "10-bit Analog-to-Digital | Updated the ADC1 Module Block Diagram (see Figure 21-1).                                                                                                                                                                             |  |  |  |  |

| Converter (ADC)"               | Updated the Notes in the ADC Input Select register (see Register 21-4).                                                                                                                                                              |  |  |  |  |

| 24.0 "Charge Time Measurement  | Updated the CTMU Block Diagram (see Figure 24-1).                                                                                                                                                                                    |  |  |  |  |

| Unit (CTMU)"                   | Added Note 3 to the CTMU Control register (see Register 24-1)                                                                                                                                                                        |  |  |  |  |

| 26.0 "Special Features"        | Added Note 1 and the PGEC4/PGED4 pin pair to the ICESEL<1:0> bits in DEVCFG0: Device Configuration Word 0 (see Register 26-1).                                                                                                       |  |  |  |  |

|                                | Removed the ALTI2C1 and ALTI2C2 bits from the Device Configuration Word 3 register (see Register 26-4).                                                                                                                              |  |  |  |  |

|                                | Removed 26.3.3 "Power-up Requirements".                                                                                                                                                                                              |  |  |  |  |

|                                | Added Note 3 to the Connections for the On-Chip Regulator diagram (see Figure 26-2).                                                                                                                                                 |  |  |  |  |

|                                | Updated the Block Diagram of Programming, Debugging and Trace Ports diagram (see Figure 26-3).                                                                                                                                       |  |  |  |  |