#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 33                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx210f016dt-v-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 11: PIN NAMES FOR 44-PIN GENERAL PURPOSE DEVICES

### 44-PIN TQFP (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX110F016D PIC32MX120F032D PIC32MX130F064D PIC32MX130F256D PIC32MX150F128D PIC32MX170F256D

44

1

| Pin # | Full Pin Name                                  | Pin # | Full Pin Name                        |

|-------|------------------------------------------------|-------|--------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                       | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 |

| 2     | RPC6/PMA1/RC6                                  | 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3   |

| 3     | RPC7/PMA0/RC7                                  | 25    | AN6/RPC0/RC0                         |

| 4     | RPC8/PMA5/RC8                                  | 26    | AN7/RPC1/RC1                         |

| 5     | RPC9/CTED7/PMA6/RC9                            | 27    | AN8/RPC2/PMA2/RC2                    |

| 6     | Vss                                            | 28    | VDD                                  |

| 7     | VCAP                                           | 29    | Vss                                  |

| 8     | PGED2/RPB10/CTED11/PMD2/RB10                   | 30    | OSC1/CLKI/RPA2/RA2                   |

| 9     | PGEC2/RPB11/PMD1/RB11                          | 31    | OSC2/CLKO/RPA3/RA3                   |

| 10    | AN12/PMD0/RB12                                 | 32    | TDO/RPA8/PMA8/RA8                    |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                     | 33    | SOSCI/RPB4/RB4                       |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10           | 34    | SOSCO/RPA4/T1CK/CTED9/RA4            |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7       | 35    | TDI/RPA9/PMA9/RA9                    |

| 14    | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 | 36    | RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          | 37    | RPC4/PMA4/RC4                        |

| 16    | AVss                                           | 38    | RPC5/PMA3/RC5                        |

| 17    | AVDD                                           | 39    | Vss                                  |

| 18    | MCLR                                           | 40    | VDD                                  |

| 19    | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          | 41    | PGED3/RPB5/PMD7/RB5                  |

| 20    | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                | 42    | PGEC3/RPB6/PMD6/RB6                  |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0           | 43    | RPB7/CTED3/PMD5/INT0/RB7             |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1          | 44    | RPB8/SCL1/CTED10/PMD4/RB8            |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

5: Shaded pins are 5V tolerant.

#### 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to documents listed in the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

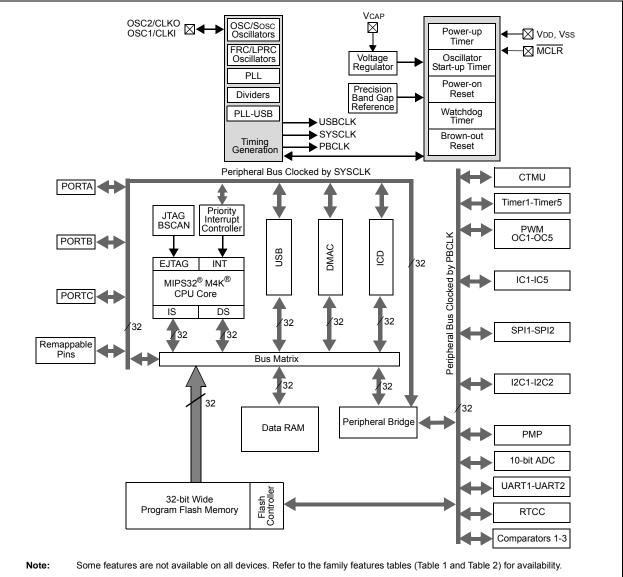

**BLOCK DIAGRAM**

This document contains device-specific information for PIC32MX1XX/2XX 28/36/44-pin Family devices.

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX1XX/2XX 28/36/44-pin Family of devices.

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

FIGURE 1-1:

|          |                        | Pin Nu                            | mber <sup>(1)</sup> | -                               |             |                |                                           |

|----------|------------------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------|-------------------------------------------|

| Pin Name | 28-pin<br>QFN          | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                               |

| OC1      | PPS                    | PPS                               | PPS                 | PPS                             | 0           |                | Output Compare Output 1                   |

| OC2      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 2                   |

| OC3      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | —              | Output Compare Output 3                   |

| OC4      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 4                   |

| OC5      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 5                   |

| OCFA     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | Output Compare Fault A Input              |

| OCFB     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | Output Compare Fault B Input              |

| INT0     | 13                     | 16                                | 17                  | 43                              | I           | ST             | External Interrupt 0                      |

| INT1     | PPS                    | PPS                               | PPS                 | PPS                             | 1           | ST             | External Interrupt 1                      |

| INT2     | PPS                    | PPS                               | PPS                 | PPS                             | 1           | ST             | External Interrupt 2                      |

| INT3     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | External Interrupt 3                      |

| INT4     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | External Interrupt 4                      |

| RA0      | 27                     | 2                                 | 33                  | 19                              | I/O         | ST             | PORTA is a bidirectional I/O port         |

| RA1      | 28                     | 3                                 | 34                  | 20                              | I/O         | ST             | -                                         |

| RA2      | 6                      | 9                                 | 7                   | 30                              | I/O         | ST             | -                                         |

| RA3      | 7                      | 10                                | 8                   | 31                              | I/O         | ST             | -                                         |

| RA4      | 9                      | 12                                | 10                  | 34                              | I/O         | ST             | -                                         |

| RA7      | _                      |                                   |                     | 13                              | I/O         | ST             | -                                         |

| RA8      |                        |                                   |                     | 32                              | I/O         | ST             | -                                         |

| RA9      | <u> </u>               |                                   | _                   | 35                              | I/O         | ST             | -                                         |

| RA10     |                        |                                   |                     | 12                              | I/O         | ST             | -                                         |

| RB0      | 1                      | 4                                 | 35                  | 21                              | I/O         | ST             | PORTB is a bidirectional I/O port         |

| RB1      | 2                      | 5                                 | 36                  | 22                              | I/O         | ST             |                                           |

| RB2      | 3                      | 6                                 | 1                   | 23                              | I/O         | ST             | -                                         |

| RB3      | 4                      | 7                                 | 2                   | 24                              | I/O         | ST             | -                                         |

| RB4      | 8                      | 11                                | 9                   | 33                              | I/O         | ST             | -                                         |

| RB5      | 11                     | 14                                | 15                  | 41                              | I/O         | ST             | -                                         |

| RB6      | 12 <sup>(2)</sup>      | 15 <sup>(2)</sup>                 | 16 <sup>(2)</sup>   | 42(2)                           | I/O         | ST             | 1                                         |

| RB7      | 13                     | 16                                | 17                  | 43                              | I/O         | ST             | 4                                         |

| RB8      | 18                     | 10                                | 18                  | 44                              | I/O         | ST             | 4                                         |

| RB9      | 15                     | 18                                | 19                  | 1                               | I/O         | ST             | 4                                         |

| RB10     | 18                     | 21                                | 24                  | 8                               | I/O         | ST             | 4                                         |

| RB11     | 10                     | 22                                | 25                  | 9                               | I/O         | ST             | 4                                         |

| RB12     | 20(2)                  | 23(2)                             | 26 <sup>(2)</sup>   | 10 <sup>(2)</sup>               | I/O         | ST             | 4                                         |

| RB13     | 21                     | 24                                | 27                  | 11                              | I/O         | ST             | 4                                         |

| RB14     | 21                     | 25                                | 28                  | 14                              | I/O         | ST             | 4                                         |

| RB15     | 23                     | 26                                | 29                  | 15                              | 1/O         | ST             | 4                                         |

|          | CMOS = C               | -                                 |                     |                                 |             |                | Analog input P = Power                    |

| Leyena.  | ST = Schm<br>TTL = TTL | itt Trigger in                    |                     |                                 |             | O = Outp       |                                           |

| Note 1:  |                        | -                                 | led for refe        | rence onlv.                     | See the     |                | grams" section for device pin availabilit |

#### DINOUT I/O DESCRIPTIONS (CONTINUED)

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

| Exception | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                               |

| DSS       | EJTAG debug single step.                                                                                                                |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                                |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                            |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                         |

| AdEL      | Fetch address alignment error.<br>Fetch reference to protected address.                                                                 |

| IBE       | Instruction fetch bus error.                                                                                                            |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                                      |

| Sys       | Execution of SYSCALL instruction.                                                                                                       |

| Вр        | Execution of BREAK instruction.                                                                                                         |

| RI        | Execution of a reserved instruction.                                                                                                    |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                           |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled.                                                                     |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                                 |

| Tr        | Execution of a trap (when trap condition is true).                                                                                      |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                           |

| AdEL      | Load address alignment error.<br>Load reference to protected address.                                                                   |

| AdES      | Store address alignment error.<br>Store to protected address.                                                                           |

| DBE       | Load or store bus error.                                                                                                                |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                            |

### TABLE 3-3: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE EXCEPTION TYPES

#### 3.3 Power Management

The MIPS M4K processor core offers many power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or Halting the clocks, which reduces system power consumption during Idle periods.

#### 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see Section 26.0 "Power-Saving Features".

### 3.4 EJTAG Debug Support

The MIPS M4K processor core provides an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the M4K core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used. NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | —                 | —                 | —                 |                   | IP03<2:0>         | IS03<1:0>         |                  |                  |  |  |

| 23:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10        | _                 | —                 |                   |                   | IP02<2:0>         |                   |                  | IS02<1:0>        |  |  |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15.0         | _                 | —                 |                   |                   | IP01<2:0>         |                   |                  | IS01<1:0>        |  |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          | _                 | _                 | _                 | IP00<2:0>         |                   |                   | IS00·            | <1:0>            |  |  |

#### REGISTER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

#### Legend:

| Logonal           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-26 IP03<2:0>: Interrupt Priority bits

- 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1 000 = Interrupt is disabled bit 25-24 IS03<1:0>: Interrupt Subpriority bits 11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1 00 = Interrupt subpriority is 0 bit 23-21 Unimplemented: Read as '0' bit 20-18 IP02<2:0>: Interrupt Priority bits 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1 000 = Interrupt is disabled bit 17-16 IS02<1:0>: Interrupt Subpriority bits 11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1 00 = Interrupt subpriority is 0 bit 15-13 Unimplemented: Read as '0' bit 12-10 IP01<2:0>: Interrupt Priority bits 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1

- 000 = Interrupt is disabled

- **Note:** This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| <b>NEGIST</b> | REGISTER 10-1. UTUTGIR. USB UTU INTERRUPT STATUS REGISTER |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|---------------|-----------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range  | Bit<br>31/23/15/7                                         | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 31:24         | U-0                                                       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24         | -                                                         | —                 | —                 | -                 | -                 | —                 | -                | —                |  |  |  |

| 23:16         | U-0                                                       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10         | -                                                         | —                 | —                 | -                 | -                 | —                 | -                | —                |  |  |  |

| 15:8          | U-0                                                       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.6          |                                                           | _                 | -                 |                   |                   | —                 |                  | —                |  |  |  |

|               | R/WC-0, HS                                                | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS        | U-0              | R/WC-0, HS       |  |  |  |

| 7:0           | IDIF                                                      | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF           | SESENDIF          |                  | VBUSVDIF         |  |  |  |

#### REGISTER 10-1: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable b  | pit                |

|-------------------|-------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIF:** ID State Change Indicator bit

- 1 = A change in the ID state was detected

- 0 = No change in the ID state was detected

- bit 6 T1MSECIF: 1 Millisecond Timer bit

- 1 = 1 millisecond timer has expired

- 0 = 1 millisecond timer has not expired

#### bit 5 LSTATEIF: Line State Stable Indicator bit

- 1 = USB line state has been stable for 1 ms, but different from last time

- 0 = USB line state has not been stable for 1 ms

- bit 4 ACTVIF: Bus Activity Indicator bit

- 1 = Activity on the D+, D-, ID or VBUS pins has caused the device to wake-up

- 0 = Activity has not been detected

- bit 3 SESVDIF: Session Valid Change Indicator bit

- 1 = VBUS voltage has dropped below the session end level

- 0 = VBUS voltage has not dropped below the session end level

- bit 2 SESENDIF: B-Device VBUS Change Indicator bit

- 1 = A change on the session end input was detected

- 0 = No change on the session end input was detected

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIF: A-Device VBUS Change Indicator bit

- 1 = A change on the session valid input was detected

- 0 = No change on the session valid input was detected

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 |                   |                   |                   | —                 |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | —                 |                   |                   | -                 | —                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | -                 | —                 | —                 | -                 | -                 | —                 | -                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | R/W-0            |

| 7:0          | IDIE              | T1MSECIE          | LSTATEIE          | ACTVIE            | SESVDIE           | SESENDIE          |                  | VBUSVDIE         |

#### REGISTER 10-2: U1OTGIE: USB OTG INTERRUPT ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIE:** ID Interrupt Enable bit

- 1 = ID interrupt is enabled

- 0 = ID interrupt is disabled

#### bit 6 T1MSECIE: 1 Millisecond Timer Interrupt Enable bit

- 1 = 1 millisecond timer interrupt is enabled

- 0 = 1 millisecond timer interrupt is disabled

#### bit 5 LSTATEIE: Line State Interrupt Enable bit

- 1 = Line state interrupt is enabled

- 0 = Line state interrupt is disabled

- bit 4 ACTVIE: Bus Activity Interrupt Enable bit

- 1 = Activity interrupt is enabled

- 0 = Activity interrupt is disabled

- bit 3 SESVDIE: Session Valid Interrupt Enable bit

- 1 = Session valid interrupt is enabled

- 0 = Session valid interrupt is disabled

- bit 2 SESENDIE: B-Device Session End Interrupt Enable bit

- 1 = B-Device session end interrupt is enabled

- 0 = B-Device session end interrupt is disabled

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIE: A-Device VBUS Valid Interrupt Enable bit

- 1 = A-Device VBUS valid interrupt is enabled

- 0 = A-Device VBUS valid interrupt is disabled

#### REGISTER 10-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 **PPBRST:** Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the EVEN Buffer Descriptor banks

- 0 = Even/Odd buffer pointers are not Reset

- bit 0 USBEN: USB Module Enable bit<sup>(4)</sup>

- 1 = USB module and supporting circuitry is enabled

- 0 = USB module and supporting circuitry is disabled

SOFEN: SOF Enable bit<sup>(5)</sup>

- 1 = SOF token is sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

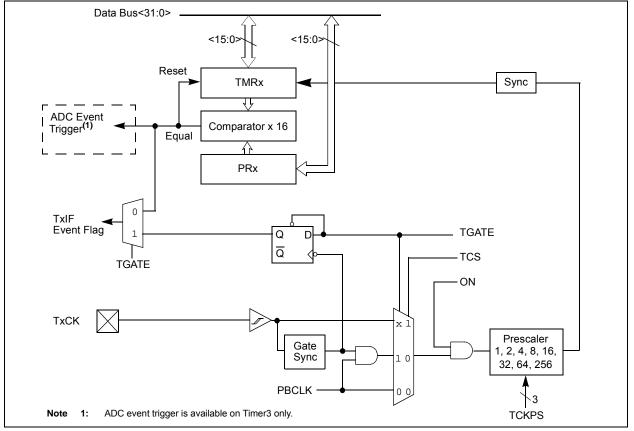

#### 13.0 TIMER2/3, TIMER4/5

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features four synchronous 16-bit timers (default) that can operate as a freerunning interval timer for various timing applications and counting external events. The following modes are supported:

- Synchronous internal 16-bit timer

- Synchronous internal 16-bit gated timer

- · Synchronous external 16-bit timer

Two 32-bit synchronous timers are available by combining Timer2 with Timer3 and Timer4 with Timer5. The 32-bit timers can operate in three modes:

- Synchronous internal 32-bit timer

- · Synchronous internal 32-bit gated timer

- Synchronous external 32-bit timer

| Note: | In this chapter, references to registers, |

|-------|-------------------------------------------|

|       | TxCON, TMRx and PRx, use 'x' to           |

|       | represent Timer2 through Timer5 in 16-bit |

|       | modes. In 32-bit modes, 'x' represents    |

|       | Timer2 or Timer4 and 'y' represents       |

|       | Timer3 or Timer5.                         |

#### **13.1 Additional Supported Features**

- · Selectable clock prescaler

- Timers operational during CPU idle

- Time base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

- ADC event trigger (Timer3 in 16-bit mode, Timer2/3 in 32-bit mode)

- Fast bit manipulation using CLR, SET and INV registers

Figure 13-1 and Figure 13-2 illustrate block diagrams of Timer2/3 and Timer4/5.

#### FIGURE 13-1: TIMER2-TIMER5 BLOCK DIAGRAM (16-BIT)

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                   | _                 | _                 | _                 | _                 | _                 | —                | _                |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                   | _                 | _                 | _                 | _                 | _                 | —                | _                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> | _                 | _                 | _                 | —                 | _                 | —                | _                |

| 7.0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          | _                   |                   | S                 | WDTWINEN          | WDTCLR            |                   |                  |                  |

#### REGISTER 14-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Configuration bits on POR       |                      |                    |  |  |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

- 1 = Enables the WDT if it is not enabled by the device configuration

- 0 = Disable the WDT if it was enabled in software

- bit 14-7 Unimplemented: Read as '0'

- bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> of Configuration bits.

- bit 1 WDTWINEN: Watchdog Timer Window Enable bit

- 1 = Enable windowed Watchdog Timer

- 0 = Disable windowed Watchdog Timer

- bit 0 **WDTCLR:** Watchdog Timer Reset bit

- 1 = Writing a '1' will clear the WDT

- 0 = Software cannot force this bit to a '0'

- **Note 1:** A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

### REGISTER 18-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | —                 | _                 | -                 | —                 |                   | _                | _                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | —                 | _                 | _                 | _                 | _                 | —                 | _                | _                |  |  |  |  |

| 45.0         | R-0, HSC          | R-0, HSC          | U-0               | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |  |  |  |  |

| 15:8         | ACKSTAT           | TRSTAT            | -                 | -                 | _                 | BCL               | GCSTAT           | ADD10            |  |  |  |  |

| 7.0          | R/C-0, HS         | R/C-0, HS         | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |  |  |  |  |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |  |  |  |  |

| Legend:           | HS = Set in hardware | HSC = Hardware set/cleared         |                   |  |

|-------------------|----------------------|------------------------------------|-------------------|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read as '0' |                   |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared               | C = Clearable bit |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 ACKSTAT: Acknowledge Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) 1 = Acknowledge was not received from slave 0 = Acknowledge was received from slave Hardware set or clear at end of slave Acknowledge. bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) 1 = Master transmit is in progress (8 bits + ACK) 0 = Master transmit is not in progress Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge. bit 13-11 Unimplemented: Read as '0' bit 10 BCL: Master Bus Collision Detect bit 1 = A bus collision has been detected during a master operation 0 = No collisionHardware set at detection of bus collision. This condition can only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module. bit 9 GCSTAT: General Call Status bit 1 = General call address was received 0 = General call address was not received Hardware set when address matches general call address. Hardware clear at Stop detection. bit 8 ADD10: 10-bit Address Status bit 1 = 10-bit address was matched 0 = 10-bit address was not matched Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.

bit 7 IWCOL: Write Collision Detect bit

| 1 = An attempt to write the I2CxTRN register failed because the I <sup>2</sup> | C module is busy |

|--------------------------------------------------------------------------------|------------------|

| 0 = No collision                                                               |                  |

Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).

- bit 6 I2COV: Receive Overflow Flag bit

- 1 = A byte was received while the I2CxRCV register is still holding the previous byte 0 = No overflow

Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

#### bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was device address

Hardware clear at device address match. Hardware set by reception of slave byte.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | _                 | —                 | -                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 |                   | —                 | —                 | -                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | IREN              | RTSMD             | _                 | UEN              | <1:0>            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL             | <1:0>            | STSEL            |

#### REGISTER 19-1: UXMODE: UARTX MODE REGISTER

#### Legend:

| Logona.                           |                  |                                    |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: UARTx Enable bit<sup>(1)</sup>

- 1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by the UEN<1:0> and UTXEN control bits.

- 0 = UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal.

- bit 14 Unimplemented: Read as '0'

#### bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

- bit 12 IREN: IrDA Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- bit 11 **RTSMD:** Mode Selection for UxRTS Pin bit

- $1 = \overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

- bit 10 Unimplemented: Read as '0'

- bit 9-8 UEN<1:0>: UARTx Enable bits

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX, UxCTS and UxRTS pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up enabled

- 0 = Wake-up disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

NOTES:

#### TABLE 30-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARA                                | CTERISTICS             | 6    | (unless other | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |             |  |  |  |

|-----------------------------------------|------------------------|------|---------------|------------------------------------------------------|-------------|--|--|--|

| Parameter<br>No.                        | Typical <sup>(3)</sup> | Max. | Units         | Conditions                                           |             |  |  |  |

| Operating Current (IDD) (Notes 1, 2, 5) |                        |      |               |                                                      |             |  |  |  |

| DC20                                    | 2                      | 3    | mA            | 4 M⊦                                                 | łz (Note 4) |  |  |  |

| DC21                                    | 7                      | 10.5 | mA            | 1                                                    | 0 MHz       |  |  |  |

| DC22                                    | 10                     | 15   | mA            | 20 MI                                                | Hz (Note 4) |  |  |  |

| DC23                                    | 15                     | 23   | mA            | 30 MHz (Note 4)                                      |             |  |  |  |

| DC24                                    | 20                     | 30   | mA            | 40 MHz                                               |             |  |  |  |

| DC25                                    | 100                    | 150  | μA            | +25°C, 3.3V LPRC (31 kHz) (Note 4)                   |             |  |  |  |

**Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

- 2: The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, Program Flash, and SRAM data memory are operational, SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- CPU executing while(1) statement from Flash

- RTCC and JTAG are disabled

- **3:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: IPD electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

|               |        | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) |                                                                                                                                                                                            |                        |            |       |                                                   |  |  |

|---------------|--------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------|-------|---------------------------------------------------|--|--|

|               |        |                                                                       | $\begin{array}{ll} \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |            |       |                                                   |  |  |

| Param.<br>No. | Symbol | Characteristics                                                       | Min.                                                                                                                                                                                       | Typical <sup>(1)</sup> | Max.       | Units | Conditions                                        |  |  |

|               | VIL    | Input Low Voltage                                                     |                                                                                                                                                                                            |                        |            |       |                                                   |  |  |

| DI10          |        | I/O Pins with PMP                                                     | Vss                                                                                                                                                                                        | —                      | 0.15 Vdd   | V     |                                                   |  |  |

|               |        | I/O Pins                                                              | Vss                                                                                                                                                                                        | —                      | 0.2 Vdd    | V     |                                                   |  |  |

| DI18          |        | SDAx, SCLx                                                            | Vss                                                                                                                                                                                        | _                      | 0.3 Vdd    | V     | SMBus disabled<br>(Note 4)                        |  |  |

| DI19          |        | SDAx, SCLx                                                            | Vss                                                                                                                                                                                        | —                      | 0.8        | V     | SMBus enabled<br>(Note 4)                         |  |  |

|               | VIH    | Input High Voltage                                                    |                                                                                                                                                                                            |                        |            |       |                                                   |  |  |

| DI20          |        | I/O Pins not 5V-tolerant <sup>(5)</sup>                               | 0.65 VDD                                                                                                                                                                                   | —                      | Vdd        | V     | (Note 4,6)                                        |  |  |

|               |        | I/O Pins 5V-tolerant with<br>PMP <sup>(5)</sup>                       | 0.25 VDD + 0.8V                                                                                                                                                                            | —                      | 5.5        | V     | (Note 4,6)                                        |  |  |

|               |        | I/O Pins 5V-tolerant <sup>(5)</sup>                                   | 0.65 VDD                                                                                                                                                                                   | —                      | 5.5        | V     |                                                   |  |  |

| DI28          |        | SDAx, SCLx                                                            | 0.65 VDD                                                                                                                                                                                   | _                      | 5.5        | V     | SMBus disabled<br>(Note 4,6)                      |  |  |

| DI29          |        | SDAx, SCLx                                                            | 2.1                                                                                                                                                                                        | _                      | 5.5        | V     | SMBus enabled,<br>2.3V ≤ VPIN ≤ 5.5<br>(Note 4,6) |  |  |

| DI30          | ICNPU  | Change Notification<br>Pull-up Current                                | _                                                                                                                                                                                          | —                      | -50        | μA    | VDD = 3.3V, VPIN = VSS<br>(Note 3,6)              |  |  |

| DI31          | ICNPD  | Change Notification<br>Pull-down Current <sup>(4)</sup>               | _                                                                                                                                                                                          | —                      | -50        | μA    | VDD = 3.3V, VPIN = VDD                            |  |  |

|               | lı∟    | Input Leakage Current<br>(Note 3)                                     |                                                                                                                                                                                            |                        |            |       |                                                   |  |  |

| DI50          |        | I/O Ports                                                             | _                                                                                                                                                                                          | _                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD$ ,<br>Pin at high-impedance |  |  |

| DI51          |        | Analog Input Pins                                                     | _                                                                                                                                                                                          | _                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance  |  |  |

| DI55          |        | MCLR <sup>(2)</sup>                                                   | —                                                                                                                                                                                          | _                      | <u>+</u> 1 | μA    | $Vss \leq V PIN \leq V DD$                        |  |  |

| DI56          |        | OSC1                                                                  | _                                                                                                                                                                                          | _                      | <u>+</u> 1 | μA    | $VSS \le VPIN \le VDD,$<br>XT and HS modes        |  |  |

#### TABLE 30-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Pin Diagrams" section for the 5V-tolerant pins.

- 6: The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

#### TABLE 30-14: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| DC CHA        |         | STICS                                                       | (unless of        | therwise | ture -40°C≤        | TA ≤ +8 | <b>o 3.6V</b><br>5°C for Industrial<br>05°C for V-temp          |

|---------------|---------|-------------------------------------------------------------|-------------------|----------|--------------------|---------|-----------------------------------------------------------------|

| Param.<br>No. | Symbol  | Characteristics                                             | Min.              | Тур.     | Max.               | Units   | Comments                                                        |

| D312          | TSET    | Internal 4-bit DAC<br>Comparator Reference<br>Settling time | _                 | _        | 10                 | μs      | See Note 1                                                      |

| D313          | DACREFH | CVREF Input Voltage                                         | AVss              | _        | AVDD               | V       | CVRSRC with CVRSS = 0                                           |

|               |         | Reference Range                                             | VREF-             | _        | VREF+              | V       | CVRSRC with CVRSS = 1                                           |

| D314          | DVREF   | CVREF Programmable<br>Output Range                          | 0                 | _        | 0.625 x<br>DACREFH | V       | 0 to 0.625 DACREFH with<br>DACREFH/24 step size                 |

|               |         |                                                             | 0.25 x<br>DACREFH | _        | 0.719 x<br>DACREFH | V       | 0.25 x DACREFH to 0.719<br>DACREFH with<br>DACREFH/32 step size |

| D315          | DACRES  | Resolution                                                  | _                 | _        | DACREFH/24         |         | CVRCON <cvrr> = 1</cvrr>                                        |

|               |         |                                                             | _                 | —        | DACREFH/32         | _       | CVRCON <cvrr> = 0</cvrr>                                        |

| D316          | DACACC  | Absolute Accuracy <sup>(2)</sup>                            |                   | _        | 1/4                | LSB     | DACREFH/24,<br>CVRCON <cvrr> = 1</cvrr>                         |

|               |         |                                                             |                   | _        | 1/2                | LSB     | DACREFH/32,<br>CVRCON <cvrr> = 0</cvrr>                         |

**Note 1:** Settling time was measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but is not tested in manufacturing.

**2:** These parameters are characterized but not tested.

#### TABLE 30-15: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHARACTERISTICS |        |                                 | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industr} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-term} \end{array}$ |    |  |       | TA $\leq$ +85°C for Industrial                                                                     |

|--------------------|--------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|-------|----------------------------------------------------------------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics                 | s Min. Typical Max                                                                                                                                                                                                                                                                 |    |  | Units | Comments                                                                                           |

| D321               | Cefc   | External Filter Capacitor Value | 8                                                                                                                                                                                                                                                                                  | 10 |  | μF    | Capacitor must be low series<br>resistance (1 ohm). Typical<br>voltage on the VCAP pin is<br>1.8V. |

NOTES:

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                          | Units            |            |      |      |  |

|--------------------------|------------------|------------|------|------|--|

| Dimensio                 | Dimension Limits |            |      | MAX  |  |

| Contact Pitch            | E                | E 1.27 BSC |      |      |  |

| Contact Pad Spacing      | С                |            | 9.40 |      |  |

| Contact Pad Width (X28)  | X                |            |      | 0.60 |  |

| Contact Pad Length (X28) | Y                |            |      | 2.00 |  |

| Distance Between Pads    | Gx               | 0.67       |      |      |  |

| Distance Between Pads    | G                | 7.40       |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

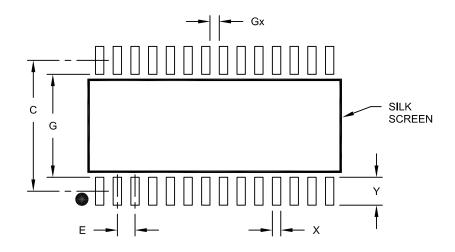

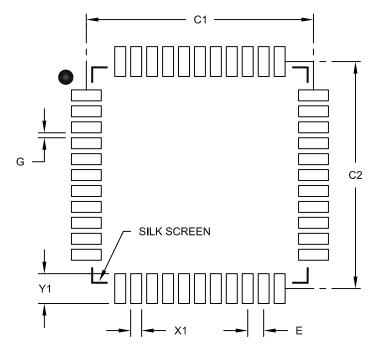

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                          | Units  |          |       |      |  |

|--------------------------|--------|----------|-------|------|--|

| Dimension                | Limits | MIN      | NOM   | MAX  |  |

| Contact Pitch            |        | 0.80 BSC |       |      |  |

| Contact Pad Spacing      | C1     |          | 11.40 |      |  |

| Contact Pad Spacing      | C2     |          | 11.40 |      |  |

| Contact Pad Width (X44)  | X1     |          |       | 0.55 |  |

| Contact Pad Length (X44) | Y1     |          |       | 1.50 |  |

| Distance Between Pads    | G      | 0.25     |       |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B