#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 19                                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx220f032b-i-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Bit<br>Range | Bit<br>31/23/15/7 | Bit Bit<br>30/22/14/6 29/21/13/5 |     | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|----------------------------------|-----|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0                              | U-0 | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | —                                | —   | —                 | —                 |                   | —                | —                |  |  |  |  |

|              | U-0               | U-0                              | U-0 | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |

| 23:16        | _                 | —                                | _   | BMX<br>ERRIXI     | BMX<br>ERRICD     | BMX<br>ERRDMA     | BMX<br>ERRDS     | BMX<br>ERRIS     |  |  |  |  |

| 45.0         | U-0               | U-0                              | U-0 | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15:8         | —                 | —                                | —   | -                 | —                 | _                 |                  | —                |  |  |  |  |

|              | U-0               | R/W-1                            | U-0 | U-0               | U-0               | R/W-0             | R/W-0            | R/W-1            |  |  |  |  |

| 7:0          | _                 | BMX<br>WSDRM                     | _   | _                 | _                 | E                 | 3MXARB<2:0       | >                |  |  |  |  |

#### REGISTER 4-1: BMXCON: BUS MATRIX CONFIGURATION REGISTER

#### Legend:

| 5                 |                  |                                    |

|-------------------|------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

#### bit 31-21 Unimplemented: Read as '0'

|          | Ommplemented. Read as 0                                                                                                                                                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 20   | BMXERRIXI: Enable Bus Error from IXI bit                                                                                                                                                                                              |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> </ul>                 |

| bit 19   | BMXERRICD: Enable Bus Error from ICD Debug Unit bit                                                                                                                                                                                   |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from ICD</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from ICD</li> </ul>                                       |

| bit 18   | BMXERRDMA: Bus Error from DMA bit                                                                                                                                                                                                     |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from DMA</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from DMA</li> </ul>                                       |

| bit 17   | BMXERRDS: Bus Error from CPU Data Access bit (disabled in Debug mode)                                                                                                                                                                 |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU data access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU data access</li> </ul>               |

| bit 16   | BMXERRIS: Bus Error from CPU Instruction Access bit (disabled in Debug mode)                                                                                                                                                          |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> </ul> |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 6    | BMXWSDRM: CPU Instruction or Data Access from Data RAM Wait State bit                                                                                                                                                                 |

|          | <ul> <li>1 = Data RAM accesses from CPU have one wait state for address setup</li> <li>0 = Data RAM accesses from CPU have zero wait states for address setup</li> </ul>                                                              |

| bit 5-3  | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 2-0  | BMXARB<2:0>: Bus Matrix Arbitration Mode bits                                                                                                                                                                                         |

|          | 111 = Reserved (using these Configuration modes will produce undefined behavior)                                                                                                                                                      |

|          | •                                                                                                                                                                                                                                     |

|          | •                                                                                                                                                                                                                                     |

|          | <ul><li>011 = Reserved (using these Configuration modes will produce undefined behavior)</li><li>010 = Arbitration Mode 2</li></ul>                                                                                                   |

|          | 001 = Arbitration Mode 1 (default)<br>000 = Arbitration Mode 0                                                                                                                                                                        |

|          |                                                                                                                                                                                                                                       |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | DCRCDATA<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.10        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | DCRCDATA<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | DCRCDATA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | DCRCDA            | TA<7:0>           |                   |                  |                  |  |  |  |  |

#### REGISTER 9-5: DCRCDATA: DMA CRC DATA REGISTER

### Legend:

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (i.e., current IP header checksum value).

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

#### REGISTER 9-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | DCRCXOR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | DCRCXOR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | DCRCXOR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | DCRCXO            | R<7:0>            |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): This register is unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = Enable the XOR input to the Shift register

- 0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

#### TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 | 0         |       |       |       |       |       |       |      |      | Bi    | ts       |       |          |        |        |           |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|-------|----------|-------|----------|--------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6     | 21/5  | 20/4     | 19/3   | 18/2   | 17/1      | 16/0     | All Resets |

| 5280                        | U1FRML <sup>(3)</sup>           | 31:16     | _     | —     | —     | —     | _     | _     | _    | _    | _     | —        | _     | —        | _      | _      | _         | —        | 0000       |

| 5200                        |                                 | 15:0      | _     | —     | _     | _     | —     | _     | —    | _    |       |          |       | FRML<    | 7:0>   |        |           |          | 0000       |

| 5290                        | U1FRMH <sup>(3)</sup>           | 31:16     | _     | —     | —     | —     |       | —     | —    | _    |       | —        |       | —        | —      | —      | _         | —        | 0000       |

| 52.50                       | OTTRAIT                         | 15:0      | _     | —     | —     | —     | —     | —     | —    |      |       | —        |       | _        | —      |        | FRMH<2:0> | >        | 0000       |

| 52A0                        | U1TOK                           | 31:16     | _     | —     | —     | —     |       | —     | —    | _    |       | —        | _     | _        | —      | —      | _         | —        | 0000       |

| 5270                        | UTTOR                           | 15:0      | _     | —     | —     | —     | —     | —     | —    |      |       | PID      | <3:0> |          |        | EP     | <3:0>     | -        | 0000       |

| 52B0                        | U1SOF                           | 31:16     | —     | —     |       |       | —     |       |      | _    | _     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 5260                        | 0130F                           | 15:0      | —     |       |       | _     | _     |       | _    |      |       |          |       | CNT<7    | /:0>   |        | -         | •        | 0000       |

| 52C0                        | U1BDTP2                         | 31:16     | _     | —     |       | _     |       |       | _    | _    | _     | —        | _     | —        | —      | _      | _         | —        | 0000       |

| 5200                        | OIBDIF2                         | 15:0      | _     | —     |       | _     |       |       | _    | _    |       |          |       | BDTPTR   | H<7:0> |        |           |          | 0000       |

| 52D0                        | U1BDTP3                         | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    | _     | —        | _     | _        | —      | —      | —         | —        | 0000       |

| 5200                        | OIBDIF3                         | 15:0      | _     | —     |       | _     |       |       | _    | _    |       |          |       | BDTPTRI  | J<7:0> |        |           |          | 0000       |

| 52E0                        | 52E0 U1CNFG1 3                  | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    | _     | —        | _     | _        | —      | —      | —         | —        | 0000       |

| 5210                        | UTCNI UT                        | 15:0      | _     | _     | —     | —     | —     | —     | —    | _    | UTEYE | UOEMON   |       | USBSIDL  | —      | —      | _         | UASUSPND | 0001       |

| 5300                        | U1EP0                           | 31:16     | _     | _     | —     | —     | —     | —     | —    | _    |       | —        |       | _        | —      | —      | _         | —        | 0000       |

| 5500                        | UIEI U                          | 15:0      | _     | _     | —     | —     | —     | —     | —    | _    | LSPD  | RETRYDIS |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5310                        | U1EP1                           | 31:16     | _     | _     | —     | —     | —     | —     | —    | _    |       | —        |       | _        | —      | —      | _         | —        | 0000       |

| 5510                        | UIEI I                          | 15:0      | _     | _     | —     | —     | —     | —     | —    | _    |       | —        |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5320                        | U1EP2                           | 31:16     | —     | —     | _     | _     | —     | _     | —    | _    | —     | —        | —     | _        | —      | _      | —         | —        | 0000       |

| 0020                        | OTET 2                          | 15:0      | _     | —     |       | —     | —     |       | —    | —    |       | —        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5330                        | U1EP3                           | 31:16     | _     | —     |       | —     | —     | —     | —    |      |       | —        | _     | _        | —      | —      |           | —        | 0000       |

| 0000                        | UTER 0                          | 15:0      | _     | —     |       | —     | —     |       | —    | —    |       | —        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5340                        | U1EP4                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      |           | —        | 0000       |

| 0010                        | 01EFT                           | 15:0      | —     | —     | —     | —     | —     |       | —    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5350                        | U1EP5                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 0000                        | 01EI 0                          | 15:0      | —     | —     | —     | —     | —     |       | —    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5360                        | U1EP6                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 0000                        | 0.2.0                           | 15:0      | _     | _     | _     | _     |       |       |      |      | _     | —        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5370                        | U1EP7                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      |           | —        | 0000       |

| 3070                        | 01217                           | 15:0      | —     | —     | —     | —     | —     | —     | —    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5380                        | U1EP8                           | 31:16     | _     | —     | —     | —     |       |       | —    | _    | _     | —        | _     | _        | —      | —      | —         | —        | 0000       |

| 5500                        | UILI U                          | 15:0      | —     | -     | _     | _     | —     | _     | _    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit Bit<br>30/22/14/6 29/21/13/ |                      | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|---------------------------------|----------------------|----------------------|-------------------|-------------------|------------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0                             | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |  |  |

| 31.24        | —                 | -                               | —                    | -                    | —                 | —                 | _                      | -                |  |  |  |

| 23:16        | U-0               | U-0                             | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |  |  |

| 23.10        | —                 | —                               | —                    | —                    | —                 | —                 | —                      | —                |  |  |  |

| 15:8         | U-0               | U-0                             | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |  |  |

| 15.0         | —                 | -                               | —                    | -                    | —                 | —                 | -                      | -                |  |  |  |

|              | R/WC-0, HS        | R/WC-0, HS                      | R/WC-0, HS           | R/WC-0, HS           | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS             | R/WC-0, HS       |  |  |  |

| 7:0          | BTSEF             | BMXEF                           | DMAEF <sup>(1)</sup> | BTOEF <sup>(2)</sup> | DFN8EF            | CRC16EF           | CRC5EF <sup>(4)</sup>  | PIDEF            |  |  |  |

|              | DISEF             | DIVIALE                         | DIVIALLY             | BIVEF                | DINOLF            | GIVE IDEF         | EOFEF <sup>(3,5)</sup> |                  |  |  |  |

#### REGISTER 10-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear HS = Hardware Settable bit |                           |                    |  |  |  |

|-------------------|----------------------------------------------------|---------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                                   | U = Unimplemented bit, re | ead as '0'         |  |  |  |

| -n = Value at POR | '1' = Bit is set                                   | '0' = Bit is cleared      | x = Bit is unknown |  |  |  |

- bit 31-8 Unimplemented: Read as '0'

- bit 7 BTSEF: Bit Stuff Error Flag bit

- 1 = Packet rejected due to bit stuff error

- 0 = Packet accepted

- bit 6 BMXEF: Bus Matrix Error Flag bit

- 1 = The base address, of the Buffer Descriptor Table, or the address of an individual buffer pointed to by a Buffer Descriptor Table entry, is invalid.

- 0 = No address error

- bit 5 DMAEF: DMA Error Flag bit<sup>(1)</sup>

- 1 = USB DMA error condition detected

- 0 = No DMA error

- bit 4 BTOEF: Bus Turnaround Time-Out Error Flag bit<sup>(2)</sup>

- 1 = Bus turnaround time-out has occurred

- 0 = No bus turnaround time-out

- bit 3 **DFN8EF:** Data Field Size Error Flag bit

- 1 = Data field received is not an integral number of bytes

- 0 = Data field received is an integral number of bytes

- bit 2 CRC16EF: CRC16 Failure Flag bit

- 1 = Data packet rejected due to CRC16 error

- 0 = Data packet accepted

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- **2:** This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0         | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          | —                 | —                 | _                 | —                 | —                 |                   | FRMH<2:0>        |                  |  |  |  |

#### REGISTER 10-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

#### Legend:

| 0                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-3 Unimplemented: Read as '0'

bit 2-0 **FRMH<2:0>:** The Upper 3 bits of the Frame Numbers bits The register bits are updated with the current frame number whenever a SOF TOKEN is received.

#### Bit Bit Bit Bit Bit Bit Bit Bit Bit 30/22/14/6 27/19/11/3 26/18/10/2 25/17/9/1 24/16/8/0 Range 31/23/15/7 29/21/13/5 28/20/12/4 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 31:24 \_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 23:16 \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 15:8 \_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 7:0 PID < 3:0 > (1)EP<3:0>

#### **REGISTER 10-15: U1TOK: USB TOKEN REGISTER**

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-4 **PID<3:0>:** Token Type Indicator bits<sup>(1)</sup>

1101 = SETUP (TX) token type transaction

- 1001 = IN (RX) token type transaction

- 0001 = OUT (TX) token type transaction

Note: All other values are reserved and must not be used.

bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits The four bit value must specify a valid endpoint.

Note 1: All other values are reserved and must not be used.

#### TABLE 11-6: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| ssa                         |                  |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |       |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| FA04                        | INT1R            | 31:16     |       | _     |       |       | _     | _     |      |      |      | _    |      |      |      | _     | _      |      | 0000       |

| FA04                        |                  | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | INT1F | R<3:0> |      | 0000       |

| FA08                        | INT2R            | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | _     | —      | —    | 0000       |

| FAUO                        | INTZR            | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | INT2F | R<3:0> |      | 0000       |

| FA0C                        | INT3R            | 31:16     | _     | _     | _     | _     | —     | —     | _    | _    | —    | _    |      | —    | _    |       | —      | —    | 0000       |

| FAUC                        | IN I 3R          | 15:0      |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | INT3F | R<3:0> |      | 0000       |

| 5440                        |                  | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | -    | 0000       |

| FA10                        | INT4R            | 15:0      | -     | _     | _     | _     | -     | -     | _    | _    | _    | _    | _    | _    |      | INT4F | R<3:0> |      | 0000       |

| 5440                        | TAOKA            | 31:16     | _     | _     | _     | _     | —     | —     | _    | _    | _    | _    | _    | _    | _    | _     | _      | —    | 0000       |

| FA18                        | T2CKR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T2CK  | R<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    |      | _    | _    |       | _      | _    | 0000       |

| FA1C                        | T3CKR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    |      | _    |      | T3CK  | R<3:0> | •    | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    |      | _    | _    |       | _      | _    | 0000       |

| FA20                        | T4CKR            | 15:0      | _     |       | _     |       | _     | _     | _    | _    | _    |      |      | _    |      | T4CK  | R<3:0> | •    | 0000       |

|                             |                  | 31:16     | _     |       | _     |       | _     | _     | _    | _    | _    |      |      | _    | _    |       | _      | _    | 0000       |

| FA24                        | T5CKR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T5CK  | R<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |       | —      | _    | 0000       |

| FA28                        | IC1R             | 15:0      | _     | _     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    |      | IC1R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      | _    | _     | _      | _    | 0000       |

| FA2C                        | IC2R             | 15:0      | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      |      | IC2R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    |      | _     | _      | _    | 0000       |

| FA30                        | IC3R             | 15:0      | _     | _     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    |      | IC3R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      | _    | _     | _      | _    | 0000       |

| FA34                        | IC4R             | 15:0      | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      |      | IC4R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      | _    | _     | _      | _    | 0000       |

| FA38                        | IC5R             | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | IC5R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     | _     |       |       | _     | _     |      | _    | _    | _    | _    | _    |      | _     |        | _    | 0000       |

| FA48                        | OCFAR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | OCFA  | R<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FA4C                        | OCFBR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | OCFB  | R<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FA50                        | U1RXR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U1RX  | R<3:0> |      | 0000       |

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### REGISTER 12-1: T1CON: TYPE A TIMER CONTROL REGISTER (CONTINUED)

- bit 3 Unimplemented: Read as '0'

bit 2 TSYNC: Timer External Clock Input Synchronization Selection bit When TCS = 1: 1 = External clock input is synchronized 0 = External clock input is not synchronized When TCS = 0: This bit is ignored.

bit 1 TCS: Timer Clock Source Select bit 1 = External clock from TxCKI pin

- 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCmLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

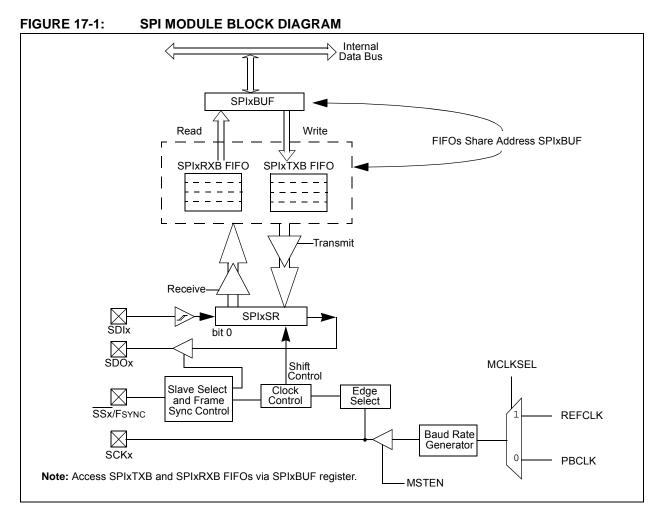

### 17.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS60001106), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontrollers. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters (ADC), etc. The PIC32 SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces. Some of the key features of the SPI module are:

- Master mode and Slave mode support

- Four clock formats

- Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

FIFO buffers act as 4/8/16-level deep FIFOs based on 32/16/8-bit data width

- Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- · Operation during Sleep and Idle modes

- Audio Codec Support:

- I<sup>2</sup>S protocol

- Left-justified

- Right-justified

- PCM

#### 21.1 RTCC Control Registers

#### TABLE 21-1: RTCC REGISTER MAP

| ess                         |                                 | ē         |        |       |          |                      |                                  |       |                   |      | Bits     |          |           |         |         |         |            |       | ŝ          |

|-----------------------------|---------------------------------|-----------|--------|-------|----------|----------------------|----------------------------------|-------|-------------------|------|----------|----------|-----------|---------|---------|---------|------------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15  | 30/14 | 29/13    | 28/12                | 27/11                            | 26/10 | 25/9              | 24/8 | 23/7     | 22/6     | 21/5      | 20/4    | 19/3    | 18/2    | 17/1       | 16/0  | All Resets |

| 0200                        | RTCCON                          | 31:16     | _      | _     | —        | —                    | —                                | —     |                   |      |          |          | CAL<      | <9:0>   |         |         |            |       | 0000       |

| 0200                        | RICCON                          | 15:0      | ON     | _     | SIDL     | —                    | —                                | —     |                   | —    | RTSECSEL | RTCCLKON | —         |         | RTCWREN | RTCSYNC | HALFSEC    | RTCOE | 0000       |

| 0210                        | RTCALRM                         | 31:16     | —      |       |          | —                    |                                  |       |                   |      | _        | —        | 0000      |         |         |         |            |       |            |

| 0210                        | RICALIN                         | 15:0      | ALRMEN | CHIME | PIV      | ALRMSYNC             |                                  | AMASI | <b>&lt;</b> <3:0> |      |          |          |           | ARPT    | <7:0>   |         |            |       | 0000       |

| 0220                        | RTCTIME                         | 31:16     | —      | _     | HR1      | 0<1:0>               |                                  | HR01  | <3:0>             |      | —        | М        | IN10<2:0> |         |         | MIN01   | <3:0>      |       | xxxx       |

| 0220                        |                                 | 15:0      | —      |       | SEC10<2: | 0>                   |                                  | SEC07 | 1<3:0>            |      | —        | —        | —         | -       | _       | _       | —          | —     | xx00       |

| 0230                        | RTCDATE                         | 31:16     |        | YEAR  | 10<3:0>  |                      |                                  | YEAR0 | 1<3:0>            |      | —        | —        | —         | MONTH10 |         | MONTH   | 01<3:0>    |       | xxxx       |

| 0230                        | RICDAIL                         | 15:0      | _      | _     | DAY      | 10<1:0>              |                                  | DAY01 | 1<3:0>            |      | —        | —        | —         |         | _       | W       | /DAY01<2:0 | >     | xx00       |

| 0240                        | ALRMTIME                        | 31:16     | _      |       | HR1      | 0<1:0>               |                                  | HR01  | <3:0>             |      | _        | М        | IN10<2:0> |         |         | MIN01   | <3:0>      |       | xxxx       |

| 0240                        |                                 | 15:0      | —      |       | SEC10<2: | 0>                   | SEC01<3:0>                       |       |                   |      |          | —        | xx00      |         |         |         |            |       |            |

| 0250                        | ALRMDATE                        | 31:16     | _      | _     | _        | MONTH10 MONTH01<3:0> |                                  |       |                   |      | 00xx     |          |           |         |         |         |            |       |            |

| 0250                        | ALNIUATE                        | 15:0      |        | DAY1  | 0<3:0>   |                      | DAY01<3:0> — — — — — WDAY01<2:0> |       |                   |      |          |          | xx0x      |         |         |         |            |       |            |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### REGISTER 21-1: RTCCON: RTC CONTROL REGISTER (CONTINUED)

- bit 5-4 **Unimplemented:** Read as '0'

- bit 3 RTCWREN: RTC Value Registers Write Enable bit<sup>(4)</sup>

- 1 = RTC Value registers can be written to by the user

- 0 = RTC Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: RTCC Value Registers Read Synchronization bit

- 1 = RTC Value registers can change while reading, due to a rollover ripple that results in an invalid data read

If the register is read twice and results in the same data, the data can be assumed to be valid

- 0 = RTC Value registers can be read without concern about a rollover ripple

- bit 1 HALFSEC: Half-Second Status bit<sup>(5)</sup>

- 1 = Second half period of a second

- 0 = First half period of a second

- bit 0 **RTCOE:** RTCC Output Enable bit

- 1 = RTCC clock output enabled clock presented onto an I/O

- 0 = RTCC clock output disabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **3:** Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- 4: The RTCWREN bit can be set only when the write sequence is enabled.

- 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

Note: This register is reset only on a Power-on Reset (POR).

#### REGISTER 21-2: RTCALRM: RTC ALARM CONTROL REGISTER (CONTINUED)

bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits<sup>(2)</sup> 11111111 = Alarm will trigger 256 times

> 00000000 = Alarm will trigger one time The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1.

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

Note: This register is reset only on a Power-on Reset (POR).

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0                 | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        | HR10<1:0> HR01<3:0> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | U-0                 | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        |                     |                   | MIN10<2:0>        |                   |                   | MIN01<3:0>        |                  |                  |  |  |  |

| 45.0         | U-0                 | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         |                     |                   | SEC10<2:0>        |                   |                   | SEC01             | <3:0>            |                  |  |  |  |

| 7.0          | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 7:0          | _                   | _                 | —                 | —                 | —                 | _                 | —                | —                |  |  |  |

|              |                     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| Leaend:      |                     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 21-5: ALRMTIME: ALARM TIME VALUE REGISTER

# R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary Coded Decimal value of hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 **HR01<3:0>:** Binary Coded Decimal value of hours bits, 1s place digit; contains a value from 0 to 9 bit 23 **Unimplemented:** Read as '0'

bit 22-20 MIN10<2:0>: Binary Coded Decimal value of minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 **MIN01<3:0>:** Binary Coded Decimal value of minutes bits, 1s place digit; contains a value from 0 to 9 bit 15 **Unimplemented:** Read as '0'

bit 14-12 SEC10<2:0>: Binary Coded Decimal value of seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 **SEC01<3:0>:** Binary Coded Decimal value of seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

#### 23.1 Comparator Control Registers

#### TABLE 23-1: COMPARATOR REGISTER MAP

| ess                         |                                 | 0         |       |       |       |       |       |       |      | Bi   | its  |        |      |      |      |       |       |       |           |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------|------|------|------|-------|-------|-------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2  | 17/1  | 16/0  | All Reset |

| 4000                        | CM1CON                          | 31:16     | _     | _     | -     | _     | -     | _     |      | -    | —    | _      | -    | —    | —    | —     | _     | —     | 0000      |

| A000                        | CIVITCON                        | 15:0      | ON    | COE   | CPOL  | _     | -     | _     | _    | COUT | EVPO | L<1:0> | -    | CREF | _    | —     | CCH   | <1:0> | 00C3      |

| A010                        | CM2CON                          | 31:16     | _     | _     |       | _     |       | _     |      |      | _    | _      |      | _    | _    | _     | _     | _     | 0000      |

| 7010                        | CIVIZCON                        | 15:0      | ON    | COE   | CPOL  |       | -     |       | -    | COUT | EVPO | L<1:0> | -    | CREF | —    | —     | CCH   | <1:0> | 00C3      |

| A020                        | CM3CON                          | 31:16     | -     |       |       |       | -     |       | -    | -    | —    | —      | -    | _    | —    | —     |       | —     | 0000      |

| A020                        | CIVISCON                        | 15:0      | ON    | COE   | CPOL  | _     | —     | _     | —    | COUT | EVPO | L<1:0> | —    | CREF | _    | —     | CCH   | <1:0> | 00C3      |

| A060                        | CMSTAT                          | 31:16     | _     | —     | _     | _     | -     | _     | _    |      | —    | _      | _    | _    | _    | —     | _     | —     | 0000      |

| 7000                        | CIVISTAI                        | 15:0      | _     | _     | SIDL  | _     |       | _     |      |      | -    | _      |      | _    | -    | C3OUT | C2OUT | C10UT | 0000      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### 28.0 INSTRUCTION SET

The PIC32MX1XX/2XX family instruction set complies with the MIPS32<sup>®</sup> Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- · Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

**Note:** Refer to *"MIPS32<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set"* at www.imgtec.com for more information.

| DC CHA        | RACTERIS               | TICS         |            | ig temperature - | <b>litions: 2.3V to 3.6V (unless otherwise stated)</b><br>$40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |

|---------------|------------------------|--------------|------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No. | Typical <sup>(2)</sup> | Max.         | Units      |                  | Conditions                                                                                                                                                          |

| Power-D       | own Curre              | nt (IPD) (No | otes 1, 5) |                  |                                                                                                                                                                     |

| DC40k         | 44                     | 70           | μA         | -40°C            |                                                                                                                                                                     |

| DC40I         | 44                     | 70           | μA         | +25°C            | Base Power-Down Current                                                                                                                                             |

| DC40n         | 168                    | 259          | μA         | +85°C            |                                                                                                                                                                     |

| DC40m         | 335                    | 536          | μA         | +105°C           |                                                                                                                                                                     |

| Module        | Differential           | Current      |            |                  |                                                                                                                                                                     |

| DC41e         | 5                      | 20           | μA         | 3.6V             | Watchdog Timer Current: AIWDT (Note 3)                                                                                                                              |

| DC42e         | 23                     | 50           | μA         | 3.6V             | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3)                                                                                                                     |

| DC43d         | 1000                   | 1100         | μA         | 3.6V             | ADC: ΔIADC (Notes 3,4)                                                                                                                                              |

#### TABLE 30-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** The test conditions for IPD current measurements are as follows:

Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

OSC2/CLKO is configured as an I/O input pin

• USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

• CPU is in Sleep mode, and SRAM data memory Wait states = 1

• No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set

• WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

• All I/O pins are configured as inputs and pulled to Vss

• MCLR = VDD

• RTCC and JTAG are disabled

2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

- 5: IPD electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

| DC CHA        |        | STICS                                                     | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 4): 2.3V for a stated) \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Indus} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temperature} \end{array}$ |         |      |       |                                                                                         |  |  |

|---------------|--------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|-----------------------------------------------------------------------------------------|--|--|

| Param.<br>No. | Symbol | Characteristics                                           | Min.                                                                                                                                                                                                                                                            | Typical | Max. | Units | Comments                                                                                |  |  |

| D300          | VIOFF  | Input Offset Voltage                                      | -                                                                                                                                                                                                                                                               | ±7.5    | ±25  | mV    | AVDD = VDD,<br>AVSS = VSS                                                               |  |  |

| D301          | VICM   | Input Common Mode Voltage                                 | 0                                                                                                                                                                                                                                                               | -       | Vdd  | V     | AVDD = VDD,<br>AVss = Vss<br>(Note 2)                                                   |  |  |

| D302          | CMRR   | Common Mode Rejection Ratio                               | 55                                                                                                                                                                                                                                                              | —       | _    | dB    | Max VICM = (VDD - 1)V<br>(Note 2)                                                       |  |  |

| D303A         | Tresp  | Large Signal Response Time                                | _                                                                                                                                                                                                                                                               | 150     | 400  | ns    | AVDD = VDD, AVSS = VSS<br>(Note 1,2)                                                    |  |  |

| D303B         | TSRESP | Small Signal Response Time                                | -                                                                                                                                                                                                                                                               | 1       | _    | μS    | This is defined as an input<br>step of 50 mV with 15 mV<br>of overdrive <b>(Note 2)</b> |  |  |

| D304          | ON2ov  | Comparator Enabled to Output<br>Valid                     | _                                                                                                                                                                                                                                                               | _       | 10   | μs    | Comparator module is<br>configured before setting<br>the comparator ON bit<br>(Note 2)  |  |  |

| D305          | IVREF  | Internal Voltage Reference                                | 1.14                                                                                                                                                                                                                                                            | 1.2     | 1.26 | V     | _                                                                                       |  |  |

| D312          | TSET   | Internal Comparator Voltage<br>DRC Reference Setting time | _                                                                                                                                                                                                                                                               | —       | 10   | μs    | (Note 3)                                                                                |  |  |

#### TABLE 30-13: COMPARATOR SPECIFICATIONS

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

**2:** These parameters are characterized but not tested.

**3:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

**4:** The Comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

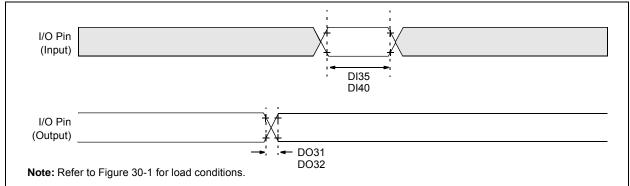

#### FIGURE 30-3: I/O TIMING CHARACTERISTICS

#### TABLE 30-21: I/O TIMING REQUIREMENTS

| AC CHAP       | RACTERIS | STICS                | Standard Ope<br>(unless other<br>Operating tem | wise state |                        | ≤ +85°C fc | or Industria |            |

|---------------|----------|----------------------|------------------------------------------------|------------|------------------------|------------|--------------|------------|

| Param.<br>No. | Symbol   | Characteris          | stics <sup>(2)</sup>                           | Min.       | Typical <sup>(1)</sup> | Max.       | Units        | Conditions |

| DO31          | TIOR     | Port Output Rise Tir | ne                                             |            | 5                      | 15         | ns           | Vdd < 2.5V |

|               |          |                      |                                                |            | 5                      | 10         | ns           | Vdd > 2.5V |

| DO32          | TIOF     | Port Output Fall Tim | е                                              | _          | 5                      | 15         | ns           | Vdd < 2.5V |

|               |          |                      |                                                |            | 5                      | 10         | ns           | VDD > 2.5V |

| DI35          | Tinp     | INTx Pin High or Lo  | w Time                                         | 10         | _                      | _          | ns           | _          |

| DI40          | Trbp     | CNx High or Low Tir  | me (input)                                     | 2          | _                      |            | TSYSCLK      |            |

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: This parameter is characterized, but not tested in manufacturing.

#### TABLE 31-8:SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| АС СНА        | ARACTERIS | TICS                                                   | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |      |      |       |            |  |  |  |

|---------------|-----------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|--|--|--|

| Param.<br>No. | Symbol    | Characteristics                                        | Min.                                                                                                                                                                                                          | Тур. | Max. | Units | Conditions |  |  |  |

| MSP70         | TscL      | SCKx Input Low Time (Note 1,2)                         | Tsck/2                                                                                                                                                                                                        |      | _    | ns    | _          |  |  |  |

| MSP71         | TscH      | SCKx Input High Time (Note 1,2)                        | Tsck/2                                                                                                                                                                                                        | —    |      | ns    | —          |  |  |  |

| MSP51         | TssH2doZ  | SSx ↑ to SDOx Output<br>High-Impedance <b>(Note 2)</b> | 5                                                                                                                                                                                                             |      | 25   | ns    | —          |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns.

#### TABLE 31-9: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        | RACTERIS | TICS                           | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industria |         |      |       |            |  |  |  |

|---------------|----------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|--|--|

| Param.<br>No. | Symbol   | Characteristics                | Min.                                                                                                                                                | Typical | Max. | Units | Conditions |  |  |  |

| SP70          | TscL     | SCKx Input Low Time (Note 1,2) | Tsck/2                                                                                                                                              |         |      | ns    |            |  |  |  |

| SP71          | TscH     | Tsck/2                         | _                                                                                                                                                   | _       | ns   | —     |            |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns.

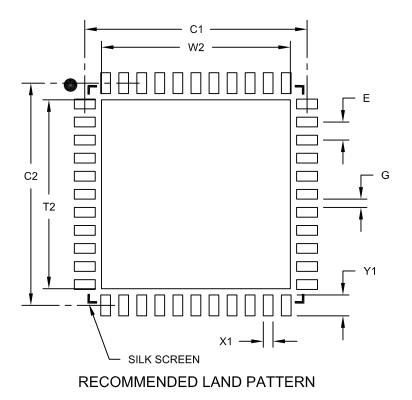

#### 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |      |          |      |  |

|----------------------------|-------------|------|----------|------|--|

| Dimensior                  | MIN         | NOM  | MAX      |      |  |

| Contact Pitch              | E           |      | 0.65 BSC |      |  |

| Optional Center Pad Width  | W2          |      |          | 6.80 |  |

| Optional Center Pad Length | T2          |      |          | 6.80 |  |

| Contact Pad Spacing        | C1          |      | 8.00     |      |  |

| Contact Pad Spacing        | C2          |      | 8.00     |      |  |

| Contact Pad Width (X44)    | X1          |      |          | 0.35 |  |

| Contact Pad Length (X44)   | Y1          |      |          | 0.80 |  |

| Distance Between Pads      | G           | 0.25 |          |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103A

NOTES: