#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 19                                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx220f032b-v-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 8: **PIN NAMES FOR 36-PIN USB DEVICES**

# 36-PIN VTLA (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX210F016C

|       | PIC32MX220F032C<br>PIC32MX230F064C<br>PIC32MX250F128C |       |                                                  |

|-------|-------------------------------------------------------|-------|--------------------------------------------------|

|       |                                                       |       | 36                                               |

|       |                                                       |       | 1                                                |

| Pin # | Full Pin Name                                         | Pin # | Full Pin Name                                    |

| 1     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2             | 19    | TDO/RPB9/SDA1/CTED4/PMD3/RB9                     |

| 2     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3               | 20    | RPC9/CTED7/RC9                                   |

| 3     | PGED4 <sup>(4)</sup> /AN6/RPC0/RC0                    | 21    | Vss                                              |

| 4     | PGEC4 <sup>(4)</sup> /AN7/RPC1/RC1                    | 22    | VCAP                                             |

| 5     | VDD                                                   | 23    | VDD                                              |

| 6     | Vss                                                   | 24    | PGED2/RPB10/D+/CTED11/RB10                       |

| 7     | OSC1/CLKI/RPA2/RA2                                    | 25    | PGEC2/RPB11/D-/RB11                              |

| 8     | OSC2/CLKO/RPA3/PMA0/RA3                               | 26    | VUSB3V3                                          |

| 9     | SOSCI/RPB4/RB4                                        | 27    | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 10    | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4                        | 28    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 11    | AN12/RPC3/RC3                                         | 29    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 12    | Vss                                                   | 30    | AVss                                             |

| 13    | Vdd                                                   | 31    | AVdd                                             |

| 14    | VDD                                                   | 32    | MCLR                                             |

| 15    | TMS/RPB5/USBID/RB5                                    | 33    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 16    | VBUS                                                  | 34    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

| 17    | TDI/RPB7/CTED3/PMD5/INT0/RB7                          | 35    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        |

| 18    | TCK/RP88/SCL1/CTED10/PM04/RB8                         | 36    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       |

Note The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin 1: Select" for restrictions.

Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information. 2:

The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally. 3:

4: This pin function is not available on PIC32MX210F016C and PIC32MX120F032C devices.

5: Shaded pins are 5V tolerant.

# 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUs

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

# 2.1 Basic Connection Requirements

Getting started with the PIC32MX1XX/2XX 28/36/44pin Family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes (see **2.5** "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.7 "External Oscillator Pins")

The following pins may be required:

• VREF+/VREF- pins – used when external voltage reference for the ADC module is implemented

Note: The AVDD and AVss pins must be connected, regardless of ADC use and the ADC voltage reference source.

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1  $\mu$ F (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

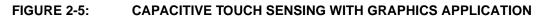

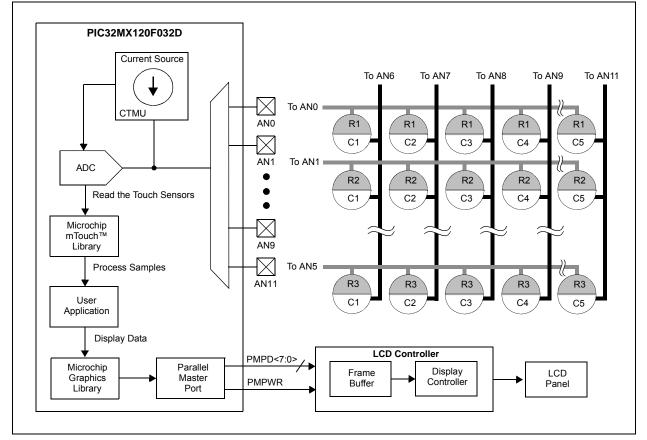

#### 2.9 Typical Application Connection Examples

Examples of typical application connections are shown in Figure 2-5 and Figure 2-6.

FIGURE 2-6: AUDIO PLAYBACK APPLICATION

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS09            | IFS08            |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | IFS07             | IFS06             | IFS05             | IFS04             | IFS03             | IFS02             | IFS01            | IFS00            |  |  |

#### REGISTER 7-4: IFSx: INTERRUPT FLAG STATUS REGISTER

#### Legend:

| <b>L</b> ogonan                   |                  |                                    |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-0 IFS31-IFS00: Interrupt Flag Status bits

- 1 = Interrupt request has occurred

- 0 = No interrupt request has occurred

**Note:** This register represents a generic definition of the IFSx register. Refer to Table 7-1 for the exact bit definitions.

#### REGISTER 7-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC09            | IEC08            |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | IEC07             | IEC06             | IEC05             | IEC04             | IEC03             | IEC02             | IEC01            | IEC00            |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-0 IEC31-IEC00: Interrupt Enable bits

1 = Interrupt is enabled

0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 7-1 for the exact bit definitions.

#### TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 | 0         |       |              |       |       |       |       |      |      | Bi    | ts       |       |          |        |        |           |          | (0         |

|-----------------------------|---------------------------------|-----------|-------|--------------|-------|-------|-------|-------|------|------|-------|----------|-------|----------|--------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14        | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6     | 21/5  | 20/4     | 19/3   | 18/2   | 17/1      | 16/0     | All Resets |

| 5280                        | U1FRML <sup>(3)</sup>           | 31:16     | _     | —            | —     | —     | _     | _     | _    | _    | _     | —        | _     | —        | _      | —      | —         | —        | 0000       |

| 5200                        |                                 | 15:0      | _     | _            | _     | _     | —     | _     | _    | _    |       |          |       | FRML<    | 7:0>   |        |           |          | 0000       |

| 5290                        | U1FRMH <sup>(3)</sup>           | 31:16     | _     | —            | —     | —     |       | —     | —    | _    |       | —        |       | —        | —      | —      | _         | —        | 0000       |

| 52.50                       | OTTRAIT                         | 15:0      | _     | —            | —     | —     | —     | —     | —    |      |       | —        |       | _        | —      |        | FRMH<2:0> | >        | 0000       |

| 52A0                        | U1TOK                           | 31:16     | _     | —            | —     | —     |       | —     | —    | _    |       | —        | _     | _        | —      | —      | _         | —        | 0000       |

| 5270                        | UTTOR                           | 15:0      | _     | —            | —     | —     | —     | —     | —    |      |       | PID      | <3:0> |          |        | EP     | <3:0>     | -        | 0000       |

| 52B0                        | U1SOF                           | 31:16     | —     | —            |       |       | —     |       |      | _    | _     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 5260                        | 0130F                           | 15:0      | —     |              |       | _     | _     |       | _    |      |       |          |       | CNT<7    | /:0>   |        | -         | •        | 0000       |

| 52C0                        | U1BDTP2                         | 31:16     | _     | —            |       | _     |       |       | _    | _    | _     | —        | _     | —        | _      | _      | _         | —        | 0000       |

| 5200                        | OIBDIF2                         | 15:0      | _     | —            |       | _     |       |       | _    | _    |       |          |       | BDTPTR   | H<7:0> |        |           |          | 0000       |

| 52D0                        | U1BDTP3                         | 31:16     | _     | —            | —     | —     | —     | —     | —    | _    | _     | —        | _     | _        | —      | —      | —         | —        | 0000       |

| 5200                        | OIBDIF3                         | 15:0      | _     | BDTPTRU<7:0> |       |       |       |       | 0000 |      |       |          |       |          |        |        |           |          |            |

| 52E0                        | 52E0 U1CNFG1                    | 31:16     | _     | —            | —     | —     | —     | —     | —    | _    | _     | —        | _     | _        | —      | —      | —         | —        | 0000       |

| 5210                        | UTCNI UT                        | 15:0      | _     | _            | —     | —     | —     | —     | —    | _    | UTEYE | UOEMON   |       | USBSIDL  | —      | —      | _         | UASUSPND | 0001       |

| 5300                        | U1EP0                           | 31:16     | _     | _            | —     | —     | —     | —     | —    | _    |       | —        |       | _        | —      | —      | _         | —        | 0000       |

| 5500                        | UIEI U                          | 15:0      | _     | _            | —     | —     | —     | —     | —    | _    | LSPD  | RETRYDIS |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5310                        | U1EP1                           | 31:16     | _     | _            | —     | —     | —     | —     | —    | _    |       | —        |       | _        | —      | —      | _         | —        | 0000       |

| 5510                        | UIEI I                          | 15:0      | _     | _            | —     | —     | —     | —     | —    | _    |       | —        |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5320                        | U1EP2                           | 31:16     | —     | —            | _     | _     | —     | _     | —    | _    | —     | —        | —     | _        | —      | _      | —         | —        | 0000       |

| 0020                        | OTET 2                          | 15:0      | _     | —            |       | —     | —     |       | —    | —    |       | —        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5330                        | U1EP3                           | 31:16     | _     | —            |       | —     | —     | —     | —    |      |       | —        | _     | _        | —      | —      |           | —        | 0000       |

| 0000                        | UTER 0                          | 15:0      | _     | —            |       | —     | —     |       | —    | —    |       | —        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5340                        | U1EP4                           | 31:16     | —     | —            | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      |           | —        | 0000       |

| 0010                        | 01EFT                           | 15:0      | —     | —            | —     | —     | —     |       | —    | —    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5350                        | U1EP5                           | 31:16     | —     | —            | —     | —     | —     | —     | —    | —    | —     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 0000                        | 01EI 0                          | 15:0      | —     | —            | —     | —     | —     |       | —    | —    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5360                        | U1EP6                           | 31:16     | —     | —            | —     | —     | —     | —     | —    | —    | —     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 0000                        | 0.2.0                           | 15:0      | _     | _            | _     | _     |       |       |      |      | _     | —        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5370                        | U1EP7                           | 31:16     | —     | —            | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      |           | —        | 0000       |

| 3070                        | 01217                           | 15:0      | —     | —            | —     | —     | —     | —     | —    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5380                        | U1EP8                           | 31:16     | _     | —            | —     | —     |       |       | —    | _    | _     | —        | _     | _        | —      | —      | —         | —        | 0000       |

| 5500                        | UILI U                          | 15:0      | —     | -            | _     | _     | —     | _     | _    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              |                   | —                 | —                 |                   |                   |                   | _                | —                |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | —                 |                   |                   | -                 | _                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | -                 | —                 | —                 | —                 | —                 | -                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | DPPULUP           | DMPULUP           | DPPULDWN          | DMPULDWN          | VBUSON            | OTGEN             | VBUSCHG          | VBUSDIS          |

#### REGISTER 10-4: U10TGCON: USB OTG CONTROL REGISTER

#### Legend:

| Logona                            |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 | DPPUL | UP: D | )+ Pull-U | p Enable | bit |  |

|-------|-------|-------|-----------|----------|-----|--|

|       |       |       |           |          |     |  |

1 = D+ data line pull-up resistor is enabled

0 = D+ data line pull-up resistor is disabled

# bit 6 **DMPULUP:** D- Pull-Up Enable bit

- It 6 DIVIPOLOP: D- Pull-Op Enable bit

- 1 = D- data line pull-up resistor is enabled

0 = D- data line pull-up resistor is disabled

- bit 5 **DPPULDWN:** D+ Pull-Down Enable bit

- 1 = D + data line pull-down resistor is enabled

- 0 = D + data line pull-down resistor is disabled

- bit 4 **DMPULDWN:** D- Pull-Down Enable bit

- 1 = D- data line pull-down resistor is enabled

- 0 = D- data line pull-down resistor is disabled

- bit 3 VBUSON: VBUS Power-on bit

- 1 = VBUS line is powered

- 0 = VBUS line is not powered

- bit 2 OTGEN: OTG Functionality Enable bit

- 1 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under software control

- 0 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under USB hardware control

- bit 1 VBUSCHG: VBUS Charge Enable bit

- 1 = VBUS line is charged through a pull-up resistor

- 0 = VBUS line is not charged through a resistor

- bit 0 VBUSDIS: VBUS Discharge Enable bit

- 1 = VBUS line is discharged through a pull-down resistor

- 0 = VBUS line is not discharged through a resistor

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                              | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------------------|------------------|

| 21.24        | U-0                                           | U-0              |

| 31:24        |                   | _                 | —                 | —                 | _                 | —                 | _                                             | _                |

| 22:16        | U-0                                           | U-0              |

| 23:16        |                   | _                 | —                 | —                 |                   |                   | _                                             |                  |

| 15:0         | U-0                                           | U-0              |

| 15:8         |                   | —                 | —                 | —                 | —                 | -                 | —                                             | —                |

|              | R/W-0                                         | R/W-0            |

| 7:0          | BTSEE             | BMXEE             | DMAEE             | BTOEE             | DFN8EE            | CRC16EE           | CRC5EE <sup>(1)</sup><br>EOFEE <sup>(2)</sup> | PIDEE            |

#### REGISTER 10-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

#### Legend:

| 0                 |                  |                                                     |                    |

|-------------------|------------------|-----------------------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | ' = Writable bit U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                                | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

|       | •                                                         |

|-------|-----------------------------------------------------------|

| bit 7 | BTSEE: Bit Stuff Error Interrupt Enable bit               |

|       | 1 = BTSEF interrupt is enabled                            |

|       | 0 = BTSEF interrupt is disabled                           |

| bit 6 | BMXEE: Bus Matrix Error Interrupt Enable bit              |

|       | 1 = BMXEF interrupt is enabled                            |

|       | 0 = BMXEF interrupt is disabled                           |

| bit 5 | DMAEE: DMA Error Interrupt Enable bit                     |

|       | 1 = DMAEF interrupt is enabled                            |

|       | 0 = DMAEF interrupt is disabled                           |

| bit 4 | BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit |

|       | 1 = BTOEF interrupt is enabled                            |

|       | 0 = BTOEF interrupt is disabled                           |

| bit 3 | DFN8EE: Data Field Size Error Interrupt Enable bit        |

|       | 1 = DFN8EF interrupt is enabled                           |

|       | 0 = DFN8EF interrupt is disabled                          |

- bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

- 1 = CRC16EF interrupt is enabled

- 0 = CRC16EF interrupt is disabled

- bit 1 CRC5EE: CRC5 Host Error Interrupt Enable bit<sup>(1)</sup>

- 1 = CRC5EF interrupt is enabled

- 0 = CRC5EF interrupt is disabled

- EOFEE: EOF Error Interrupt Enable bit<sup>(2)</sup>

- 1 = EOF interrupt is enabled

- 0 = EOF interrupt is disabled

- bit 0 PIDEE: PID Check Failure Interrupt Enable bit

- 1 = PIDEF interrupt is enabled

- 0 = PIDEF interrupt is disabled

- Note 1: Device mode.

- 2: Host mode.

Note: For an interrupt to propagate the USBIF register, the UERRIE (U1IE<1>) bit must be set.

## TABLE 11-6: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| ssa                         |                  |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |                |        |      |            |  |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|----------------|--------|------|------------|--|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2           | 17/1   | 16/0 | All Resets |  |

| FA04                        | INT1R            | 31:16     |       |       |       |       | _     | _     |      |      |      |      |      |      |      | _              | _      |      | 0000       |  |

| FA04                        |                  | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | INT1F          | R<3:0> |      | 0000       |  |

| FA08                        | INT2R            | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | _              | —      | —    | 0000       |  |

| FAUO                        | INTZR            | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | INT2F          | R<3:0> |      | 0000       |  |

| FA0C                        | INT3R            | 31:16     | _     | _     | _     | _     | —     | —     | _    | _    | —    | _    |      | —    | _    |                | —      | —    | 0000       |  |

| FAUC                        | IN I 3R          | 15:0      |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | INT3F          | R<3:0> |      | 0000       |  |

| 5440                        |                  | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _              | _      | -    | 0000       |  |

| FA10                        | INT4R            | 15:0      | -     | _     | _     | _     | -     | -     | _    | _    | _    | _    | _    | _    |      | INT4F          | R<3:0> |      | 0000       |  |

| 5440                        | TAOKA            | 31:16     | _     | _     | _     | _     | —     | —     | _    | _    | _    | _    | _    | _    | _    | _              | _      | —    | 0000       |  |

| FA18                        | T2CKR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T2CK           | R<3:0> |      | 0000       |  |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    |      | _    | _    |                | _      | _    | 0000       |  |

| FA1C                        | T3CKR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    |      | _    |      | T3CK           | R<3:0> | •    | 0000       |  |

|                             |                  | 31:16     |       | _     | _     |       | _     | _     | 0000 |      |      |      |      |      |      |                |        |      |            |  |

| FA20                        | T4CKR            | 15:0      |       |       | _     |       | _     | _     | _    | _    | _    |      |      | _    |      | T4CKR<3:0>     |        | 0000 |            |  |

|                             |                  | 31:16     |       |       | _     |       | _     | _     | _    | _    | _    |      |      | _    | _    |                | _      | _    | 0000       |  |

| FA24                        | T5CKR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T5CK           | R<3:0> |      | 0000       |  |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |                | —      | _    | 0000       |  |

| FA28                        | IC1R             | 15:0      | _     | _     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    |      | IC1R           | <3:0>  |      | 0000       |  |

|                             |                  | 31:16     | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      | _    | _              | _      | _    | 0000       |  |

| FA2C                        | IC2R             | 15:0      | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      |      | IC2R           | <3:0>  |      | 0000       |  |

|                             |                  | 31:16     | _     | _     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    |      | _              | _      | _    | 0000       |  |

| FA30                        | IC3R             | 15:0      | _     | _     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    |      | IC3R           | <3:0>  |      | 0000       |  |

|                             |                  | 31:16     | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      | _    | _              | _      | _    | 0000       |  |

| FA34                        | IC4R             | 15:0      | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      |      | IC4R           | <3:0>  |      | 0000       |  |

|                             |                  | 31:16     | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      | _    | _              | _      | _    | 0000       |  |

| FA38                        | IC5R             | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | IC5R           | <3:0>  |      | 0000       |  |

|                             |                  | 31:16     | _     | _     |       |       | _     | _     |      | _    | _    | _    | _    | _    |      | _              |        | _    | 0000       |  |

| FA48                        | OCFAR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | OCFAR<3:0> 000 |        |      |            |  |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _              | _      | _    | 0000       |  |

| FA4C                        | OCFBR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | OCFB           | R<3:0> |      | 0000       |  |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _              | _      | _    | 0000       |  |

| FA50                        | U1RXR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U1RX           | R<3:0> |      | 0000       |  |

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### REGISTER 15-1: ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER (CONTINUED)

ICM<2:0>: Input Capture Mode Select bits

bit 2-0

- 111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

- 110 = Simple Capture Event mode every edge, specified edge first and every edge thereafter

- 101 = Prescaled Capture Event mode every sixteenth rising edge

- 100 = Prescaled Capture Event mode every fourth rising edge

- 011 = Simple Capture Event mode every rising edge

- 010 = Simple Capture Event mode every falling edge

- 001 = Edge Detect mode every edge (rising and falling)

- 000 = Input Capture module is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 19-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | <ul> <li>ABAUD: Auto-Baud Enable bit</li> <li>1 = Enable baud rate measurement on the next character – requires reception of Sync character (0x55); cleared by hardware upon completion</li> <li>0 = Baud rate measurement disabled or completed</li> </ul> |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | RXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                           |

| bit 3   | BRGH: High Baud Rate Enable bit<br>1 = High-Speed mode – 4x baud clock enabled<br>0 = Standard Speed mode – 16x baud clock enabled                                                                                                                          |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits<br>11 = 9-bit data, no parity<br>10 = 8-bit data, odd parity<br>01 = 8-bit data, even parity<br>00 = 8-bit data, no parity                                                                                       |

| bit 0   | <b>STSEL:</b> Stop Selection bit<br>1 = 2 Stop bits<br>0 = 1 Stop bit                                                                                                                                                                                       |

**Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

# 26.0 POWER-SAVING FEATURES

| Note: | This data sheet summarizes the features<br>of the PIC32MX1XX/2XX 28/36/44-pin<br>Family of devices. It is not intended to be<br>a comprehensive reference source. To<br>complement the information in this data<br>sheet, refer to <b>Section 10. "Power-</b><br><b>Saving Features"</b> (DS60001130), which<br>is available from the <i>Documentation</i> ><br><i>Reference Manual</i> section of the<br>Microchip PIC32 web site |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | (www.microchip.com/pic32).                                                                                                                                                                                                                                                                                                                                                                                                         |

|       | (                                                                                                                                                                                                                                                                                                                                                                                                                                  |

This section describes power-saving features for the PIC32MX1XX/2XX 28/36/44-pin Family. The PIC32 devices offer a total of nine methods and modes, organized into two categories, that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

# 26.1 Power Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the PBCLK and by individually disabling modules. These methods are grouped into the following categories:

- FRC Run mode: the CPU is clocked from the FRC clock source with or without postscalers

- LPRC Run mode: the CPU is clocked from the LPRC clock source

- Sosc Run mode: the CPU is clocked from the Sosc clock source

In addition, the Peripheral Bus Scaling mode is available where peripherals are clocked at the programmable fraction of the CPU clock (SYSCLK).

#### 26.2 CPU Halted Methods

The device supports two power-saving modes, Sleep and Idle, both of which Halt the clock to the CPU. These modes operate with all clock sources, as follows:

- Posc Idle mode: the system clock is derived from the Posc. The system clock source continues to operate. Peripherals continue to operate, but can optionally be individually disabled.

- FRC Idle mode: the system clock is derived from the FRC with or without postscalers. Peripherals continue to operate, but can optionally be individually disabled.

- Sosc Idle mode: the system clock is derived from the Sosc. Peripherals continue to operate, but can optionally be individually disabled.

- LPRC Idle mode: the system clock is derived from the LPRC. Peripherals continue to operate, but can optionally be individually disabled. This is the lowest power mode for the device with a clock running.

- Sleep mode: the CPU, the system clock source and any peripherals that operate from the system clock source are Halted. Some peripherals can operate in Sleep using specific clock sources. This is the lowest power mode for the device.

## 26.3 Power-Saving Operation

Peripherals and the CPU can be Halted or disabled to further reduce power consumption.

#### 26.3.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are Halted. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- The CPU is halted

- The system clock source is typically shutdown. See Section 26.3.3 "Peripheral Bus Scaling Method" for specific information.

- There can be a wake-up delay based on the oscillator selection

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode

- The BOR circuit remains operative during Sleep mode

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep

- The USB module can override the disabling of the Posc or FRC. Refer to the USB section for specific details.

- Modules can be individually disabled by software prior to entering Sleep in order to further reduce consumption

#### 26.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid. To disable a peripheral, the associated PMDx bit must be set to '1'. To enable a peripheral, the associated PMDx bit must be cleared (default). See Table 26-1 for more information.

Note: Disabling a peripheral module while it's ON bit is set, may result in undefined behavior. The ON bit for the associated peripheral module must be cleared prior to disable a module via the PMDx bits.

| TABLE 26-1: | PERIPHERAL MODULE DISABLE BITS AND LOCATIONS | 5 |

|-------------|----------------------------------------------|---|

|             |                                              |   |

| Peripheral <sup>(1)</sup>    | PMDx bit Name <sup>(1)</sup> | Register Name and Bit Location |

|------------------------------|------------------------------|--------------------------------|

| ADC1                         | AD1MD                        | PMD1<0>                        |

| СТМU                         | CTMUMD                       | PMD1<8>                        |

| Comparator Voltage Reference | CVRMD                        | PMD1<12>                       |

| Comparator 1                 | CMP1MD                       | PMD2<0>                        |

| Comparator 2                 | CMP2MD                       | PMD2<1>                        |

| Comparator 3                 | CMP3MD                       | PMD2<2>                        |

| Input Capture 1              | IC1MD                        | PMD3<0>                        |

| Input Capture 2              | IC2MD                        | PMD3<1>                        |

| Input Capture 3              | IC3MD                        | PMD3<2>                        |

| Input Capture 4              | IC4MD                        | PMD3<3>                        |

| Input Capture 5              | IC5MD                        | PMD3<4>                        |

| Output Compare 1             | OC1MD                        | PMD3<16>                       |

| Output Compare 2             | OC2MD                        | PMD3<17>                       |

| Output Compare 3             | OC3MD                        | PMD3<18>                       |

| Output Compare 4             | OC4MD                        | PMD3<19>                       |

| Output Compare 5             | OC5MD                        | PMD3<20>                       |

| Timer1                       | T1MD                         | PMD4<0>                        |

| Timer2                       | T2MD                         | PMD4<1>                        |

| Timer3                       | T3MD                         | PMD4<2>                        |

| Timer4                       | T4MD                         | PMD4<3>                        |

| Timer5                       | T5MD                         | PMD4<4>                        |

| UART1                        | U1MD                         | PMD5<0>                        |

| UART2                        | U2MD                         | PMD5<1>                        |

| SPI1                         | SPI1MD                       | PMD5<8>                        |

| SPI2                         | SPI2MD                       | PMD5<9>                        |

| I2C1                         | I2C1MD                       | PMD5<16>                       |

| I2C2                         | I2C2MD                       | PMD5<17>                       |

| USB <sup>(2)</sup>           | USBMD                        | PMD5<24>                       |

| RTCC                         | RTCCMD                       | PMD6<0>                        |

| Reference Clock Output       | REFOMD                       | PMD6<1>                        |

| PMP                          | PMPMD                        | PMD6<16>                       |

Note 1: Not all modules and associated PMDx bits are available on all devices. See TABLE 1: "PIC32MX1XX 28/36/44-Pin General Purpose Family Features" and TABLE 2: "PIC32MX2XX 28/36/44-pin USB Family Features" for the lists of available peripherals.

2: The module must not be busy after clearing the associated ON bit and prior to setting the USBMD bit.

#### TABLE 26-2: PERIPHERAL MODULE DISABLE REGISTER MAP

| ess                         |                                 |           |       |       |       |       |       |       |        |        | Bits |      |      |       |       |        |        |        | 6          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|--------|--------|------|------|------|-------|-------|--------|--------|--------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8   | 23/7 | 22/6 | 21/5 | 20/4  | 19/3  | 18/2   | 17/1   | 16/0   | All Resets |

| 5040                        | PMD1                            | 31:16     | —     | —     | _     | —     | _     | _     | _      | —      | —    | —    | —    | —     | —     | —      | —      | —      | 0000       |

| F240                        | FIVIDI                          | 15:0      | -     |       |       | CVRMD | Ι     |       |        | CTMUMD | —    | -    |      | -     | —     |        | —      | AD1MD  | 0000       |

| 5250                        | PMD2                            | 31:16     | —     | —     |       | —     | _     | _     |        | —      | —    | —    | —    | —     | —     | —      | —      | —      | 0000       |

| F250                        | FIVIDZ                          | 15:0      | -     |       |       | —     | Ι     |       |        | —      | —    | -    |      | -     | —     | CMP3MD | CMP2MD | CMP1MD | 0000       |

| F260                        | PMD3                            | 31:16     | _     |       |       | _     | -     |       |        | _      | _    |      | _    | OC5MD | OC4MD | OC3MD  | OC2MD  | OC1MD  | 0000       |

| F200                        | FIVIDS                          | 15:0      | _     |       |       | _     | -     |       |        | _      | _    |      | _    | IC5MD | IC4MD | IC3MD  | IC2MD  | IC1MD  | 0000       |

| F270                        | PMD4                            | 31:16     | _     |       |       | _     | -     |       |        | _      | _    |      | _    | -     | _     | _      | —      | _      | 0000       |

| F270                        | F IVID4                         | 15:0      | _     |       |       | _     | -     |       |        | _      | _    |      | _    | T5MD  | T4MD  | T3MD   | T2MD   | T1MD   | 0000       |

| F280                        | PMD5                            | 31:16     | _     |       |       | _     | -     |       |        | USB1MD | _    |      | _    | -     | _     | _      | I2C1MD | I2C1MD | 0000       |

| F200                        | FIVIDS                          | 15:0      | _     | -     |       | _     | -     |       | SPI2MD | SPI1MD | _    |      | _    | -     | _     | _      | U2MD   | U1MD   | 0000       |

| F200                        | PMD6                            | 31:16     | _     | —     |       | —     | _     | _     |        | _      | —    | _    | —    | —     | —     | —      | —      | PMPMD  | 0000       |

| F290                        | I WD0                           | 15:0      | —     | _     | _     | —     | _     | _     | -      | —      | —    | _    | _    | _     | —     | _      | REFOMD | RTCCMD | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### REGISTER 27-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

bit 18-10 **PWP<8:0>:** Program Flash Write-Protect bits<sup>(3)</sup>

| DIT 18-10 | PWP<8:0>: Program Flash Write-Protect bits <sup>30</sup>                                                       |

|-----------|----------------------------------------------------------------------------------------------------------------|

|           | Prevents selected program Flash memory pages from being modified during code execution.<br>11111111 = Disabled |

|           | 111111110 = Memory below 0x0400 address is write-protected                                                     |

|           | 111111101 = Memory below 0x0400 address is write-protected                                                     |

|           | 111111100 = Memory below 0x0000 address is write-protected                                                     |

|           | 111111001 = Memory below 0x0000 address is write-protected                                                     |

|           | 111111010 = Memory below 0x1000 (44) address is write-protected                                                |

|           | 111111001 = Memory below 0x1400 address is write-protected                                                     |

|           | 111111000 = Memory below 0x1000 address is write-protected                                                     |

|           | 111110111 = Memory below 0x2000 (8K) address is write-protected                                                |

|           | 111110110 = Memory below 0x2400 address is write-protected                                                     |

|           | 111110101 = Memory below 0x2800 address is write-protected                                                     |

|           | 111110100 = Memory below 0x2C00 address is write-protected                                                     |

|           | 111110011 = Memory below 0x3000 address is write-protected                                                     |

|           | 111110010 = Memory below 0x3400 address is write-protected                                                     |

|           | 111110001 = Memory below 0x3800 address is write-protected                                                     |

|           | 111110000 = Memory below 0x3C00 address is write-protected                                                     |

|           | 111101111 = Memory below 0x4000 (16K) address is write-protected                                               |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | •<br>110111111 = Memory below 0x10000 (64K) address is write-protected                                         |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | 101111111 = Memory below 0x20000 (128K) address is write-protected                                             |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | 011111111 = Memory below 0x40000 (256K) address is write-protected                                             |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | 00000000 = All possible memory is write-protected                                                              |

|           |                                                                                                                |

| bit 9-5   | Reserved: Write '1'                                                                                            |

| bit 4-3   | ICESEL<1:0>: In-Circuit Emulator/Debugger Communication Channel Select bits <sup>(2)</sup>                     |

|           | 11 = PGEC1/PGED1 pair is used                                                                                  |

|           | 10 = PGEC2/PGED2 pair is used                                                                                  |

|           | 01 = PGEC3/PGED3 pair is used                                                                                  |

|           | 00 = PGEC4/PGED4 pair is used <sup>(2)</sup>                                                                   |

| bit 2     | JTAGEN: JTAG Enable bit <sup>(1)</sup>                                                                         |

| bit 2     | 1 = JTAG is enabled                                                                                            |

|           | 0 = JTAG is disabled                                                                                           |

| bit 1-0   | <b>DEBUG&lt;1:0&gt;:</b> Background Debugger Enable bits (forced to '11' if code-protect is enabled)           |

|           |                                                                                                                |

|           | 1x = Debugger is disabled                                                                                      |

|           | 0x = Debugger is enabled                                                                                       |

| Note 1:   | This bit sets the value for the JTAGEN bit in the CFGCON register.                                             |

|           | -                                                                                                              |

| 2:        | The PGEC4/PGED4 pin pair is not available on all devices. Refer to the " <b>Pin Diagrams</b> " section for     |

|           | availability.                                                                                                  |

| -         |                                                                                                                |

3: The PWP<8:7> bits are only available on devices with 256 KB Flash.

| DC CHA        | RACTER | ISTICS                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                                        |     |        |                                               |  |  |  |

|---------------|--------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----|--------|-----------------------------------------------|--|--|--|

| Param.<br>No. | Symbol | Characteristics                      | Min.                                                                                                                                                                                                                                                                                | Min. Typical <sup>(1)</sup> Max. Units |     |        | Conditions                                    |  |  |  |

|               |        | Program Flash Memory <sup>(3)</sup>  |                                                                                                                                                                                                                                                                                     |                                        |     |        |                                               |  |  |  |

| D130          | Eр     | Cell Endurance                       | 20,000                                                                                                                                                                                                                                                                              | —                                      | _   | E/W    | —                                             |  |  |  |

| D131          | Vpr    | VDD for Read                         | 2.3                                                                                                                                                                                                                                                                                 | —                                      | 3.6 | V      | —                                             |  |  |  |

| D132          | VPEW   | VDD for Erase or Write               | 2.3                                                                                                                                                                                                                                                                                 | —                                      | 3.6 | V      | —                                             |  |  |  |

| D134          | Tretd  | Characteristic Retention             | 20                                                                                                                                                                                                                                                                                  | —                                      | _   | Year   | Provided no other specifications are violated |  |  |  |

| D135          | IDDP   | Supply Current during<br>Programming | _                                                                                                                                                                                                                                                                                   | 10                                     | _   | mA     | —                                             |  |  |  |

|               | Tww    | Word Write Cycle Time                | —                                                                                                                                                                                                                                                                                   | 411                                    | _   | es     | See Note 4                                    |  |  |  |

| D136          | Trw    | Row Write Cycle Time                 | —                                                                                                                                                                                                                                                                                   | 6675                                   | _   | Cycles | See Note 2,4                                  |  |  |  |

| D137          | TPE    | Page Erase Cycle Time                | —                                                                                                                                                                                                                                                                                   | 20011                                  | _   |        | See Note 4                                    |  |  |  |

|               | TCE    | Chip Erase Cycle Time                | —                                                                                                                                                                                                                                                                                   | 80180                                  | _   | FRC    | See Note 4                                    |  |  |  |

#### TABLE 30-12: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: The minimum SYSCLK for row programming is 4 MHz. Care should be taken to minimize bus activities during row programming, such as suspending any memory-to-memory DMA operations. If heavy bus loads are expected, selecting Bus Matrix Arbitration mode 2 (rotating priority) may be necessary. The default Arbitration mode is mode 1 (CPU has lowest priority).

**3:** Refer to the *"PIC32 Flash Programming Specification"* (DS60001145) for operating conditions during programming and erase cycles.

4: This parameter depends on FRC accuracy (See Table 30-19) and FRC tuning values (See Register 8-2).

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### FIGURE 30-10: SPIx MODULE MASTER MODE (CKE = 0) TIMING CHARACTERISTICS SCKx (CKP = 0) SP11 SP10 SP21 SP20 SCKx (CKP = 1) SP35 SP20 SP21 SDOx MSb Bit 14 -1 LSb **SP31** SP30 SDIx LSb In MSb In Bit 14 SP40 'SP41' Note: Refer to Figure 30-1 for load conditions.

#### TABLE 30-28: SPIx MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHA        | RACTERIST             | TICS                                       | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |      |       |                    |  |  |  |

|---------------|-----------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|--|--|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>             | Min.                                                                                                                                                                                                                                                                                | Typical <sup>(2)</sup> | Max. | Units | Conditions         |  |  |  |

| SP10          | TscL                  | SCKx Output Low Time<br>(Note 3)           | Тѕск/2                                                                                                                                                                                                                                                                              | _                      |      | ns    | _                  |  |  |  |

| SP11          | TscH                  | SCKx Output High Time<br>(Note 3)          | Тѕск/2                                                                                                                                                                                                                                                                              | —                      | _    | ns    | _                  |  |  |  |

| SP20          | TscF                  | SCKx Output Fall Time (Note 4)             | —                                                                                                                                                                                                                                                                                   | —                      |      | ns    | See parameter DO32 |  |  |  |

| SP21          | TscR                  | SCKx Output Rise Time (Note 4)             | —                                                                                                                                                                                                                                                                                   | —                      | _    | ns    | See parameter DO31 |  |  |  |

| SP30          | TDOF                  | SDOx Data Output Fall Time (Note 4)        | —                                                                                                                                                                                                                                                                                   | —                      | _    | ns    | See parameter DO32 |  |  |  |

| SP31          | TDOR                  | SDOx Data Output Rise Time (Note 4)        | —                                                                                                                                                                                                                                                                                   | _                      | _    | ns    | See parameter DO31 |  |  |  |

| SP35          | TscH2doV,             | SDOx Data Output Valid after               | —                                                                                                                                                                                                                                                                                   | —                      | 15   | ns    | VDD > 2.7V         |  |  |  |

|               | TscL2doV              | SCKx Edge                                  |                                                                                                                                                                                                                                                                                     | _                      | 20   | ns    | VDD < 2.7V         |  |  |  |

| SP40          | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge | 10                                                                                                                                                                                                                                                                                  | —                      | —    | ns    | —                  |  |  |  |

| SP41          | TSCH2DIL,<br>TSCL2DIL | Hold Time of SDIx Data Input to SCKx Edge  | 10                                                                                                                                                                                                                                                                                  | —                      |      | ns    |                    |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 50 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

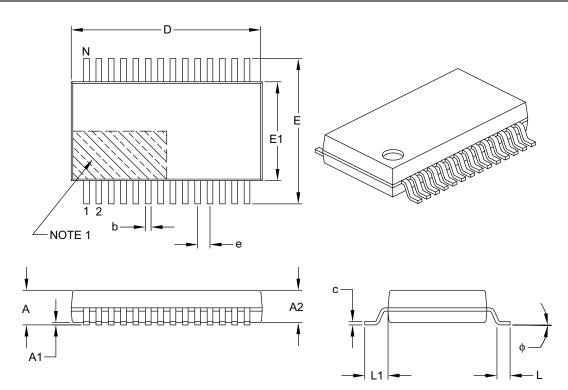

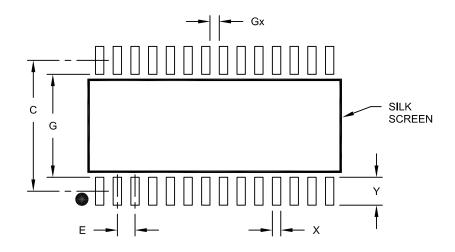

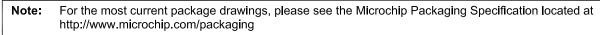

#### 33.2 Package Details

This section provides the technical details of the packages.

#### 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |          |       |  |  |

|--------------------------|------------------|-------------|----------|-------|--|--|

|                          | Dimension Limits | MIN         | NOM      | MAX   |  |  |

| Number of Pins           | N                |             | 28       |       |  |  |

| Pitch                    | e                |             | 0.65 BSC |       |  |  |

| Overall Height           | A                | -           | -        | 2.00  |  |  |

| Molded Package Thickness | A2               | 1.65        | 1.75     | 1.85  |  |  |

| Standoff                 | A1               | 0.05        | -        | -     |  |  |

| Overall Width            | E                | 7.40        | 7.80     | 8.20  |  |  |

| Molded Package Width     | E1               | 5.00        | 5.30     | 5.60  |  |  |

| Overall Length           | D                | 9.90        | 10.20    | 10.50 |  |  |

| Foot Length              | L                | 0.55        | 0.75     | 0.95  |  |  |

| Footprint                | L1               | 1.25 REF    |          |       |  |  |

| Lead Thickness           | С                | 0.09        | -        | 0.25  |  |  |

| Foot Angle               | φ                | 0°          | 4°       | 8°    |  |  |