### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Detuns                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 19                                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 28-SPDIP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx220f032b-v-sp |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to documents listed in the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

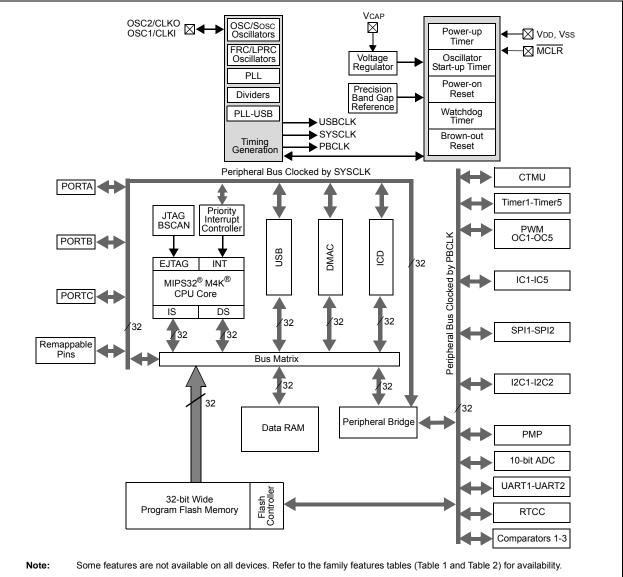

**BLOCK DIAGRAM**

This document contains device-specific information for PIC32MX1XX/2XX 28/36/44-pin Family devices.

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX1XX/2XX 28/36/44-pin Family of devices.

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

FIGURE 1-1:

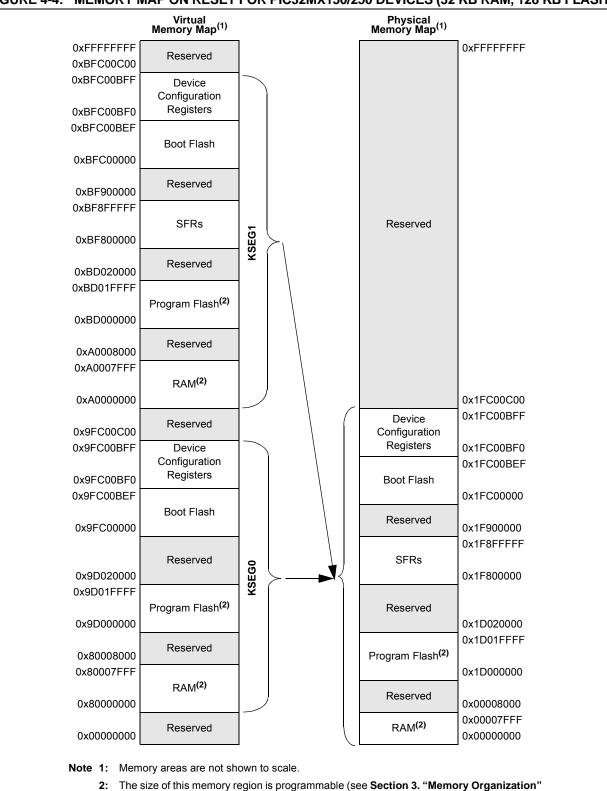

# FIGURE 4-4: MEMORY MAP ON RESET FOR PIC32MX150/250 DEVICES (32 KB RAM, 128 KB FLASH)

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS60001115) in the "*PIC32 Family Reference Manual*") and can be changed by initialization code provided by end-user development tools (refer to the specific development tool documentation for information).

# TABLE 4-1: SFR MEMORY MAP

|                           | Virtual A | ddress          |

|---------------------------|-----------|-----------------|

| Peripheral                | Base      | Offset<br>Start |

| Watchdog Timer            |           | 0x0000          |

| RTCC                      |           | 0x0200          |

| Timer1-5                  |           | 0x0600          |

| Input Capture 1-5         |           | 0x2000          |

| Output Compare 1-5        |           | 0x3000          |

| IC1 and IC2               |           | 0x5000          |

| SPI1 and SPI2             |           | 0x5800          |

| UART1 and UART2           |           | 0x6000          |

| PMP                       |           | 0x7000          |

| ADC                       | 0xBF80    | 0x9000          |

| CVREF                     |           | 0x9800          |

| Comparator                |           | 0xA000          |

| CTMU                      |           | 0xA200          |

| Oscillator                |           | 0xF000          |

| Device and Revision ID    |           | 0xF220          |

| Peripheral Module Disable |           | 0xF240          |

| Flash Controller          |           | 0xF400          |

| Reset                     |           | 0xF600          |

| PPS                       |           | 0xFA04          |

| Interrupts                |           | 0x1000          |

| Bus Matrix                |           | 0x2000          |

| DMA                       | 0xBF88    | 0x3000          |

| USB                       |           | 0x5050          |

| PORTA-PORTC               |           | 0x6000          |

| Configuration             | 0xBFC0    | 0x0BF0          |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |

| 31:24        |                   |                   |                   | NVMKE             | Y<31:24>          |                   |                  |                  |  |  |  |

| 00.40        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |

| 23:16        | NVMKEY<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |

| 15:8         | NVMKEY<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |

| 7:0          | NVMKEY<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

# REGISTER 5-2: NVMKEY: PROGRAMMING UNLOCK REGISTER

# Legend:

| Legena.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

### bit 31-0 NVMKEY<31:0>: Unlock Register bits

These bits are write-only, and read as '0' on any read

Note: This register is used as part of the unlock sequence to prevent inadvertent writes to the PFM.

# REGISTER 5-3: NVMADDR: FLASH ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        |                   |                   |                   | NVMADI            | DR<31:24>         |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | NVMADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | NVMADDR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | NVMADDR<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 NVMADDR<31:0>: Flash Address bits

Bulk/Chip/PFM Erase: Address is ignored. Page Erase: Address identifies the page to erase. Row Program: Address identifies the row to program. Word Program: Address identifies the word to program.

# TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION

| (1)                                 | IRQ | Vector |          | Persistent |             |              |           |  |

|-------------------------------------|-----|--------|----------|------------|-------------|--------------|-----------|--|

| Interrupt Source <sup>(1)</sup>     | #   | #      | Flag     | Enable     | Priority    | Sub-priority | Interrupt |  |

| Highest Natural Order Priority      |     |        |          |            |             |              |           |  |

| CT – Core Timer Interrupt           | 0   | 0      | IFS0<0>  | IEC0<0>    | IPC0<4:2>   | IPC0<1:0>    | No        |  |

| CS0 – Core Software Interrupt 0     | 1   | 1      | IFS0<1>  | IEC0<1>    | IPC0<12:10> | IPC0<9:8>    | No        |  |

| CS1 – Core Software Interrupt 1     | 2   | 2      | IFS0<2>  | IEC0<2>    | IPC0<20:18> | IPC0<17:16>  | No        |  |

| INT0 – External Interrupt           | 3   | 3      | IFS0<3>  | IEC0<3>    | IPC0<28:26> | IPC0<25:24>  | No        |  |

| T1 – Timer1                         | 4   | 4      | IFS0<4>  | IEC0<4>    | IPC1<4:2>   | IPC1<1:0>    | No        |  |

| IC1E – Input Capture 1 Error        | 5   | 5      | IFS0<5>  | IEC0<5>    | IPC1<12:10> | IPC1<9:8>    | Yes       |  |

| IC1 – Input Capture 1               | 6   | 5      | IFS0<6>  | IEC0<6>    | IPC1<12:10> | IPC1<9:8>    | Yes       |  |

| OC1 – Output Compare 1              | 7   | 6      | IFS0<7>  | IEC0<7>    | IPC1<20:18> | IPC1<17:16>  | No        |  |

| INT1 – External Interrupt 1         | 8   | 7      | IFS0<8>  | IEC0<8>    | IPC1<28:26> | IPC1<25:24>  | No        |  |

| T2 – Timer2                         | 9   | 8      | IFS0<9>  | IEC0<9>    | IPC2<4:2>   | IPC2<1:0>    | No        |  |

| IC2E – Input Capture 2              | 10  | 9      | IFS0<10> | IEC0<10>   | IPC2<12:10> | IPC2<9:8>    | Yes       |  |

| IC2 – Input Capture 2               | 11  | 9      | IFS0<11> | IEC0<11>   | IPC2<12:10> | IPC2<9:8>    | Yes       |  |

| OC2 – Output Compare 2              | 12  | 10     | IFS0<12> | IEC0<12>   | IPC2<20:18> | IPC2<17:16>  | No        |  |

| INT2 – External Interrupt 2         | 13  | 11     | IFS0<13> | IEC0<13>   | IPC2<28:26> | IPC2<25:24>  | No        |  |

| T3 – Timer3                         | 14  | 12     | IFS0<14> | IEC0<14>   | IPC3<4:2>   | IPC3<1:0>    | No        |  |

| IC3E – Input Capture 3              | 15  | 13     | IFS0<15> | IEC0<15>   | IPC3<12:10> | IPC3<9:8>    | Yes       |  |

| IC3 – Input Capture 3               | 16  | 13     | IFS0<16> | IEC0<16>   | IPC3<12:10> | IPC3<9:8>    | Yes       |  |

| OC3 – Output Compare 3              | 17  | 14     | IFS0<17> | IEC0<17>   | IPC3<20:18> | IPC3<17:16>  | No        |  |

| INT3 – External Interrupt 3         | 18  | 15     | IFS0<18> | IEC0<18>   | IPC3<28:26> | IPC3<25:24>  | No        |  |

| T4 – Timer4                         | 19  | 16     | IFS0<19> | IEC0<19>   | IPC4<4:2>   | IPC4<1:0>    | No        |  |

| IC4E – Input Capture 4 Error        | 20  | 17     | IFS0<20> | IEC0<20>   | IPC4<12:10> | IPC4<9:8>    | Yes       |  |

| IC4 – Input Capture 4               | 21  | 17     | IFS0<21> | IEC0<21>   | IPC4<12:10> | IPC4<9:8>    | Yes       |  |

| OC4 – Output Compare 4              | 22  | 18     | IFS0<22> | IEC0<22>   | IPC4<20:18> | IPC4<17:16>  | No        |  |

| INT4 – External Interrupt 4         | 23  | 19     | IFS0<23> | IEC0<23>   | IPC4<28:26> | IPC4<25:24>  | No        |  |

| T5 – Timer5                         | 24  | 20     | IFS0<24> | IEC0<24>   | IPC5<4:2>   | IPC5<1:0>    | No        |  |

| IC5E – Input Capture 5 Error        | 25  | 21     | IFS0<25> | IEC0<25>   | IPC5<12:10> | IPC5<9:8>    | Yes       |  |

| IC5 – Input Capture 5               | 26  | 21     | IFS0<26> | IEC0<26>   | IPC5<12:10> | IPC5<9:8>    | Yes       |  |

| OC5 – Output Compare 5              | 27  | 22     | IFS0<27> | IEC0<27>   | IPC5<20:18> | IPC5<17:16>  | No        |  |

| AD1 – ADC1 Convert done             | 28  | 23     | IFS0<28> | IEC0<28>   | IPC5<28:26> | IPC5<25:24>  | Yes       |  |

| FSCM – Fail-Safe Clock Monitor      | 29  | 24     | IFS0<29> | IEC0<29>   | IPC6<4:2>   | IPC6<1:0>    | No        |  |

| RTCC – Real-Time Clock and Calendar | 30  | 25     | IFS0<30> | IEC0<30>   | IPC6<12:10> | IPC6<9:8>    | No        |  |

| FCE – Flash Control Event           | 31  | 26     | IFS0<31> | IEC0<31>   | IPC6<20:18> | IPC6<17:16>  | No        |  |

| CMP1 – Comparator Interrupt         | 32  | 27     | IFS1<0>  | IEC1<0>    | IPC6<28:26> | IPC6<25:24>  | No        |  |

| CMP2 – Comparator Interrupt         | 33  | 28     | IFS1<1>  | IEC1<1>    | IPC7<4:2>   | IPC7<1:0>    | No        |  |

| CMP3 – Comparator Interrupt         | 34  | 29     | IFS1<2>  | IEC1<2>    | IPC7<12:10> | IPC7<9:8>    | No        |  |

| USB – USB Interrupts                | 35  | 30     | IFS1<3>  | IEC1<3>    | IPC7<20:18> | IPC7<17:16>  | Yes       |  |

| SPI1E – SPI1 Fault                  | 36  | 31     | IFS1<4>  | IEC1<4>    | IPC7<28:26> | IPC7<25:24>  | Yes       |  |

| SPI1RX – SPI1 Receive Done          | 37  | 31     | IFS1<5>  | IEC1<5>    | IPC7<28:26> | IPC7<25:24>  | Yes       |  |

| SPI1TX – SPI1 Transfer Done         | 38  | 31     | IFS1<6>  | IEC1<6>    | IPC7<28:26> | IPC7<25:24>  | Yes       |  |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX 28/36/44-Pin General Purpose Family Features" and TABLE 2: "PIC32MX2XX 28/36/44-pin USB Family Features" for the lists of available peripherals.

# 8.0 OSCILLATOR CONFIGURATION

| Note: | This data sheet summarizes the features<br>of the PIC32MX1XX/2XX 28/36/44-pin<br>Family of devices. It is not intended to be<br>a comprehensive reference source. To<br>complement the information in this data |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | sheet, refer to Section 6. "Oscillator                                                                                                                                                                          |

|       | Configuration" (DS60001112), which is                                                                                                                                                                           |

|       | available from the Documentation >                                                                                                                                                                              |

|       | Reference Manual section of the                                                                                                                                                                                 |

|       | Microchip PIC32 web site                                                                                                                                                                                        |

|       | (www.microchip.com/pic32).                                                                                                                                                                                      |

The PIC32MX1XX/2XX 28/36/44-pin Family oscillator system has the following modules and features:

- Four external and internal oscillator options as clock sources

- On-Chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-Chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Dedicated On-Chip PLL for USB peripheral

A block diagram of the oscillator system is provided in Figure 8-1.

| REGISTE | R 9-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER (CONTINUED)                                                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | CHDHIF: Channel Destination Half Full Interrupt Flag bit                                                                                                                                   |

|         | <ul> <li>1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)</li> <li>0 = No interrupt is pending</li> </ul>                                           |

| bit 3   | CHBCIF: Channel Block Transfer Complete Interrupt Flag bit                                                                                                                                 |

|         | <ul> <li>1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs</li> <li>0 = No interrupt is pending</li> </ul> |

| bit 2   | CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit                                                                                                                                  |

|         | <ul><li>1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)</li><li>0 = No interrupt is pending</li></ul>                                                          |

| bit 1   | CHTAIF: Channel Transfer Abort Interrupt Flag bit                                                                                                                                          |

|         | <ul> <li>1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted</li> <li>0 = No interrupt is pending</li> </ul>                                          |

| bit 0   | CHERIF: Channel Address Error Interrupt Flag bit                                                                                                                                           |

|         | <ul> <li>1 = A channel address error has been detected (either the source or the destination address is invalid)</li> <li>0 = No interrupt is pending</li> </ul>                           |

DS60001168J-page 96

#### **USB Control Registers** 10.1

# TABLE 10-1: USB REGISTER MAP

| ess                         |                                 |           |       |       |       |       |       |       |      |      | Bit                    | s        |          |                  |          |          |                 |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------------------------|----------|----------|------------------|----------|----------|-----------------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7                   | 22/6     | 21/5     | 20/4             | 19/3     | 18/2     | 17/1            | 16/0     | All Resets |

| 5040                        | (4)                             | 31:16     | _     | —     | —     | —     | —     | —     |      | _    | —                      | —        | —        | —                | —        | —        | _               | —        | 000        |

| 5040                        | UTUTUIK()                       | 15:0      |       | _     | _     | —     | _     | _     |      | _    | IDIF                   | T1MSECIF | LSTATEIF | ACTVIF           | SESVDIF  | SESENDIF | 1               | VBUSVDIF | 000        |

| 5050                        | <b>U10TGIE</b>                  | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —                      |          | —        | —                | —        | —        | _               | —        | 000        |

| 0000                        | OTOTOLE                         | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | IDIE                   | T1MSECIE | LSTATEIE | ACTVIE           | SESVDIE  | SESENDIE | _               | VBUSVDIE | 000        |

| 5060                        | U10TGSTAT <sup>(3)</sup>        | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |                        |          | —        | —                |          | —        | _               |          | 000        |

| 0000                        | 0101001/11                      | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | ID                     |          | LSTATE   | —                | SESVD    | SESEND   | _               | VBUSVD   | 000        |

| 5070                        | U10TGCON                        | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |                        |          | —        | —                |          | —        | _               |          | 000        |

| 0070                        | UTOTOOON                        | 15:0      | _     | —     | —     | —     | —     | —     | _    | —    | DPPULUP                | DMPULUP  | DPPULDWN | DMPULDWN         | VBUSON   | OTGEN    | VBUSCHG         | VBUSDIS  | 000        |

| 5080                        | U1PWRC                          | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |                        |          | —        | —                |          | —        | _               |          | 000        |

| 0000                        | on wite                         | 15:0      | _     | —     | —     | —     | —     | —     | _    | —    | UACTPND <sup>(4)</sup> |          | —        | USLPGRD          | USBBUSY  | —        | USUSPEND        | USBPWR   | 000        |

|                             |                                 | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |                        |          | —        | —                |          | —        | _               |          | 000        |

| 5200                        | U1IR <sup>(2)</sup>             | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | STALLIF                | ATTACHIF | RESUMEIF | IDLEIF           | TRNIF    | SOFIF    | UERRIF          | URSTIF   | 000        |

|                             |                                 | 04.40     |       |       |       |       |       |       |      |      |                        |          |          |                  |          |          |                 | DETACHIF | 000        |

| 5210                        | U1IE                            | 31:16     | _     | _     |       |       |       |       |      | _    | —                      | —        |          | —                | —        | —        | —               |          | 000        |

| 5210                        | OTIE                            | 15:0      | —     | —     |       | —     | —     | —     | —    | —    | STALLIE                | ATTACHIE | RESUMEIE | IDLEIE           | TRNIE    | SOFIE    | UERRIE          | DETACHIE | 000        |

|                             |                                 | 31:16     | _     | _     | _     | _     |       | _     |      |      | _                      | _        | _        | _                | _        | _        | _               |          | 000        |

| 5220                        | U1EIR <sup>(2)</sup>            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | BTSEF                  | BMXEF    | DMAEF    | BTOEF            | DFN8EF   | CRC16EF  | CRC5EF<br>EOFEF | PIDEF    | 000        |

|                             |                                 | 31:16     | _     | _     |       | _     | _     | _     | _    | _    | _                      |          | _        | _                | _        |          | _               |          | 000        |

| 5230                        | U1EIE                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | BTSEE                  | BMXEE    | DMAEE    | BTOEE            | DFN8EE   | CRC16EE  | CRC5EE<br>EOFEE | PIDEE    | 000        |

|                             | (2)                             | 31:16     | _     | _     |       | _     | _     |       |      | _    |                        | _        |          | _                | _        |          | _               | _        | 000        |

| 5240                        | U1STAT <sup>(3)</sup>           | 15:0      | _     | _     | _     | _     | _     | _     |      | _    |                        |          | PT<3:0>  |                  | DIR      | PPBI     | _               | _        | 000        |

|                             |                                 | 31:16     | _     |       | _     | _     | _     | _     |      | _    | _                      | _        |          |                  | _        | _        | _               | _        | 000        |

| 5250                        | U1CON                           |           |       |       |       |       |       |       |      |      |                        |          | PKTDIS   |                  |          |          |                 | USBEN    | 000        |

|                             |                                 | 15:0      |       | —     | —     | —     | —     | —     |      | —    | JSTATE                 | SE0      | TOKBUSY  | USBRST           | HOSTEN   | RESUME   | PPBRST          | SOFEN    | 000        |

| 5260                        | U1ADDR                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _                      | _        | _        | _                | _        | _        | _               | —        | 000        |

| 5260                        | UTADDR                          | 15:0      | _     | _     | _     | _     | _     | —     | _    | _    | LSPDEN                 |          |          | DE               | VADDR<6: | 0>       |                 |          | 000        |

| 5070                        |                                 | 31:16     | -     | _     | _     | _     | _     | _     | _    | _    | _                      | _        | _        | _                | _        | _        | _               | _        | 000        |

| 5270                        | U1BDTP1                         | 15:0      | —     |       |       | —     |       |       |      | _    |                        |          | BC       | )<br>TPTRL<15:9> | >        |          |                 |          | 0000       |

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information. Note 1:

2: This register does not have associated SET and INV registers.

This register does not have associated CLR, SET and INV registers. 3:

4: Reset value for this bit is undefined.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range |       |          | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------|----------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0   | U-0      | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |       | _        |                   |                   |                   | —                 |                  | —                |

| 23:16        | U-0   | U-0      | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -     | —        |                   |                   | -                 | —                 |                  | —                |

| 15:8         | U-0   | U-0      | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | -     | —        | —                 | -                 | -                 | —                 | —                | —                |

| 7:0          | R/W-0 | R/W-0    | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | R/W-0            |

| 7:0          | IDIE  | T1MSECIE | LSTATEIE          | ACTVIE            | SESVDIE           | SESENDIE          |                  | VBUSVDIE         |

# REGISTER 10-2: U1OTGIE: USB OTG INTERRUPT ENABLE REGISTER

### Legend:

| R = Readable bit  | = Readable bit W = Writable bit |                      | ead as '0'         |

|-------------------|---------------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set                | '0' = Bit is cleared | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIE:** ID Interrupt Enable bit

- 1 = ID interrupt is enabled

- 0 = ID interrupt is disabled

### bit 6 T1MSECIE: 1 Millisecond Timer Interrupt Enable bit

- 1 = 1 millisecond timer interrupt is enabled

- 0 = 1 millisecond timer interrupt is disabled

### bit 5 LSTATEIE: Line State Interrupt Enable bit

- 1 = Line state interrupt is enabled

- 0 = Line state interrupt is disabled

- bit 4 ACTVIE: Bus Activity Interrupt Enable bit

- 1 = Activity interrupt is enabled

- 0 = Activity interrupt is disabled

- bit 3 SESVDIE: Session Valid Interrupt Enable bit

- 1 = Session valid interrupt is enabled

- 0 = Session valid interrupt is disabled

- bit 2 SESENDIE: B-Device Session End Interrupt Enable bit

- 1 = B-Device session end interrupt is enabled

- 0 = B-Device session end interrupt is disabled

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIE: A-Device VBUS Valid Interrupt Enable bit

- 1 = A-Device VBUS valid interrupt is enabled

- 0 = A-Device VBUS valid interrupt is disabled

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                              | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------------------|------------------|

| 21.24        | U-0                                           | U-0              |

| 31:24        |                   | _                 | —                 | —                 | _                 | —                 | _                                             | _                |

| 22:16        | U-0                                           | U-0              |

| 23:16        |                   | _                 | _                 | _                 |                   |                   | _                                             |                  |

| 15:0         | U-0                                           | U-0              |

| 15:8         |                   | —                 | —                 | —                 | —                 | -                 | —                                             | —                |

|              | R/W-0                                         | R/W-0            |

| 7:0          | BTSEE             | BMXEE             | DMAEE             | BTOEE             | DFN8EE            | CRC16EE           | CRC5EE <sup>(1)</sup><br>EOFEE <sup>(2)</sup> | PIDEE            |

# REGISTER 10-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

# Legend:

| 0                                 |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

### bit 31-8 Unimplemented: Read as '0'

|       | •                                                         |

|-------|-----------------------------------------------------------|

| bit 7 | BTSEE: Bit Stuff Error Interrupt Enable bit               |

|       | 1 = BTSEF interrupt is enabled                            |

|       | 0 = BTSEF interrupt is disabled                           |

| bit 6 | BMXEE: Bus Matrix Error Interrupt Enable bit              |

|       | 1 = BMXEF interrupt is enabled                            |

|       | 0 = BMXEF interrupt is disabled                           |

| bit 5 | DMAEE: DMA Error Interrupt Enable bit                     |

|       | 1 = DMAEF interrupt is enabled                            |

|       | 0 = DMAEF interrupt is disabled                           |

| bit 4 | BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit |

|       | 1 = BTOEF interrupt is enabled                            |

|       | 0 = BTOEF interrupt is disabled                           |

| bit 3 | DFN8EE: Data Field Size Error Interrupt Enable bit        |

|       | 1 = DFN8EF interrupt is enabled                           |

|       | 0 = DFN8EF interrupt is disabled                          |

- bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

- 1 = CRC16EF interrupt is enabled

- 0 = CRC16EF interrupt is disabled

- bit 1 CRC5EE: CRC5 Host Error Interrupt Enable bit<sup>(1)</sup>

- 1 = CRC5EF interrupt is enabled

- 0 = CRC5EF interrupt is disabled

- EOFEE: EOF Error Interrupt Enable bit<sup>(2)</sup>

- 1 = EOF interrupt is enabled

- 0 = EOF interrupt is disabled

- bit 0 PIDEE: PID Check Failure Interrupt Enable bit

- 1 = PIDEF interrupt is enabled

- 0 = PIDEF interrupt is disabled

- Note 1: Device mode.

- 2: Host mode.

Note: For an interrupt to propagate the USBIF register, the UERRIE (U1IE<1>) bit must be set.

NOTES:

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

### REGISTER 17-2: SPIxCON2: SPI CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0        |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|-------------------------|

| 31:24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 31.24        | —                    | —                 | —                 | —                 | —                        | —                 | _                | —                       |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 23.10        | —                    | —                 | —                 | —                 | —                        | —                 | _                | —                       |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                   |

| 10.0         | SPISGNEXT            | —                 | —                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                  |

| 7:0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                   |

| 7:0          | AUDEN <sup>(1)</sup> | _                 | _                 | —                 | AUDMONO <sup>(1,2)</sup> | —                 | AUDMOD           | )<1:0> <sup>(1,2)</sup> |

### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-16 Unimplemented: Read as '0'

- bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

- 1 = Data from RX FIFO is sign extended

- 0 = Data from RX FIFO is not sign extended

- bit 14-13 Unimplemented: Read as '0'

- bit 12 **FRMERREN:** Enable Interrupt Events via FRMERR bit

- 1 = Frame Error overflow generates error events

- 0 = Frame Error does not generate error events

- bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit

- 1 = Receive overflow generates error events

- 0 = Receive overflow does not generate error events

- bit 10 SPITUREN: Enable Interrupt Events via SPITUR bit

- 1 = Transmit underrun generates error events

- 0 = Transmit underrun does not generate error events

- bit 9 IGNROV: Ignore Receive Overflow bit (for Audio Data Transmissions)

- 1 = A ROV is not a critical error; during ROV data in the FIFO is not overwritten by receive data

0 = A ROV is a critical error that stops SPI operation

- bit 8 **IGNTUR:** Ignore Transmit Underrun bit (for Audio Data Transmissions)

- 1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty

- 0 = A TUR is a critical error that stops SPI operation

- bit 7 AUDEN: Enable Audio CODEC Support bit<sup>(1)</sup>

- 1 = Audio protocol enabled

- 0 = Audio protocol disabled

- bit 6-5 Unimplemented: Read as '0'

- bit 3 AUDMONO: Transmit Audio Data Format bit<sup>(1,2)</sup>

- 1 = Audio data is mono (Each data word is transmitted on both left and right channels)

- 0 = Audio data is stereo

- bit 2 Unimplemented: Read as '0'

- bit 1-0 AUDMOD<1:0>: Audio Protocol Mode bit<sup>(1,2)</sup>

- 11 = PCM/DSP mode

- 10 = Right-Justified mode

- 01 = Left-Justified mode

- $00 = I^2S \mod$

- **Note 1:** This bit can only be written when the ON bit = 0.

- **2:** This bit is only valid for AUDEN = 1.

# 18.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

| Note: | This data sheet summarizes the features              |

|-------|------------------------------------------------------|

|       | of the PIC32MX1XX/2XX 28/36/44-pin                   |

|       | Family of devices. It is not intended to be          |

|       | a comprehensive reference source. To                 |

|       | complement the information in this data              |

|       | sheet, refer to Section 24. "Inter-                  |

|       | Integrated Circuit (I <sup>2</sup> C)" (DS60001116), |

|       | which is available from the Documentation            |

|       | > Reference Manual section of the Micro-             |

|       | chip PIC32 web site                                  |

|       | (www.microchip.com/pic32).                           |

The I<sup>2</sup>C module provides complete hardware support for both Slave and Multi-Master modes of the I<sup>2</sup>C serial communication standard. Figure 18-1 illustrates the I<sup>2</sup>C module block diagram.

Each  $I^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- · Provides support for address bit masking

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0              | U-0              |

| 15:8         |                   | VCFG<2:0>         |                   | OFFCAL            | —                 | CSCNA             | —                | —                |

| 7.0          | R-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | BUFS              |                   |                   | SMP               | BUFM              | ALTS              |                  |                  |

# REGISTER 22-2: AD1CON2: ADC CONTROL REGISTER 2

### Legend:

| R = Readable bit  | bit W = Writable bit |                      | U = Unimplemented bit, read as '0' |  |  |  |

|-------------------|----------------------|----------------------|------------------------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared | x = Bit is unknown                 |  |  |  |

### bit 31-16 Unimplemented: Read as '0'

### bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

|     | VREFH              | VREFL              |

|-----|--------------------|--------------------|

| 000 | AVDD               | AVss               |

| 001 | External VREF+ pin | AVss               |

| 010 | AVdd               | External VREF- pin |

| 011 | External VREF+ pin | External VREF- pin |

| 1xx | AVdd               | AVss               |

### bit 12 **OFFCAL:** Input Offset Calibration Mode Select bit

### 1 = Enable Offset Calibration mode

Positive and negative inputs of the sample and hold amplifier are connected to VREFL

### 0 = Disable Offset Calibration mode

The inputs to the sample and hold amplifier are controlled by AD1CHS or AD1CSSL

### bit 11 Unimplemented: Read as '0'

- bit 10 **CSCNA:** Input Scan Select bit

- 1 = Scan inputs

0 = Do not scan inputs

### bit 9-8 **Unimplemented:** Read as '0'

bit 7 **BUFS:** Buffer Fill Status bit

Only valid when BUFM = 1.

1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

### bit 6 Unimplemented: Read as '0'

### bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

```

1111 = Interrupts at the completion of conversion for each 16<sup>th</sup> sample/convert sequence

```

1110 = Interrupts at the completion of conversion for each 15<sup>th</sup> sample/convert sequence

- •

0001 = Interrupts at the completion of conversion for each 2<sup>nd</sup> sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

### bit 1 BUFM: ADC Result Buffer Mode Select bit

- 1 = Buffer configured as two 8-word buffers, ADC1BUF7-ADC1BUF0, ADC1BUFF-ADCBUF8

- 0 = Buffer configured as one 16-word buffer ADC1BUFF-ADC1BUF0

### bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses Sample A input multiplexer settings for first sample, then alternates between Sample B and Sample A input multiplexer settings for all subsequent samples

- 0 = Always use Sample A input multiplexer settings

NOTES:

# TABLE 30-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARA         | CTERISTICS             | 6               | (unless other | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |             |  |  |  |

|------------------|------------------------|-----------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| Parameter<br>No. | Typical <sup>(3)</sup> | Max.            | Units         | Units Conditions                                                                                                                                                                                   |             |  |  |  |

| Operating (      | Current (IDD)          | (Notes 1, 2, 5) | )             |                                                                                                                                                                                                    |             |  |  |  |

| DC20             | 2                      | 3               | mA            | 4 M⊦                                                                                                                                                                                               | łz (Note 4) |  |  |  |

| DC21             | 7                      | 10.5            | mA            | 1                                                                                                                                                                                                  | 0 MHz       |  |  |  |

| DC22             | 10                     | 15              | mA            | 20 MI                                                                                                                                                                                              | Hz (Note 4) |  |  |  |

| DC23             | 15                     | 23              | mA            | 30 MHz (Note 4)                                                                                                                                                                                    |             |  |  |  |

| DC24             | 20                     | 30              | mA            | 40 MHz                                                                                                                                                                                             |             |  |  |  |

| DC25             | 100                    | 150             | μA            | +25°C, 3.3V LPRC (31 kHz) (Note 4)                                                                                                                                                                 |             |  |  |  |

**Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

- 2: The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, Program Flash, and SRAM data memory are operational, SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- CPU executing while(1) statement from Flash

- RTCC and JTAG are disabled

- **3:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: IPD electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

# TABLE 30-34: ADC MODULE SPECIFICATIONS

|               | AC CHAR    | ACTERISTICS                       | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 5): 2.5V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |              |      |       |                                                         |  |

|---------------|------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|-------|---------------------------------------------------------|--|

| Param.<br>No. | Symbol     | Characteristics                   | Min.                                                                                                                                                                                                                                                                                             | Typical      | Max. | Units | Conditions                                              |  |

| ADC Ac        | curacy – N | leasurements with Inter           | nal VREF+/V                                                                                                                                                                                                                                                                                      | REF-         |      |       | •                                                       |  |

| AD20d         | Nr         | Resolution                        |                                                                                                                                                                                                                                                                                                  | 10 data bits | 3    | bits  | (Note 3)                                                |  |

| AD21d         | INL        | Integral Non-linearity            | > -1                                                                                                                                                                                                                                                                                             | _            | < 1  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |

| AD22d         | DNL        | Differential Non-linearity        | > -1                                                                                                                                                                                                                                                                                             | —            | < 1  | LSb   | VINL = AVss = 0V,<br>AVDD = 2.5V to 3.6V<br>(Notes 2,3) |  |

| AD23d         | Gerr       | Gain Error                        | > -4                                                                                                                                                                                                                                                                                             | _            | < 4  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |

| AD24d         | EOFF       | Offset Error                      | > -2                                                                                                                                                                                                                                                                                             | _            | < 2  | Lsb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |

| AD25d         |            | Monotonicity                      |                                                                                                                                                                                                                                                                                                  |              | _    | _     | Guaranteed                                              |  |

| Dynami        | c Performa | ance                              | ·                                                                                                                                                                                                                                                                                                |              |      |       | <u> </u>                                                |  |

| AD32b         | SINAD      | Signal to Noise and<br>Distortion | 55                                                                                                                                                                                                                                                                                               | 58.5         | _    | dB    | (Notes 3,4)                                             |  |

| AD34b         | ENOB       | Effective Number of bits          | 9.0                                                                                                                                                                                                                                                                                              | 9.5          |      | bits  | (Notes 3,4)                                             |  |

**Note 1:** These parameters are not characterized or tested in manufacturing.

2: With no missing codes.

**3:** These parameters are characterized, but not tested in manufacturing.

4: Characterized with a 1 kHz sine wave.

**5:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

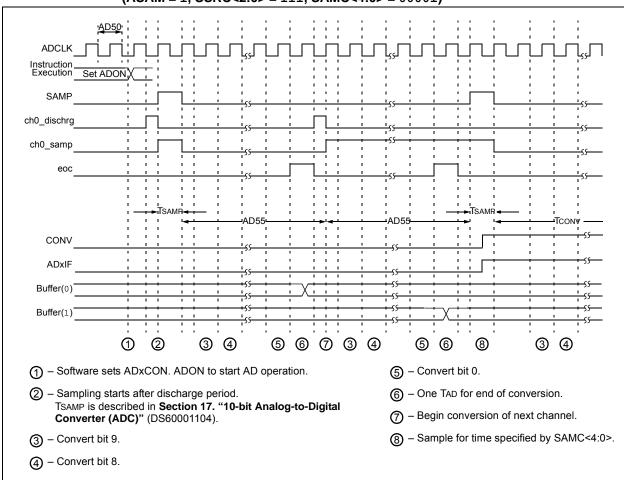

# FIGURE 30-19: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 1, SSRC<2:0> = 111, SAMC<4:0> = 00001)

|               |         |                                                                      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |       |      |       |            |  |

|---------------|---------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>                                       | Min.                                                                                                                                                                                                                                                                            | Тур.  | Max. | Units | Conditions |  |

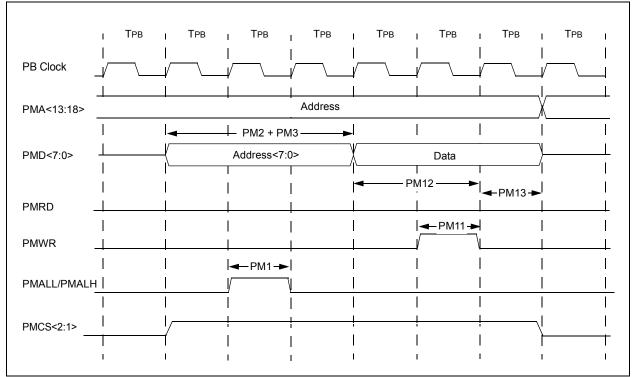

| PM1           | Tlat    | PMALL/PMALH Pulse Width                                              |                                                                                                                                                                                                                                                                                 | 1 Трв | _    | _     | _          |  |

| PM2           | TADSU   | Address Out Valid to<br>PMALL/PMALH Invalid (address<br>setup time)  | _                                                                                                                                                                                                                                                                               | 2 Трв | _    | _     | _          |  |

| PM3           | Tadhold | PMALL/PMALH Invalid to<br>Address Out Invalid (address<br>hold time) | —                                                                                                                                                                                                                                                                               | 1 Трв | _    | —     | _          |  |

| PM4           | TAHOLD  | PMRD Inactive to Address Out<br>Invalid<br>(address hold time)       | 5                                                                                                                                                                                                                                                                               | _     | _    | ns    | _          |  |

| PM5           | Trd     | PMRD Pulse Width                                                     | _                                                                                                                                                                                                                                                                               | 1 Трв | _    | _     | —          |  |

| PM6           | TDSU    | PMRD or PMENB Active to Data<br>In Valid (data setup time)           | 15                                                                                                                                                                                                                                                                              | —     | —    | ns    | _          |  |

| PM7           | TDHOLD  | PMRD or PMENB Inactive to Data In Invalid (data hold time)           | —                                                                                                                                                                                                                                                                               | 80    | —    | ns    |            |  |

### TABLE 30-38: PARALLEL MASTER PORT READ TIMING REQUIREMENTS

Note 1: These parameters are characterized, but not tested in manufacturing.

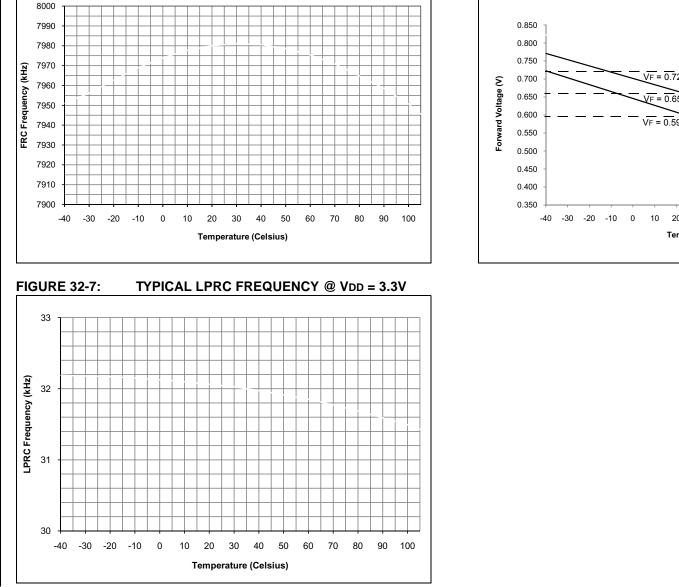

TYPICAL FRC FREQUENCY @ VDD = 3.3V

**FIGURE 32-6:**