#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0 0              |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 19                                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx220f032b-v-ss |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | Device Overview                                    |     |

|-------|----------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 32-bit MCUs    |     |

| 3.0   | CPU                                                |     |

| 4.0   | Memory Organization                                |     |

| 5.0   | Flash Program Memory                               | 53  |

| 6.0   | Resets                                             | 59  |

| 7.0   | Interrupt Controller                               | 63  |

| 8.0   | Oscillator Configuration                           | 73  |

| 9.0   | Direct Memory Access (DMA) Controller              | 83  |

| 10.0  | USB On-The-Go (OTG)                                | 103 |

| 11.0  | I/O Ports                                          | 127 |

| 12.0  | Timer1                                             | 143 |

| 13.0  | Timer2/3, Timer4/5                                 | 147 |

| 14.0  | Watchdog Timer (WDT)                               | 153 |

| 15.0  | Input Capture                                      | 157 |

| 16.0  | Output Compare                                     | 161 |

| 17.0  | Serial Peripheral Interface (SPI)                  |     |

| 18.0  | Inter-Integrated Circuit (I <sup>2</sup> C)        |     |

| 19.0  | Universal Asynchronous Receiver Transmitter (UART) | 181 |

|       | Parallel Master Port (PMP)                         |     |

|       | Real-Time Clock and Calendar (RTCC)                |     |

| 22.0  | 10-bit Analog-to-Digital Converter (ADC)           | 209 |

| 23.0  |                                                    |     |

| 24.0  | Comparator Voltage Reference (CVREF)               |     |

| 25.0  | Charge Time Measurement Unit (CTMU)                | 227 |

| 26.0  | Power-Saving Features                              | 233 |

| 27.0  | Special Features                                   | 239 |

| 28.0  | Instruction Set                                    |     |

| 29.0  | Development Support                                | 253 |

| 30.0  | Electrical Characteristics                         | 257 |

|       | 50 MHz Electrical Characteristics                  |     |

|       | DC and AC Device Characteristics Graphs            |     |

|       | Packaging Information                              |     |

| The I | Vicrochip Web Site                                 | 341 |

|       | omer Change Notification Service                   |     |

|       | omer Support                                       |     |

| Prod  | uct Identification System                          | 342 |

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

| Exception | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                               |

| DSS       | EJTAG debug single step.                                                                                                                |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                                |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                            |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                         |

| AdEL      | Fetch address alignment error.<br>Fetch reference to protected address.                                                                 |

| IBE       | Instruction fetch bus error.                                                                                                            |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                                      |

| Sys       | Execution of SYSCALL instruction.                                                                                                       |

| Вр        | Execution of BREAK instruction.                                                                                                         |

| RI        | Execution of a reserved instruction.                                                                                                    |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                           |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled.                                                                     |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                                 |

| Tr        | Execution of a trap (when trap condition is true).                                                                                      |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                           |

| AdEL      | Load address alignment error.<br>Load reference to protected address.                                                                   |

| AdES      | Store address alignment error.<br>Store to protected address.                                                                           |

| DBE       | Load or store bus error.                                                                                                                |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                            |

# TABLE 3-3: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE EXCEPTION TYPES

## 3.3 Power Management

The MIPS M4K processor core offers many power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or Halting the clocks, which reduces system power consumption during Idle periods.

#### 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see Section 26.0 "Power-Saving Features".

# 3.4 EJTAG Debug Support

The MIPS M4K processor core provides an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the M4K core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | —                 |                  | _                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        |                   | —                 | —                 | -                 | _                 | —                 |                  | _                |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |

| 15:8         | BMXDUPBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | BMXDU             | PBA<7:0>          |                   |                  |                  |  |  |  |

### REGISTER 4-4: BMXDUPBA: DATA RAM USER PROGRAM BASE ADDRESS REGISTER

## Legend:

| Legena.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUPBA<15:10>: DRM User Program Base Address bits

When non-zero, the value selects the relative base address for User mode program space in RAM, BMXDUPBA must be greater than BMXDUDBA.

bit 9-0 **BMXDUPBA<9:0>:** Read-Only bits This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 04.04        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |  |

| 31:24        | NVMKEY<31:24>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 00.40        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |  |

| 23:16        | NVMKEY<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |  |

| 15:8         | NVMKEY<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |  |

| 7:0          |                   |                   | •                 | NVMK              | NVMKEY<7:0>       |                   |                  |                  |  |  |  |  |  |  |

#### REGISTER 5-2: NVMKEY: PROGRAMMING UNLOCK REGISTER

# Legend:

| Legena.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-0 NVMKEY<31:0>: Unlock Register bits

These bits are write-only, and read as '0' on any read

Note: This register is used as part of the unlock sequence to prevent inadvertent writes to the PFM.

#### REGISTER 5-3: NVMADDR: FLASH ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | NVMADDR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | NVMADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | NVMADDR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | NVMAE             | )DR<7:0>          |                   |                  |                  |  |  |  |

| Legend:           |                                                               |                      |                    |  |

|-------------------|---------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | lable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                              | '0' = Bit is cleared | x = Bit is unknown |  |

bit 31-0 NVMADDR<31:0>: Flash Address bits

Bulk/Chip/PFM Erase: Address is ignored. Page Erase: Address identifies the page to erase. Row Program: Address identifies the row to program. Word Program: Address identifies the word to program. NOTES:

## TABLE 7-2: INTERRUPT REGISTER MAP (CONTINUED)

| ess                         |                                 | ¢,        | θits  |       |       |       |             |       |        |        |      |      |      |      |             |      |        |                  |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------------|-------|--------|--------|------|------|------|------|-------------|------|--------|------------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11       | 26/10 | 25/9   | 24/8   | 23/7 | 22/6 | 21/5 | 20/4 | 19/3        | 18/2 | 17/1   | 16/0             | All<br>Resets |

| 1100                        | 1007                            | 31:16     | _     | —     | —     |       | SPI1IP<2:0> |       | SPI1IS | S<1:0> | -    | —    | —    | US   | SBIP<2:0>(2 | :)   | USBIS  | <1:0> <b>(2)</b> | 0000          |

| 1100                        | IPC7                            | 15:0      | _     | -     | —     | (     | CMP3IP<2:0> | >     | CMP3IS | S<1:0> | _    | _    | _    | CI   | MP2IP<2:0>  | •    | CMP2I  | S<1:0>           | 0000          |

| 1110                        | IPC8                            | 31:16     | _     | _     | —     |       | PMPIP<2:0>  |       | PMPIS  | S<1:0> | _    | —    | _    | (    | CNIP<2:0>   |      | CNIS   | <1:0>            | 0000          |

| 1110                        | IPCo                            | 15:0      |       | —     | _     |       | I2C1IP<2:0> |       | I2C1IS | <1:0>  | —    | —    | _    | I    | J1IP<2:0>   |      | U1IS   | <1:0>            | 0000          |

| 1120                        | IPC9                            | 31:16     |       | —     | _     | (     | CTMUIP<2:0  | >     | CTMU   | S<1:0> | —    | —    | _    | 12   | 2C2IP<2:0>  |      | 12C218 | 6<1:0>           | 0000          |

| 1120                        | IFC9                            | 15:0      | -     | —     | _     |       | U2IP<2:0>   |       | U2IS<  | <1:0>  | _    | _    | _    | S    | PI2IP<2:0>  |      | SPI2IS | S<1:0>           | 0000          |

| 1130                        |                                 | 31:16     | —     | _     | —     | [     | DMA3IP<2:0> | >     | DMA3IS | S<1:0> | _    | —    | _    | DI   | MA2IP<2:0>  | •    | DMA2I  | S<1:0>           | 0000          |

| 1130                        | IPC10                           | 15:0      | _     | _     | _     | [     | DMA1IP<2:0> | >     | DMA1IS | S<1:0> | _    | _    | _    | DI   | VA0IP<2:0   | •    | DMA0I  | S<1:0>           | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX1XX devices.

3: This register does not have associated CLR, SET, INV registers.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | —                 | —                 | —                 |                   | IP03<2:0>         | IS03<1:0>         |                  |                  |  |

| 23:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23.10        | _                 | —                 |                   |                   | IP02<2:0>         |                   | IS02<1:0>        |                  |  |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15.0         | _                 | —                 |                   |                   | IP01<2:0>         |                   | IS01·            | <1:0>            |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7.0          | _                 | _                 | _                 |                   | IP00<2:0>         |                   | IS00·            | <1:0>            |  |

#### REGISTER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

#### Legend:

| Logonal           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-26 IP03<2:0>: Interrupt Priority bits

- 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1 000 = Interrupt is disabled bit 25-24 IS03<1:0>: Interrupt Subpriority bits 11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1 00 = Interrupt subpriority is 0 bit 23-21 Unimplemented: Read as '0' bit 20-18 IP02<2:0>: Interrupt Priority bits 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1 000 = Interrupt is disabled bit 17-16 IS02<1:0>: Interrupt Subpriority bits 11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1 00 = Interrupt subpriority is 0 bit 15-13 Unimplemented: Read as '0' bit 12-10 IP01<2:0>: Interrupt Priority bits 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1

- 000 = Interrupt is disabled

- **Note:** This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions.

# 8.1 Oscillator Control Regiters

| TABLE 8-1: OSCILLATOR CONTROL REGISTER MAP |                                 |           |                       |             |          |       |       |       |          |         |          |                      |        |       |           |                       |                     |       |           |

|--------------------------------------------|---------------------------------|-----------|-----------------------|-------------|----------|-------|-------|-------|----------|---------|----------|----------------------|--------|-------|-----------|-----------------------|---------------------|-------|-----------|

| ess                                        |                                 | 0         |                       | Bits        |          |       |       |       |          |         |          |                      |        |       | ú         |                       |                     |       |           |

| Virtual Address<br>(BF80_#)                | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15                 | 30/14       | 29/13    | 28/12 | 27/11 | 26/10 | 25/9     | 24/8    | 23/7     | 22/6                 | 21/5   | 20/4  | 19/3      | 18/2                  | 17/1                | 16/0  | All Reset |

| F000                                       | OSCCON                          | 31:16     | 1:16 — — PLLODIV<2:0> |             |          | )>    |       |       |          | SOSCRDY | PBDIVRDY | PBDI\                | /<1:0> | PL    | LMULT<2:0 | >                     | x1xx <sup>(2)</sup> |       |           |

| FUUU                                       | 030001                          | 15:0      | —                     |             | COSC<2:0 | V     | Ι     |       | NOSC<2:0 | >       | CLKLOCK  | ULOCK <sup>(3)</sup> | SLOCK  | SLPEN | CF        | UFRCEN <sup>(3)</sup> | SOSCEN              | OSWEN | xxxx(2)   |

| F010                                       | OSCTUN                          | 31:16     | _                     | _           |          | _     | _     |       |          | _       | _        | _                    | _      | _     |           | _                     | —                   | _     | 0000      |

| 1010                                       | 030101                          | 15:0      | _                     | _           |          | _     | _     |       |          | _       | _        | _                    |        |       | TUN       | l<5:0>                |                     |       | 0000      |

| 5000                                       |                                 | 31:16     | _                     |             |          |       |       |       |          |         | RODIV<1  | 4:0>                 |        |       |           |                       |                     |       | 0000      |

| F020                                       | REFOCON                         | 15:0      | ON                    |             | SIDL     | OE    | RSLP  | -     | DIVSWEN  | ACTIVE  | —        | —                    |        |       |           | ROSE                  | _<3:0>              |       | 0000      |

| F000                                       | DEEOTDIM                        | 31:16     |                       | ROTRIM<8:0> |          |       |       |       | _        | _       | _        | _                    | _      | _     | _         | 0000                  |                     |       |           |

| F030 F                                     | REFOTRIM                        | 15:0      | _                     | _           |          | _     | _     |       |          | -       | _        | _                    | _      | _     |           | _                     | —                   | _     | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

3: This bit is only available on PIC32MX2XX devices.

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6              | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-----------------------------|--------------------------------|-------------------|-------------------|---------------------|-------------------|------------------|------------------|--|--|--|

|              | U-0                         | R/W-0                          | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | _                           | – RODIV<14:8> <sup>(1,3)</sup> |                   |                   |                     |                   |                  |                  |  |  |  |

|              | R/W-0                       | R/W-0                          | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | RODIV<7:0> <sup>(1,3)</sup> |                                |                   |                   |                     |                   |                  |                  |  |  |  |

| 45.0         | R/W-0                       | U-0                            | R/W-0             | R/W-0             | R/W-0               | U-0               | R/W-0, HC        | R-0, HS, HC      |  |  |  |

| 15:8         | ON                          | _                              | SIDL              | OE                | RSLP <sup>(2)</sup> | _                 | DIVSWEN          | ACTIVE           |  |  |  |

|              | U-0                         | U-0                            | U-0               | U-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                             |                                |                   |                   |                     | ROSEL             | .<3:0>(1)        |                  |  |  |  |

#### REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| Legend:           | HC = Hardware Clearable | HS = Hardware Settable   |                    |  |  |

|-------------------|-------------------------|--------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |  |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |  |  |

bit 31 Unimplemented: Read as '0'

| bit 30-16 | RODIV<14:0> Reference Clock Divider bits <sup>(1,3)</sup>                           |

|-----------|-------------------------------------------------------------------------------------|

|           | The value selects the reference clock divider bits. See Figure 8-1 for information. |

| bit 15    | ON: Output Enable bit                                                               |

|           | 1 = Reference Oscillator module is enabled                                          |

|           | 0 = Reference Oscillator module is disabled                                         |

| bit 14    | Unimplemented: Read as '0'                                                          |

| bit 13    | SIDL: Peripheral Stop in Idle Mode bit                                              |

- 1 = Discontinue module operation when the device enters Idle mode

- 0 =Continue module operation when the device enters lide mode

- bit 12 **OE:** Reference Clock Output Enable bit

- 1 = Reference clock is driven out on REFCLKO pin

- 0 = Reference clock is not driven out on REFCLKO pin

- bit 11 RSLP: Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference Oscillator module output continues to run in Sleep

- 0 = Reference Oscillator module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 DIVSWEN: Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- bit 8 ACTIVE: Reference Clock Request Status bit

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- **2:** This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

## REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- bit 3-0 ROSEL<3:0>: Reference Clock Source Select bits<sup>(1)</sup>

- 1111 = Reserved; do not use

- 1001 = Reserved; do not use 1000 = REFCLKI 0111 = System PLL output 0110 = USB PLL output 0101 = Sosc 0100 = LPRC 0011 = FRC 0010 = POSC 0001 = PBCLK 0000 = SYSCLK

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- 2: This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| REGIST       | CONSTER 10-1. OTOTOIR. OSB OTO INTERROFT STATUS REGISTER |                   |                   |                   |                   |                   |                  |                  |  |  |

|--------------|----------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                                        | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 31:24        | U-0                                                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | -                                                        | —                 | —                 | -                 | -                 | —                 | -                | —                |  |  |

| 23:16        | U-0                                                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | -                                                        | —                 | —                 | -                 | -                 | —                 | -                | —                |  |  |

| 15:8         | U-0                                                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.6         |                                                          | _                 | -                 |                   |                   | —                 |                  | —                |  |  |

| 7.0          | R/WC-0, HS                                               | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS        | U-0              | R/WC-0, HS       |  |  |

| 7:0          | IDIF                                                     | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF           | SESENDIF          |                  | VBUSVDIF         |  |  |

## REGISTER 10-1: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable b           | pit                |  |

|-------------------|-------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIF:** ID State Change Indicator bit

- 1 = A change in the ID state was detected

- 0 = No change in the ID state was detected

- bit 6 T1MSECIF: 1 Millisecond Timer bit

- 1 = 1 millisecond timer has expired

- 0 = 1 millisecond timer has not expired

#### bit 5 LSTATEIF: Line State Stable Indicator bit

- 1 = USB line state has been stable for 1 ms, but different from last time

- 0 = USB line state has not been stable for 1 ms

- bit 4 ACTVIF: Bus Activity Indicator bit

- 1 = Activity on the D+, D-, ID or VBUS pins has caused the device to wake-up

- 0 = Activity has not been detected

- bit 3 SESVDIF: Session Valid Change Indicator bit

- 1 = VBUS voltage has dropped below the session end level

- 0 = VBUS voltage has not dropped below the session end level

- bit 2 SESENDIF: B-Device VBUS Change Indicator bit

- 1 = A change on the session end input was detected

- 0 = No change on the session end input was detected

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIF: A-Device VBUS Change Indicator bit

- 1 = A change on the session valid input was detected

- 0 = No change on the session valid input was detected

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

### REGISTER 10-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER (CONTINUED)

- bit 1 CRC5EF: CRC5 Host Error Flag bit<sup>(4)</sup>

- 1 = Token packet rejected due to CRC5 error

- 0 = Token packet accepted

- **EOFEF:** EOF Error Flag bit<sup>(3,5)</sup>

- 1 = An EOF error condition was detected

- 0 = No EOF error condition was detected

- bit 0 PIDEF: PID Check Failure Flag bit

- 1 = PID check failed

- 0 = PID check passed

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- **2:** This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | —                 | —                 | _                 | _                 | —                 | _                | —                |  |  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | -                | —                |  |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         | ON                | —                 | SIDL              | _                 | _                 | —                 | _                | _                |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7:0          |                   |                   |                   |                   |                   | _                 | _                | _                |  |  |

### **REGISTER 11-3:** CNCONX: CHANGE NOTICE CONTROL FOR PORTX REGISTER (X = A, B, C)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Change Notice (CN) Control ON bit

- 1 = CN is enabled

- 0 = CN is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Control bit

- 1 = Idle mode halts CN operation

- 0 = Idle does not affect CN operation

- bit 12-0 Unimplemented: Read as '0'

### REGISTER 15-1: ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER (CONTINUED)

ICM<2:0>: Input Capture Mode Select bits

bit 2-0

- 111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

- 110 = Simple Capture Event mode every edge, specified edge first and every edge thereafter

- 101 = Prescaled Capture Event mode every sixteenth rising edge

- 100 = Prescaled Capture Event mode every fourth rising edge

- 011 = Simple Capture Event mode every rising edge

- 010 = Simple Capture Event mode every falling edge

- 001 = Edge Detect mode every edge (rising and falling)

- 000 = Input Capture module is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### REGISTER 22-3: AD1CON3: ADC CONTROL REGISTER 3

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6        | Bit<br>29/21/13/5 | Bit<br>28/20/12/4        | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|--------------------------|-------------------|--------------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0                      | U-0               | U-0                      | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | —                        | —                 | _                        | —                 | —                 | —                | -                |  |  |  |

| 00.40        | U-0               | U-0                      | U-0               | U-0                      | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                        | —                 | _                        | —                 | —                 | _                | -                |  |  |  |

| 45.0         | R/W-0             | U-0                      | U-0               | R/W-0                    | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | ADRC              | _                        | —                 | SAMC<4:0> <sup>(1)</sup> |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0                    | R/W-0             | R/W-0                    | R/W-0             | R/W-0             | R/W              | R/W-0            |  |  |  |

| 7:0          |                   | ADCS<7:0> <sup>(2)</sup> |                   |                          |                   |                   |                  |                  |  |  |  |

## Legend:

| =ogona.           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | ead as '0'           |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ADRC: ADC Conversion Clock Source bit

- 1 = Clock derived from FRC

- 0 = Clock derived from Peripheral Bus Clock (PBCLK)

- bit 14-13 Unimplemented: Read as '0'

- - 00000001 =TPB • 2 • (ADCS<7:0> + 1) = 4 • TPB = TAD 00000000 =TPB • 2 • (ADCS<7:0> + 1) = 2 • TPB = TAD

- **Note 1:** This bit is only used if the SSRC<2:0> bits (AD1CON1<7:5>) = 111.

- **2:** This bit is not used if the ADRC (AD1CON3<15>) bit = 1.

### REGISTER 27-2: DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

#### bit 15-14 FCKSM<1:0>: Clock Switching and Monitor Selection Configuration bits

- 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled

- 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled

- 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled

- bit 13-12 FPBDIV<1:0>: Peripheral Bus Clock Divisor Default Value bits

- 11 = PBCLK is SYSCLK divided by 8

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- bit 11 Reserved: Write '1'

- bit 10 OSCIOFNC: CLKO Enable Configuration bit

- 1 = CLKO output disabled

- 0 = CLKO output signal active on the OSCO pin; Primary Oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 or 00)

#### bit 9-8 **POSCMOD<1:0>:** Primary Oscillator Configuration bits

- 11 = Primary Oscillator is disabled

- 10 = HS Oscillator mode is selected

- 01 = XT Oscillator mode is selected

- 00 = External Clock mode is selected

- bit 7 IESO: Internal External Switchover bit

- 1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled)

- 0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled)

- bit 6 **Reserved:** Write '1'

- bit 5 **FSOSCEN:** Secondary Oscillator Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

- bit 4-3 Reserved: Write '1'

- bit 2-0 **FNOSC<2:0>:** Oscillator Selection bits

- 111 = Fast RC Oscillator with divide-by-N (FRCDIV)

- 110 = FRCDIV16 Fast RC Oscillator with fixed divide-by-16 postscaler

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XT+PLL, HS+PLL, EC+PLL)

- 010 = Primary Oscillator (XT, HS, EC)<sup>(1)</sup>

- 001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)

- 000 = Fast RC Oscillator (FRC)

- **Note 1:** Do not disable the POSC (POSCMOD = 11) when using this oscillator source.

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3           | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-----------------------------|-------------------|---------------------|-------------------|-----------------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R                           | R                 | R                   | R                 | R                           | R                 | R                | R                |  |  |

| 31:24        |                             | VER<              | 3:0> <sup>(1)</sup> |                   | DEVID<27:24> <sup>(1)</sup> |                   |                  |                  |  |  |

| 00.40        | R                           | R                 | R                   | R                 | R                           | R                 | R                | R                |  |  |

| 23:16        | DEVID<23:16> <sup>(1)</sup> |                   |                     |                   |                             |                   |                  |                  |  |  |

| 45.0         | R                           | R                 | R                   | R                 | R                           | R                 | R                | R                |  |  |

| 15:8         | DEVID<15:8> <sup>(1)</sup>  |                   |                     |                   |                             |                   |                  |                  |  |  |

| 7.0          | R                           | R                 | R                   | R                 | R                           | R                 | R                | R                |  |  |

| 7:0          |                             |                   |                     | DEVID             | <7:0>(1)                    |                   |                  |                  |  |  |

## REGISTER 27-6: DEVID: DEVICE AND REVISION ID REGISTER

### Legend:

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 DEVID<27:0>: Device ID bits<sup>(1)</sup>

**Note 1:** See the "*PIC32 Flash Programming Specification*" (DS60001145) for a list of Revision and Device ID values.

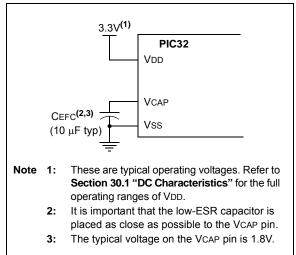

# 27.3 On-Chip Voltage Regulator

All PIC32MX1XX/2XX 28/36/44-pin Family devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX1XX/2XX 28/36/44-pin Family family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 30.1 "DC Characteristics"**.

| Note: | It is important that the low-ESR capacitor |

|-------|--------------------------------------------|

|       | is placed as close as possible to the VCAP |

|       | pin.                                       |

## 27.3.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

## 27.3.2 ON-CHIP REGULATOR AND BOR

PIC32MX1XX/2XX 28/36/44-pin Family devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specific in **Section 30.1 "DC Characteristics"**.

# FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

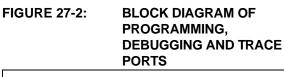

# 27.4 Programming and Diagnostics

PIC32MX1XX/2XX 28/36/44-pin Family devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

Figure 27-2 illustrates a block diagram of the programming, debugging, and trace ports.

| AC CHARAG                         | S <sup>(2)</sup> |                       |         |                 |                            |  |

|-----------------------------------|------------------|-----------------------|---------|-----------------|----------------------------|--|

| ADC Speed                         | TAD Min.         | Sampling<br>Time Min. | Rs Max. | Vdd             | ADC Channels Configuration |  |

| 1 Msps to 400 ksps <sup>(1)</sup> | 65 ns            | 132 ns                | 500Ω    | 3.0V to<br>3.6V | ANX CHX ADC                |  |

| Up to 400 ksps                    | 200 ns           | 200 ns                | 5.0 kΩ  | 2.5V to<br>3.6V | ANX CHX<br>ANX OF VREF-    |  |

#### TABLE 30-35:10-BIT CONVERSION RATE PARAMETERS

**Note 1:** External VREF- and VREF+ pins must be used for correct operation.

2: These parameters are characterized, but not tested in manufacturing.

**3:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

### TABLE 31-5: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                                                    | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |         |          |       |                               |  |

|--------------------|--------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|-------|-------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics                                                                    | Min.                                                                                                                                            | Typical | Max.     | Units | Conditions                    |  |

| MOS10              |        | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC<br>4                                                                                                                                         |         | 50<br>50 |       | EC (Note 2)<br>ECPLL (Note 1) |  |

Note 1: PLL input requirements: 4 MHz  $\leq$  FPLLIN  $\leq$  5 MHz (use PLL prescaler to reduce Fosc). This parameter is characterized, but tested at 10 MHz only at manufacturing.

**2:** This parameter is characterized, but not tested in manufacturing.

## TABLE 31-6:SPIX MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                    | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industria |         |      |       |            |

|--------------------|--------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|

| Param.<br>No.      | Symbol | Characteristics                    | Min.                                                                                                                                           | Typical | Max. | Units | Conditions |

| MSP10              | TscL   | SCKx Output Low Time<br>(Note 1,2) | Тѕск/2                                                                                                                                         |         | —    | ns    | _          |

| MSP11              | TscH   | SCKx Output High Time (Note 1,2)   | Тѕск/2                                                                                                                                         | _       | _    | ns    |            |

Note 1: These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

### TABLE 31-7: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                                     | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industria |        |      |      |       |            |

|--------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|-------|------------|

| Param.<br>No.      | Symbol Characteristics <sup>1</sup> |                                                                                                                                                |        | Тур. | Max. | Units | Conditions |

| MSP10              | TscL                                | SCKx Output Low Time<br>(Note 1,2)                                                                                                             | Тѕск/2 | —    | _    | ns    | —          |

| MSP11              | TSCH                                | SCKx Output High Time<br>(Note 1,2)                                                                                                            | Тѕск/2 | —    | —    | ns    | —          |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.