Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 19                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

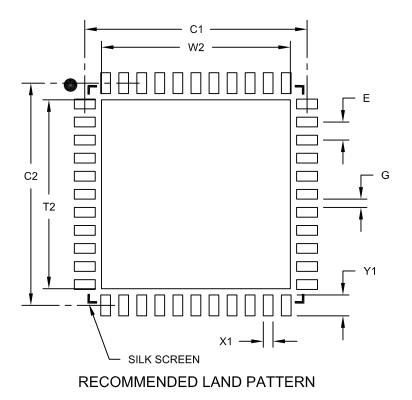

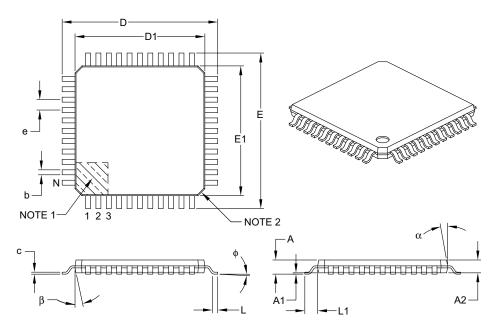

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx220f032bt-i-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 4:PIN NAMES FOR 28-PIN USB DEVICES

| 28                                              | PIN SOIC, SPDIP, SSOP (TOP VIEW) <sup>(1,2,3)</sup>                                                                                                                                                                                                                                                                                                                                     |                                                                |                                                                                                                                                                                                                    |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                 | 1<br>SSOP                                                                                                                                                                                                                                                                                                                                                                               | 28                                                             | 1 28 1 28<br>SOIC SPDIP                                                                                                                                                                                            |

|                                                 | PIC32MX210F016B<br>PIC32MX220F032B<br>PIC32MX230F064B<br>PIC32MX230F256B<br>PIC32MX250F128B<br>PIC32MX270F256B                                                                                                                                                                                                                                                                          |                                                                |                                                                                                                                                                                                                    |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                         |                                                                |                                                                                                                                                                                                                    |

| Pin #                                           | Full Pin Name                                                                                                                                                                                                                                                                                                                                                                           | Pin #                                                          | Full Pin Name                                                                                                                                                                                                      |

| <b>Pin #</b>                                    | Full Pin Name                                                                                                                                                                                                                                                                                                                                                                           | <b>Pin #</b>                                                   | Full Pin Name                                                                                                                                                                                                      |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                         |                                                                |                                                                                                                                                                                                                    |

| 1                                               | MCLR                                                                                                                                                                                                                                                                                                                                                                                    | 15                                                             | VBUS                                                                                                                                                                                                               |

| 1                                               | MCLR                                                                                                                                                                                                                                                                                                                                                                                    | 15                                                             | VBUS                                                                                                                                                                                                               |

|                                                 | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0                                                                                                                                                                                                                                                                                                                                        | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 1                                               | MCLR                                                                                                                                                                                                                                                                                                                                                                                    | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0                                                                                                                                                                                                                                                                                                                                        | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1                                                                                                                                                                                                                                                                                                                                              | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 1                                               | MCLR                                                                                                                                                                                                                                                                                                                                                                                    | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0                                                                                                                                                                                                                                                                                                                                        | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1                                                                                                                                                                                                                                                                                                                                              | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0                                                                                                                                                                                                                                                                                                                                               | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 1                                               | MCLR      PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0      PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1      PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0      PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1                                                                                                                                                                               | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 19                                                             | Vss                                                                                                                                                                                                                |

| 1                                               | MCLR      PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0      PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1      PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0      PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1      AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2                                                                                                                                | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 19                                                             | Vss                                                                                                                                                                                                                |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 20                                                             | Vcap                                                                                                                                                                                                               |

| 1                                               | MCLR      PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0      PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1      PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0      PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1      AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2      AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3                                                                                   | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 19                                                             | Vss                                                                                                                                                                                                                |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 20                                                             | Vcap                                                                                                                                                                                                               |

| 7                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 21                                                             | PGED2/RPB10/D+/CTED11/RB10                                                                                                                                                                                         |

| 1                                               | MCLR      PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0      PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1      PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0      PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1      AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2      AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3      Vss                                                                          | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 19                                                             | Vss                                                                                                                                                                                                                |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 20                                                             | Vcap                                                                                                                                                                                                               |

| 7                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 21                                                             | PGED2/RPB10/D+/CTED11/RB10                                                                                                                                                                                         |

| 8                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 22                                                             | PGEC2/RPB11/D-/RB11                                                                                                                                                                                                |

| 1                                               | MCLR      PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0      PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1      PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0      PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1      AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2      AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3      Vss      OSC1/CLKI/RPA2/RA2                                                  | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 19                                                             | Vss                                                                                                                                                                                                                |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 20                                                             | VCAP                                                                                                                                                                                                               |

| 7                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 21                                                             | PGED2/RPB10/D+/CTED11/RB10                                                                                                                                                                                         |

| 8                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 22                                                             | PGEC2/RPB11/D-/RB11                                                                                                                                                                                                |

| 9                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 23                                                             | VUSB3V3                                                                                                                                                                                                            |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10 | MCLR      PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0      PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1      PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0      PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1      AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2      AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3      Vss      OSC1/CLKI/RPA2/RA2      OSC2/CLKO/RPA3/PMA0/RA3                     | 15<br>16<br>17<br>18<br>19<br>20<br>21<br>21<br>22<br>23<br>24 | VBUS<br>TDI/RPB7/CTED3/PMD5/INT0/RB7<br>TCK/RPB8/SCL1/CTED10/PMD4/RB8<br>TDO/RPB9/SDA1/CTED4/PMD3/RB9<br>VSS<br>VCAP<br>PGED2/RPB10/D+/CTED11/RB10<br>PGEC2/RPB11/D-/RB11<br>VUSB3V3<br>AN11/RPB13/CTPLS/PMRD/RB13 |

| 1                                               | MCLR      PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0      PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1      PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0      PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1      AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2      AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3      Vss      OSC1/CLKI/RPA2/RA2      OSC2/CLKO/RPA3/PMA0/RA3      SOSCI/RPB4/RB4 | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 19                                                             | Vss                                                                                                                                                                                                                |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 20                                                             | VcAP                                                                                                                                                                                                               |

| 7                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 21                                                             | PGED2/RPB10/D+/CTED11/RB10                                                                                                                                                                                         |

| 8                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 22                                                             | PGEC2/RPB11/D-/RB11                                                                                                                                                                                                |

| 9                                               |                                                                                                                                                                                                                                                                                                                                                                                         | 23                                                             | VUSB3V3                                                                                                                                                                                                            |

| 10                                              |                                                                                                                                                                                                                                                                                                                                                                                         | 24                                                             | AN11/RPB13/CTPLS/PMRD/RB13                                                                                                                                                                                         |

| 11                                              |                                                                                                                                                                                                                                                                                                                                                                                         | 25                                                             | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB                                                                                                                                                                     |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

#### TABLE 1-1: **PINOUT I/O DESCRIPTIONS**

|          | Pin Number <sup>(1)</sup>                    |                                             |                                        |                                        |             |                |                                                                                                                                                                                                |  |

|----------|----------------------------------------------|---------------------------------------------|----------------------------------------|----------------------------------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name | 28-pin<br>28-pin SSOP/<br>QFN SPDIP/<br>SOIC |                                             | 36-pin<br>VTLA                         | 44-pin<br>QFN/<br>TQFP/<br>VTLA        | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                    |  |

| AN0      | 27                                           | 2                                           | 33                                     | 19                                     |             | Analog         | Analog input channels.                                                                                                                                                                         |  |

| AN1      | 28                                           | 3                                           | 34                                     | 20                                     | I           | Analog         |                                                                                                                                                                                                |  |

| AN2      | 1                                            | 4                                           | 35                                     | 21                                     |             | Analog         |                                                                                                                                                                                                |  |

| AN3      | 2                                            | 5                                           | 36                                     | 22                                     |             | Analog         |                                                                                                                                                                                                |  |

| AN4      | 3                                            | 6                                           | 1                                      | 23                                     | I           | Analog         |                                                                                                                                                                                                |  |

| AN5      | 4                                            | 7                                           | 2                                      | 24                                     | I           | Analog         |                                                                                                                                                                                                |  |

| AN6      | _                                            | _                                           | 3                                      | 25                                     | I           | Analog         |                                                                                                                                                                                                |  |

| AN7      | _                                            | _                                           | 4                                      | 26                                     | I           | Analog         |                                                                                                                                                                                                |  |

| AN8      | _                                            | _                                           | _                                      | 27                                     | I           | Analog         |                                                                                                                                                                                                |  |

| AN9      | 23                                           | 26                                          | 29                                     | 15                                     | I           | Analog         |                                                                                                                                                                                                |  |

| AN10     | 22                                           | 25                                          | 28                                     | 14                                     | I           | Analog         |                                                                                                                                                                                                |  |

| AN11     | 21                                           | 24                                          | 27                                     | 11                                     | I           | Analog         |                                                                                                                                                                                                |  |

| AN12     | 20 <sup>(2)</sup>                            | 23 <sup>(2)</sup>                           | 26 <sup>(2)</sup><br>11 <sup>(3)</sup> | 10 <sup>(2)</sup><br>36 <sup>(3)</sup> | 1           | Analog         | *                                                                                                                                                                                              |  |

| CLKI     | 6                                            | 9                                           | 7                                      | 30                                     | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                         |  |

| CLKO     | 7                                            | 10                                          | 8                                      | 31                                     | 0           | _              | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes. Always associated<br>with OSC2 pin function. |  |

| OSC1     | 6                                            | 9                                           | 7                                      | 30                                     | I           | ST/CMOS        | -                                                                                                                                                                                              |  |

| OSC2     | 7                                            | 10                                          | 8                                      | 31                                     | 0           | -              | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes.                                              |  |

| SOSCI    | 8                                            | 11                                          | 9                                      | 33                                     | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal<br>input; CMOS otherwise.                                                                                                                              |  |

| SOSCO    | 9                                            | 12                                          | 10                                     | 34                                     | 0           | —              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                |  |

| REFCLKI  | PPS                                          | PPS                                         | PPS                                    | PPS                                    |             | ST             | Reference Input Clock                                                                                                                                                                          |  |

| REFCLKO  | PPS                                          | PPS                                         | PPS                                    | PPS                                    | 0           | —              | Reference Output Clock                                                                                                                                                                         |  |

| IC1      | PPS                                          | PPS                                         | PPS                                    | PPS                                    |             | ST             | Capture Inputs 1-5                                                                                                                                                                             |  |

| IC2      | PPS                                          | PPS                                         | PPS                                    | PPS                                    | 1           | ST             | 1                                                                                                                                                                                              |  |

| IC3      | PPS                                          | PPS                                         | PPS                                    | PPS                                    | 1           | ST             | 1                                                                                                                                                                                              |  |

| IC4      | PPS                                          | PPS                                         | PPS                                    | PPS                                    |             | ST             | 1                                                                                                                                                                                              |  |

| IC5      | PPS                                          | PPS                                         | PPS                                    | PPS                                    |             | ST             | 1                                                                                                                                                                                              |  |

|          | ST = Schm                                    | MOS compa<br>itt Trigger in<br>input buffer |                                        |                                        | •           | O = Outp       | Analog inputP = PowerutI = Inputeripheral Pin Select— = N/A                                                                                                                                    |  |

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability. 2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site:

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- *"MPLAB<sup>®</sup> ICD 3 Design Advisory"* (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

## 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

## 2.7 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

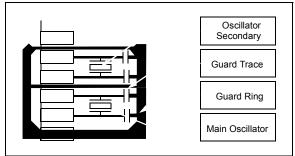

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

## 2.8 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

| REGIST  | ER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER (CONTINUED)                                                         |

|---------|-----------------------------------------------------------------------------------------------------------------------|

| bit 9-8 | IS01<1:0>: Interrupt Subpriority bits                                                                                 |

|         | 11 = Interrupt subpriority is 3                                                                                       |

|         | 10 = Interrupt subpriority is 2                                                                                       |

|         | 01 = Interrupt subpriority is 1                                                                                       |

|         | 00 = Interrupt subpriority is 0                                                                                       |

| bit 7-5 | Unimplemented: Read as '0'                                                                                            |

| bit 4-2 | IP00<2:0>: Interrupt Priority bits                                                                                    |

|         | 111 = Interrupt priority is 7                                                                                         |

|         | •                                                                                                                     |

|         | •                                                                                                                     |

|         | •                                                                                                                     |

|         | 010 = Interrupt priority is 2                                                                                         |

|         | 001 = Interrupt priority is 1                                                                                         |

|         | 000 = Interrupt is disabled                                                                                           |

| bit 1-0 | IS00<1:0>: Interrupt Subpriority bits                                                                                 |

|         | 11 = Interrupt subpriority is 3                                                                                       |

|         | 10 = Interrupt subpriority is 2                                                                                       |

|         | 01 = Interrupt subpriority is 1                                                                                       |

|         | 00 = Interrupt subpriority is 0                                                                                       |

| Note:   | This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions. |

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | —                 | _                 | —                 | —                 | _                 | _                | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | _                 | —                 | —                 | —                 | _                | —                |  |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |

| 15:8         | ON <sup>(1)</sup> | —                 | _                 | SUSPEND           | DMABUSY           | _                 | _                | —                |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

## REGISTER 9-1: DMACON: DMA CONTROLLER CONTROL REGISTER

#### Legend:

| 0                 |                               |                      |                    |

|-------------------|-------------------------------|----------------------|--------------------|

| R = Readable bit  | Readable bit W = Writable bit |                      | nd as '0'          |

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: DMA On bit<sup>(1)</sup>

- 1 = DMA module is enabled

- 0 = DMA module is disabled

- bit 14-13 **Unimplemented:** Read as '0'

- bit 12 SUSPEND: DMA Suspend bit

- 1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

- 0 = DMA operates normally

#### bit 11 DMABUSY: DMA Module Busy bit

- 1 = DMA module is active

- 0 = DMA module is disabled and not actively transferring data

- bit 10-0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-----------------------|-------------------|-------------------|--------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0              | U-0               | U-0              | R/W-0            |

| 31:24        | —                 | _                     | BYTC              | <1:0>             | WBO <sup>(1)</sup> | —                 | _                | BITO             |

| 22:16        | U-0               | U-0                   | U-0               | U-0               | U-0                | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                     | —                 | _                 | —                  | —                 | _                | _                |

| 45.0         | U-0               | U-0                   | U-0               | R/W-0             | R/W-0              | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   | _                     | _                 | PLEN<4:0>         |                    |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0                | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> | CRCTYP            | _                 | _                  | (                 | CRCCH<2:0>       |                  |

## Legend:

| Logona.           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-30 Unimplemented: Read as '0'

- bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (i.e., source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (i.e., reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (i.e., reverse source byte order)

- 00 = No swapping (i.e., source byte order)

- bit 27 **WBO:** CRC Write Byte Order Selection bit<sup>(1)</sup>

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (i.e., reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (i.e., not reflected)

#### <u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (i.e., reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (i.e., not reflected)

#### bit 23-13 Unimplemented: Read as '0'

bit 12-8 **PLEN<4:0>:** Polynomial Length bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): These bits are unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Denotes the length of the polynomial -1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- Note 1: When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

| Bit<br>Range      | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24             | DCRCDATA<31:24>   |                   |                   |                   |                   |                   |                  |                  |

| 00.10             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16             |                   |                   |                   | DCRCDAT           | 4<23:16>          |                   |                  |                  |

| 15.0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8              | DCRCDATA<15:8>    |                   |                   |                   |                   |                   |                  |                  |

| 7.0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0 DCRCDATA<7:0> |                   |                   |                   |                   |                   |                   |                  |                  |

#### REGISTER 9-5: DCRCDATA: DMA CRC DATA REGISTER

## Legend:

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.