Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 19                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx220f032bt-v-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|----------------------|---------------------|-------------------|-------------------|-----------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0                  | R/W-y               | R/W-y             | R/W-y             | R/W-0                 | R/W-0            | R/W-1            |  |  |  |

| 31:24        | —                 | —                    | Р                   | LLODIV<2:0        | <b>`</b>          | F                     | RCDIV<2:0>       |                  |  |  |  |

| 00.40        | U-0               | R-0                  | R-1                 | R/W-y             | R/W-y             | R/W-y                 | R/W-y            | R/W-y            |  |  |  |

| 23:16        | —                 | SOSCRDY              | CRDY PBDIVRDY PBDIN |                   |                   | Р                     | LLMULT<2:0>      | •                |  |  |  |

| 45.0         | U-0               | R-0                  | R-0                 | R-0               | U-0               | R/W-y                 | R/W-y            | R/W-y            |  |  |  |

| 15:8         | —                 |                      | COSC<2:0>           |                   | —                 |                       | NOSC<2:0>        |                  |  |  |  |

| 7:0          | R/W-0             | R-0                  | R-0                 | R/W-0             | R/W-0             | R/W-0                 | R/W-y            | R/W-0            |  |  |  |

| 7:0          | CLKLOCK           | ULOCK <sup>(1)</sup> | SLOCK               | SLPEN             | CF                | UFRCEN <sup>(1)</sup> | SOSCEN           | OSWEN            |  |  |  |

#### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| Legend:      y = Value set from Configuration bits on POR |                  |                      |                    |  |  |  |

|-----------------------------------------------------------|------------------|----------------------|--------------------|--|--|--|

| R = Readable bit                                          | W = Writable bit | U = Unimplemented bi | t, read as '0'     |  |  |  |

| -n = Value at POR                                         | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |  |  |

#### bit 31-30 **Unimplemented:** Read as '0'

#### bit 29-27 **PLLODIV<2:0>:** Output Divider for PLL

- 111 = PLL output divided by 256

- 110 = PLL output divided by 64

- 101 = PLL output divided by 32

- 100 = PLL output divided by 16

- 011 = PLL output divided by 8

- 010 = PLL output divided by 4

- 001 = PLL output divided by 2

- 000 = PLL output divided by 1

#### bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2 (default setting)

- 000 = FRC divided by 1

- bit 23 Unimplemented: Read as '0'

- bit 22 SOSCRDY: Secondary Oscillator (Sosc) Ready Indicator bit

- 1 = The Secondary Oscillator is running and is stable

- 0 = The Secondary Oscillator is still warming up or is turned off

- bit 21 **PBDIVRDY:** Peripheral Bus Clock (PBCLK) Divisor Ready bit

- 1 = PBDIV<1:0> bits can be written

- 0 = PBDIV<1:0> bits cannot be written

- bit 20-19 **PBDIV<1:0>:** Peripheral Bus Clock (PBCLK) Divisor bits

- 11 = PBCLK is SYSCLK divided by 8 (default)

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

Note 1: This bit is only available on PIC32MX2XX devices.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6            | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|------------------------------|-------------------|-------------------|---------------------|-------------------|------------------|------------------|--|--|--|--|

|              | U-0               | R/W-0                        | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | _                 | RODIV<14:8> <sup>(1,3)</sup> |                   |                   |                     |                   |                  |                  |  |  |  |  |

|              | R/W-0             | R/W-0                        | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        |                   | RODIV<7:0> <sup>(1,3)</sup>  |                   |                   |                     |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | U-0                          | R/W-0             | R/W-0             | R/W-0               | U-0               | R/W-0, HC        | R-0, HS, HC      |  |  |  |  |

| 15:8         | ON                | _                            | SIDL              | OE                | RSLP <sup>(2)</sup> | _                 | DIVSWEN          | ACTIVE           |  |  |  |  |

|              | U-0               | U-0                          | U-0               | U-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                              |                   |                   |                     | ROSEL             | .<3:0>(1)        |                  |  |  |  |  |

#### REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| Legend:           | HC = Hardware Clearable | HS = Hardware Settable   |                    |

|-------------------|-------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |

bit 31 Unimplemented: Read as '0'

| bit 30-16 | RODIV<14:0> Reference Clock Divider bits <sup>(1,3)</sup>                           |

|-----------|-------------------------------------------------------------------------------------|

|           | The value selects the reference clock divider bits. See Figure 8-1 for information. |

| bit 15    | ON: Output Enable bit                                                               |

|           | 1 = Reference Oscillator module is enabled                                          |

|           | 0 = Reference Oscillator module is disabled                                         |

| bit 14    | Unimplemented: Read as '0'                                                          |

| bit 13    | SIDL: Peripheral Stop in Idle Mode bit                                              |

- 1 = Discontinue module operation when the device enters Idle mode

- 0 =Continue module operation when the device enters lide mode

- bit 12 **OE:** Reference Clock Output Enable bit

- 1 = Reference clock is driven out on REFCLKO pin

- 0 = Reference clock is not driven out on REFCLKO pin

- bit 11 RSLP: Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference Oscillator module output continues to run in Sleep

- 0 = Reference Oscillator module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 DIVSWEN: Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- bit 8 ACTIVE: Reference Clock Request Status bit

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- **2:** This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

# 11.3 Peripheral Pin Select

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin-count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only option.

The Peripheral Pin Select (PPS) configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The PPS configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

# 11.3.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the PPS feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

# 11.3.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digitalonly peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital-only peripheral modules are never included in the PPS feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin.

Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.3.3 CONTROLLING PERIPHERAL PIN SELECT

PPS features are controlled through two sets of SFRs: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

# 11.3.4 INPUT MAPPING

The inputs of the PPS options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The [*pin name*]R registers, where [*pin name*] refers to the peripheral pins listed in Table 11-1, are used to configure peripheral input mapping (see Register 11-1). Each register contains sets of 4 bit fields. Programming these bit fields with an appropriate value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field is shown in Table 11-1.

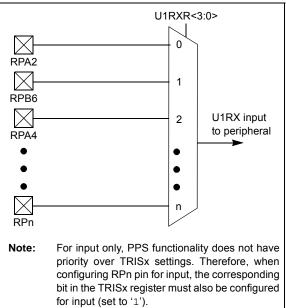

For example, Figure 11-2 illustrates the remappable pin selection for the U1RX input.

#### FIGURE 11-2: REMAPPABLE INPUT EXAMPLE FOR U1RX

# 11.4 Ports Control Registers

# TABLE 11-3: PORTA REGISTER MAP

| ess                         |                                 | 0         |       |       |       |       |       |                          |                       | Bits                    | 6                       |      |      |          |          |          |          |          | 6          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|--------------------------|-----------------------|-------------------------|-------------------------|------|------|----------|----------|----------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10                    | 25/9                  | 24/8                    | 23/7                    | 22/6 | 21/5 | 20/4     | 19/3     | 18/2     | 17/1     | 16/0     | All Resets |

| 6000                        | ANSELA                          | 31:16     | _     | —     | —     | —     | _     | _                        | _                     | _                       | —                       |      |      | _        | _        | —        | —        | _        | 0000       |

|                             |                                 | 15:0      | _     | —     | —     | —     | —     | -                        |                       |                         | —                       | _    | —    | —        | _        | _        | ANSA1    | ANSA0    | 0003       |

| 6010                        | TRISA                           | 31:16     | _     | —     | —     | —     | —     | —                        |                       |                         | —                       | _    | —    |          | —        | _        | _        | —        | 0000       |

| 0010                        |                                 | 15:0      | —     | —     | —     | —     | _     | TRISA10 <sup>(2)</sup>   | TRISA9 <sup>(2)</sup> | TRISA8 <sup>(2)</sup>   | TRISA7 <sup>(2)</sup>   | _    | —    | TRISA4   | TRISA3   | TRISA2   | TRISA1   | TRISA0   | 079F       |

| 6020                        | PORTA                           | 31:16     | —     | —     | —     | —     | _     | —                        | —                     | _                       | —                       | _    | —    |          |          |          |          |          | 0000       |

| 0020                        |                                 | 15:0      | —     | —     | —     | —     | _     | RA10 <sup>(2)</sup>      | RA9 <sup>(2)</sup>    | RA8 <sup>(2)</sup>      | RA7 <sup>(2)</sup>      | _    | —    | RA4      | RA3      | RA2      | RA1      | RA0      | xxxx       |

| 6030                        | LATA                            | 31:16     | _     | —     | —     | —     | _     |                          | _                     | _                       | —                       | —    | —    | _        | _        | _        |          | _        | 0000       |

| 0000                        |                                 | 15:0      | —     | —     | —     | —     | —     | LATA10 <sup>(2)</sup>    | LATA9 <sup>(2)</sup>  | LATA8 <sup>(2)</sup>    | LATA7 <sup>(2)</sup>    | —    | —    | LATA4    | LATA3    | LATA2    | LATA1    | LATA0    | xxxx       |

| 6040                        | ODCA                            | 31:16     | —     | —     | —     | —     | —     | —                        | _                     | _                       | —                       | —    | —    | —        |          | —        |          |          | 0000       |

| 0040                        | ODOA                            | 15:0      | —     | —     | —     | —     | —     | ODCA10 <sup>(2)</sup>    | ODCA9 <sup>(2)</sup>  | ODCA8 <sup>(2)</sup>    | ODCA7 <sup>(2)</sup>    | —    | —    | ODCA4    | ODCA3    | ODCA2    | ODCA1    | ODCA0    | 0000       |

| 6050                        | CNPUA                           | 31:16     | —     | —     | —     | —     | —     | —                        | _                     | _                       | —                       | —    | —    | —        |          | —        |          |          | 0000       |

| 0030                        | CINFUA                          | 15:0      | _     | _     | —     | —     | _     | CNPUA10 <sup>(2)</sup>   | CNPUA9 <sup>(2)</sup> | CNPUA8 <sup>(2)</sup>   | CNPUA7 <sup>(2)</sup>   | _    | —    | CNPUA4   | CNPUA3   | CNPUA2   | CNPUA1   | CNPUA0   | 0000       |

| 6060                        | CNPDA                           | 31:16     | —     | —     | —     | —     |       | _                        |                       |                         |                         | —    | —    |          |          | —        |          |          | 0000       |

| 0000                        | CINFDA                          | 15:0      | _     | _     | —     | —     | _     | CNPDA10 <sup>(2)</sup>   | CNPDA9 <sup>(2)</sup> | CNPDA8 <sup>(2)</sup>   | CNPDA7 <sup>(2)</sup>   | _    | —    | CNPDA4   | CNPDA3   | CNPDA2   | CNPDA1   | CNPDA0   | 0000       |

| 6070                        | CNCONA                          | 31:16     | —     | —     | —     | —     |       | _                        |                       | _                       | _                       | —    | —    |          |          | —        |          |          | 0000       |

| 0070                        | CINCONA                         | 15:0      | ON    | —     | SIDL  | —     | _     | _                        | _                     | _                       | —                       | _    | _    | _        | —        | —        | —        | —        | 0000       |

| 6080                        | CNENA                           | 31:16     | _     | —     | —     | —     | _     | _                        | _                     | _                       | —                       | _    | —    | —        | _        | _        | _        | _        | 0000       |

| 0000                        | CINEINA                         | 15:0      | _     | _     | —     | —     |       | CNIEA10 <sup>(2)</sup>   | CNIEA9 <sup>(2)</sup> | CNIEA8 <sup>(2)</sup>   | CNIEA7 <sup>(2)</sup>   |      |      | CNIEA4   | CNIEA3   | CNIEA2   | CNIEA1   | CNIEA0   | 0000       |

| 6000                        | CNISTATA                        | 31:16     | _     | _     | —     | —     |       |                          |                       |                         | _                       |      | _    |          |          | —        | _        |          | 0000       |

| 0090                        | CNSTATA                         | 15:0      | _     | _     | —     | —     |       | CNSTATA10 <sup>(2)</sup> | CNSTATA9(2)           | CNSTATA8 <sup>(2)</sup> | CNSTATA7 <sup>(2)</sup> |      |      | CNSTATA4 | CNSTATA3 | CNSTATA2 | CNSTATA1 | CNSTATA0 | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This bit is only available on 44-pin devices.

# TABLE 11-7: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| Bits                        |                      |           |       |       |       |       |       |       |      |      |      |      |      |      |      |      |       |      |            |

|-----------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|-------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0 | All Resets |

| 5000                        | RPC8R <sup>(1)</sup> | 31:16     | _     | —     | —     | —     | —     | _     | —    | —    | _    | —    | —    | —    | _    | —    | —     | —    | 0000       |

| FB8C                        | RPCort               | 15:0      | —     | —     | —     | —     | —     | _     | —    | —    | _    | —    | —    | —    |      | RPC8 | <3:0> |      | 0000       |

| 5000                        | RPC9R <sup>(3)</sup> | 31:16     | —     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | _    | _    | —    | —     |      | 0000       |

| FB90                        | RPC9R**              | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    |      | RPC  | <3:0> |      | 0000       |

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1:

2:

This register is only available on 44-pin devices. This register is only available on PIC32MX1XX devices. This register is only available on 36-pin and 44-pin devices. 3:

|              |                   |                   |                   |                   |                   |                   |                  | ., _, _,         |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04-04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | _                 |                   |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | -                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 | SIDL              | _                 | _                 |                   |                  | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          |                   | _                 |                   |                   |                   |                   | _                | _                |

# **REGISTER 11-3:** CNCONX: CHANGE NOTICE CONTROL FOR PORTX REGISTER (X = A, B, C)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Change Notice (CN) Control ON bit

- 1 = CN is enabled

- 0 = CN is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Control bit

- 1 = Idle mode halts CN operation

- 0 = Idle does not affect CN operation

- bit 12-0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                   | _                 | _                 | _                 | _                 | _                 | —                | _                |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                   | _                 | _                 | _                 | _                 | _                 | —                | _                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> | _                 | _                 | _                 | —                 | _                 | —                | _                |

| 7.0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          | _                   |                   |                   | WDTWINEN          | WDTCLR            |                   |                  |                  |

#### REGISTER 14-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Configuration bits on POR       |                      |                    |  |  |  |  |  |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|--|--|--|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |  |  |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

- 1 = Enables the WDT if it is not enabled by the device configuration

- 0 = Disable the WDT if it was enabled in software

- bit 14-7 Unimplemented: Read as '0'

- bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> of Configuration bits.

- bit 1 WDTWINEN: Watchdog Timer Window Enable bit

- 1 = Enable windowed Watchdog Timer

- 0 = Disable windowed Watchdog Timer

- bit 0 **WDTCLR:** Watchdog Timer Reset bit

- 1 = Writing a '1' will clear the WDT

- 0 = Software cannot force this bit to a '0'

- **Note 1:** A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

NOTES:

NOTES:

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | -                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 45.0         | R-0               | R/W-0, HSC        | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | IBF               | IBOV              | _                 | _                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7.0          | R-1               | R/W-0, HSC        | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          | OBE               | OBUF              |                   | _                 | OB3E              | OB2E              | OB1E             | OB0E             |

#### REGISTER 20-5: PMSTAT: PARALLEL PORT STATUS REGISTER (SLAVE MODES ONLY)

| Legend:           | HSC = Set by Hardware; Cleared by Software |                          |                    |  |  |  |

|-------------------|--------------------------------------------|--------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                           | U = Unimplemented bit, r | ead as '0'         |  |  |  |

| -n = Value at POR | '1' = Bit is set                           | '0' = Bit is cleared     | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 IBF: Input Buffer Full Status bit

- 1 = All writable input buffer registers are full

- 0 = Some or all of the writable input buffer registers are empty

- bit 14 IBOV: Input Buffer Overflow Status bit

- 1 = A write attempt to a full input byte buffer occurred (must be cleared in software)0 = No overflow occurred

- bit 13-12 Unimplemented: Read as '0'

- bit 11-8 IBxF: Input Buffer 'x' Status Full bits

- 1 = Input Buffer contains data that has not been read (reading buffer will clear this bit)

- 0 = Input Buffer does not contain any unread data

- bit 7 **OBE:** Output Buffer Empty Status bit

- 1 = All readable output buffer registers are empty

- 0 = Some or all of the readable output buffer registers are full

- bit 6 **OBUF:** Output Buffer Underflow Status bit

- 1 = A read occurred from an empty output byte buffer (must be cleared in software)

0 = No underflow occurred

- bit 5-4 Unimplemented: Read as '0'

- bit 3-0 **OBxE:** Output Buffer 'x' Status Empty bits

- 1 = Output buffer is empty (writing data to the buffer will clear this bit)

- 0 = Output buffer contains data that has not been transmitted

#### TABLE 26-2: PERIPHERAL MODULE DISABLE REGISTER MAP

| ess                         |                                 |           | Bits  |       |       |       |       |       | 6      |        |      |      |      |       |       |        |        |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|--------|--------|------|------|------|-------|-------|--------|--------|--------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8   | 23/7 | 22/6 | 21/5 | 20/4  | 19/3  | 18/2   | 17/1   | 16/0   | All Resets |

| F0.40                       | PMD1                            | 31:16     | —     | —     | _     | —     | _     | _     | _      | —      | —    | —    | —    | —     | _     | —      | —      | —      | 0000       |

| F240                        | FIVIDI                          | 15:0      | -     |       |       | CVRMD | Ι     |       |        | CTMUMD | —    | -    |      | -     |       |        | —      | AD1MD  | 0000       |

| 5250                        | PMD2                            | 31:16     | —     | —     |       | —     | _     | _     |        | —      | —    | —    | —    | —     | _     | —      | —      | —      | 0000       |

| F250                        | FIVIDZ                          | 15:0      | -     |       |       | —     | Ι     |       |        | —      | —    | -    |      | -     |       | CMP3MD | CMP2MD | CMP1MD | 0000       |

| F260                        | PMD3                            | 31:16     | _     |       |       | _     | -     |       |        | _      | _    |      | _    | OC5MD | OC4MD | OC3MD  | OC2MD  | OC1MD  | 0000       |

| F200                        | FIVIDS                          | 15:0      | _     |       |       | _     | -     |       |        | _      | _    |      | _    | IC5MD | IC4MD | IC3MD  | IC2MD  | IC1MD  | 0000       |

| F270                        | PMD4                            | 31:16     | _     |       |       | _     | -     |       |        | _      | _    |      | _    | -     | _     | _      | —      | _      | 0000       |

| F270                        | F IVID4                         | 15:0      | _     |       |       | _     | -     |       |        | _      | _    |      | _    | T5MD  | T4MD  | T3MD   | T2MD   | T1MD   | 0000       |

| F280                        | PMD5                            | 31:16     | _     |       |       | _     | -     |       |        | USB1MD | _    |      | _    | -     | _     | _      | I2C1MD | I2C1MD | 0000       |

| F200                        | FIVIDS                          | 15:0      | _     |       |       | _     | -     |       | SPI2MD | SPI1MD | _    |      | _    | -     | _     | _      | U2MD   | U1MD   | 0000       |

| F200                        | PMD6                            | 31:16     | _     | —     |       | —     | _     | _     |        | _      | —    | _    | —    | _     | _     | —      | —      | PMPMD  | 0000       |

| F290                        | I WD0                           | 15:0      | —     | _     | _     | —     | _     | _     | -      | —      | —    | _    | _    | _     | _     | _      | REFOMD | RTCCMD | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

# 28.0 INSTRUCTION SET

The PIC32MX1XX/2XX family instruction set complies with the MIPS32<sup>®</sup> Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- · Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

**Note:** Refer to "*MIPS32*<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set" at www.imgtec.com for more information.

|               |         |                                                         | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) |                                                                                                                                                                                            |            |       |                                                   |  |  |  |

|---------------|---------|---------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|---------------------------------------------------|--|--|--|

|               | ARACTER |                                                         | Operating tempe                                                       | $\begin{array}{ll} \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |            |       |                                                   |  |  |  |

| Param.<br>No. | Symbol  | Characteristics                                         | Min.                                                                  | Typical <sup>(1)</sup>                                                                                                                                                                     | Max.       | Units | Conditions                                        |  |  |  |

|               | VIL     | Input Low Voltage                                       |                                                                       |                                                                                                                                                                                            |            |       |                                                   |  |  |  |

| DI10          |         | I/O Pins with PMP                                       | Vss                                                                   | —                                                                                                                                                                                          | 0.15 Vdd   | V     |                                                   |  |  |  |

|               |         | I/O Pins                                                | Vss                                                                   | —                                                                                                                                                                                          | 0.2 Vdd    | V     |                                                   |  |  |  |

| DI18          |         | SDAx, SCLx                                              | Vss                                                                   | _                                                                                                                                                                                          | 0.3 Vdd    | V     | SMBus disabled<br>(Note 4)                        |  |  |  |

| DI19          |         | SDAx, SCLx                                              | Vss                                                                   | —                                                                                                                                                                                          | 0.8        | V     | SMBus enabled<br>(Note 4)                         |  |  |  |

|               | VIH     | Input High Voltage                                      |                                                                       |                                                                                                                                                                                            |            |       |                                                   |  |  |  |

| DI20          |         | I/O Pins not 5V-tolerant <sup>(5)</sup>                 | 0.65 VDD                                                              | _                                                                                                                                                                                          | Vdd        | V     | (Note 4,6)                                        |  |  |  |

|               |         | I/O Pins 5V-tolerant with<br>PMP <sup>(5)</sup>         | 0.25 VDD + 0.8V                                                       | —                                                                                                                                                                                          | 5.5        | V     | (Note 4,6)                                        |  |  |  |

|               |         | I/O Pins 5V-tolerant <sup>(5)</sup>                     | 0.65 VDD                                                              | —                                                                                                                                                                                          | 5.5        | V     |                                                   |  |  |  |

| DI28          |         | SDAx, SCLx                                              | 0.65 VDD                                                              | _                                                                                                                                                                                          | 5.5        | V     | SMBus disabled<br>(Note 4,6)                      |  |  |  |

| DI29          |         | SDAx, SCLx                                              | 2.1                                                                   | _                                                                                                                                                                                          | 5.5        | V     | SMBus enabled,<br>2.3V ≤ VPIN ≤ 5.5<br>(Note 4,6) |  |  |  |

| DI30          | ICNPU   | Change Notification<br>Pull-up Current                  | _                                                                     | —                                                                                                                                                                                          | -50        | μA    | VDD = 3.3V, VPIN = VSS<br>(Note 3,6)              |  |  |  |

| DI31          | ICNPD   | Change Notification<br>Pull-down Current <sup>(4)</sup> | _                                                                     | —                                                                                                                                                                                          | -50        | μA    | VDD = 3.3V, VPIN = VDD                            |  |  |  |

|               | lı∟     | Input Leakage Current<br>(Note 3)                       |                                                                       |                                                                                                                                                                                            |            |       |                                                   |  |  |  |

| DI50          |         | I/O Ports                                               | _                                                                     | _                                                                                                                                                                                          | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD$ ,<br>Pin at high-impedance |  |  |  |

| DI51          |         | Analog Input Pins                                       | _                                                                     | _                                                                                                                                                                                          | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance  |  |  |  |

| DI55          |         | MCLR <sup>(2)</sup>                                     | —                                                                     | _                                                                                                                                                                                          | <u>+</u> 1 | μA    | $Vss \leq V PIN \leq V DD$                        |  |  |  |

| DI56          |         | OSC1                                                    | _                                                                     | _                                                                                                                                                                                          | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD,$<br>XT and HS modes        |  |  |  |

# TABLE 30-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Pin Diagrams" section for the 5V-tolerant pins.

- 6: The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

| DC CHA        |        | STICS                                                     | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 4): 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |         |      |       |                                                                                         |  |

|---------------|--------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|-----------------------------------------------------------------------------------------|--|

| Param.<br>No. | Symbol | Characteristics                                           | Min.                                                                                                                                                                                                                                                                                               | Typical | Max. | Units | Comments                                                                                |  |

| D300          | VIOFF  | Input Offset Voltage                                      | -                                                                                                                                                                                                                                                                                                  | ±7.5    | ±25  | mV    | AVDD = VDD,<br>AVSS = VSS                                                               |  |

| D301          | VICM   | Input Common Mode Voltage                                 | 0                                                                                                                                                                                                                                                                                                  | -       | Vdd  | V     | AVDD = VDD,<br>AVss = Vss<br>(Note 2)                                                   |  |

| D302          | CMRR   | Common Mode Rejection Ratio                               | 55                                                                                                                                                                                                                                                                                                 | —       | _    | dB    | Max VICM = (VDD - 1)V<br>(Note 2)                                                       |  |

| D303A         | TRESP  | Large Signal Response Time                                | _                                                                                                                                                                                                                                                                                                  | 150     | 400  | ns    | AVDD = VDD, AVSS = VSS<br>(Note 1,2)                                                    |  |

| D303B         | TSRESP | Small Signal Response Time                                | -                                                                                                                                                                                                                                                                                                  | 1       | _    | μS    | This is defined as an input<br>step of 50 mV with 15 mV<br>of overdrive <b>(Note 2)</b> |  |

| D304          | ON2ov  | Comparator Enabled to Output<br>Valid                     | _                                                                                                                                                                                                                                                                                                  | _       | 10   | μs    | Comparator module is<br>configured before setting<br>the comparator ON bit<br>(Note 2)  |  |

| D305          | IVREF  | Internal Voltage Reference                                | 1.14                                                                                                                                                                                                                                                                                               | 1.2     | 1.26 | V     | —                                                                                       |  |

| D312          | TSET   | Internal Comparator Voltage<br>DRC Reference Setting time | —                                                                                                                                                                                                                                                                                                  | —       | 10   | μs    | (Note 3)                                                                                |  |

#### TABLE 30-13: COMPARATOR SPECIFICATIONS

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

**2:** These parameters are characterized but not tested.

**3:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

**4:** The Comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

# TABLE 30-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS (CONTINUED)

| AC CHA        |                      | <b>FICS</b>                                        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |                        |      |       |            |  |  |

|---------------|----------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|------------|--|--|

| Param.<br>No. | Symbol               | Characteristics <sup>(1)</sup>                     | Min.                                                                                                                                                                                                                                                                              | Typical <sup>(2)</sup> | Max. | Units | Conditions |  |  |

| SP51          | TssH2doZ             | SSx ↑ to SDOx Output<br>High-Impedance<br>(Note 4) | 5                                                                                                                                                                                                                                                                                 | _                      | 25   | ns    | _          |  |  |

| SP52          | TscH2ssH<br>TscL2ssH | SSx ↑ after SCKx Edge                              | Тѕск +<br>20                                                                                                                                                                                                                                                                      | —                      | _    | ns    | —          |  |  |

| SP60          | TssL2doV             | SDOx Data Output Valid after<br>SSx Edge           | —                                                                                                                                                                                                                                                                                 | —                      | 25   | ns    |            |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 50 ns.

**4:** Assumes 50 pF load on all SPIx pins.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

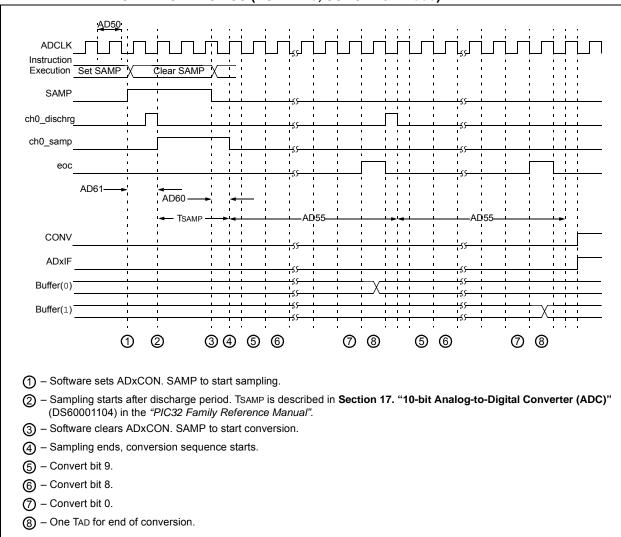

# FIGURE 30-18: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000)

# 33.1 Package Marking Information (Continued)

# 44-Lead VTLA

# 44-Lead QFN

# 44-Lead TQFP

Example

# Example

# Example

# Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                 | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (@3) |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|        |                                                                                                                                                                                          | can be found on the outer packaging for this package.                                                                                                                                                                                                                                                               |  |  |  |

| Note:  | If the full Microchip part number cannot be marked on one line, it is carried over to the next line, thus limiting the number of available characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                     |  |  |  |

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

NOTES:

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

**Poland - Warsaw** Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820