Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | MIPS32 ® M4K™                                                                  |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 23                                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 12x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

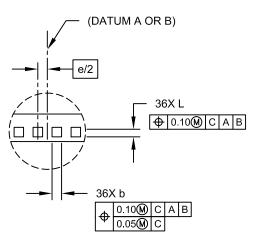

| Package / Case             | 36-VFTLA Exposed Pad                                                           |

| Supplier Device Package    | 36-VTLA (5x5)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx220f032c-i-tl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 5.1 Flash Controller Control Registers

### TABLE 5-1: FLASH CONTROLLER REGISTER MAP

|                             |                        |           |       | OOM INCLEASE THE MANAGEMENT OF THE PROPERTY OF |       |       |       |       |      |              |         |      |      |      |      |      |      |      |            |

|-----------------------------|------------------------|-----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|------|--------------|---------|------|------|------|------|------|------|------|------------|

| ess                         |                        | 3         |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |       |       |       |      | Bit          | s       |      |      |      |      |      |      |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range | 31/15 | 30/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8         | 23/7    | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| F400                        | NVMCON <sup>(1)</sup>  | 31:16     | _     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |       |       |       |      |              |         |      |      |      |      |      |      |      |            |

| F400                        | INVIVICOIN             | 15:0      | WR    | R WREN WRERR LVDERR LVDSTAT NVMOP<3:0> 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |       |       |       |      |              |         |      |      |      |      |      |      |      |            |

| F410                        | NVMKEY                 | 31:16     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |       |       |       |      | NVMKEY       | ′~31·0> |      |      |      |      |      |      |      | 0000       |

| 1 4 10                      | IN VIVINE I            | 15:0      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |       |       |       |      | IN V IVINL I | ~31.0>  |      |      |      |      |      |      |      | 0000       |

| F420                        | NVMADDR <sup>(1)</sup> | 31:16     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |       |       |       |      | NVMADD       | 2<31.0> |      |      |      |      |      |      |      | 0000       |

| 1 720                       | INVIVIADDIC: .         | 15:0      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |       |       |       |      | INVIVIADO    | ( 1.0   |      |      |      |      |      |      |      | 0000       |

| F430                        | NVMDATA                | 31:16     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |       |       |       |      | NVMDAT       | \<31·0> |      |      |      |      |      |      |      | 0000       |

| 1 +30                       | NVIVIDAIA              | 15:0      |       | NVMDATA<31:0> 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |       |       |       |      |              |         |      |      |      |      |      | 0000 |      |            |

| E440                        | NVMSRCADDR             | 31:16     |       | NVMSRCADDR<31:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |       |       |       |      |              |         |      |      |      |      |      |      |      |            |

| 1 +40                       | INVINIONCADDIN         | 15:0      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |       |       |       | i N  | VIVIOINOAL   | אטוי.טר |      |      |      |      |      |      |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

### REGISTER 7-4: IFSx: INTERRUPT FLAG STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS09            | IFS08            |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | IFS07             | IFS06             | IFS05             | IFS04             | IFS03             | IFS02             | IFS01            | IFS00            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 IFS31-IFS00: Interrupt Flag Status bits

1 = Interrupt request has occurred

0 = No interrupt request has occurred

Note: This register represents a generic definition of the IFSx register. Refer to Table 7-1 for the exact bit

definitions.

### REGISTER 7-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.6         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC09            | IEC08            |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | IEC07             | IEC06             | IEC05             | IEC04             | IEC03             | IEC02             | IEC01            | IEC00            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 IEC31-IEC00: Interrupt Enable bits

1 = Interrupt is enabled0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 7-1 for the exact bit definitions.

### REGISTER 9-8: DCHxECON: DMA CHANNEL 'x' EVENT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|----------------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 31:24        | U-0                        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 31.24        | _                          | _                 | _                 | _                 |                      | _                 | _                | _                |  |  |  |  |  |  |

| 22:46        | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |  |  |

| 23:16        | CHAIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                      |                   |                  |                  |  |  |  |  |  |  |

| 15:8         | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |  |  |

| 13.6         |                            |                   |                   | CHSIRQ-           | <7:0> <sup>(1)</sup> |                   |                  |                  |  |  |  |  |  |  |

| 7:0          | S-0                        | S-0               | R/W-0             | R/W-0             | R/W-0                | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 7.0          | CFORCE                     | CABORT            | PATEN             | SIRQEN            | AIRQEN               |                   | -                | _                |  |  |  |  |  |  |

Legend:S = Settable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-24 Unimplemented: Read as '0'

bit 23-16 CHAIRQ<7:0>: Channel Transfer Abort IRQ bits(1)

11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag

•

.

00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag 00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag

bit 15-8 CHSIRQ<7:0>: Channel Transfer Start IRQ bits<sup>(1)</sup>

11111111 = Interrupt 255 will initiate a DMA transfer

•

.

00000001 = Interrupt 1 will initiate a DMA transfer 00000000 = Interrupt 0 will initiate a DMA transfer

bit 7 CFORCE: DMA Forced Transfer bit

1 = A DMA transfer is forced to begin when this bit is written to a '1'

0 = This bit always reads '0'

bit 6 CABORT: DMA Abort Transfer bit

1 = A DMA transfer is aborted when this bit is written to a '1'

0 = This bit always reads '0'

bit 5 PATEN: Channel Pattern Match Abort Enable bit

1 = Abort transfer and clear CHEN on pattern match

0 = Pattern match is disabled

bit 4 SIRQEN: Channel Start IRQ Enable bit

1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs

0 = Interrupt number CHSIRQ is ignored and does not start a transfer

bit 3 AIRQEN: Channel Abort IRQ Enable bit

1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs

0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer

bit 2-0 Unimplemented: Read as '0'

Note 1: See Table 7-1: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

### REGISTER 10-11: U1CON: USB CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|

| 24.24        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 31:24        | _                 | _                 | _                        | _                 | -                     |                       | _                | _                    |

| 23:16        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 23.10        | _                 | -                 |                          | _                 | 1                     |                       | _                | _                    |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 15.6         | _                 | _                 | _                        | _                 | -                     |                       | _                | _                    |

|              | R-x               | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |

| 7:0          | ICTATE            | SE0               | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST           | USBEN <sup>(4)</sup> |

| JSTATE       |                   | SEU               | TOKBUSY <sup>(1,5)</sup> | USBRST            | HOSTEN                | RESUME                | FFDRSI           | SOFEN <sup>(5)</sup> |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

1 = JSTATE was detected on the USB

0 = No JSTATE was detected

bit 6 SE0: Live Single-Ended Zero flag bit

1 = Single-Ended Zero was detected on the USB

0 = No Single-Ended Zero was detected

bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

1 = Token and packet processing is disabled (set upon SETUP token received)

0 = Token and packet processing is enabled

TOKBUSY: Token Busy Indicator bit (1,5)

1 = Token is being executed by the USB module

0 = No token is being executed

bit 4 USBRST: Module Reset bit<sup>(5)</sup>

1 = USB reset generated

0 = USB reset terminated

bit 3 **HOSTEN:** Host Mode Enable bit<sup>(2)</sup>

1 = USB host capability is enabled

0 = USB host capability is disabled

bit 2 **RESUME:** RESUME Signaling Enable bit<sup>(3)</sup>

1 = RESUME signaling is activated

0 = RESUME signaling is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

### 11.1 Parallel I/O (PIO) Ports

All port pins have 10 registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

#### 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx, and TRISx registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V-tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the "Pin Diagrams" section for the available pins and their functionality.

# 11.1.2 CONFIGURING ANALOG AND DIGITAL PORT PINS

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs must have their corresponding ANSEL and TRIS bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

If the TRIS bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or Comparator module.

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 11.1.3 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP.

### 11.1.4 INPUT CHANGE NOTIFICATION

The input change notification function of the I/O ports allows the PIC32MX1XX/2XX 28/36/44-pin Family devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a change-of-state.

Five control registers are associated with the CN functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups act as a current source or sink source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

**Note:** Pull-ups and pull-downs on change notification pins should always be disabled when the port pin is configured as a digital output.

An additional control register (CNCONx) is shown in Register 11-3.

### 11.2 CLR, SET and INV Registers

Every I/O module register has a corresponding CLR (clear), SET (set) and INV (invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR, or INV register, the base register must be read.

| $\Box$ |

|--------|

| Ś      |

| 8      |

| 3000   |

| 0      |

| 0      |

| _      |

| _      |

| 0      |

| 89     |

| ے      |

|        |

| page   |

| ~      |

| ∺      |

| v      |

| _      |

| w      |

| 139    |

| _      |

|        |

|        |

| TABLE 11-7: | PERIPHERAL PIN SELECT OUTPUT REGISTER MAR | (CONTINUED) |

|-------------|-------------------------------------------|-------------|

|             |                                           |             |

| SS                          |                      |               |       |       |       |       |       |       |      | Ві   | its  |      |      |      |      |           |               |      |            |

|-----------------------------|----------------------|---------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-----------|---------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2      | 17/1          | 16/0 | All Resets |

| FB4C                        | RPB8R                | 31:16         | _     | _     | _     | _     | -     | _     | _    | _    | _    | _    | _    | _    | -    | _         | _             | _    | 0000       |

| 1 540                       | THE DOTA             | 15:0          |       | _     | _     | _     | _     |       | _    | _    |      | _    | _    | _    |      | RPB8      | 3<3:0>        |      | 0000       |

| FB50                        | RPB9R                | 31:16         |       | _     | _     | _     | _     |       | _    | _    |      | _    |      |      | -    | _         | _             | _    | 0000       |

| . 500                       | THE BOTT             | 15:0          |       | _     | _     | _     | _     |       | _    | _    |      | _    |      |      |      | RPB9      | >3:0>         |      | 0000       |

| FB54                        | RPB10R               | 31:16         |       | _     | _     | _     | _     |       | _    | _    | _    | _    |      |      | _    | _         | _             |      | 0000       |

| . 50.                       |                      | 15:0          |       | _     | _     | _     | _     |       | _    | _    | _    | _    |      |      |      | RPB10     | 0<3:0>        |      | 0000       |

| FB58                        | RPB11R               | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |           | _             | _    | 0000       |

|                             |                      | 15:0          | _     | _     | _     |       |       | _     | _    |      |      | _    | _    | _    |      | RPB1      | 1<3:0>        |      | 0000       |

| FB60                        | RPB13R               | 31:16         |       | _     | _     |       |       |       | _    |      |      | _    | _    | _    | _    | _         |               |      | 0000       |

|                             |                      | 15:0          |       | _     | _     |       |       |       | _    |      |      | _    | _    | _    |      | RPB1      |               |      | 0000       |

| FB64                        | RPB14R               | 31:16         |       | _     | _     |       | _     |       | _    |      |      | _    |      |      | -    |           |               |      | 0000       |

|                             |                      | 15:0          |       | _     | _     | _     | _     |       | _    | _    |      | _    |      |      |      | RPB1      | 4<3:0>        |      | 0000       |

| FB68                        | RPB15R               | 31:16         |       |       |       |       | _     |       | _    | _    |      |      |      |      |      |           | -             | _    | 0000       |

|                             |                      | 15:0          |       |       | _     | _     |       |       | _    | _    |      |      |      |      |      | RPB1      |               |      | 0000       |

| FB6C                        | RPC0R(3)             | 31:16         |       | _     | _     | _     |       |       | _    | _    | _    |      |      |      | _    | RPC0      | -             |      | 0000       |

|                             |                      | 15:0          |       | _     | _     | _     | _     |       | _    | _    | _    |      |      |      |      |           |               |      | 0000       |

| FB70                        | RPC1R <sup>(3)</sup> | 31:16         |       |       |       |       | _     |       |      |      |      | _    |      |      | _    |           | <3:0>         | _    | 0000       |

|                             |                      | 15:0<br>31:16 |       |       |       |       | _     |       |      |      |      | _    |      |      |      |           | 3.0>          | _    | 0000       |

| FB74                        | RPC2R <sup>(1)</sup> | 15:0          |       |       |       |       | _     |       |      |      |      | _    |      |      | _    | —<br>BDC2 | 2<3:0>        |      | 0000       |

|                             |                      |               | _     | _     | _     | _     |       | _     | _    |      |      | _    | _    | _    |      |           |               |      | 0000       |

| FB78                        | RPC3R <sup>(3)</sup> | 31:16<br>15:0 |       | _     | _     | _     |       |       | _    |      |      |      |      |      | _    | —<br>DDC3 | S<3:0>        | _    | 0000       |

|                             |                      | 31:16         |       | _     |       |       |       |       | _    | _    |      |      |      |      | _    | — KF03    | _             | _    | 0000       |

| FB7C                        | RPC4R <sup>(1)</sup> | 15:0          |       | _     |       |       |       |       |      |      |      |      |      |      | _    | RPC4      |               |      | 0000       |

|                             |                      | 31:16         |       | _     |       |       |       |       |      |      |      |      |      |      |      | KF 04     |               | _    | 0000       |

| FB80                        | RPC5R <sup>(1)</sup> | 15:0          |       | _     | _     |       |       |       | _    |      |      | _    |      |      |      |           | 5<3:0>        |      | 0000       |

|                             |                      | 31:16         |       | _     |       |       |       |       | _    |      |      |      |      |      |      | — KF03    | _             | _    | 0000       |

| FB84                        | RPC6R <sup>(1)</sup> | 15:0          |       | _     |       |       |       |       | _    |      |      |      |      |      | _    | RPC6      |               |      | 0000       |

| -                           |                      | 31:16         |       | _     |       |       |       |       | _    |      |      |      |      |      |      | — KF00    | _             | _    | 0000       |

| FB88                        | RPC7R <sup>(1)</sup> | 15:0          |       |       |       |       |       |       |      |      |      |      |      |      | _    | RPC7      |               |      | 0000       |

|                             |                      | 15.0          |       |       | _     | _     |       | _     | _    | _    |      | _    | _    |      |      | RPU/      | <b>~</b> 3.0≥ |      | 0000       |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register is only available on 44-pin devices. Note 1:

This register is only available on PIG32MX1XX devices. This register is only available on 36-pin and 44-pin devices.

### REGISTER 12-1: T1CON: TYPE A TIMER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | -                 | _                 | -                 | -                | _                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | U-0              | U-0              |

| 15.6         | ON <sup>(1)</sup> | _                 | SIDL              | TWDIS             | TWIP              | _                 | _                | _                |

| 7:0          | R/W-0 U-0         |                   | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7:0          | TGATE             | _                 | TCKPS             | S<1:0>            | _                 | TSYNC             | TCS              | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Timer On bit<sup>(1)</sup>

1 = Timer is enabled

0 = Timer is disabled

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

${\tt 1}$  = Discontinue module operation when the device enters Idle mode

0 = Continue module operation when the device enters Idle mode

bit 12 **TWDIS:** Asynchronous Timer Write Disable bit

1 = Writes to Timer1 are ignored until pending write operation completes

0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)

bit 11 **TWIP:** Asynchronous Timer Write in Progress bit

In Asynchronous Timer mode:

1 = Asynchronous write to the Timer1 register in progress

0 = Asynchronous write to Timer1 register is complete

In Synchronous Timer mode:

This bit is read as '0'.

bit 10-8 Unimplemented: Read as '0'

bit 7 TGATE: Timer Gated Time Accumulation Enable bit

$\frac{\text{When TCS} = 1:}{\text{This bit is ignored.}}$

When TCS = 0:

1 = Gated time accumulation is enabled

0 = Gated time accumulation is disabled

bit 6 Unimplemented: Read as '0'

bit 5-4 TCKPS<1:0>: Timer Input Clock Prescale Select bits

11 = 1:256 prescale value

10 = 1:64 prescale value

01 = 1:8 prescale value

00 = 1:1 prescale value

**Note 1:** When using 1:1 PBCmLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

### REGISTER 16-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                    | _                 | _                 | _                |                  |

| 22.40        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                    | _                 | _                 | -                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | _                    | _                 | _                 | _                | _                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Output Compare Peripheral On bit<sup>(1)</sup>

1 = Output Compare peripheral is enabled

0 = Output Compare peripheral is disabled

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Discontinue module operation when the device enters Idle mode

0 = Continue module operation when the device enters Idle mode

bit 12-6 Unimplemented: Read as '0'

bit 5 OC32: 32-bit Compare Mode bit

1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source

0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

bit 4 OCFLT: PWM Fault Condition Status bit<sup>(2)</sup>

1 = PWM Fault condition has occurred (cleared in hardware only)

0 = No PWM Fault condition has occurred

bit 3 OCTSEL: Output Compare Timer Select bit

1 = Timer3 is the clock source for this Output Compare module

0 = Timer2 is the clock source for this Output Compare module

bit 2-0 OCM<2:0>: Output Compare Mode Select bits

111 = PWM mode on OCx; Fault pin enabled

110 = PWM mode on OCx; Fault pin disabled

101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

100 = Initialize OCx pin low; generate single output pulse on OCx pin

011 = Compare event toggles OCx pin

010 = Initialize OCx pin high; compare event forces OCx pin low

001 = Initialize OCx pin low; compare event forces OCx pin high

000 = Output compare peripheral is disabled but continues to draw current

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

2: This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

### 17.1 SPI Control Registers

### TABLE 17-1: SPI1 AND SPI2 REGISTER MAP

|                             | LE 17-1                         |           | FIT AND SPIZ REGISTER MAP |         |        |              |              |              |          |        |         |           |        |        |             |          |        |        |            |

|-----------------------------|---------------------------------|-----------|---------------------------|---------|--------|--------------|--------------|--------------|----------|--------|---------|-----------|--------|--------|-------------|----------|--------|--------|------------|

| ess                         |                                 | 4         |                           |         |        |              |              |              |          | Bit    | ts      |           |        |        |             |          |        |        |            |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15                     | 30/14   | 29/13  | 28/12        | 27/11        | 26/10        | 25/9     | 24/8   | 23/7    | 22/6      | 21/5   | 20/4   | 19/3        | 18/2     | 17/1   | 16/0   | All Resets |

| 5900                        | SPI1CON                         | 31:16     | FRMEN                     | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2: | )>     | MCLKSEL | _         | -      | 1      | _           | 1        | SPIFE  | ENHBUF | 0000       |

| 3000                        | SFITCON                         | 15:0      | ON                        | _       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP      | CKE    | SSEN    | CKP       | MSTEN  | DISSDI | STXISE      | L<1:0>   | SRXISE | L<1:0> | 0000       |

| E010                        | SPI1STAT                        | 31:16     | _                         | _       | _      |              | RXE          | BUFELM<4:    | 0>       |        | _       | _         | 1      |        | TXI         | BUFELM<4 | :0>    |        | 0000       |

| 5610                        | SFIISIKI                        | 15:0      | _                         | _       | _      | FRMERR       | SPIBUSY      | -            |          | SPITUR | SRMT    | SPIROV    | SPIRBE |        | SPITBE      |          | SPITBF | SPIRBF | 8000       |

| 5820                        | SPI1BUF                         | 31:16     |                           |         |        |              |              |              |          | DATA<  | 31.0>   |           |        |        |             |          |        |        | 0000       |

| 3620                        | 51 11001                        | 15:0      |                           |         |        |              |              |              |          | DAIA   | 31.0    |           |        |        |             |          |        |        | 0000       |

| 5830                        | SPI1BRG                         | 31:16     |                           | _       | _      |              |              |              |          |        |         |           |        | _      | 0000        |          |        |        |            |

| 3030                        | oi Tibico                       | 15:0      |                           | _       | _      |              |              |              |          |        | E       | 3RG<12:0> |        |        |             |          |        |        | 0000       |

|                             |                                 | 31:16     | _                         | _       | _      | _            | _            | _            | _        | _      | _       | _         | _      | _      | _           | _        | _      | _      | 0000       |

| 5840                        | SPI1CON2                        | 15:0      | SPI<br>SGNEXT             | _       | _      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV   | IGNTUR | AUDEN   | _         | _      | _      | AUD<br>MONO | _        | AUDMO  | D<1:0> | 0000       |

| E A OO                      | SDI3CON                         | 31:16     | FRMEN                     | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2: | )>     | MCLKSEL | _         | -      | _      | _           | _        | SPIFE  | ENHBUF | 0000       |

| 5A00                        | SPI2CON                         | 15:0      | ON                        | _       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP      | CKE    | SSEN    | CKP       | MSTEN  | DISSDI | STXISE      | L<1:0>   | SRXISE | L<1:0> | 0000       |

| E A 40                      | SPI2STAT                        | 31:16     | _                         | _       | _      |              | RXE          | BUFELM<4:    | 0>       |        | _       | _         | 1      |        | TXI         | BUFELM<4 | :0>    |        | 0000       |

| 5A10                        | SPIZSTAT                        | 15:0      | _                         | _       | _      | FRMERR       | SPIBUSY      | -            | _        | SPITUR | SRMT    | SPIROV    | SPIRBE | _      | SPITBE      | _        | SPITBF | SPIRBF | 8000       |

| E A 20                      | SPI2BUF                         | 31:16     |                           |         |        |              |              |              |          | DATA<  | 21:05   |           |        |        |             |          |        |        | 0000       |

| 5A20                        | SFIZEOI                         | 15:0      |                           |         |        |              |              |              |          | DAIA   | 31.0    |           |        |        |             |          |        |        | 0000       |

| E A 20                      | SPI2BRG                         | 31:16     | _                         | _       | _      | -            | _            | -            | _        | _      | _       | _         | _      | _      | _           | _        | _      | _      | 0000       |

| 5A30                        | OI IZDINO                       | 15:0      |                           | _       | _      |              |              |              |          |        | E       | 3RG<12:0> |        |        |             |          |        |        | 0000       |

|                             |                                 | 31:16     |                           | _       | _      | _            | _            | _            | _        | _      | _       | _         | _      | _      | _           | _        | _      | _      | 0000       |

| 5A40                        | SPI2CON2                        | 15:0      | SPI<br>SGNEXT             | _       | -      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV   | IGNTUR | AUDEN   | _         | _      | 1      | AUD<br>MONO | 1        | AUDMO  | D<1:0> | 0000       |

egend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except SPIxBUF have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

### 19.1 UART Control Registers

### TABLE 19-1: UART1 AND UART2 REGISTER MAP

| ess                         |                       | •         |        |        |        |       |        |       |       | Bi          | ts          |         |       |             |        |      |        |       |            |

|-----------------------------|-----------------------|-----------|--------|--------|--------|-------|--------|-------|-------|-------------|-------------|---------|-------|-------------|--------|------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15  | 30/14  | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8        | 23/7        | 22/6    | 21/5  | 20/4        | 19/3   | 18/2 | 17/1   | 16/0  | All Resets |

| 6000                        | U1MODE <sup>(1)</sup> | 31:16     | _      | _      | _      | _     | _      | _     | _     | _           | _           | _       | _     | _           | _      | _    | _      | _     | 0000       |

| 0000                        | OTWODE                | 15:0      | ON     | _      | SIDL   | IREN  | RTSMD  | _     | UEN:  | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV       | BRGH   | PDSE | L<1:0> | STSEL | 0000       |

| 6010                        | U1STA <sup>(1)</sup>  | 31:16     | _      | _      | _      | _     | _      | _     | _     | ADM_EN      |             |         |       | ADDF        |        |      |        |       | 0000       |

| 0010                        | O IOIA.               | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXIS       | EL<1:0> | ADDEN | RIDLE       | PERR   | FERR | OERR   | URXDA | 0110       |

| 6020                        | U1TXREG               | 31:16     | _      | _      | _      | _     | _      | _     | -     | _           | _           | _       | _     | _           | _      | _    | _      | _     | 0000       |

| 0020                        | 0020 OTTAILE          |           | _      | _      | _      | _     | _      | _     | -     |             |             |         | Tra   | nsmit Regis | ster   |      |        |       | 0000       |

| 6030 U1RXI                  | U1RXREG               | 31:16     | _      | _      | _      | _     | _      | _     | -     | _           | _           | _       | _     | _           | _      | _    | _      | _     | 0000       |

| 0000                        | OTIVANLO              | 15:0      | _      | _      | _      | _     | _      | _     | -     |             |             |         | Re    | ceive Regis | ster   |      |        |       | 0000       |

| 6040                        | U1BRG <sup>(1)</sup>  | 31:16     | _      | _      | _      | _     | _      | _     | -     | _           | _           | _       | _     | _           | _      | _    | _      | _     | 0000       |

| 00+0                        | O IDICO.              | 15:0      |        |        |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |             |        | 00   |        |       | 0000       |

| 6200                        | U2MODE <sup>(1)</sup> | 31:16     | _      | _      | _      | _     | _      | _     | -     | _           | _           | _       | _     | _           | _      | _    | _      | _     | 0000       |

| 0200                        | 02MODE: 1             | 15:0      | ON     | _      | SIDL   | IREN  | RTSMD  | _     | UEN:  | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV       | BRGH   | PDSE | L<1:0> | STSEL | 0000       |

| 6210                        | U2STA <sup>(1)</sup>  | 31:16     | _      | _      | _      | _     | _      | _     | -     | ADM_EN      |             |         |       | ADDF        | R<7:0> |      |        |       | 0000       |

| 0210                        | 02017                 | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE      | EL<1:0> | ADDEN | RIDLE       | PERR   | FERR | OERR   | URXDA | 0110       |

| 6220                        | U2TXREG               | 31:16     | _      | _      | _      | _     | _      | _     | -     | _           | _           | _       | _     | _           | _      | _    | _      | _     | 0000       |

| 0220                        | OZIANLO               | 15:0      | _      | _      | _      | _     | _      | _     | _     |             |             |         | Tra   | nsmit Regis | ster   |      |        |       | 0000       |

| 6230                        | U2RXREG               | 31:16     | _      | _      | _      | _     | _      | _     | -     | _           | _           | _       | _     | _           | _      | _    | _      | _     | 0000       |

| 0230                        | UZIVANLU              | 15:0      | _      | _      | _      | _     | _      | _     | -     |             |             |         | Re    | ceive Regis | ster   |      |        |       | 0000       |

| 6240                        | U2BRG <sup>(1)</sup>  | 31:16     | _      | -      | _      | -     | _      | _     | I     | _           | _           | _       | -     |             | _      | _    | _      | _     | 0000       |

| 0240 0281                   | OZDNO,                | 15:0      |        |        |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |             |        |      |        |       | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

### REGISTER 19-1: UxMODE: UARTX MODE REGISTER